|

作者:Manish Patel

职务:德州仪器 (TI) DSP 系统部通信基础局端市场营销经理

专为无线通信基础局端 (CI) 的基站及其它类型系统定制的数字信号处理器 (DSP) 通常属于市场上处理速率最快、功能最强大的处理器之列。不过,如果 CI 系统开发人员只考虑频率的话,就会忽视针对 CI 优化的 DSP 的某些最关键的属性,而这些属性往往不仅有助于降低整体系统成本,简化软硬件设计,使当前设计能够满足今后多年的要求,而且还能提高其它重要的性能参数。

说到底,选择针对 CI 应用而精心优化的 DSP而不是通用的 DSP将会使设备制造商及其服务供应商受益匪浅。

多样性需要灵活性

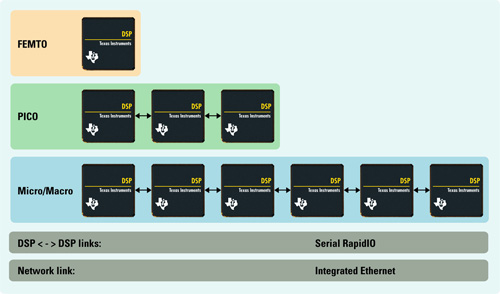

从实际角度讲,CI 市场的多样性与快速变化的特点要求设备制造商必须支持高度灵活的基础架构。例如,全球基站制造商必须使系统支持多种空中接口,如 GSM、CDMA、UMTS、EDGE 及中国的 TD-SCDMA 等。此外,如今设备的形状大小日益多样化,不可能再做到一劳永逸。若基站总是保持同样的尺寸,就不能满足需要。当前市场上出现了一种最新配置即所谓的“毫微微”基站,该基站非常小,小到足以作为家庭无线基站。除这种基站之外,微微基站、宏基站及超大型基站如今也非常普遍。基础架构应能实现低成本的扩展,可支持各种尺寸,这将使设备制造商受益匪浅。就可扩展性而言(如图 1所示),针对 CI 精心优化的 DSP 显然优于通用 DSP ,因为 CI DSP 通常包括诸如 RapidIO 等高度可扩展的高速串行接口。

图 1

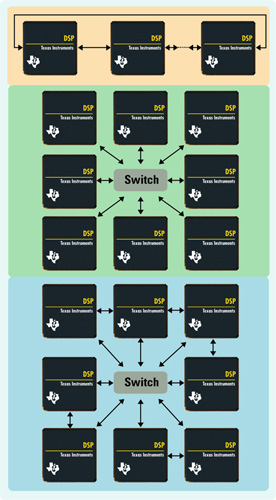

不同的CI 基站及其它类型系统的制造商也会遇到不同的板级架构问题。事实上,某部基站中的不同电路板会发挥完全不同的作用。有的电路板专用于接收信号,有的专用于发射信号,还有的则负责系统级运营管理和网络控制。由于功能多种多样,因此同一系统内的电路板拓扑也会大不相同。环形拓扑结构、网状拓扑结构、交换拓扑结构、星形拓扑结构等在业界都很普遍。

除上述各种变量之外,新特性、新功能及新服务仍在加速发展,业界标准也在不断推进。没有一定适应性的话,新型基站在推出后不久就会过时。与适用于通用信号处理的通用 DSP 不同,专为基站及其它 CI 系统优化的 DSP 能够确保其适用于不同空中接口、设备尺寸、设备级和板级架构,以及不断发展的技术要求。

适者生存

要在当前竞争激烈的 CI 市场中生存,DSP 必须不断提高其适应性。举例来说,可编程 CI DSP 能支持数种空中接口。这就简化了设备制造商新产品的开发过程,因为工程师能集中精力解决某款或某个系列 DSP 的问题,而不用为 DSP 采用哪种空中接口而发愁。此外,不同基站平台可采用统一的 DSP 技术,这就简化了制造商的技术支持和现场维修工作。

DSP 上的输入/输出 (I/O) 端口也会对其所支持架构的尺寸、可扩展性及范围产生巨大影响。与许多配有千兆以太网及 PCI Express 等通用外设接口的现成的型 DSP 不同,针对CI 优化的 DSP 采用的是 Serial RapidIO 等高速串行接口,可支持 DSP 间或芯片间的直接互连,而且还可作为背板总线。因具有内在的灵活性与较高的数据吞吐率,开放式标准 RapidIO 总线正日益成为新一代基站及其它 CI 系统的关键性能指标。RapidIO 通过 2 个或 4 个串行线路差分对进行互联,每个差分对的数据传输速率均达 3.125Gbps,潜在的总数据吞吐率可超过 12 Gbps。由于配置 RapidIO 串行线路非常灵活,因此可通过添加更多 DSP 来方便地扩展平台的基本功能,此外也可重新安排芯片间的串行互连,以支持多种架构配置(如图 2 所示)。

图 2

除采用 RapidIO 等高速外设接口之外,适用于 CI 应用的 DSP 还集成了某些精选的加速器与协处理器,这在一般的现成的 DSP 中是非常少见的。这种协处理器能分担 DSP 内核的部分处理任务,从而使其可以执行其它功能。通用 DSP 不采用这种专用的无线加速器,因此相对于 CI 优化型 DSP 而言,其性能较低,占用的处理周期更多,执行相关功能时需要更多的代码。

其它一些现成的 DSP 中不太常见的高速接口类型,如 OBSAI / CPRI 接口等,也在 CI 应用中日益普及,因为这些接口不仅提高了板上 DSP 的适应性,而且提高了系统的吞吐能力。这些接口主要用于将天线接口数据和 DSP 连接起来,以支持基带处理。

提高性能的压力巨大

新的无线用户数量不断增加,这就要求基础局端系统不断改进语音与数据通信性能。多年来,随着 DSP 技术不断发展,系统设计人员只需在基站电路板中增加更多 DSP就能提高系统性能。不幸的是,这种方法也有其局限性。电路板的物理空间限制了板上集成的 DSP 数量,如果同一电路板上集成的 DSP 过多,就会因功耗而引起散热问题。在基站的小型密闭空间内的高温问题,很快就会影响到电子器件的可靠性。

与其它多内核 DSP 处理器不同,CI 专用的多内核 DSP 集成了节能机制,以尽可能减少散热。这样就可以在空间不变的情况下提高吞吐能力,同时降低系统过热的危险。此外,一些专为 CI 系统设计的 DSP 还具有功耗和性能监控功能。DSP 芯片本身能识别系统的工作温度,在不影响性能和吞吐能力的情况下,芯片可以降低内核电压,以减小功耗和热消散。这使 CI DSP 能在预期的性能水平上工作,同时又保持整体功耗不超标。

一些 CI DSP 还集成了片上协处理器,有的协处理器可以完成专门的无线通信任务。举例来说,实践证明,支持语音处理的 Viterbi 协处理器也能加速数据通信,成为非常有用的数据型协处理器。协处理器可减轻主 DSP 内核或内核的处理任务,从而提高设备的数据吞吐量,并使内核 DSP能够处理其它更重要的工作。此外,专门的协处理器还能执行诸如加速某些空中接口的接收速率等工作,这种接收加速器可接收 W-CDMA 天线信号,在向 DSP 传输数据之前就能进行很多重要的数据关联处理。

CI DSP 集成了专门的协处理器功能后,采用独立设备来完成任务的需求就会降低。举例来说,在许多基站设计中,专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA) 通常配合 DSP 使用,来处理辅助性任务。在有些情况下,针对CI 精心优化的 DSP 可完成这些任务,从而减少了芯片数量,降低了整体系统成本。

有些 CI 优化型 DSP 还专为执行网络控制操作进行了精心优化,进一步加强了集成技术的发展趋势,无需专门执行上述功能的通用微处理器或 RISC 处理器。

软件捷径

针对CI 应用优化的 DSP 的软件环境与架构对系统的吞吐能力、整体开发成本及产品上市时间都有很大影响。为了满足无线通信领域中的一些重复性功能需求,最新或增强型指令通常都集成在 CI DSP 上。例如,最新的指令集架构 (ISA) 可提高信号速率、芯片速率与矩阵数学处理能力,从而增强基站中 DSP 的性能;高级 ISA 还能提高电路板的密度,从而降低每通道的系统成本;高效 ISA 则能缩减系统软件代码,减少外部存储器占用的板级空间,从而释放出一定的存储空间,以满足关键任务数据的存储需求。(图 3)通用 DSP 肯定支持编程,可执行通信功能,然而,若不采用 CI 专用的 ISA 的话,执行同一功能时,通用 DSP 将会比集成 CI ISA 架构的优化型 DSP 需要多三至四倍的指令及更多的指令空间与编程时间。

图 3

除面向 CI 应用的 ISA 之外,一些厂商还提供专为 DSP 而优化的 CI 功能例程库。这些例程只需一个指令就能执行多种功能,避免分别执行,从而缩减代码并提高性能。

在 CI DSP 升级过程中保持软件的连续性对缩短开发周期,加速 CI 系统新产品上市进程有着巨大的影响。为保持合理的开发成本,大部分 DSP 软件都应支持升级与重复使用特性,旧设备的软件可在新设备上通用。

针对 CI 而优化

CI 市场错综复杂,有着特殊的要求,因此,大多数通用 DSP 在无线基站等应用中难以胜任,不如 CI 优化型 DSP 管用。在要求较高的基础局端系统中部署现成的通用 DSP,需要制造商进行更多设计工作,这会延长系统上市时间。与之相反,CI 专用 DSP 在时钟速度上属于市场上功能最强大的产品之列。同样重要的是,这些器件还提供适当的外设集与存储器接口,支持适当的加速器、高速内部存储器、通信协处理器、高级 CI 专用软件及多种其它功能,可优化系统开发,加速高吞吐能力的系统的推出。

插图说明

图 1——说明:基站的配置日益向着外形多样化的方向发展,从最小的所谓“毫微微”家用配置开始,逐渐发展到微微、微型和大型等多种规模。

图 2——说明:针对 CI 应用的 DSP 上的高速串行 IO 接口在支持多种拓扑方面非常有用,具体取决于系统类型与电路板功能。

图 3——说明:小型指令集架构 (ISA) 缩小了系统软件代码占用的存储器尺寸,在不增加系统成本的前提下释放了存储空间,以支持更多通道。

|