ZHCSDB8A February 2014 – August 2014 LP8754

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 General Electrical Characteristics

- 6.6 6-Phase Buck Electrical Characteristics

- 6.7 6-Phase Buck System Characteristics

- 6.8 Protection Features Characteristics

- 6.9 I2C Serial Bus Timing Parameters

- 6.10 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Features Descriptions

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6

Register Maps

- 7.6.1 Register Descriptions

- 7.6.2 VSET_B0

- 7.6.3 FPWM

- 7.6.4 BUCK0_CTRL

- 7.6.5 BUCK1_CTRL

- 7.6.6 BUCK2_CTRL

- 7.6.7 BUCK3_CTRL

- 7.6.8 BUCK4_CTRL

- 7.6.9 BUCK5_CTRL

- 7.6.10 FLAGS_0

- 7.6.11 FLAGS_1

- 7.6.12 INT_MASK_0

- 7.6.13 GENERAL

- 7.6.14 RESET

- 7.6.15 DELAY_BUCK0

- 7.6.16 CHIP_ID

- 7.6.17 PFM_LEV_B0

- 7.6.18 PHASE_LEV_B0

- 7.6.19 SEL_I_LOAD

- 7.6.20 LOAD_CURR

- 7.6.21 INT_MASK_2

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械封装和可订购信息

1 特性

- 6 个高效降压 DC-DC 转换器内核:

- 最大输出电流为 10A

- 各内核捆绑到一个 6 相位转换器

- 负载电流报告

- 可编程过流保护 (OCP)

- 自动脉宽调制 (PWM)/脉冲频率调制 (PFM) 和强制 PWM 操作以及自动低功耗模式设置

- 自动增相/切相

- 远程差分反馈电压感测

- 输出电压斜升控制

- VOUT 范围为 0.6V 至 1.67V进行动态电压调节 (DVS)

- I2C 兼容接口,支持标准 (100kHz)、快速 (400kHz) 和高速 (3.4MHz) 三种模式

- 四个可选的 I2C 地址

- 具有可编程屏蔽的中断功能

- 输出短路和输入过压保护 (OVP)

- 扩展频谱与相位控制,用于降低电磁干扰 (EMI)

- 过温保护 (OTP)

- 欠压闭锁 (UVLO)

2 应用

- 智能手机、电子书和平板电脑

- GSM、GPRS、EDGE、LTE、CDMA 和 WCDMA 手机

- 游戏设备

3 说明

LP8754 旨在满足移动电话和类似便携式应用中最新应用处理器的电源管理需求。 此器件包含 6 个降压 DC-DC 转换器内核,一起捆绑在 6 相位降压转换器中,。 此器件由动态电压调节 (DVS) 接口或 I2C 兼容串行接口完全控制。

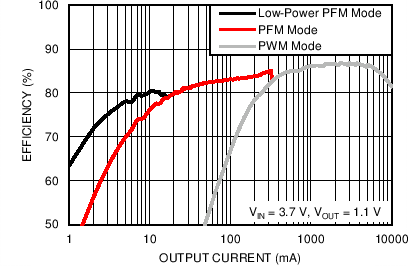

自动 PWM/PFM 操作搭配自动增相/切相功能,最大程度提高了宽泛输出电流范围内的效率。 LP8754 支持进行远程差分电压感测,以补偿稳压器输出与负载点之间的 IR 下降,从而提高输出电压的精度。

保护特性包括短路保护、电流限制、输入 OVP、UVLO、温度警告以及关断功能。 此器件还提供多个错误标志,用于指示集成电路 (IC) 的状态信息。 此外,I2C 回读信息包括总负载电流以及各降压内核的负载电流:LP8754 无需添加电流感测电阻就能感测到传递给负载的电流。在启动期间,器件会控制输出电压转换率,以最大程度降低过冲和浪涌电流。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(最大值) |

|---|---|---|

| LP8754 | DSBGA (49) | 3.022mm x 2.882mm |

- 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

效率与 负载电流间的关系

4 修订历史记录

| 日期 | 修订版本 | 注释 |

|---|---|---|

| 2014 年 8 月 | 版本 A | 初始 Web 版本 |

Changes from * Revision (February 2014) to A Revision

- Changed “端子”至“引脚”;已根据 SDS 标准进行少量修改;自定义 DS(删除 NDA 限制标题)的目录以用于 WEB 发布Go