ZHCSDX7B August 2012 – June 2015 DS1776QML

PRODUCTION DATA.

- 1特性

- 2说明

- 3修订历史记录

- 4Pin Configuration and Functions

-

5Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommend Operating Conditions

- 5.4 Thermal Information

- 5.5 Quality Conformance Inspection

- 5.6 Pi Bus Transceiver DS1776 DC Parameters

- 5.7 Pi Bus Transceiver DS1776 AC Parameters: B To A Path

- 5.8 Pi Bus Transceiver DS1776 AC Parameters: A To B Path

- 5.9 Pi Bus Transceiver DS1776 AC Parameters: Setup / Hold / Pulse Width Specifications

- 5.10 Test Circuit And Waveforms

- 6Detailed Description

- 7器件和文档支持

- 8机械、封装和可订购信息

1 特性

- 类似于桥接负载 (BTL)

- 低功耗 ICCL = 41mA(最大值)

- B 输出控制的斜率

- B 输入抗扰度:4ns(典型值)

- 与 Signetics 54F776 引脚和功能兼容

2 说明

DS1776 是一款八路 PI 总线收发器。 A 到 B 的路径被锁存。 B 输出是串联肖特基二极管的集电极开路输出,可确保将 B 输出负载降至最低。 B 输出还具有斜升和斜降时间(典型值为 2.5ns),可确保将 PI 总线振铃最小化。 B 输入具有毛刺脉冲抑制电路,典型值为 4ns。

该器件采用德州仪器 (TI) 的双极互补金属氧化物半导体 (Bi-CMOS) 工艺设计,在工作和禁用状态下均可实现低功耗。 其交流性能针对 PI 总线的互操作性要求进行了优化。

DS1776 是一款八路锁存收发器,旨在为高性能线或总线提供电气接口。 该总线的负载特性阻抗范围为 20Ω 至 50Ω,两端采用 30Ω 至 40Ω 范围内的电阻进行端接。

DS1776 是一款具有集电极开路 B 和三态 A 端口输出驱动器的八路双向收发器。 该器件为 A 端口信号提供了锁存功能。 B 端口输出驱动器设计为在 2V 电压时具有 100mA 灌电流,并且特有受控线性斜坡,能够最大限度降低总线上的串扰和振铃。

该器件提供了独立的高电平控制电压 (VX),以防止 A 侧输出高电平超过未来高密度处理器的电源电压。 对于 5V 系统,VX 连接至 VCC。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| DS1776QML | LCCC (FK) | 11.43mm x 11.43mm |

- 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

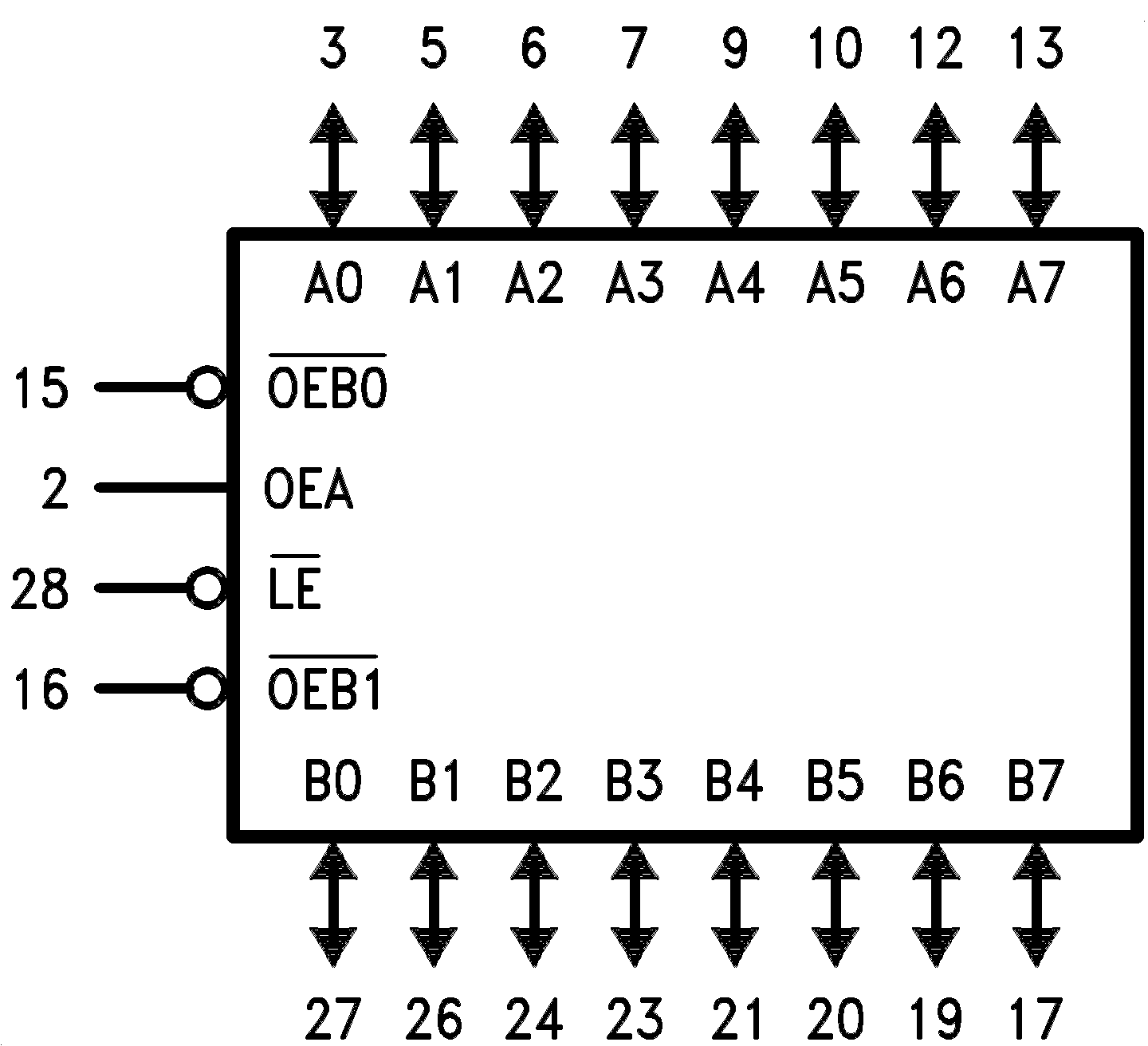

逻辑符号

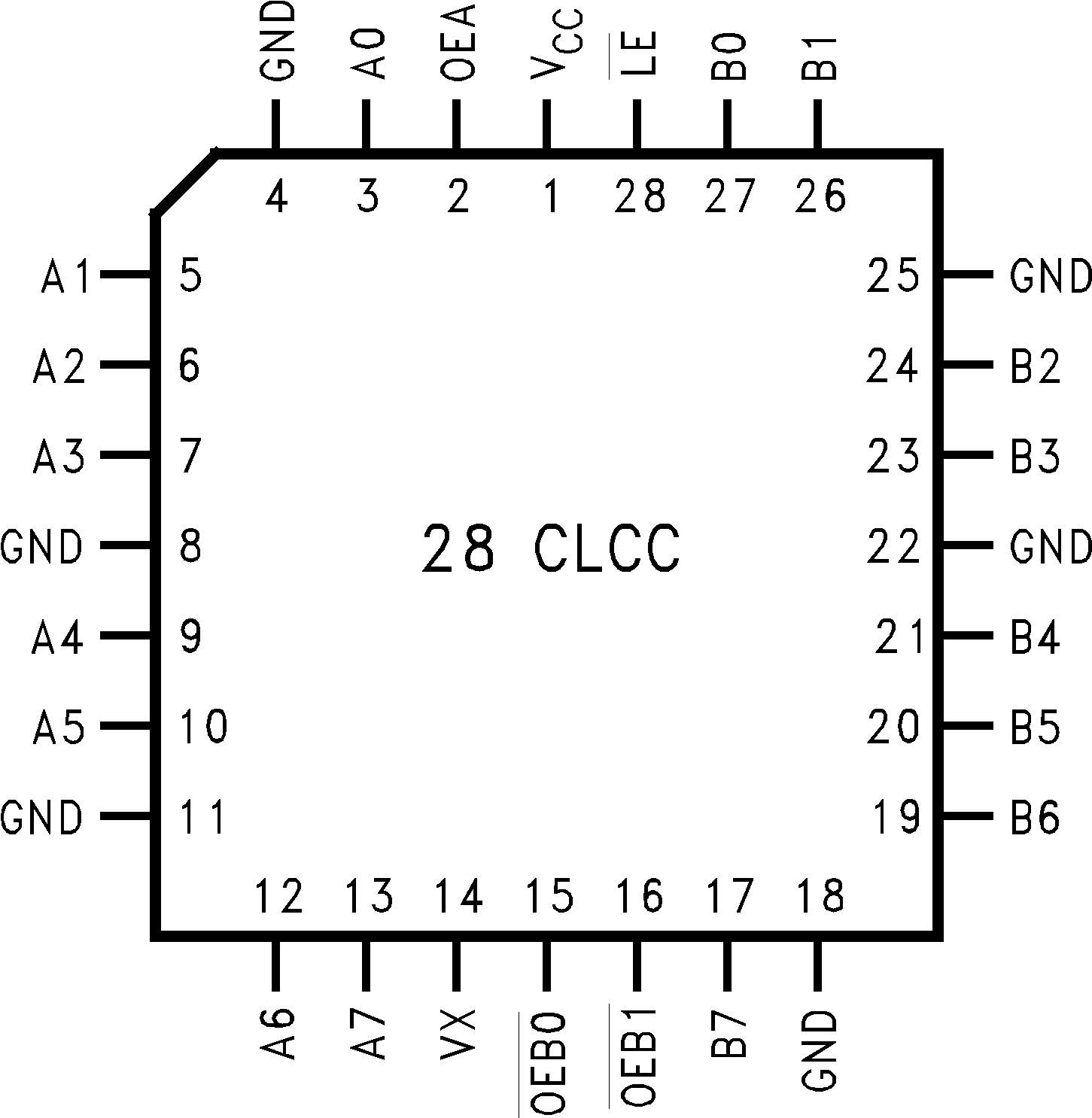

4 Pin Configuration and Functions

LCCC Package

FK0028A

Top View

Pin Descriptions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| A0 | 3 | I/O | TTL Level, latched input/TRI-STATE output (with VX control option) |

| A1 | 5 | I/O | |

| A2 | 6 | I/O | |

| A3 | 7 | I/O | |

| A4 | 9 | I/O | |

| A5 | 10 | I/O | |

| A6 | 12 | I/O | |

| A7 | 13 | I/O | |

| B0 | 27 | I/O | Data input with special threshold circuitry to reject noise/Open Collector output, High current drive |

| B1 | 26 | I/O | |

| B2 | 24 | I/O | |

| B3 | 23 | I/O | |

| B4 | 21 | I/O | |

| B5 | 20 | I/O | |

| B6 | 19 | I/O | |

| B7 | 17 | I/O | |

| OEB 0 | 15 | I | Enables the B outputs when both pins are low |

| OEB 1 | 16 | I | |

| OEA | 2 | I | Enables the A outputs when High |

| LE | 28 | I | Latched when High (a special delay feature is built in for proper enabling times) |

| VX | 14 | I | Clamping voltage keeping VOH from rising above VX (VX = VCC for normal use) |