ZHCSBF4B July 2013 – September 2015 ADS42JB46

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: ADS42JB46

- 7.6 Electrical Characteristics: General

- 7.7 Timing Characteristics

- 7.8 Digital Characteristics

- 7.9 Reset Timing

- 7.10 Serial Interface Timing

- 7.11 Typical Characteristics: ADS42JB46

- 7.12 Typical Characteristics: Contour

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 Summary of Serial Interface Registers

- 8.6.2

Description of Serial Interface Registers

- 8.6.2.1 Register Address 06

- 8.6.2.2 Register Address 07

- 8.6.2.3 Register Address 08

- 8.6.2.4 Register Address 0B

- 8.6.2.5 Register Address 0C

- 8.6.2.6 Register Address 0D

- 8.6.2.7 Register Address 0E

- 8.6.2.8 Register Address 0F

- 8.6.2.9 Register Address 10

- 8.6.2.10 Register Address 11

- 8.6.2.11 Register Address 12

- 8.6.2.12 Register Address 13

- 8.6.2.13 Register Address 1F

- 8.6.2.14 Register Address 26

- 8.6.2.15 Register Address 27

- 8.6.2.16 Register Address 2B

- 8.6.2.17 Register Address 2C

- 8.6.2.18 Register Address 2D

- 8.6.2.19 Register Address 30

- 8.6.2.20 Register Address 36

- 8.6.2.21 Register Address 37

- 8.6.2.22 Register Address 38

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

1 特性

- 双通道模数转换器 (ADC)

- 14 位分辨率

- 最大时钟速率:160MSPS

- JESD204B 串口

- 与子类别 0,1,2 兼容

- 高达 3.125Gbps

- 支持两信道和四信道

- 具有高阻抗输入的模拟输入缓冲器

- 灵活的输入时钟缓冲器:

1,2 和 4 分频 - 差分满量程输入:2VPP和 2.5VPP

(寄存器可编程) - 封装:9mm x 9mm 四方扁平无引线 (QFN)-64 封装

- 功率耗散:每通道 679mW

- 间隙抖动:85 fsrms

- 内部抖动

- 通道隔离:100dB

- 性能:

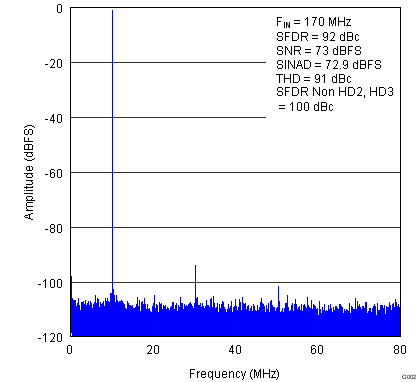

- 2 VPP,-1 dBFS 时,f输入 = 170MHz

- 信噪比 (SNR):72.9dBFS

- 无杂散动态范围 (SFRD):对于二次谐波 (HD2),三次谐波 (HD3) 为 90dBc

- SFDR:对于非 HD2,HD3 为 100dBc

- 2.5 VPP,-1 dBFS 时,f输入 = 170MHz

- 信噪比 (SNR):74.2dBFS

- SFDR:对于 HD2,HD3 为 84dBc

对于非 HD2,HD3 为 95dBc

- 2 VPP,-1 dBFS 时,f输入 = 170MHz

2 应用

- 通信和线缆基础设施

- 多载波、多模蜂窝接收器

- 雷达和智能天线阵列

- 宽带无线

- 测试和测量仪器

- 软件定义的和多样性射频

- 微波和双通道 I/O 接收器

- 集线器

- 功率放大器线性化

3 说明

ADS42JB46 是一款高线性,双通道,14 位,160MSPS,模数转换器 (ADC)。此器件支持数据速率高达 3.125Gbps 的 JESD204B 串口。经缓冲的模拟输入在大大降低采样保持毛刺脉冲能量的同时提供统一的输入阻抗,从而轻松地将模拟输入驱动至极高输入频率。采样时钟分频器可实现更灵活的系统时钟架构设计。此器件采用内部抖动算法来在宽输入频率范围内提供出色的无杂散动态范围 (SFDR)。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| ADS42JB46 | VQFN (64) | 9.00mm x 9.00mm |

- 要了解所有可用封装,请见数据表末尾的可订购产品附录。

简化电路原理图

160 MSPS 时采样的 170MHz 输入信号的快速傅立叶变换 (FFT)