## OMAP5912 Multimedia Processor Multimedia Card (MMC/SD/SDIO) Interface Reference Guide

Literature Number: SPRU765A March 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from TI under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

St Office Box 055505 Dallas, Texas 75205

Copyright © 2004, Texas Instruments Incorporated

## Preface

## **Read This First**

#### About This Manual

This document describes the multimedia card (MMC) interface of the OMAP5912 multimedia processor.

### Notational Conventions

This document uses the following conventions.

Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### **Related Documentation From Texas Instruments**

The following documents describe the OMAP5910 device and related peripherals. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- **OMAP5912** Multimedia Processor Device Overview and Architecture Reference Guide (literature number SPRU748) introduces the setup, components, and features of the OMAP5912 multimedia processor and provides a high-level view of the device architecture.

- OMAP5912 Multimedia Processor OMAP 3.2 Subsystem Reference Guide (literature number SPRU749) introduces and briefly defines the main features of the OMAP3.2 subsystem of the OMAP5912 multimedia processor.

- **OMAP5912** Multimedia Processor DSP Sybsystem Reference Guide (literature number SPRU750) describes the OMAP5912 multimedia processor DSP subsystem. The digital signal processor (DSP) subsystem is built around a core processor and peripherals that interface with: 1) The ARM926EJS via the microprocessor unit interface (MPUI); 2) Various standard memories via the external memory interface (EMIF); 3) Various system peripherals via the TI peripheral bus (TIPB) bridge.

- **OMAP5912** Multimedia Processor Clocks Reference Guide (literature number SPRU751) describes the clocking mechanisms of the OMAP5912 multimedia processor. In OMAP5912, various clocks are created from special components such as the digital phase locked loop (DPLL) and the analog phase-locked loop (APLL).

- **OMAP5912** Multimedia Processor Initialization Reference Guide (literature number SPRU752) describes the reset architecture, the configuration, the initialization, and the boot ROM of the OMAP5912 multimedia processor.

- **OMAP5912 Multimedia Processor Power Management Reference Guide** (literature number SPRU753) describes power management in the OMAP5912 multimedia processor. The ultralow-power device (ULPD) generates and manages clocks and reset signals to OMAP3.2 and to some peripherals. It controls chip-level power-down modes and handles chip-level wake-up events. In deep sleep mode, this module is still active to monitor wake-up events. This book describes the ULPD module and outline architecture.

- **OMAP5912 Multimedia Processor Security Features Reference Guide** (literature number SPRU754) describes the security features of teh OMAP5912 multimedia processor. The OMAP5912 security scheme relies on the OMAP3.2 secure mode. The distributed security on the OMAP3.2 platform is a Texas Instruments solution to address m-commerce and security issues within a mobile phone environment. The OMAP3.2 secure mode was developed to bring hardware robustness to the overall OMAP5912 security scheme.

- OMAP5912 Multimedia Processor Direct Memory Access (DMA) Support Reference Guide (literature number SPRU755) describes the direct memory access support of the OMAP5912 multimedia processor. The OMAP5912 processor has three DMAs:

- The system DMA is embedded in OMAP3.2. It handles DMA transfers associated with MPU and shared peripherals.

- The DSP DMA is embedded in OMAP3.2. It handles DMA transfers associated with DSP peripherals.

- The generic distributed DMA (GDD) is an OMAP5912 resource attached to the SSI peripheral. It handles only DMA transfers associated with the SSI peripheral.

4 OMAP5912

OMAP5912 Multimedia Processor Memory Interfaces Reference Guide

(literature number SPRU756) describes the memory interfaces of the OMAP5912 multimedia processor.

- SDRAM (external memory interface fast, or EMIFF)

- Asynchronous and synchronous burst memory (external memory interface slow, or EMIFS)

- NAND flash (hardware controller or software controller)

- CompactFlash on EMIFS interface

- Internal static RAM

**OMAP5912** Multimedia Processor Interrupts Reference Guide (literature number SPRU757) describes the interrupts of the OMAP5912 multimedia processor. Three level 2 interrupt controllers are used in OMAP5912:

- One MPU level 2 interrupt handler (also referred to as MPU interrupt level 2) is implemented outside of OMAP3.2 and can handle 128 interrupts.

- One DSP level 2 interrupt handler (also referred to as DSP interrupt level 2.1) is instantiated outside of OMAP3.2 and can handle 64 interrupts.

- One OMAP3.2 DSP level 2 interrupt handler (referenced as DSP interrupt level 2.0) can handle 16 interrupts.

- OMAP5912 Multimedia Processor Peripheral Interconnects Reference Guide (literature number SPRU758) describes various periperal interconnects of the OMAP5912 multimedia processor.

- **OMAP5912** Multimedia Processor Timers Reference Guide (literature number SPRU759) describes various timers of the OMAP5912 multimedia processor.

- **OMAP5912 Multimedia Processor Serial Interfaces Reference Guide** (literature number SPRU760) describes the serial interfaces of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Universal Serial Bus (USB) Reference Guide (literature number SPRU761) describes the universal serial bus (USB) host on the OMAP5912 multimedia processor. The OMAP5912 processor provides several varieties of USB functionality. Flexible multiplexing of signals from the OMAP5912 USB host controller, the OMAP5912 USB function controller, and other OMAP5912 peripherals allow a wide variety of system-level USB capabilities. Many of the OMAP5912 pins can be used for USB-related signals or for signals from other OMAP5912 peripherals. The OMAP5912 top-level pin multiplexing

controls each pin individually to select one of several possible internal pin signal interconnections. When these shared pins are programmed for use as USB signals, the OMAP5912 USB signal multiplexing selects how the signals associated with the three OMAP5912 USB host ports and the OMAP5912 USB function controller can be brought out to OMAP5912 pins.

- OMAP5912 Multimedia Processor Multi-channel Buffered Serial Ports (McBSPs) Reference Guide (literature number SPRU762) describes the three multi-channel buffered serial ports (McBSPs) available on the OMAP5912 device. The OMAP5912 device provides multiple highspeed multichannel buffered serial ports (McBSPs) that allow direct interface to codecs and other devices in a system.

- **OMAP5912** Multimedia Processor Camera Interface Reference Guide (literature number SPRU763) describes two camera inerfaces implemented in the OMAP5912 multimedia processor: compact serial camera port and camera parallel interface.

- **OMAP5912** Multimedia Processor Display Interface Reference Guide (literature number SPRU764) describes the display interface of the OMAP5912 multimedia processor.

- LCD module

- LCD data conversion module

- LED pulse generator

- Display interface

- **OMAP5912** Multimedia Processor Multimedia Card (MMC/SD/SDIO) (literature number SPRU765) describes the multimedia card (MMC) interface of the OMAP5912 multimedia processor. The multimedia card/secure data/secure digital IO (MMC/SD/SDIO) host controller provides an interface between a local host, such as a microprocessor unit (MPU) or digital signal processor (DSP), and either an MMC or SD memory card, plus up to four serial flash cards. The host controller handles MMC/SD/SDIO or serial port interface (SPI) transactions with minimal local host intervention.

- **OMAP5912 Multimedia Processor Keyboard Interface Reference Guide** (literature number SPRU766) describes the keyboard interface of the OMAP5912 multimedia processor. The MPUIO module enables direct I/O communication between the MPU (through the public TIPB) and external devices. Two types of I/O can be used: specific I/Os dedicated for 8 x 8 keyboard connection, and general-purpose I/Os.

- OMAP5912 Multimedia Processor General-Purpose Interface Reference Guide (literature number SPRU767) describes the general-purpose in-

terface of the OMAP5912 multimedia processor. There are four GPIO modules in the OMAP5912. Each GPIO peripheral controls 16 dedicated pins configurable either as input or output for general purposes. Each pin has an independent control direction set by a programmable register. The two–edge control registers configure events (rising edge, falling edge, or both edges) on an input pin to trigger interrupts or wake–up requests (depending on the system mode). In addition, an interrupt mask register masks out specified pins. Finally, the GPIO peripherals provide the set and clear capabilities on the data output registers and the interrupt mask registers. After detection, all event sources are merged and a single synchronous interrupt (per module) is generated in active mode, whereas a unique wake–up line is issued in idle mode. Eight data output lines of the GPIO3 are ORed together to generate a global output line at the OMAP5912 boundary. This global output line can be used in conjunction with the SSI to provide a CMT–APE interface to the OMAP5912.

OMAP5912 Multimedia Processor VLYNQ Serial Communications Interface Reference Guide (literature number SPRU768) describes the VLYNQ of the OMAP5912 multimedia processor.

VLYNQ is a serial communications interface that enables the extension of an internal bus segment to one or more external physical devices. The external devices are mapped into local, physical address space and appear as if they are on the internal bus of the OMAP 5912. The external devices must also have a VLYNQ interface. The VLYNQ module serializes bus transactions in one device, transfers the serialized data between devices via a VLYNQ port, and de-serializes the transaction in the external device.

OMAP5912 includes one VLYNQ module connected on OCPT2 target port and OCPI initiator port. These connections are configured via a static switch, which selects either SSI or VLYNQ module. This switch, forbids the simultaneous use of GDD/SSI and VLYNQ. The switch is controlled by the VLYNQ\_EN bit in the OMAP5912 configuration control register (CONF\_5912\_CTRL).

**OMAP5912 Multimedia Processor Pinout Reference Guide** (literature number SPRU769) provides the pinout of the OMAP5912 multimedia processor. After power-up reset, the user can change the configuration of the default interfaces. If another interface is available on top of the default, it is possible to enable a new interface for each ball by setting the corresponding 3-bit field of the associated FUNC\_MUX\_CTRL register. It is also possible to configure on-chip pullup/pulldown. This document

also describes the various power domains so that the user can apply the different interfaces seamlessly with external components.

- **OMAP5912** Multimedia Processor Window Tracer (WT) Reference Guide (literature number SPRU770) describes the window tracer module used to capture the memory transactions from four interfaces: EMIFF, EMIFS, OCP-T1, and OCP-T2. This module is located in the OMAP3.2 traffic controller (TC).

- **OMAP5912 Multimedia Processor Real-Time Clock Reference Guide** (literature number SPRUxxx) describes the real-time clock of the OMAP5912 multimedia processor. The real-time clock (RTC) block is an embedded real-time clock module directly accessible from the TIPB bus interface.

### Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

## Contents

| 2       MMC Registers       22         MMC.CMD/SPI.DO[15] Data Direction (DDIR)       24         MMC.CMD/SPI.DO[14] Stream Command or Broadcast Host Response (SHR)       25         MMC.CMD/SPI.DD[13:12] Command Type (TYPE)       25         MMC.CMD/SPI.DO[10:8] Command Response (RSP)       26         MMC.CMD/SPI.DO[17] Send Initialization Stream/Data Abort Command (INAB)       26         MMC.CMD/SPI.DO[7] Send Initialization Stream/Data Abort Command (INAB)       26         MMC.CMD/SPI.DO[6] Card Open Drain Mode/Extended Command Time-Out (ODTO)       27         MMC.CON[51] Bus Width During Data Phase (DW)       29         MMC_CON[15] Bus Width During Data Phase (DW)       29         MMC_CON[11] Power-Up Control (POW)       30         MMC_CON[10] Big Endian (BE)       30         MMC_CON[10] Big Endian (BE)       30         MMC_STAT[14] Card Status Error (CERR)       35         MMC_STAT[13] Card IRQ (CIRQ)       35         MMC_STAT[13] Buffer Almost Empty (AE)       36         MMC_STAT[11] Buffer Almost Full (AF)       37         MMC_STAT[12] CCR Busy (OCRB)       38         MMC_STAT[13] Gord Read Wait (CRW)       38         MMC_STAT[19] Card Read Wait (CRW)       38         MMC_STAT[2] Card Read Wait (CRW)       38         MMC_STAT[5] Data Time-Out Erro | 1 | MMC<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Overview<br>MMC/SD/SDIO Host Controller Features<br>MMC/SD Host Controller Signal Pads<br>MMC.CLK, SPI.CLK Signals ac Characteristics<br>MMC/SD/SDIO Modes—Interface Signal ac Characteristics<br>SPI Mode—Interface Signal ac Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17<br>18<br>20<br>21                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| MMC_STAT[0] End of Command (EOC) 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 | MMC                                    | MMC.CMD/SPI.DO[15] Data Direction (DDIR)<br>MMC.CMD/SPI.DO[14] Stream Command or Broadcast Host Response (SHR)<br>MMC.CMD/SPI.DO[13:12] Command Type (TYPE)<br>MMC.CMD/SPI.DO[11] Command With Busy Response (BUSY)<br>MMC.CMD/SPI.DO[7] Send Initialization Stream/Data Abort Command (INAB)<br>MMC.CMD/SPI.DO[6] Card Open Drain Mode/Extended Command Time-Out (ODTO)<br>MMC.CMD/SPI.DO[5:0] Command Index (INDX)<br>MMC_CON[15] Bus Width During Data Phase (DW)<br>MMC_CON[13:12] Mode Select (MODE)<br>MMC_CON[13:12] Mode Select (MODE)<br>MMC_CON[11] Power-Up Control (POW)<br>MMC_CON[10] Big Endian (BE)<br>MMC_CON[10] Big Endian (BE)<br>MMC_STAT[14] Card Status Error (CERR)<br>MMC_STAT[14] Card Status Error (CERR)<br>MMC_STAT[13] Card IRQ (CIRQ)<br>MMC_STAT[13] Card IRQ (CIRQ)<br>MMC_STAT[11] Buffer Almost Empty (AE)<br>MMC_STAT[10] Buffer Almost Full (AF)<br>MMC_STAT[10] Buffer Almost Full (AF)<br>MMC_STAT[10] Command CRC Error (CCRC)<br>MMC_STAT[17] Command Time-Out Error (CTO)<br>MMC_STAT[4] Card Exit Busy State (EOFB)<br>MMC_STAT[4] Card Exit Busy State (EOFB)<br>MMC_STAT[2] Card Enter Busy State (CB) | $\begin{array}{c} 24\\ 25\\ 26\\ 26\\ 27\\ 28\\ 29\\ 30\\ 31\\ 35\\ 36\\ 37\\ 38\\ 39\\ 39\\ 40\\ 41\\ 41\\ \end{array}$ |

| MMC_CTO[7:0] Command Time-Out Value (CTO)                            | 43 |

|----------------------------------------------------------------------|----|

| MMC_DTO[15:0] Data Time-Out Value (DTO)                              |    |

| MMC_DATA[15:0] Transmit/Receive FIFO Data Value (DATA)               | 45 |

| MMC_BLEN[10:0] Block Length (BLEN)                                   | 46 |

| MMC_NBLK[10:0] Number of Blocks (NBLK)                               | 47 |

| MMC_BUF[15] Receive DMA Channel Enable (RXDE)                        | 48 |

| MMC_BUF[12:8] Buffer Almost Full Level (AFL)                         | 49 |

| MMC_BUF[7] Transmit DMA Channel Enable (TXDE)                        | 49 |

| MMC_BUF[4:0] Buffer Almost Empty Level (AEL)                         |    |

| MMC_SPI[15] Start SPI Transfer (STR)                                 | 51 |

| MMC_SPI[14] Write /Not Read (WNR)                                    | 51 |

| MMC_SPI[13] Serial-Out Default Value (SODV)                          |    |

| MMC_SPI[12] SPI Transfer Controlled Start (CSTR)                     |    |

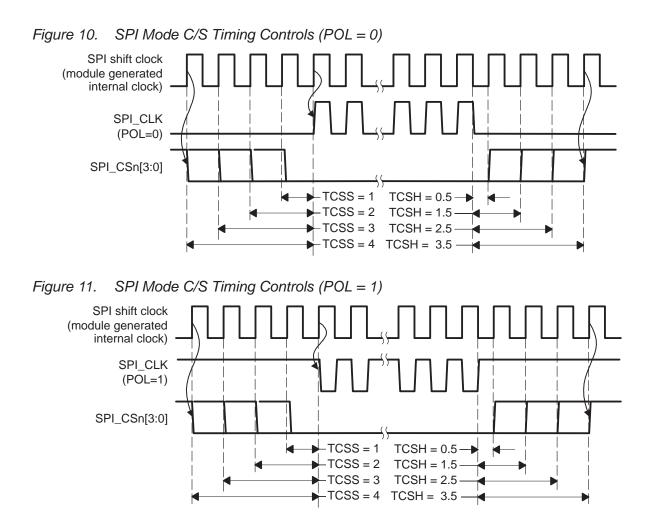

| MMC_SPI[11:10] Chip-Select Hold Time Control (TCSH)                  |    |

| MMC_SPI[9:8] Chip-Select Setup Time Control (TCSS)                   |    |

| MMC_SPI[7] Card Socket Connector Select (CSEL)                       |    |

| MMC_SPI[5:4] Chip-Select Control (CS)                                |    |

| MMC_SPI[3] Chip-Select Mode (CSM)                                    |    |

| MMC_SPI[2] Chip-Select Disable (CSD)                                 |    |

| MMC_SPI[1] Clock Phase (PHA)                                         |    |

| MMC_SPI[0] Clock Polarity (POL)                                      |    |

| MMC_SDIO[15] Card Status Error on R5 Enable (C5E)                    |    |

| MMC SDIO[14] Card Status Error on Bit 4 of Response R1 Enable (C14E) |    |

| MMC_SDIO[13] Card Status Error on Bit 3 of Response R1 Enable (C13E) |    |

| MMC_SDIO[12] Card Status Error on Bit 2 of Response R1 Enable (C12E) |    |

| MMC_SDIO[11] DAT3 Polarity Select (D3PS)                             |    |

| MMC_SDIO[10] DAT3 Polarity Select (D3ES)                             |    |

| MMC_SDIO[9] Card-Detect Wake-Request Enable (CDWE)                   |    |

| MMC_SDIO[8] Interrupt Wake Request Enable (IWE)                      |    |

| MMC_SDIO[7] Disable CRC7 Check on R4 Response (DCR4)                 |    |

| MMC_SDIO[6] Extended Data Time-Out Mode Select (XDTS)                |    |

| MMC_SDIO[5] Data Time-Out Prescaler Enable (DPE)                     |    |

| MMC_SDIO[4] Assert Read Wait Condition (RW)                          |    |

| MMC_SDIO[2] Card-Detect Enable (CDE)                                 |    |

| MMC_SDIO[1] SDIO Read Wait Mode Enable (RWE)                         |    |

| MMC_SDIO[0] SDIO Interrupt Mode Enable (IRQE)                        |    |

| MMC_SYST[15] WAKE_REQ Data (WAKD)                                    |    |

| MMC_SYST[14] Set Status Bits (SSB)                                   |    |

| MMC_SYST[13] Ready/Busy Data (RDYD)                                  |    |

| MMC_SYST[12] Direction (DDIR)                                        |    |

| MMC_SYST[11:8] Data (DnD)                                            |    |

| MMC_SYST[7] CMD Direction (CDIR)                                     |    |

| MMC_SYST[6] CMD Data (CDAT)                                          |    |

| MMC_SYST[5] MMC.CLK Data (MCKD)                                      | 63 |

|                                                                      |    |

10 *OMAP5912*

SPRU765A

|   |                                        | MMC_SYST[4] SPI.CLK Data (SCKD)         MMC_SYST[3:0] CSData (CSnD)         MMC_REV[7:0] Module Revision Number (REV)         MMC_IOSR[3] Stop Core Data Operation Request (STOP)         MMC_IOSR[2] Save FIFO Contents of Suspended Function (SAVE)         MMC_IOSR[1] Next SD Command Is a RESUME Request (RESU)         MMC_IOSR[0] Next SD Command Is a SUSPEND Request (SUSP)         MMC_SYSC[1] Software Reset (SRST)         MMC_SISS[0] Reset Done Status (RSTD) | 63<br>64<br>67<br>67<br>67<br>68 |

|---|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

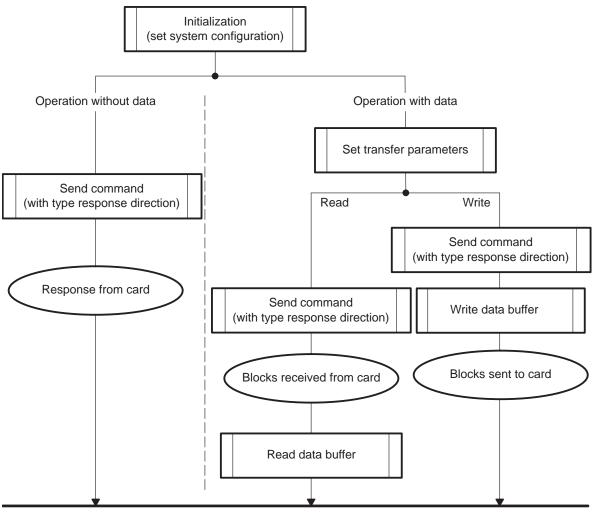

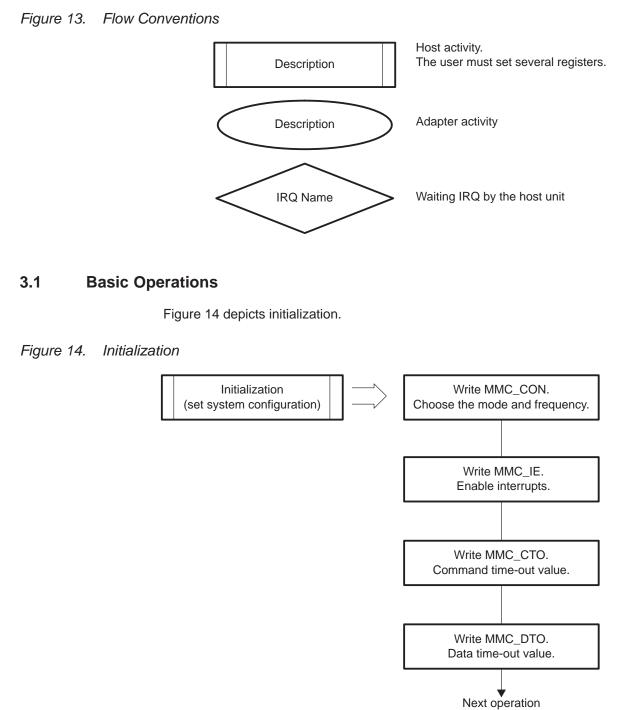

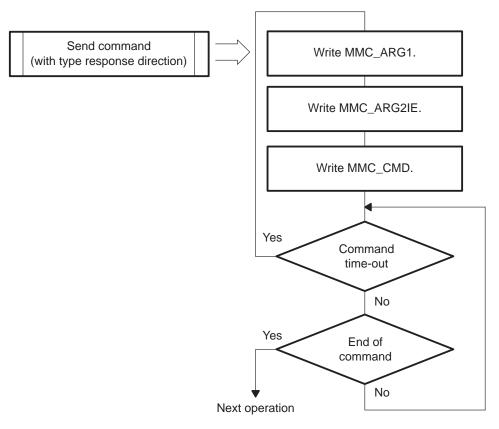

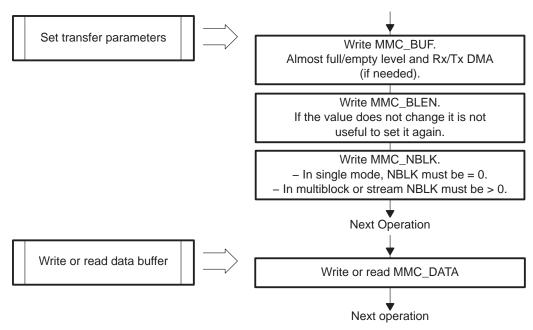

| 3 | <b>MMC</b><br>3.1<br>3.2<br>3.3        | Command Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>69</b><br>71<br>75            |

| 4 | <b>DMA</b><br>4.1<br>4.2<br>4.3<br>4.4 | Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77<br>79<br>81                   |

# Figures

| 1  | OMAP5912 MMC Area                          |  |

|----|--------------------------------------------|--|

| 2  | MMC/SD/SDIO System Overview                |  |

| 3  | MMC.CLK/SPI.CLK Signals ac Characteristics |  |

| 4  | MMC/SD/SDIO ac Characteristics             |  |

| 5  | SPI ac Characteristics                     |  |

| 6  | Clock Control                              |  |

| 7  | Little/Big Endian Mode FIFO Access         |  |

| 8  | Buffer Almost Full Level (AFL)             |  |

| 9  | Figure 1: Buffer Almost-Empty Level (AEL)  |  |

| 10 | SPI Mode C/S Timing Controls (POL = 0)     |  |

| 11 | SPI Mode C/S Timing Controls (POL = 1)     |  |

| 12 | General Command Flow                       |  |

| 13 | Flow Conventions                           |  |

| 14 | Initialization                             |  |

| 15 | Command Transfer                           |  |

| 16 | Data Transfer                              |  |

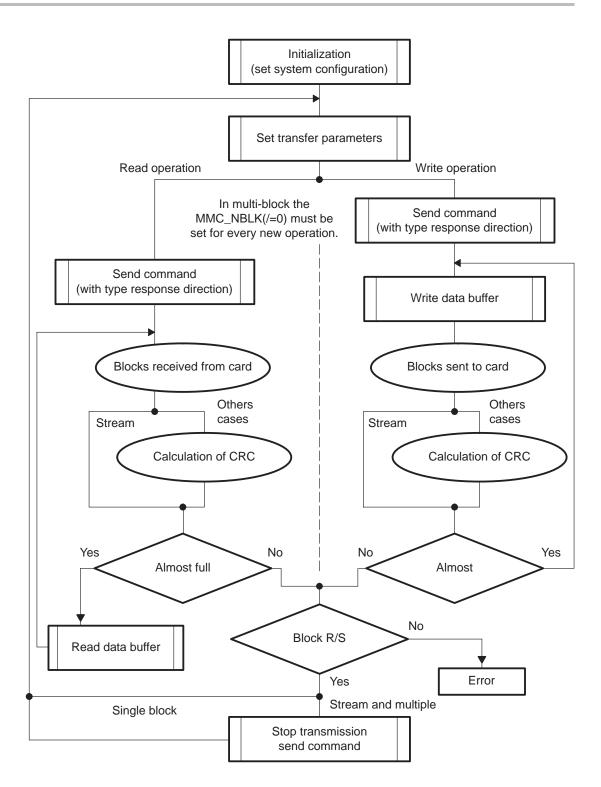

| 17 | Data Transfer in MMC/SD Mode               |  |

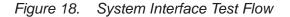

| 18 | System Interface Test Flow                 |  |

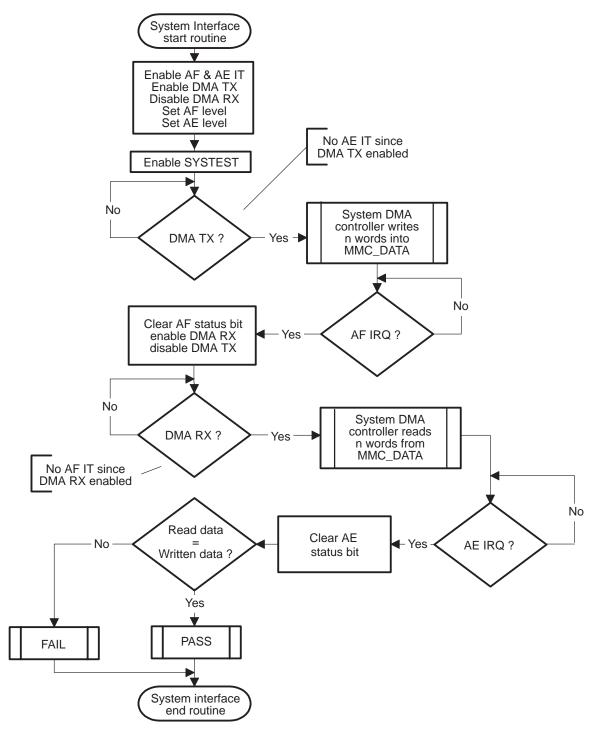

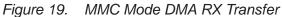

| 19 | MMC Mode DMA RX Transfer                   |  |

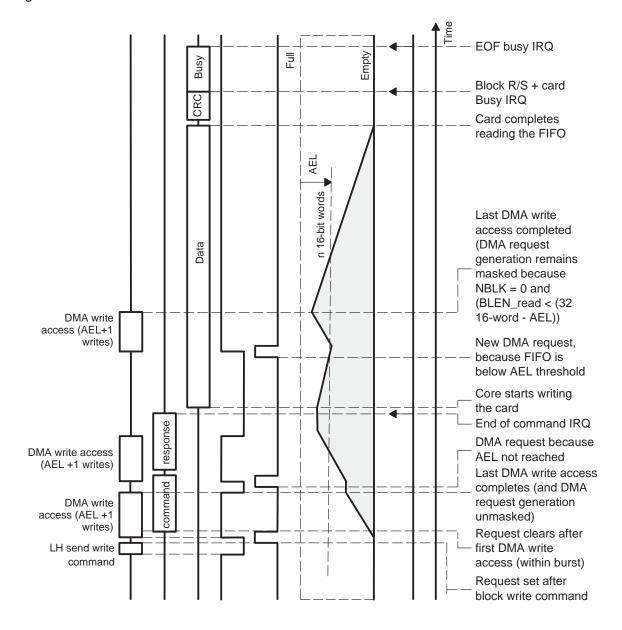

| 20 | MMC Mode DMA TX Transfer                   |  |

## **Tables**

| 1  | Signal Pads                                        |

|----|----------------------------------------------------|

| 2  | MMC.CLK/SPI.CLK Signals ac Parameters              |

| 3  | MMC/SD/SDIO ac Parameters                          |

| 4  | SPI ac Parameters                                  |

| 5  | MMC Registers                                      |

| 6  | MMC Command Register (MMC_CMD) 24                  |

| 7  | System Argument Low Register (MMC_ARGL)            |

| 8  | System Argument High Register (MMC_ARGH) 28        |

| 9  | Module Configuration Register (MMC_CON)            |

| 10 | MMC.CLK/SPI.CLK High/Low Time Computation          |

| 11 | Module Status Register (MMC_STAT)                  |

| 12 | Card Status Error (CERR)                           |

| 13 | System Interrupt Enable Register (MMC_IE) 42       |

| 14 | Command Time-Out Register(MMC_CTO) 43              |

| 15 | Data Read Time-Out Register (MMC_DTO) 43           |

| 16 | Clock Cycles for Time-out Value 44                 |

| 17 | Data Access Register (MMC_DATA) 44                 |

| 18 | Block Length Register (MMC_BLEN) 46                |

| 19 | Number of Blocks Register (MMC_NBLK) 47            |

| 20 | Buffer Configuration Register (MMC_BUF) 48         |

| 21 | SPI Configuration Register (MMC_SPI) 50            |

| 22 | Chip-Select Control (SPI Mode) 55                  |

| 23 | SDIO Mode Configuration Register (MMC_SDIO) 56     |

| 24 | System Test Register (MMC_SYST) 61                 |

| 25 | Module Revision Register (MMC_REV) 63              |

| 26 | MMC/SD Command Response Register 0 (MMC_RSP0) 64   |

| 27 | MMC/SD Command Response Register 1 (MMC_RSP1) 64   |

| 28 | MMC/SD Command Response Register 2 (MMC_RSP2) 64   |

| 29 | MMC/SD Command Response Register 3 (MMC_RSP3) 65   |

| 30 | MMC/SD Command Response Register 4 (MMC_RSP4) 65   |

| 31 | MMC/SD Command Response Register 5 (MMC_RSP5) 65   |

| 32 | MMC/SD Command Response Register 6 (MMC_RSP6) 65   |

| 33 | MMC/SD Command Response Register 7 (MMC_RSP7) 66   |

| 34 | SDIO Suspend/Resume Control Register (MMC_IOSR) 66 |

| 35 | System Control Register(1.1MMC_SYSC) 68            |

| 36 | System Status Register(MMC_SYSS) 68                |

| 37 | Programming Aid for CMD Register (MMC_CMD) 82      |

SPRU765A

*OMAP5912* 13

## **Notes**

| ites               | 4 |

|--------------------|---|

| ive Transfer Phase |   |

| ive Transfer Phase | 9 |

| IA TX Request      | 7 |

| IA RX Request      | 7 |

| mmand Time-Out     |   |

| ta Time-Out        |   |

| ad/Write Access    |   |

| ue Requirement     |   |

| ck Size            |   |

| ck Size            | 9 |

## Multimedia Card (MMC/SD/SDIO) Interface

This document describes the multimedia card (MMC) interface of the OMAP5912 multimedia processor.

#### 1 MMC Overview

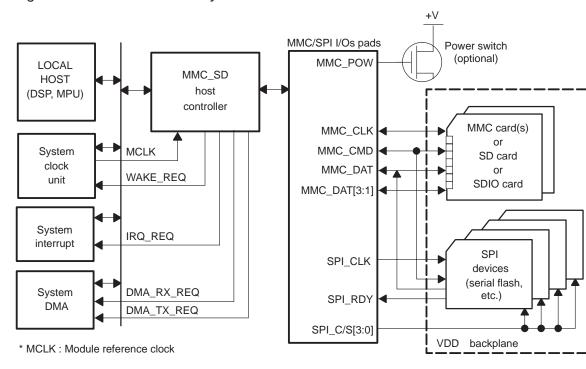

The multimedia card/secure data/secure digital IO (MMC/SD/SDIO) host controller provides an interface between a local host, such as a microprocessor unit (MPU) or digital signal processor (DSP), and either an MMC or SD memory card, plus up to four serial flash cards. The host controller handles MMC/SD/SDIO or serial port interface (SPI) transactions with minimal local host intervention. Figure 2 provides an overview of the system.

The host controller supports the following combination of external devices:

- One or more MMC memory cards sharing the same bus, plus up to four devices with 8-bit SPI protocol interface (serial flash memories)

- One SD memory card or SDIO card, plus up to four devices with 8-bit SPI protocol interface

Other combinations, such as two SD cards or one MMC card plus one SD card, are not supported through a single controller.

The application interface manages transaction semantics. The MMC/SD/SDIO host controller handles the MMC/SD protocol at the transmission level, including data packing, adding the cyclic redundancy check (CRC) and start/end bits, and checking for syntactical correctness. It also supports SD mode wide-bus width.

The application interface can send every MMC/SD/SDIO command and either poll for the status of the adapter, wait for an interrupt request, which is sent back in case of exceptions, or warn of the end of the operation. The application interface reads card responses and flag registers, and masks interrupt sources individually. These operations are performed by reading and writing control registers. The MMC/SD/SDIO module also supports two direct memory access (DMA) channels.

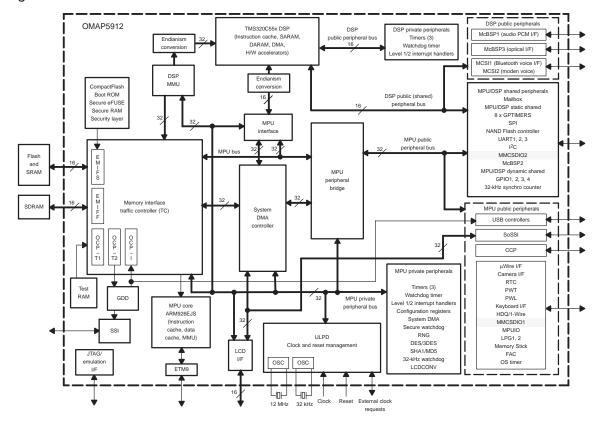

Figure 1 shows the OMAP5912 processor with the MMC area highlighted.

### Figure 1. OMAP5912 MMC Area

#### Figure 2. MMC/SD/SDIO System Overview

## 1.1 MMC/SD/SDIO Host Controller Features

The main features of the controller are:

- Full compliance with MMC command/response sets as defined in *The Multimedia Card-System Specification*, MMCA Technical Committee, Version 3.1, June 2001

- Full compliance with SD command/response sets as defined in SD Memory Card Specification-Part 1, Physical Layer Specification, SD Group, Version 1.0, March 2000, and Supplementary Notes-Part 1, Physical Layer Specification, SD Group, June 2000

- Full compliance with SDIO command/response sets and interrupt/read-wait mode as defined in SDIO Card Specification Part E1, SDIO Working Group, Version 1.0, October 2001

- Flexible architecture that allows support for new command structure

- Separate SPI interface with four CS. Provides support for up to four serial flash devices

- Built-in 64-byte FIFO for buffered read or write

- 16-bit-wide access bus to maximize bus throughput

- Low-power design

- U Wide interrupt capability

- Programmable clock generation

- Two DMA channels

- Big- /little-endian mode for data

Known limitations:

□ No built-in hardware support for error correction codes (ECC)

## 1.2 MMC/SD Host Controller Signal Pads

The signal pads listed in Table 1 describe the physical interface between the driving IC (the transceiver) and the target MMC/SD memory cards, SDIO device, or serial flash memories.

The transceiver provides a dc-level adaptation function between the controller core and the target devices. It can be integrated either on-chip with the controller or implemented off-chip (system-dependent issue).

| Name                                | Туре   | Pull-Up | Reset<br>Value | Description                                                                                                                                                     |

|-------------------------------------|--------|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MMC.CLK                             | Out    | _       | 0              | MMC/SD/SDIO card CLK signal.<br>Only active during active command to MMC/SD/SDIO<br>card using MMC or SPI protocols.                                            |

| MMC.CMD/SPI.<br>DO<br>(SPI_SO)      | In/out | Yes     | Input          | MMC/SD card CMD signal in MMC/SD mode.<br>SPI serial out signal in SPI modes (output—goes to serial<br>in of target device(s)).                                 |

| MMC.DAT0<br>(SPI_SI)                | In/out | Yes     | Input          | MMC card DAT signal or SD/SDIO card DAT[0] signal in<br>MMC/SD mode.<br>SPI serial in signal in SPI modes (input—comes from<br>serial out of target device(s)). |

| MMC.DAT1<br>(SDIO_IRQ) <sup>†</sup> | In/out | Yes     | Input          | SD/SDIO card DAT[1] signal.<br>Interrupt (IRQ) for SDIO card (SD and SPI protocol).                                                                             |

| MMC.DAT2<br>(SDIO_RW) <sup>†</sup>  | In/out | Yes     | Input          | SD/SDIO card DAT[2] signal.<br>Read wait (RW) for SDIO card.                                                                                                    |

| MMC.DAT3<br>(MMC_CS,<br>SD_CD)¶     | In/out | Yes     | Input          | SD/SDIO card DAT[3] signal.<br>Chip-select (CS) for MMC/SD/SDIO cards using SPI<br>protocol.<br>Chip detect (CD) for SD/SDIO cards.                             |

| SPI.CLK‡                            | Out    | _       | 0              | SPI CLK signal.<br>Only active in SPI mode during active SPI transfers,<br>except when MMC_CLK is selected.                                                     |

| SPI_C/Sn[3:0]‡                      | Out    | -       | b1111          | Four SPI chip-select signals. Active low.<br>Only active in SPI mode during active SPI transfers                                                                |

| SPI.RDY‡                            | In     | Yes     | Input          | SPI ready/busy signal.<br>When low, denotes a busy condition. Only active in SPI<br>mode during active SPI transfers.                                           |

| MMC_POW§                            | Out    | -       | 0              | MMC/SD cards on/off power supply control.<br>When high, denotes power-on condition.                                                                             |

Signal Pads Table 1.

† Optional signals. Only needed for SD/SDIO cards.

‡ Optional signals. Only needed for devices with SPI interfaces (serial flash, additional MMC, SD, or SDIO cards).

§ Optional signal. Only needed if power supply (VDD) of cards or other SPI devices are to be switched on and off in the application.

¶ Optional signals. Only needed for SD/SDIO cards or for MMC card operated in SPI mode.

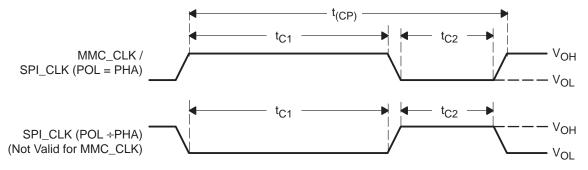

### 1.3 MMC.CLK, SPI.CLK Signals ac Characteristics

The core internally gates the MMC or SPI clock signals to be active only during a valid transaction to the selected target device (memory cards or serial flash). The duty cycle of the clock depends on the clock division factor and the polarity setting.

| Table 2. | MMC.CLK/SPI.CLK Signals ac Parameters |

|----------|---------------------------------------|

|          |                                       |

| Parameter       | Description                                                            | Min | Max | Unit |

|-----------------|------------------------------------------------------------------------|-----|-----|------|

| t <sub>CP</sub> | Clock period                                                           | 40  | _   | ns   |

| t <sub>C1</sub> | MMC mode: Clock high time                                              | -   | _   | ns   |

|                 | SPI mode: Clock high time (POL = PHA), clock low time (POL $\neq$ PHA) |     |     |      |

| t <sub>C2</sub> | MMC mode: Clock low time                                               | -   | _   | ns   |

|                 | SPI mode: Clock low time (POL = PHA), clock high time (POL $\neq$ PHA) |     |     |      |

The clock period and the high and low times specified in Table 2, as well as all timings in subsequent pages, are controller capabilities.

The real clock period must be computed as a function of the system reference clock and adjusted to the target device used in the application. All derived timings must be checked against selected target device specifications.

For example:

- MMC card: max 20 MHz (min 50 ns)

- SD card: max 25 MHz (min 40 ns)

- SPI serial flash: max 13 MHz (min 77 ns)

## 1.4 MMC/SD/SDIO Modes—Interface Signal ac Characteristics

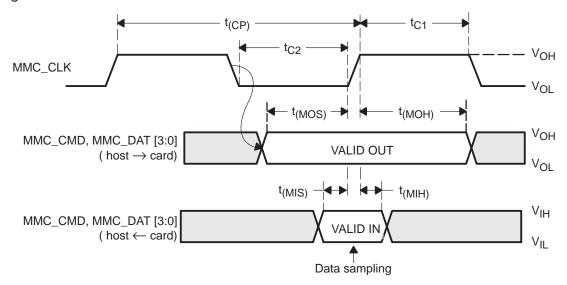

Figure 4 depicts the ac characteristics of the interface signals when the interface is configured for MMC/SD/SDIO operation.

SPI-specific output signals (SPI\_C/Sn[3:0], SPI.CLK) are held to their inactive state, and SPI-specific input signals are don't care (SPI.RDY).

Figure 4. MMC/SD/SDIO ac Characteristics

Data is sampled on the rising edge of the clock.

| Table 3. | MMC/SD/SDIO | ac Parameters |

|----------|-------------|---------------|

|          |             |               |

| Parameter        | Description                               | Min                | Max | Unit |

|------------------|-------------------------------------------|--------------------|-----|------|

| t <sub>MOS</sub> | Data output setup to rising edge of clock | t <sub>C2</sub> -5 | -   | ns   |

| <sup>t</sup> MOH | Data output hold to rising edge of clock  | t <sub>C1</sub> –5 | -   | ns   |

| t <sub>MIS</sub> | Data input setup to rising edge of clock  | 4                  | -   | ns   |

| t <sub>MIH</sub> | Data input hold to rising edge of clock   | 4                  | -   | ns   |

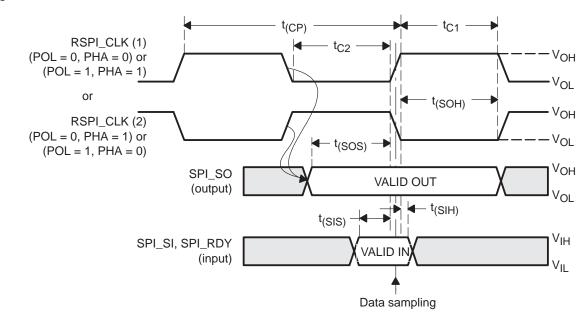

## 1.5 SPI Mode—Interface Signal ac Characteristics

Figure 5 depicts the ac characteristics of the interface signals when the interface is configured for SPI operation.

MMC-specific input/output signals (MMC.DAT3) are held to their inactive state.

SPRU765A

The SPI interface is master only.

Figure 5. SPI ac Characteristics

Data is sampled on the rising or falling edge of the clock, depending on the polarity/phase setting. See Table 4.

| Parameter        | Description                                                                 | Min                | Мах | Unit |

|------------------|-----------------------------------------------------------------------------|--------------------|-----|------|

| tsos             | Data output set up to rising edge of clock (1) or falling edge of clock (2) | t <sub>C2</sub> -5 | -   | ns   |

| t <sub>SOH</sub> | Data output hold to rising edge of clock (1) or falling edge of clock (2)   | t <sub>C1</sub> -5 | -   | ns   |

| t <sub>SIS</sub> | Data input set up to rising edge of clock (1) or falling edge of clock (2)  | 16                 | -   | ns   |

| t <sub>SIH</sub> | Data input hold to rising edge of clock (1) or falling edge of clock (2)    | 0                  | -   | ns   |

## 2 MMC Registers

Table 5 lists the MMC registers. Table 6 through Table 36 describe the registers bits.

| Base Address = FFFB 7800 and 0xFFFB 7C00 |                                 |     |         |

|------------------------------------------|---------------------------------|-----|---------|

| Register                                 | Description                     | R/W | Offset  |

| MMC.CMD/SPI.DO                           | MMC command                     |     | 0x00    |

| MMC_ARGL                                 | MMC argument low                |     | 0x04    |

| MMC_ARGH                                 | MMC argument high               |     | 0x08    |

| MMC_CON                                  | MMC module configuration        |     | 0x0C    |

| MMC_STAT                                 | MMC module status               |     | 0x10    |

| MMC_IE                                   | MMC system interrupt enable     |     | 0x14    |

| MMC_CTO                                  | MMC command time-out            |     | 0x18    |

| MMC_DTO                                  | MMC data read time-out          |     | 0x1C    |

| MMC_DATA                                 | MMC data access                 |     | 0x20    |

| MMC_BLEN                                 | MMC block length                |     | 0x24    |

| MMC_NBLK                                 | MMC number of blocks            |     | 0x28    |

| MMC_BUF                                  | MMC buffer configuration        |     | 0x2C    |

| MMC_SPI                                  | MMC SPI configuration           |     | 0x30    |

| MMC_SDIO                                 | MMC SDIO mode configuration     |     | 0x34    |

| MMC_SYST                                 | MMC system test                 |     | 0x38    |

| MMC_REV                                  | MMC module revision             |     | 0x3C    |

| MMC_RSP0                                 | MMC/SD command response 0       |     | 0x40    |

| MMC_RSP1                                 | MMC/SD command response 1       |     | 0x44    |

| MMC_RSP2                                 | MMC/SD command response 2       |     | 0x48    |

| MMC_RSP3                                 | MMC/SD command response 3       |     | 0x4C    |

| MMC_RSP4                                 | MMC/SD command response 4       |     | 0x50    |

| MMC_RSP5                                 | MMC/SD command response 5       |     | 0x54    |

| MMC_RSP6                                 | MMC/SD command response 6       |     | 0x58    |

| MMC_RSP7                                 | MMC/SD command response 7       |     | 0x5C    |

| MMC_IOSR                                 | MMC SDIO suspend/resume control |     | 0x60    |

| MMC_SYSC                                 | MMC system control              |     | 0x64    |

| MMC_SYSS                                 | MMC system status               |     | 0x68    |

| Reserved                                 | Reserved                        |     | 0x6C-7C |

Table 5. MMC Registers

SPRU765A

| Table 6. | MMC Command R | Register ( | MMC_ | CMD | ) |

|----------|---------------|------------|------|-----|---|

|----------|---------------|------------|------|-----|---|

|       | Base Address = 0xFFFB 7800 and 0xFFFB 7C00, Offset Address = 0x00 |                                                                       |  |  |  |

|-------|-------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Bit   | Name                                                              | Description                                                           |  |  |  |

| 15    | DDIR                                                              | Data direction [write, read]                                          |  |  |  |

| 14    | SHR                                                               | Stream command or broadcast host response [normal, stream/host]       |  |  |  |

| 13:12 | TYPE                                                              | Command type [bc, bcr, ac, adtc]                                      |  |  |  |

| 11    | BUSY                                                              | Command with busy response                                            |  |  |  |

| 10:8  | RSP                                                               | Command responses [no response, R1/R1b, R2, R3, R4, R5, R6, reserved] |  |  |  |

| 7     | INAB                                                              | Send initialization stream/data abort command                         |  |  |  |

| 6     | ODTO                                                              | Card open drain mode/extended command time-out mode                   |  |  |  |

| 5:0   | INDX                                                              | Command index [CMD0, …, CMD63]                                        |  |  |  |

A write to this register sends a command to the card.

If the local host accesses this register byte-wise, the card receives the command only after a write access to the least significant (LS) byte (bits 7:0). Therefore, the most significant (MS) byte must always be written first in a byte-accessed situation.

A read has no effect except to return the last command that was sent.

#### Note: Writes

A write into this register with MMC\_CMD[TYPE] = adtc resets the FIFO. Writes with other type of values (bc, bcr, ac) do not affect the FIFO contents. Hence, data must be written into the FIFO after sending a single or multiple block-write command.

#### MMC.CMD/SPI.DO[15] Data Direction (DDIR)

This bit specifies whether the data transfer is a read or a write, and is valid only if the command type is adtc.

This bit has the same polarity as the RD/WR argument bit 0 for a GEN\_CMD command (CMD56):

- 0: Data write

- 1: Data read

Value after reset is low.

Multimedia Card (MMC/SD/SDIO) Interface

SPRU765A

### MMC.CMD/SPI.DO[14] Stream Command or Broadcast Host Response (SHR)

MMC card only.

The SD card does not support stream operation or host-generated response. This bit must be set to 1 in two cases:

- Associated with adtc command type, if the command is a stream data transfer (read or write). Stream read is a class 1 command (CMD11: READ\_DAT\_UNTIL\_STOP). Stream write is a class 3 command (CMD20: WRITE\_DAT\_UNTIL\_STOP).

- Associated with a bc command type, the host generates a 48-bit response instead of a command. It can be used to terminate the interrupt mode by generating a CMD40 response by the core (see Section 4.3, *Interrupt Mode* in *The Multimedia Card-System Specification*). In order for the host response to be generated in open drain mode, MMC\_CMD[ODTO] must be set to 1.

This bit is valid only if the command type is adtc or bc:

- 0: Normal mode

- 1: Stream mode (MMC\_CMD[TYPE] = adtc), host response (MMC\_CMD[TYPE] = bc)

Value after reset is low.

### MMC.CMD/SPI.DO[13:12] Command Type (TYPE)

Encoded bits that define the type of command passed by the core to the MMC/SD memory card (see Section 4.7.1, *Command Types, The Multimedia Card–System Specification,* or *SD Memory Card Specification–Part 1 Physical*

Layer Specification and Supplementary Notes–Part 1 Physical Layer Specification).

- 00: Broadcast commands (bc), no response

- 01: Broadcast commands with response (bcr)

- 10: Addressed commands (ac), no data transfer

- 11: Addressed data transfer commands (adtc) and reset of the FIFO

Value after reset is low (both bits).

SPRU765A

Multimedia Card (MMC/SD/SDIO) Interface

25

### MMC.CMD/SPI.DO[11] Command With Busy Response (BUSY)

This bit must be set to 1 if the response to the command sent is type R1b (R1 + busy):

- □ 0: Response without busy (R1, R2, R3, R4, R5, R6)

- 1: Response with busy (R1b)

Value after reset is low.

#### MMC.CMD/SPI.DO[10:8] Command Response (RSP)

Encoded bits that define the response for the command that the core passes to the MMC/SD memory card (see Section 4.9, *Responses* in *The Multimedia Card-System Specification*, or *SD Memory Card Specifications–Part 1 Physical Layer Specification* and *Supplementary Notes–Part 1 Physical Layer Specification*).

- 000: No response

- □ 001: R1/R1b (normal response command)

- 010: R2 (CID, CSD registers)

- O11: R3 (OCR register)

- □ 100: R4 (fast I/O—MMC card only)

- 101: R5 (interrupt request—MMC card only/IO\_RW\_DIRECT—SDIO card only)

- □ 110: R6 (published RCA response—SD card only)

- 111: Reserved

Value after reset is low (3 bits).

#### MMC.CMD/SPI.DO[7] Send Initialization Stream/Data Abort Command (INAB)

This bit must only be set in two particular cases:

When the card is idle, to send an initialization sequence. This option simplifies the acquisition of new cards. An initialization sequence consists of setting the CMD line to 1 during 80 clock cycles (see Section 6.3, *Power-Up* in *The Multimedia Card-System Specification*, or Section 6.4, *SD Memory Card Specifications–Part 1 Physical Layer Specification* and

Multimedia Card (MMC/SD/SDIO) Interface

26

Supplementary Notes–Part 1 Physical Layer Specification SD Memory Card Specifications–Part 1 Physical Layer Specification and Supplementary Notes–Part 1 Physical Layer Specification). In this mode, no command is sent to the card and no response is expected.

- When the card is in the data transfer stage, to stop or abort an ongoing data transfer. The card is said to be in such state when the previous command was of type adtc and has not yet completed (MMC\_STAT[BRS] = 0). A stop or aborted data command:

- Freezes the MMC\_BLEN[BLEN] and MMC\_NBLK[NBLK] values according to the last valid byte written to or read from the card

- Sets the MMC\_STAT[BRS] status bit as follows:

- 0: No action

- 1: Initialization (80 clock cycles)/data abort command

Value after reset is low.

#### MMC.CMD/SPI.DO[6] Card Open Drain Mode/Extended Command Time-Out (ODTO)

This bit has a dual function, depending upon the value set in the MMC\_SDIO[XDTS] bit.

□ Open drain control function (MMC\_SDIO[XDTS] = 0—MMC card only

This bit must be set to 1 if the MMC card bus is operating in open-drain mode during the response phase to the command sent. Typically, it occurs during card identification mode when the card is in idle, ready, or ident state. It is also necessary to set this bit to 1 for a broadcast host response (see MMC.CMD[SHR]). This bit must be set for MMC card commands 1, 2, 3, and 40.

For the SD card, this bit must always be kept low because SD cards do not have open drain capability.

- 0: Push-pull

- 1: Open drain

- Extended command time-out function (MMC\_SDIO[XDTS] = 1)—SDIO card only.

SPRU765A

This bit must be set to 1 if the SDIO command response requires a long time-out (typically an IO\_RW\_DIRECT CMD52). When set, the command time-out is set to the data time-out value (see MMC\_DTO[DTO]). When clear, the normal command time-out applies (see MMC\_CTO[CTO]).

- O: Command time-out equals CTO

- 1: Command time-out equals DTO

Value after reset is low.

#### MMC.CMD/SPI.DO[5:0] Command Index (INDX)

Binary encoded value from 0 to 63 specifying the command number sent to the card.

- 000000: CMD0

- 000001: CMD1

•••

1111111: CMD63

Value after reset is low (all 6 bits).

#### Table 7. System Argument Low Register (MMC\_ARGL)

| Base Address = 0xFFFB 7800 and 0xFFFB 7C00, Offset Address = 0x04 |      |                                         |  |

|-------------------------------------------------------------------|------|-----------------------------------------|--|

| Bit Name Description                                              |      |                                         |  |

| 15:0                                                              | ARGL | Command argument bits [15:0]            |  |

|                                                                   |      | Value after reset is low (all 16 bits). |  |

#### Table 8. System Argument High Register (MMC\_ARGH)

| Base Address = 0xFFFB 7800 and 0xFFFB 7C00, Offset Address = 0x08 |      |                               |  |  |

|-------------------------------------------------------------------|------|-------------------------------|--|--|

| Bit                                                               | Name | Description                   |  |  |

| 15:0                                                              | ARGH | Command argument bits [31:16] |  |  |

Value after reset is low (all 16 bits).

Table 9 lists the module configuration characteristics.

These two 16-bit registers (Table 7 and Table 8) specify the 32-bit argument value that is passed with the command. These registers must be initialized before sending the command to the card (write action into the MMC\_CMD register). The only exception making a write unnecessary is a command index specifying stuff bits in arguments.

This section describes the module configuration register.

#### Table 9. Module Configuration Register (MMC\_CON)

|       | Base Address = 0xFFFB 7800 and 0xFFFB 7C00, Offset Address = 0x0C |                                              |  |  |  |  |

|-------|-------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

| Bit   | Name                                                              | Description                                  |  |  |  |  |

| 15    | DW                                                                | Data bus width                               |  |  |  |  |

| 14    | -                                                                 | Reserved                                     |  |  |  |  |

| 13:12 | MODE                                                              | Operating mode select [MMC/SD, SPI, SYSTEST] |  |  |  |  |

| 11    | POWER_UP                                                          | Power-up control                             |  |  |  |  |

| 10    | BE                                                                | Big-endian mode [little, big]                |  |  |  |  |

| 9:0   | CLKD                                                              | Clock divider [disabled, 1:1023]             |  |  |  |  |

#### Note: Active Transfer Phase

This register must never be written during an active transfer phase. Changing it may result in unpredictable behavior.

#### MMC\_CON[15] Bus Width During Data Phase (DW)

#### SD mode only.

This bit must be set following a valid SET\_BUS\_WIDTH command (ACMD6) with the value written in bit 1 of the argument. Prior to this command, the SD card configuration register (SCR) must be verified for the bus width supported by the SD card.

- □ 0: 1-bit data width (DAT[0] used)

- 1: 4-bit data width (DAT[3:0] used, SD card only)

Value after reset is low.

This bit must always be set to 0 for MMC cards or during SPI transfer. Failing to set this bit correctly results in unpredictable behavior.

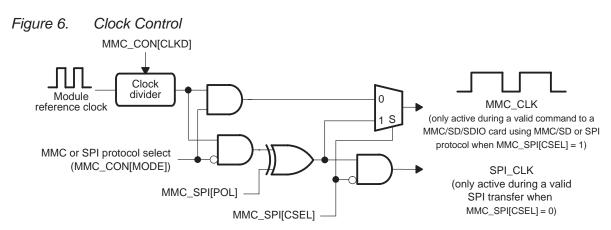

#### MMC\_CON[13:12] Mode Select (MODE)

These two bits select among MMC/SD, SPI, and SYSTEST modes.

In MMC/SD mode, transfers to the MMC/SD/SDIO card follow the MMC protocol. The MMC clock is enabled and the SPI clock is disabled. MMC/SD transfers are operated under the control of the MMC.CMD register.

29

- In SPI mode, transfers to as many as four SPI controlled devices (serial flash, MMC/SD/SDIO cards) are supported. SPI transfers are operated under the control of the MMC SPI register.

- □ In SYSTEST mode, the signal pins are configured as general-purpose input/output, and the 64-byte FIFO is configured as a stack memory accessible only by the local host or system DMA. The pins retain their default type (input, output, or in-out). The YSTEST mode is operated under the control of the MMC SYST register.

- 00: MMC/SD mode (MMC/SD/SDIO cards using MMC/SD protocol)

- 01: SPI mode (for serial flash or others SPI slave devices)

- 10: SYSTEST mode

- 11: Reserved

Value after reset is low (both bits).

#### MMC\_CON[11] Power-Up Control (POW)

This bit must be set to 1 before any valid transaction to either MMC/SD or SPI memory cards.

When 1, the card is considered powered-up and the controller core is enabled.

When 0, the card is considered powered-down (system dependent), and the controller core logic is in pseudo-reset state. This is, the MMC STAT flags and the FIFO pointers are reset, any access to MMC\_DATA[DATA] has no effect, a write into the MMC.CMD register is ignored, and a setting of MMC SPI[STR] to 1 is ignored.

This bit directly controls the MMC\_POW signal (if implemented as device pin).

- O: Powered-down/pseudo-reset state.

- 1: Powered-up/normal operation mode.

Value after reset is low.

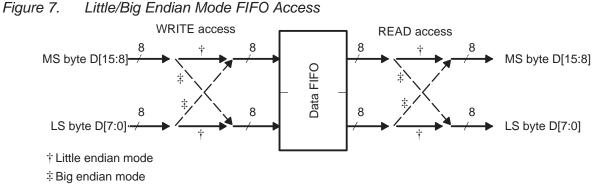

#### MMC\_CON[10] Big Endian (BE)

When this bit is 0 (default), the FIFO is accessed in little endian format. In transmit mode, the LS byte (MMC DATA[7:0]) is transmitted first, and the MS byte (MMC DATA[15:8]) is transmitted to the card in second position. Conversely, in receive mode, the first or odd byte received (1, 3, 5, ...) is stored in the LS byte position, and the second or even byte received is stored in the MS byte position.

When the LH sets this bit to a 1, the FIFO is accessed in big endian format. In transmit mode, the MS byte (MMC\_DATA[15:8]) is transmitted first and the LS byte (MMC\_DATA[7:0]) is transmitted to the card in second position. Conversely, in receive mode, the first or odd byte received (1, 3, 5, ...) is stored in the MS byte position, and the second or even byte received is stored in the LS byte position.

- O: Little-endian mode

- 1: Big-endian mode

Value after reset is low.

### MMC\_CON[9:0] Clock Divider (CLKD)

These bits define the ratio between a reference clock frequency (system dependent) and the output clock frequency on the CLK pin of either the memory card (MMC or SD) or other 8-bit mode SPI-controlled device.

The division factor is equal to the binary encoded decimal value for values between 1 and 1023. A value of 0 disables the clock.

- Ox00: Clock disabled

- Ox01: Ref clock/1

....

□ 0x3FF: Ref clock/1023

Value after reset is low (all 10 bits).

- Notes: 1) During the identification phase, the maximum frequency on the MMC CLK line is 400 kHz (see Section 6.7, Bus Timing in The Multimedia Card-System Specification, or Section 6.8, SD Memory Card Specifications–Part 1, Physical Layer Specification or Supplementary Notes–Part 1, Physical Layer Specification). A value of 50 must be set into the frequency ratio register if the reference clock frequency to the MMC/SD host controller is 20 MHz.

- 2) During the data transfer phase, the maximum frequency is 20 MHz for MMC card and 25 MHz for SD cards.

- 3) The duty cycle of the generated MMC.CLK and SPI.CLK signals depends on the clock divider value (MMC\_CON[CLKD]) and on the polarity setting (MMC\_SPI[POL]) in SPI mode only. The low and high times approximate values can be computed using rules set in Table 10.

- 4) In MMC/SD mode, the idle value of MMC.CLK signal is low. In SPI mode, the idle value of either the MMC.CLK (MMC\_SPI[CSEL] = 1) or the SPI.CLK (MMC\_SPI[CSEL] = 0) is a function of the polarity setting (low if MMC\_SPI[POL] = 0, high if MMC\_SPI[POL] = 1).

| MMC_CON[CLKD]                                | MMC.CLK/SPI.CLK High Time       | MMC.CLK/SPI.CLK Low Time        |

|----------------------------------------------|---------------------------------|---------------------------------|

| 1                                            | REF_CLK_HIGH_TIME               | REF_CLK_LOW_TIME                |

| Even $\geq 2$                                | REF_CLK_PER (CLKD/2)            | REF_CLK_PER (CLKD/2)            |

| $Odd \ge 3 (POL = PHA)$                      | REF_CLK_PER (TRUNC[CLKD/2] + 1) | REF_CLK_PER (TRUNC[CLKD/2])     |

| $Odd \geq 3 \; (\text{POL} \neq \text{PHA})$ | REF_CLK_PER (TRUNC[CLKD/2])     | REF_CLK_PER (TRUNC[CLKD/2] + 1) |

#### Notes:

- 1) REF\_CLK\_PER is the reference clock period (in ns) to the module (end-system dependent).

- 2) TRUNC is the truncate function to an integer number (round down).

#### Example 1:

Module reference clock = 48 MHz (20.83 ns); target is the MMC card.

- 1) a) (MMC\_CON[CLKD] = 3 (because the MMC card is 20 MHz max)

- 2) b) MMC\_CLK period = 62.5 ns (> 50 ns OK)

- 3) c) Ideal MMC\_CLK high time = 41.66 ns (>>10 ns OK)

- 4) d) Ideal MMC\_CLK low time = 20.83 ns (>>10 ns OK)

#### Example 2:

Module reference clock = 60 MHz (16.67 ns); target is the 13-MHz serial flash requiring polarity 1 programming.

- 1) a) (MMC\_CON[CLKD] = 5 (because 13-MHz serial flash)

- 2) b) SPI\_CLK period = 83.33 ns (> 77 ns OK)

- 3) c) Ideal SPI\_CLK high time = 33.3 ns (<35 ns FAIL, use (MMC\_CON[CLKD] = 6)

- 4) d) Ideal SPI\_CLK low time = 50 ns (>>35 ns OK)

- 5) e) (MMC\_CON[CLKD] = 6 (because clock high time min 35 ns)

- 6) f) SPI\_CLK period = 100 ns (> 77 ns OK)

- 7) g) Ideal SPI\_CLK high time = 50 ns (>>35 ns OK)

- 8) h) Ideal SPI\_CLK low time = 50 ns (>>35 ns OK)

| Base Address = 0xFFFB 7800 and 0xFFFB 7C00, Offset Address = 0x10 |      |                                                                    |  |  |

|-------------------------------------------------------------------|------|--------------------------------------------------------------------|--|--|

| Bit                                                               | Name | Description                                                        |  |  |

| 15                                                                | -    | Reserved                                                           |  |  |

| 14                                                                | CERR | Card status error in response                                      |  |  |

| 13                                                                | CIRQ | MMC card IRQ received (following CMD40) or SDIO card interrupt     |  |  |

| 12                                                                | OCRB | Operation condition register (OCR) busy (following CMD1 or ACMD41) |  |  |

| 11                                                                | AE   | Buffer almost empty                                                |  |  |

| 10                                                                | AF   | Buffer almost full                                                 |  |  |

| 9                                                                 | CRW  | Card read wait                                                     |  |  |

| 8                                                                 | CCRC | Command CRC error                                                  |  |  |

| 7                                                                 | СТО  | Command response time-out (no response)                            |  |  |

| 6                                                                 | DCRC | Data CRC error                                                     |  |  |

| 5                                                                 | DTO  | Data response time-out (no response)                               |  |  |

| 4                                                                 | EOFB | Card exit busy state                                               |  |  |

| 3                                                                 | BRS  | Block received/sent                                                |  |  |

| 2                                                                 | СВ   | Card enter busy state                                              |  |  |

| 1                                                                 | CD   | Card detect on DAT3                                                |  |  |

| 0                                                                 | EOC  | End of command phase                                               |  |  |

## Table 11. Module Status Register (MMC\_STAT)

The following is common to all bits:

- ☐ The local host can clear a set bit location only by writing a 1 into that bit location. Writing 0 has no effect.

- □ When the core sets a bit location to 1, the local host receives an interrupt signal if the interrupt was enabled.

#### MMC\_STAT[14] Card Status Error (CERR)

| Response<br>Type | Card Status<br>Bits With<br>Error                    | Response Register<br>Significant Bits | Comments                                                                                                                 |

|------------------|------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| R1 (MMC,         | 31–26, 24–16,                                        | MMC_RSP7[15-10, 8-0]†                 | Bit 4 if MMC_SDIO[C14E] = 1 (SDIO)                                                                                       |

| SD, SDIO)        | 4 <sup>2</sup> 3 <sup>2</sup> , 2 <sup>2</sup> (opt) | MMC_RSP6[4, 3, 2] <sup>‡</sup>        | Bit 3 if MMC_SDIO[C13E] = 1 (SD/app spec)                                                                                |

|                  |                                                      |                                       | Bit 2 if MMC_SDIO[C12E] = 1 (app spec)                                                                                   |

| R6 (SD,<br>SDIO) | 15–13, 3                                             | MMC_RSP6[15-13, 3]                    | These correspond to 23, 22, 19, 3 card status<br>errors (SDIO card does not generate error on bit<br>3 force 0—superset) |

| R5 (SDIO)        | 7, 6, 3, 1, 0 <sup>3</sup>                           | MMC_RSP6[15,14, 11, 9, 8]             | <sup>3</sup> Only if MMC_SDIO[15] = 1                                                                                    |

Table 12. Card Status Error (CERR)

<sup>†</sup>These 15 bits can all generate errors (SDIO spec specifies 31, 23–22, 19 while others are 0—superset).

<sup>‡</sup> These 3 bits can also generate errors if enabled.

#### MMC/SD mode only.

The core automatically sets this bit when there is at least one error in a response of type R1, R1b, R6, or R5 if enabled. Only bits referenced as type E (error) set a card status error.

The error handler must parse the response registers to understand the source of the error.

Other responses (type R2, R3, or R4) do not trigger a card status error.

This bit has no meaning and always reads 0 in SPI or SYSTEST modes.

O: No action or no error

1: Error occurred

Value after reset is low.

#### MMC\_STAT[13] Card IRQ (CIRQ)

#### MMC card only:

The core automatically sets this bit when a card is in interrupt mode and exits Wait\_IRQ state (irq) by asserting a low level on the CMD line (cards are in open-drain mode). Only Class 9 MMC cards can be put into interrupt mode when in standby state using a GO\_IRQ\_STATE (CMD40) command.

SPRU765A

#### SDIO card only:

The core automatically sets this bit when a SDIO card has signaled an interrupt on DAT1 line and if the MMC\_SDIO[IRQE] bit was set to 1. The interrupt condition is detected in either 1-bit or 4-bit transfer mode and for either MMC/SD or SPI operation mode. SD memory cards do not support interrupt mode.

This bit has no meaning and always reads 0 in SPI or SYSTEST mode.

- 0: No action or idle

- 1: Card exits IRQ state (MMC card), card interrupt detected (SDIO card).

Value after reset is low.

#### MMC\_STAT[12] OCR Busy (OCRB)

MMC/SD mode only:

The core automatically sets this bit after a SEND\_OP\_COND (CMD1) or a SD\_APP\_OP\_COND (ACMD1) command when one or more cards have not yet completed power-up. When this bit is set, the CMD1/ACMD1 command must be repeated until the card stops responding with a busy condition (a low value on bit 31 of OCR register indicates a busy condition) (see Section 6.3, *Power-Up*, in *The MultiMediaCard–System Specification* or Section 6.4, *SD Memory Card Specifications–Part 1, Physical Layer Specification* or Supplementary Notes–Part 1, Physical Layer Specification).

This bit has no meaning and always reads 0 in SPI or SYSTEST mode.

- 0: No action or card powered up

- 1: OCR busy

Value after reset is low.

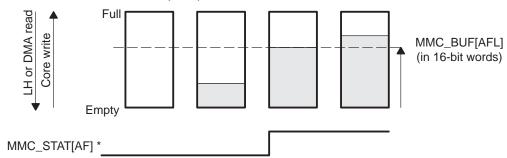

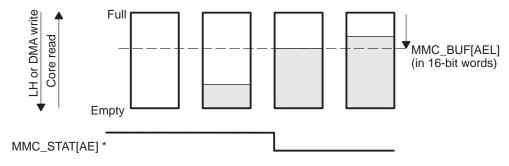

### MMC\_STAT[11] Buffer Almost Empty (AE)

The core automatically sets this bit during a write operation to the card (see class 4 block-oriented write command in Section 4.7.3, *Command Classes,* in *The MultiMediaCard–System Specification–Part 1, Physical Layer Specification, SD Group June 2000*) when the level equals or is below the threshold value (in 16-bit words) set in MMC\_BUF[AEL]. It indicates that the memory card has emptied the buffer to the specified level and that the local host is able to write more data into the buffer.

If the DMA transmit mode is enabled, this bit is never set. Instead, a DMA TX request is generated to the system's main DMA controller.

#### Note: DMA TX Request

The almost-empty status bit and DMA TX request are generated under the same conditions. This bit is set initially when a new block write command is sent to the card. Once the bit is set, the core internally masks a new set condition until the local host has performed MMC\_BUF[AEL] 16-bit word write access(es) to the FIFO.

0: No action or buffer is equal or above almost-empty level

□ 1: Buffer almost empty

Value after reset is low.

## MMC\_STAT[10] Buffer Almost Full (AF)

The core automatically sets this bit during a read operation to the card (see class 2 block-oriented read commands in Section 4.7.3, *Command Classes,* in *The MultiMediaCard–System Specification–Part 1, Physical Layer Specification, SD Group June 2000*) when the level equals or is above the threshold value (in 16-bit words) set in MMC\_BUF[AFL]. It indicates that the memory card has filled out the buffer to the specified level and that the local host needs to empty the buffer by reading it.

If the DMA-receive mode is enabled, this bit is never set. Instead, a DMA RX request is generated to the system's main DMA controller.

#### Note: DMA RX Request

The almost full status bit and DMA RX request are generated under the same conditions. Once set, the core internally masks a new set condition till the local host has performed MMC\_BUF[AFL] 16-bit word read access(es) from the FIFO.

0: No action or buffer is below or equal almost full level

1: Buffer almost full

Value after reset is low.

SPRU765A

## MMC\_STAT[9] Card Read Wait (CRW)

SDIO card only.

The core automatically sets this bit when an SDIO card has entered read wait. It indicates that the previous read multiple transfer (CMD53) has been temporarily stalled and that a new command without data stage (such as CMD52) can be sent to the SDIO card.

This bit is set on the condition that the core has requested a wait to the card (MMC\_SDIO[RW] = 1) and the read wait mode is enabled (MMC\_SDIO[RWE] = 1). The read wait condition is detected in either 1- or 4-bit transfer mode.

0: No action

1: SDIO card in read wait

Value after reset is low.

## MMC\_STAT[8] Command CRC Error (CCRC)

MMC/SD mode only.

The core automatically sets this bit if there is a CRC7 error in the command response (bits 7:1 of response). CRC7 is checked for all command response types (R1 through R6) with the exception of type R3, and conditionally for type R4 if MMC\_SDIO[DCR4] = 1.

In SPI or SYSTEST modes, this bit has no meaning and always reads 0.

- O: No action or no CRC7 error

- 1: CRC7 error

Value after reset is low.

## MMC\_STAT[7] Command Time-Out Error (CTO)

MMC/SD mode only.

The core automatically sets this bit if the card does not respond to any command requiring a response within the specified number of command time-out clock cycles set in MMC\_CTO[CTO].

#### Note: Command Time-Out

If this bit is set after a command time-out, clearing this bit automatically stops the MMC clock and forces the controller FSM to its default state.

This bit has no meaning and always reads 0 in SPI or SYSTEST mode.

• 0: No action or no command time-out

□ 1: Command time-out

Value after reset is low.

# MMC\_STAT[6] Data CRC Error (DCRC)

MMC/SD mode only.