# TEXAS INSTRUMENTS

# 说明

此参考设计展示了一种使用 TI 的 ISO121x 器件对 16 个隔离数字输入通道的紧凑型实现方式。本设计不使用隔离电源,并且每个通道可支持最高 100kHz 输入信号 (200 kbit)。16 个通道总共使用的输入功率不到 1W,因此可实现紧凑的布局和极低的热耗散。所有输入通道均可承受符合 IEC 6100-4-2 标准的 ESD、EFT 和浪涌事件。而且这些通道可承受的输入电压高达 ±60V。

#### 资源

| TIDA-01508   | 设计文件夹 |

|--------------|-------|

| ISO1211      | 产品文件夹 |

| ISO1212      | 产品文件夹 |

| SN74LV165A   | 产品文件夹 |

| SN74LVC1GU04 | 产品文件夹 |

| TVS3300      | 产品文件夹 |

咨询我们的 E2E™ 专家

# 特性

- 16 个数字输入通道,输入电压容差高达 ±60V

- 只需使用主电源,无需隔离电源

- 并行和串行输出选项

- ±6kV IEC 61000-4-2 ESD 性能

- 可耐受 ±2kV 浪涌和 EFT 脉冲群抗扰

- LaunchPad™接头便于快速轻松地进行评估

#### 应用

- 数字输入模块

- 工业机器人 IO 模块

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

System Description www.ti.com.cn

# 1 System Description

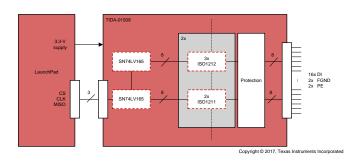

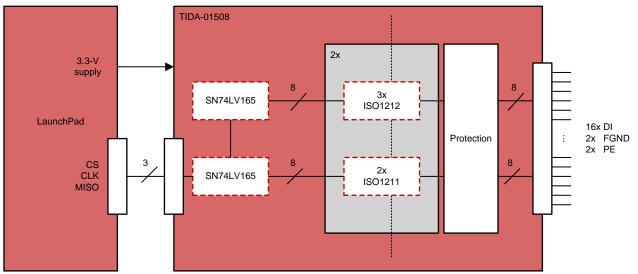

This reference design shows a compact implementation of 16 isolated digital input channels using TI's new ISO121x devices, a single (ISO1211) and dual (ISO1212) channel, isolated, 24-V digital input receiver. The ISO121x device provides an accurate current limit for digital inputs, enabling a power dissipation of less than 1 W for 16 inputs channels. The 16 channels are divided into two groups of eight channels, each consisting out of three dual-channel ISO1212 and two single-channel ISO1211 devices.

ISO121x devices can be configured for IEC 61131-2 Type 1, 2, 3 compliant characteristics with only two external resistors, which are at the same time protecting the device itself against ESD, EFT, and surge events. In this design, all inputs are configured for Type 1.

Every channel is designed to withstand ESD, EFT, and surge events according to IEC 6100-4-2, IEC 6100-4-4, and IEC 6100-4-5, respectively. This protection is achieved by using pulse resistant resistors to configure ISO121x for Type 1. Furthermore, every input can withstand input voltages of up to ±60 V. For additional protection, every channel is either protected with a varistor or with two of Tl's TVS3300 TVS diodes.

To read the output states of the 16 channels, each group of eight outputs is connected to a parallel-in serial-out register (SN74LV165A). The serial outputs of the two registers can be read out using the SPI of a microcontroller. Therefore, this reference design can be plugged onto the MSP430FR5969 LaunchPad or any other TI LaunchPad with the same SPI pinout. The LaunchPad also supplies power to the system.

For serial readout of the output states, the board is designed to support up to input signals of up to 100 kHz (200 kbit) per channel. However, ISO121x devices support data rates of up to 4 Mbps. For parallel readout, an additional 16-pin connector is mounted on the board.

# 1.1 Key System Specifications

#### 表 1. Key System Specifications

| PARAMETER                                                                                                   | SPECIFICATIONS                                                                            | DETAILS   |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------|

| Number of channels                                                                                          | 16 (in groups of 8)                                                                       | 节 2.3.1   |

| Low level threshold = 0                                                                                     | 12.5 V                                                                                    | 节 2.3.1   |

| High level threshold = 1                                                                                    | 13.65 V                                                                                   | 节 2.3.1   |

| Typical threshold voltage hysteresis                                                                        | 1.2 V                                                                                     | 节 2.3.1   |

| I <sub>(INX+SENSEX), typ</sub> Typical sum of current drawn from IN and SENSE pins across temperature       | 2.2 mA per 2.47 mA per channel                                                            | 节 3.2.2.1 |

| I <sub>(INX+SENSEX), max</sub><br>Maximum sum of current drawn from IN and<br>SENSE pins across temperature | 2.1 mA to 2.83 mA per channel; 30 V < V <sub>SENSE</sub> < 36 V                           | 节 3.2.2.1 |

| Power consumption                                                                                           | 859 mW for 16 channels, 24 V <sub>IN</sub>                                                | 节 3.2.2.1 |

| Maximum sampling speed, serial                                                                              | 100 kHz (200 kbps) per channel                                                            | 节 3.2.2.3 |

| Maximum sampling speed, parallel                                                                            | 2 MHz (4 Mbps) per channel                                                                | 节 3.2.2.3 |

| Thermal dissipation                                                                                         | 43°C max after 1 hour of continuous operation, 24 $\rm V_{IN}$ , 25°C ambient temperature | 节 3.2.2.1 |

| ISO121x CHARACTERISTICS                                                                                     |                                                                                           |           |

| Propagation delay                                                                                           | 125 ns                                                                                    |           |

| Isolation rating                                                                                            | 3 kV <sub>RMS</sub>                                                                       |           |

| Working voltage                                                                                             | 500 V <sub>RMS</sub> for 1 minute                                                         |           |

| Common-mode transient immunity                                                                              | 25 kV/μs                                                                                  |           |

| Maximum standoff voltage at input pins                                                                      | ±60 V                                                                                     |           |

www.ti.com.cn System Overview

# 2 System Overview

#### 2.1 Block Diagram

Copyright © 2017, Texas Instruments Incorporated

图 1. Block Diagram of TIDA-01508

# 2.2 Highlighted Products

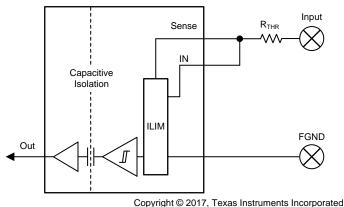

#### 2.2.1 ISO121x

The ISO1211 and ISO1212 are isolated 24-V digital input receivers, compliant to IEC 61131-2 Type 1, 2, and 3 characteristics, and suitable for programmable logic controllers (PLCs) and motor-control digital input modules. Unlike traditional optocoupler solutions with discrete, imprecise current limiting circuitry, the ISO121x devices provide a simple, low-power solution with an accurate current limit to enable the design of compact and high-density I/O modules. These devices do not require field-side power supply and are compatible with high-side or low-side switches. The ISO121x devices operate over the supply range of 2.25 V to 5.5 V, supporting 2.5-V, 3.3-V, and 5-V controllers. A ±60-V input tolerance with reverse polarity protection helps ensure the input pins are protected in case of faults with negligible reverse current. These devices support up to 4-Mbps data rates passing a minimum pulse width of 150 ns for high-speed operation. The ISO1211 device is ideal for designs that require channel-to-channel isolation and the ISO1212 device is ideal for multichannel space-constrained designs.

System Overview www.ti.com.cn

图 2. Functional Block Diagram of ISO121x

#### 2.2.2 **SN74LV165A**

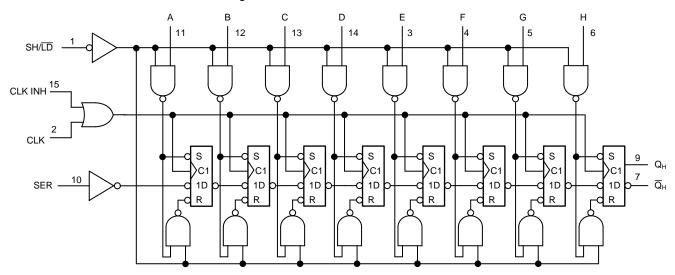

The SN74LV165A devices are parallel-load, 8-bit shift registers designed for 2-V to 5.5-V VCC operation. When the devices are clocked, data is shifted toward the serial output QH. Parallel-in access to each stage is provided by eight individual direct data inputs that are enabled by a low level at the shift/load (SH/LD) input. The SN74LV165A devices feature a clock-inhibit function and a complemented serial output, QH.

S 3 shows a functional block diagram of SN74LV165A.

图 3. Functional Block Diagram of SN74LV165A

#### 2.2.3 SN74LVC1GU04

This single inverter gate is designed for 1.65-V to 5.5-V VCC operation. The SN74LVC1GU04 device contains one inverter with an unbuffered output and performs the boolean function  $Y = \overline{A}$ .

www.ti.com.cn System Overview

#### 2.2.4 TVS3300

The TVS3300 is a transient voltage suppressor that provides robust protection for electronic circuits exposed to high transient voltage events. Unlike a traditional TVS diode, the TVS3300 precision clamp triggers at a lower breakdown voltage and regulates to maintain a flat clamping voltage throughout a transient overvoltage event. The lower clamping voltage combined with a low dynamic resistance enables a unique TVS protection solution that can lower the voltage a system is exposed during a surge event by up to 30% in unidirectional configuration and up to 20% in bidirectional configuration when compared to traditional TVS diodes.

# 2.3 System Design Theory

This section explains the digital input stage and readout functionality of the design.

### 2.3.1 Digital Input Stage

The 16 inputs of this reference design are built up in two groups of eight channels. Three dual-channel ISO1212 and two single-channel ISO1211 are used per group so that maximum flexibility is provided to the user.

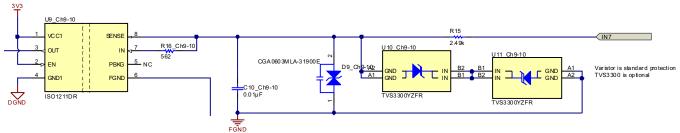

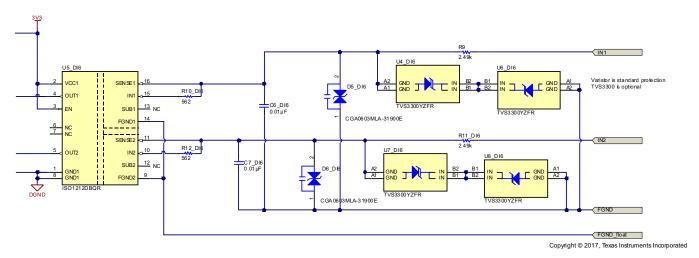

4 and 5 show the input stages of one ISO1212 and one ISO1211, respectively. Although not visible in these figures, pin FGND of the ISO1211 as well as pins FGND1 and FGND2 of the ISO1212 are all connected to input port FGND, which is the common field ground of all digital inputs.

Copyright © 2017, Texas Instruments Incorporated

图 4. ISO1211 Input Stage Schematic

图 5. ISO1212 Input Stage Schematic

System Overview www.ti.com.cn

Every input of the ISO1211 can be configured for Type 1, 2, 3 characteristics according to IEC 61131-2 with resistors  $R_{THR}$  and  $R_{SENSE}$ . In addition, an input capacitor  $C_{IN}$  is connected after  $R_{THR}$  to GND creating an RC filter with  $R_{THR}$  for further protection against ESD, EFT, and surge events. To withstand high pulse voltages,  $R_{THR}$  is selected as a pulse proof resistor.  $\frac{1}{2}$  2 shows the configuration for Type 1 and 3 digital inputs as well as the resulting voltage ratings according to IEC 61002-4-2, IEC 61002-4-4, and IEC 61002-4-5 for specific values of  $R_{THR}$ ,  $R_{SENSE}$ , and  $C_{IN}$ , respectively.

| IEC 61131-2       | R <sub>SENSE</sub> | R <sub>THR</sub> | •               | SURGE      |              | ESD          | IEC EFT |         |

|-------------------|--------------------|------------------|-----------------|------------|--------------|--------------|---------|---------|

| TYPE              |                    |                  | C <sub>IN</sub> | LINE-TO-PE | LINE-TO-LINE | LINE-TO-FGND | E3D     | IEC EFI |

| Type 1            | 562                | 3 kΩ             | 10 nF           | ±1 kV      | ±1 kV        | ±1 kV        | ±6 kV   | ±4 kV   |

| Type 3            | pe 3 562 1 kΩ      | 10 nF            | ±1 kV           | ±1 kV      | ±500 kV      | ±6 kV        | ±4 kV   |         |

| 1 ype 3 502 1 Kt2 | 330 nF             | ±1 kV            | ±1 kV           | ±1 kV      | ±6 kV        | ±4 kV        |         |         |

表 2. Surge, ESD, and EFT

To protect the inputs against surge events with even higher ratings, all inputs are as well protected with either a varistor or two TVS3300 TVS diodes. Those devices are placed in parallel to  $C_{IN}$ .

In this design, all channels as configured for Type 1 inputs with  $R_{THR}$  = 2.4 k $\Omega$  and  $R_{SENSE}$  = 562  $\Omega$ . The typical high-level threshold  $V_{IH}$  and minimum low-level threshold  $V_{IL}$  at the ISO121x input (include  $R_{THR}$ ) for output high and low are given by  $\Delta \vec{x}$  1 and  $\Delta \vec{x}$  2.

$$V_{IH}$$

(typ) = 8.25 V + R  $_{THR}$  ×  $\frac{2.25 \text{ mA} \times 562 \Omega}{\text{R}_{SENSE}}$  = 13.65 V (1)

$$V_{IL} (min) = 7.1 \text{ V} + R_{THR} \times \frac{2.25 \text{ mA} \times 562 \Omega}{R_{SENSE}} = 12.5 \text{ V}$$

(2)

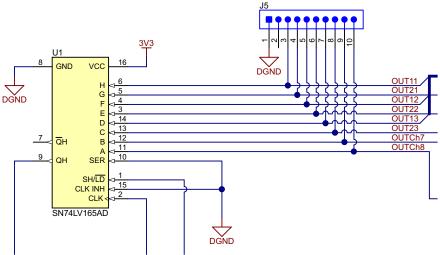

#### 2.3.2 Readout of Digital Outputs

To readout the 16 digital output signals, there exist two options:

- 1. Parallel readout of output signals at connectors J5 (channels 1-8) and J8 (channels 9-16)

- 2. Serial readout of output signals from parallel-in serial-out registers U1 and U2

Copyright © 2017, Texas Instruments Incorporated

图 6. Schematic of Parallel and Serial Readout Options for Output Signals

www.ti.com.cn System Overview

For serial readout, all eight output signals per group are connected to the parallel-in serial-out register SN74LV165A. The output QH of register U1 is connected to input pin SER of register U2. To readout the register, the SPI of the LaunchPad is used. For this, the LaunchPad SPI is connected to the SN74LV165A registers as shown in 表 3:

#### 表 3. Electrical Connections Between SPI and U1, U2

| LAUNCHPAD | U1 (CHANNELS 1-8) | U2 (CHANNELS 9-16) |

|-----------|-------------------|--------------------|

| SPI_MOSI  | Not used          | Not used           |

| SPI_MISO  | Not connected     | QH                 |

| SPI_nCS   | SH/LD             | SH/LD              |

| SPI_CLK   | CLK               | CLK                |

|           | QH                | SER                |

注: The SPI\_nCS signal of the LaunchPad is inverted using a logic gate SN74LVC1GU04 with function  $Y = \overline{A}$ .

$\rightarrow$  SPI\_nCS logic '0' / low = logic '1' / high at SH/ $\overline{LD}$  pin of SN74LV165A

The readout of the 16 output states works as follows:

- 1. SPI\_nCS is high → both SN74LV165A continuously load input states

- 2. SPI\_nCS pulled low → both SN74LV165A store current status of their respective eight inputs

- 3. SPI\_CLK is clocked 16 times → output QH of register U2 first gives out outputs states of inputs H–A (channel 9–16) of U2, second gives out output states H–A (channel 1–8) of U1.

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware and Software

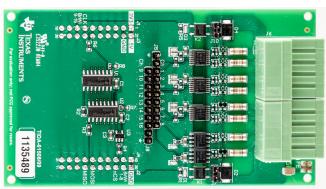

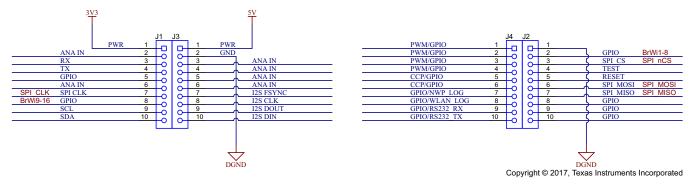

The board can be powered and interfaced over connectors J1–J4. 🛭 7 shows a snapshot of the interface. To simplify the evaluation, it is recommended to use a LaunchPad like the MSP430FR5969 or the CC3220 to power and interface the board.

图 7. BoosterPack Interface of TIDA-01508

#### 3.1.1 Hardware

- Laptop

- MSP430FR5969 LaunchPad

- Signal generator and scope: National Instruments Virtual Bench

- Precision source measure unit (SMU): Keysight B2912A

#### 3.1.2 Software

For parallel readout of the output signals of the ISO121x devices, no special hardware is required. For serial readout using registers U1 and U2, program an SPI routine as described in † 2.3.2.

# 3.2 Testing and Results

#### 3.2.1 Test Setup

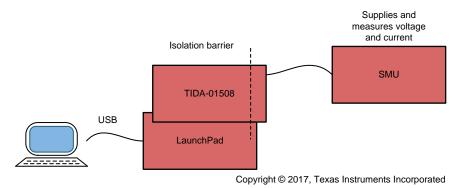

This reference design is plugged onto an MSP430™ LaunchPad, which is connected over USB to a laptop. The laptop is used to readout these stored values. Registers U1 and U2 are read out using the SPI of the LaunchPad. The LaunchPad performs multiple readout and stores the data in its memory. Afterwards, the information is sent to the laptop using the USB interface of the LaunchPad. To generate the digital input signals, test the voltage thresholds, and to measure the power consumption, the SMU is used.

8 shows a simple picture of the test setup.

图 8. Test Setup of TIDA-01508

#### 3.2.2 Test Results

#### 3.2.2.1 Power Dissipation and Thermal Images

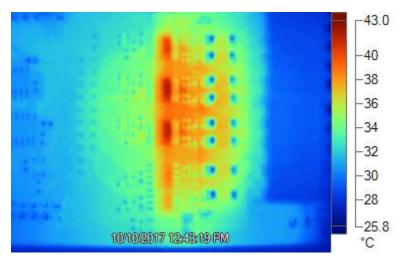

To test the power dissipation of the 16 inputs, a 24-V signal is connected from the SMU to each input. The current that is drawn from the inputs is measured by the same SMU. The setup is left running for one hour, then the current measured and a thermal image is taken.

All 16 inputs together draw a current of 35.8 mA. Therefore, the power dissipation of all 16 channels together is 24 V  $\times$  35.8 mA = 859.2 mW. This means that every channel is only drawing 2.2375 mA in average.

The thermal images show that the two channel devices (ISO1212) heat up to 43°C (see

9). The ambient temperature is around 25.8°C, which is a difference of 17.2°C. Furthermore, this difference shows that the devices only dissipate a small amount of energy, which enables to use them also in applications with high ambient temperatures.

图 9. Thermal Image of TIDA-01508 After 1 Hour With 24-V Input Connected to Every Channel

Next, the input signals are changed to 30 V and the test is repeated. The resulting input current is now 36.3 mA, which results in a power dissipation of 1089 mW. Hence, every channel is only drawing 2.26875 mA in average. Furthermore, this value shows that even for input voltages, the input current stays low.

The power dissipation of the rest of the board is also measured. For an input voltage of 3.3 V, the board consumes 41 mA, which results in an additional 135-mW power dissipation, dominated by the LED power dissipation. This value is the same for 24-V inputs and 30-V inputs.

# 3.2.2.2 Serial Readout of Output States

☑ 10 shows the CLK and MISO signal lines of the SPI for the readout of 16 channels. The output states of the channels are 0-0-1-1-1-0-1 and 1-1-0-1-0-1-0 (channels 9–16 and channels 1–8, respectively). The SPI is running at a frequency of 8 MHz. The overall readout procedure takes around 6 μs. This results in a readout frequency of around 167 kHz.

There is a delay between the readout of the first eight channels and the second eight channels. In a final application, this delay can be optimized to achieve higher readout frequencies.

图 10. Readout Procedure With SPI Running at 8 MHz

11 shows the readout procedure for the first eight channels when the SPI is running at 16 MHz. This results in a readout time for eight output states of only 600 ns. Also for this higher speed, the readout works fine.

图 11. Readout Procedure With SPI Running at 16 MHz

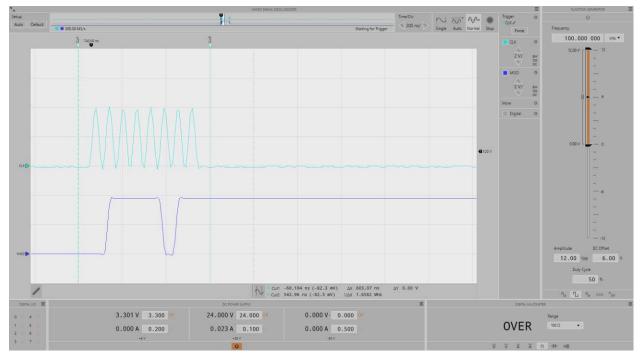

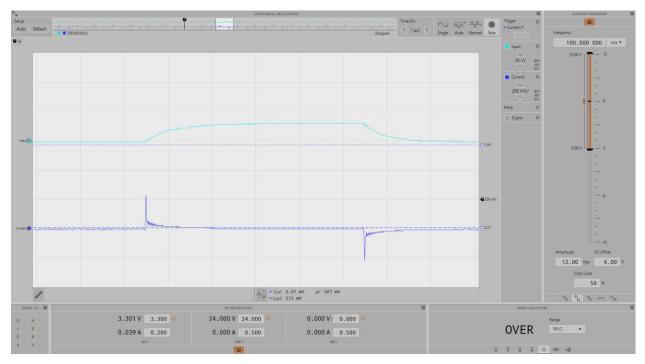

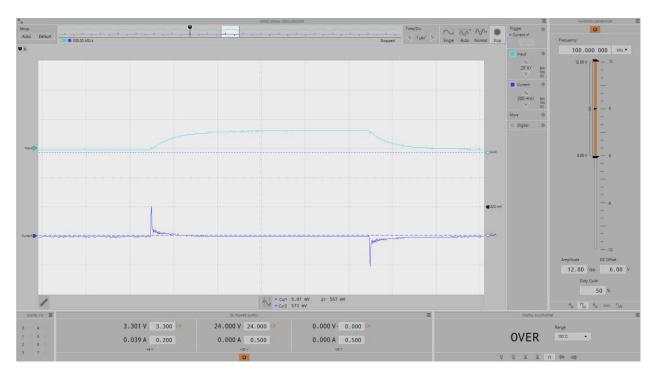

# 3.2.2.3 Input Switching Frequency

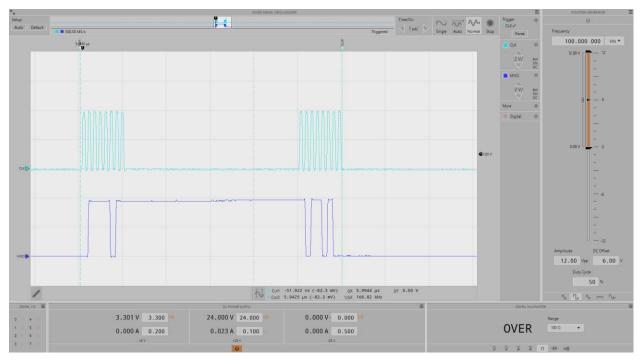

Both TVS3300 and varistor inputs are tested up to 100 kHz by using the signal generator of the SMU. Because the signal generator only supports signals up to 12 V peak to peak, the voltage threshold resistor  $R_{THR}$  has been removed for this test so that the voltage thresholds of the ISO121x are low enough. The signal is set to 12 V peak to peak, rectangular waveform, 100 kHz.

The outputs of the ISO121x are measured with a scope. Furthermore, a 150-m $\Omega$  resistor is placed between the GND of this reference design and the actual GND of the power supply to observe peak currents with a scope. 2 12 shows an input protected with the TVS3300, and 3 13 shows an input protected with the varistor.

图 12. Switching of Outputs and Peak Currents With TVS Protection

图 13. Switching of Outputs and Peak Currents With Varistor Protection

For both protection schemes, the switching can go up to 100 kHz without any problem. Furthermore, when the 12-V signal is switching, a peak current of 200 mV/150 m $\Omega$  = 1.3 A is flowing for a very short time. This is due to the input capacitor in front of the ISO121x.

Design Files www.ti.com.cn

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01508.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01508.

# 4.3 PCB Layout Recommendations

For layout guidelines regarding the digital input stage, refer to the Layout section of ISO121x Isolated 24-V to 60-V Digital Input Receivers for Digital Input Modules.

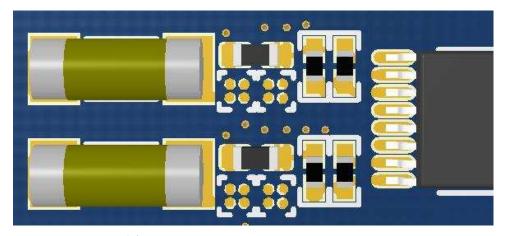

### 4.3.1 Protection Circuit Input Stage

$\boxtimes$  14 shows the two input stages of one ISO1212 from left to right. In this case, the protection circuit consists of the resistor R <sub>THR</sub> and a varistor. Depending on the channel, the varistor can also be replaced by two TVS3300 devices. The two smaller components next to the ISO1211 input pins are the input capacitor C  $_{\text{IN}}$  and the sense resistor R  $_{\text{SENSE}}$ .

图 14. Input Protection Stage of ISO1212

As described in  $\ddagger$  2.3.1, R<sub>THR</sub> is a pulse proof resistor in a 0207 footprint. After R<sub>THR</sub> is passed, the signal line is first routed through the pads of the TVS3300, and varistors before it are connected to the pads of C<sub>IN</sub> and R<sub>SENSE</sub>. This connection ensures that in case of ESD, EFT, or surge events, the protection stage is always passed first before any possibly damaging voltage or current strikes reach the ISO121x. Furthermore, this results in a distance around 8 mm between the high-voltage side or left pad of R<sub>THR</sub>, where the ESD, EFT, or surge event hits first, and the pad of C<sub>IN</sub>. This distance results in additional protection against voltage spikes.

In general, do not place the resistor pad connected to external high voltage within 4 mm of the ISO121x device pins or the  $C_{\text{IN}}$  and  $R_{\text{SENSE}}$  pins to avoid flashovers during EMC tests (refer to the Layout section of ISO121x Isolated 24-V to 60-V Digital Input Receivers for Digital Input Modules).

#### 4.3.2 Layout Prints

To download the layer plots, see the design files at TIDA-01508.

www.ti.com.cn Design Files

#### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01508.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01508.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01508.

#### 5 Software Files

To download the software files, see the design files at TIDA-01508.

#### 6 Related Documentation

- 1. Texas Instruments, ISO121x Isolated 24-V to 60-V Digital Input Receivers for Digital Input Modules

Data Sheet

- 2. Texas Instruments, SNx4LV165A Parallel-Load 8-Bit Shift Registers Data Sheet

- 3. Texas Instruments, SN74LVC1GU04 Single Inverter Gate Data Sheet

- 4. Texas Instruments, TVS3300 33-V Precision Surge Protection Clamp Data Sheet

#### 6.1 商标

E2E, LaunchPad, MSP430 are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 7 About the Author

**TOBIAS PUETZ** is a systems engineer in the Texas Instruments Factory Automation and Control team, where he is focusing on PLC and robotics. Tobias brings to this role his expertise in various sensing technologies as well as power design. Tobias earned his master's degree in electrical engineering and information technology at the Karlsruhe Institute of Technology (KIT), Germany in 2014.

#### 7.1 Acknowledgments

Thank you to ANANT KAMATH for his continuous feedback and support throughout the design process.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司