## **Ⅱ**参考设计 具有功率计量测试结果的两相交错式 **PFC** 转换器

# TEXAS INSTRUMENTS

### TI 参考设计

TI 参考设计为您提供了所需的基础方法、测试和设计文件,以便您快速评估和定制系统。TI 参考设计可帮助您 缩短产品上市时间。

### 设计资源

ILPFC 转换器设计文件 F28xxx 用户指南 包含设计文件的工具文件夹 产品文件夹

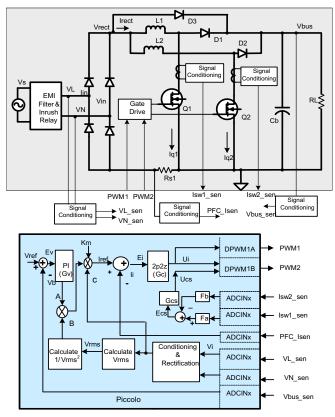

图 1. 采用 C2000 微控制器的交错式 PFC 转换器控制

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

### 设计 特性

- 两相交错式 PFC 硬件和软件

- 95~260Vrms, 47~63Hz, 600W/750W

- 全数字控制环路

- 200kHz 开关频率

- THD 1.5%, PF 0.99, HL 轻负载 0.95(最小值)

- 集成式频率响应分析器 (FRA)

### 应用 场合

- 快速输入电压前馈

- 通过自适应电流环路、谐波补偿和过采样改进 THD

- 借助非线性控制和陷波滤波器实现更快电压环路

- 过压保护

- 输入 RMS 电流、电压、功率和频率测量

- 过零检测, +ve/-ve 半周期检测

咨询我们的 E2E 专家 WebBench 计算器工具

A

### 1 System Description

This document presents the implementation details of a digitally controlled 2-Phase Interleaved Power Factor Correction (ILPFC) converter. A C2000 Piccolo-B control card and a 700W ILPFC EVM are used to implement the complete system.

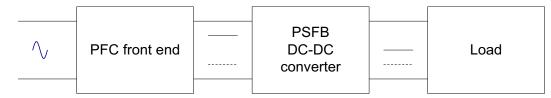

With various regulations limiting the input current harmonic content, especially with the IEC 61000-3-2 standard that defines the harmonic components that an electronic load may inject into the supply line, a power factor correction (PFC) stage has become an integral part of most rectifier designs. The PFC stage usually forms the front end of an isolated ac-dc rectifier system as shown in 🕅 2.

图 2. Isolated AC-DC Rectifier Block Diagram

The PFC converter provides power to non-linear loads from the AC mains while maintaining AC input current of the same wave-shape and phase of that of the AC mains voltage. At the same time, the PFC converter regulates its output DC voltage in order to provide a regulated high voltage bus to any downstream DC-DC converter connected to its output. The downstream DC-DC converter is usually a phase shifted full bridge (PSFB) converter which converts the high DC bus voltage from the PFC stage to a lower voltage such as, +12V, or, an intermediate distribution voltage, typically closer to 48V. The phase shifted full bridge (PSFB) stage provides the desired voltage translation and the high frequency isolation for this offline rectifier system. This document focuses on the implementation detail of the PFC stage. Specifically, it presents the hardware design and the corresponding software to control a 2-phase interleaved power factor correction (ILPFC) front end.

This PFC EVM comes with a Piccolo-B control card. However, the controller resources used for the PFC implementation shows that Piccolo EL can also be used to implement full control of the PFC stage.

### 2 Introduction

The function of a PFC stage is to convert the AC mains voltage to a regulated DC bus voltage while drawing a sine wave input current in phase with the AC input voltage. Typically, this is implemented using a bridge rectifier followed by a boost PFC stage. A C2000 piccolo microcontroller with its on-chip PWM and ADC modules is able to implement complete digital control of such interleaved PFC (ILPFC) system.

### 2.1 PFC Stage Implementation

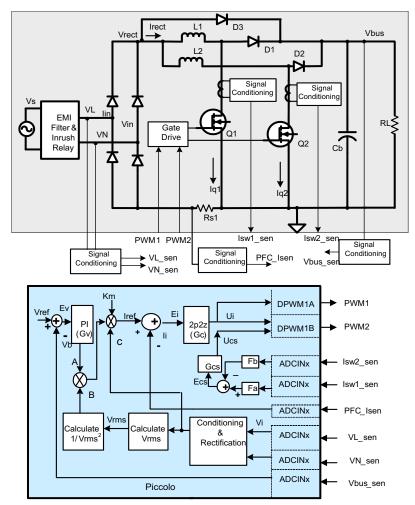

3 illustrates a C2000 controller based interleaved PFC converter control system. The input AC voltage is applied to the PFC converter through the input EMI filter, followed by an inrush current limit and a bridge rectifier. The PFC stage consists of two interleaved boost converters each operating at 200kHz and phase shifted by 180 deg.

图 3. Interleaved PFC Converter Control Using the C2000 Microcontroller

Inductor L1, MOSFET switch Q1 and diode D1 together form one of the boost stages while, L2, Q2, and D2 form the other boost stage. A capacitor Cb at the boost converter output acts as an energy reservoir and this, in conjunction with closed loop PFC control, provides regulated dc voltage to the PFC load RL.

Image 3 indicates all the interface signals needed for full control of this interleaved PFC converter using a C2000 micro-controller (MCU). The MCU controls the hardware using four feedback signals and two PWM outputs. The signals that are sensed and fed back to the MCU include, the line and neutral voltages (Vin\_L & Vin\_N), the PFC input current(Irect), and the DC bus output voltage (Vbus). These sensed signals are used to implement the voltage and current control loops for this IL PFC converter. For phase current balancing two PFC switch currents (Isw1, Isw2) can also be monitored. However, this feature is not implemented in this EVM

The dc bus voltage Vbus, sensed through one of the ADC channels, is compared against the reference bus voltage Vref. The error signal Ev is input to the voltage loop controller Gv which regulates the bus voltage at the reference level so as minimize Ev. The voltage controller Gv has the form of a two pole two zero (2P2Z) compensator. The output of Gv, denoted by the letter A in 8 3, is proportional to the amount of power transfer by the PFC converter. This output A is then multiplied by three parameters, indicated by B, C and Km in 🔄 3, in order to form the reference current command Iref for the PFC current control loop. The signal indicated by B is the inverse of the square of the RMS input voltage which also enables fast feed-forward control of the PFC system. The signal C is proportional to the rectified input voltage, which modulates the voltage controller output A such that the PFC input current has the same shape as that of the PFC input voltage. The parameter Km is the multiplier gain which is used to adjust the range of Iref corresponding to the full input voltage range of the PFC converter. The output of the multiplier block provides the reference signal Iref that is used for control of the total average inductor current, i.e., the PFC input current. This reference current command Iref for the PFC current control loop is compared against the sensed PFC input current li sensed through one ADC channel. The resulting current error signal Ei is then input to the current loop controller Gc which generates the PFC duty ratio command d such that the PFC input current tracks the reference current lref.

In addition to implementing the voltage and current loop controllers, C2000 MCU also uses the sensed line and neutral voltage signals to determine the polarity of the input voltage (+ve & –ve half cycle) and calculates the rectified input voltage, the RMS input voltage, RMS input power and the input line frequency. All these time critical functions are implemented in a fast sampling loop enabled by the C2000 Micro-controller high speed CPU, interrupts, on chip 12-bit ADC module and high frequency PWM modules. A detailed description of the software algorithm is provided in the following chapters.

### 2.2 IL PFC Electrical Specifications

Following lists the key highlights of the C2000 IL PFC EVM:

- Input Voltage (AC Line): 100V (Min) to 260V (Max), 47~63Hz

- Rated Output Voltage 390Vdc

- Rated Output Power 700 Watts @220V input, 550W@110V input

- Full Load efficiency: 97% @220V input

- Power factor at 50% or greater load 0.98 (Min)

- Input Power Monitoring

- PWM frequency 200kHz

### 3 Software Overview

### 3.1 Software Control Flow

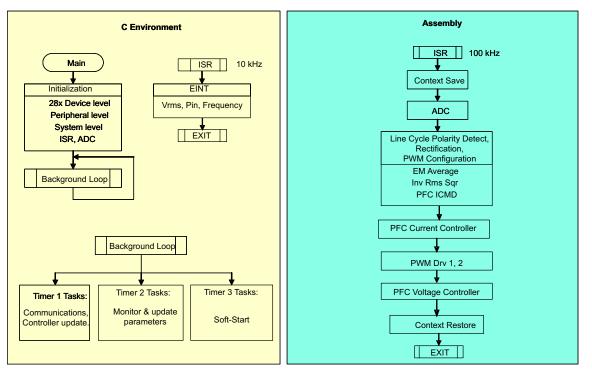

The CCS project for C2000 ILPFC mostly makes use of the "C-background/ASM-ISR" framework. The main fast ISR (100kHz) runs in assembly environment. A slower ISR (10kHz) is also run from C environment. This slow ISR is made interruptible by the fast ISR.

图 4. IL PFC Software Flow Diagram

The CCS project uses C-code as the main supporting program for the application, and is responsible for all system management tasks, monitoring, decision making, intelligence, and host interaction. The assembly code is strictly limited to the fast Interrupt Service Routine (ISR), which runs all the critical control code. Typically this includes reading ADC values, input line cycle polarity detect, sensed line volt rectification, control calculations, and PWM updates. The slower ISR in the C environment calculates the RMS input voltage, RMS input current, RMS input power and frequency of the input line voltage. [8] 4 depicts the general software flow for this project.

The key framework C files used in this project are:

*InterleavedPFC-Main.c* – this file is used to initialize, run, and manage the application. *InterleavedPFC-DevInit\_F2803x.c* – this file is used for 2803x controller initialization. A 2803x control card is provided with the IL PFC EVM. This file is responsible for a one time initialization and configuration of the F280xx device, and includes functions such as setting up the clocks, PLL, GPIO, etc.

The fast ISR consists of a single file:

*InterleavedPFC-DPL-ISR.asm* – this file contains all time critical "control type" code. This file has an initialization section (one time execute) and a run-time section which executes at half the rate (100kHz) as the PWM time-base(200kHz) used to trigger it.

The slow ISR consists of a single file:

SineAnalyzer.h – this file contains code for calculating the RMS voltage, RMS input current, RMS input power and frequency of the input line voltage. This file has an initialization section (one time execute) and a run-time section which executes at 10kHz rate.

The Power Library functions (modules) are "called" from the fast ISR framework.

Library modules may have both a C and an assembly component. In this project, seven library modules are used. The C and corresponding assembly module names are:

| C configure function   | ASM initialization macro   | ASM run-time macro    |

|------------------------|----------------------------|-----------------------|

| PWM_2ch_UpDwnCnt_Cnf.c | PWMDRV_2ch_UpDwnCnt_INIT n | PWMDRV_2ch_UpDwnCnt n |

| ADC_SOC_Cnf.c          | ADCDRV_1ch_INIT m,n,p,q    | ADCDRV_1ch m,n,p,q    |

|                        | PFC_InvRmsSqr_INIT n       | PFC_ InvRmsSqr n      |

|                        | MATH_EMAVG_INIT n          | MATH_EMAVG n          |

|                        | PFC_ICMD_INIT n            | PFC_ICMD n            |

|                        | CNTL_2P2Z_INIT n           | CNTL_2P2Z n           |

#### 表 1. Library Modules

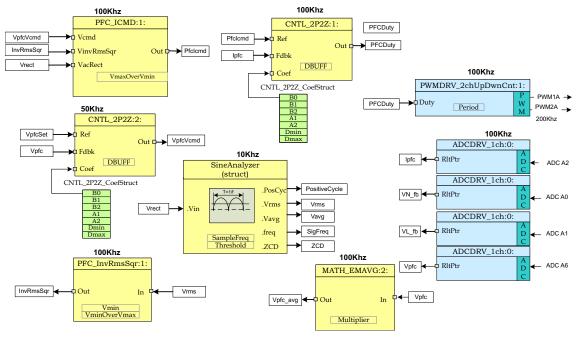

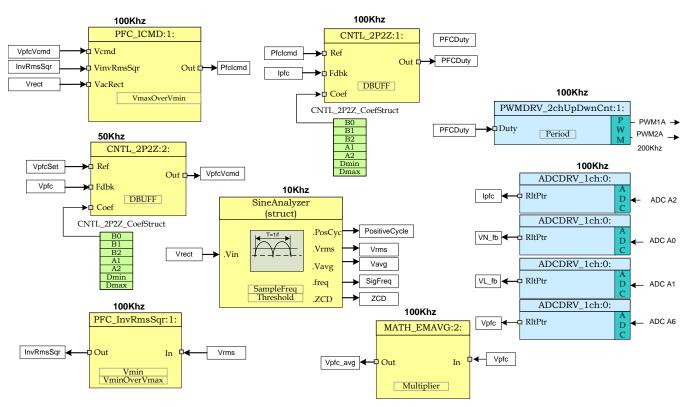

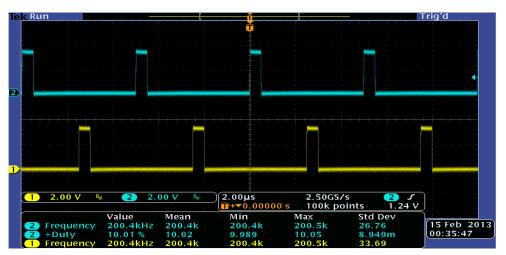

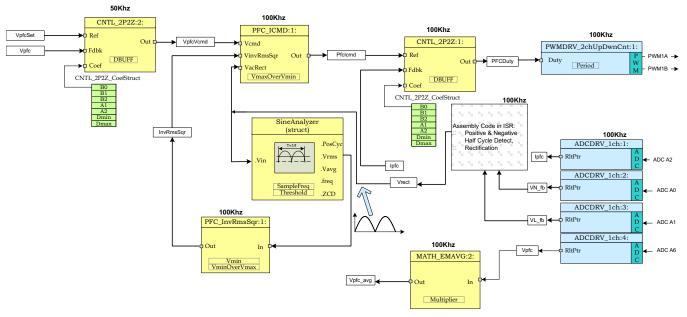

The modules can also be represented graphically as shown in 85.

注: Note the color coding used for the modules in 图 5. The blocks in 'dark blue' represent the on-chip hardware modules in C2000 controller. The blocks in 'blue' are the software drivers associated with these modules. The blocks in 'yellow' are part of the computation carried out on various signals. The controllers used for voltage and current loops have the form of a 2-pole 2-zero compensator. However these can be of other forms such as, PI, PID, 3-pole 3-zero or any other controller suitable for the application. The modular library structure makes it convenient to visualize and understand the complete system software flow as shown in 图 5. It also allows for easy use and modifications of various functionalities. This fact is amply demonstrated in this project by implementing an incremental build approach. This is discussed in more detail in 3.2 节.

图 6. C2000 ILPFC Software Control Flow

As mentioned in 1 <sup>‡</sup>, the IL PFC system is controlled by two feedback loops. The outer voltage loop regulates the DC bus voltage, while a faster inner current loop shapes the input current in order to maintain a high input power factor. <sup>[A]</sup> 6 also shows the rate at which the software modules are executed. For example, the current controller is executed at a rate of 100kHz (half of the PWM switching frequency) while the voltage controller is executed at 50kHz rate.

### 3.2 Incremental Builds

The complete CCS project for ILPFC is divided into three incremental builds. This approach provides the user with a step-by-step method to get familiar with the software and understand how it interacts with the IL PFC hardware. This approach also simplifies the task of debugging and testing the boards.

The build options are shown in  $\mathbb{R}$  2. To select a particular build option set the parameter INCR\_BUILD to the corresponding build selection as shown. This parameter is found in *InterleavedPFC-Settings.h* file. Once the build option is selected, compile the complete project by selecting rebuild-all compiler option. Next chapter provides more details to run each of the build options.

| INCR_BUILD = 1 | Open loop test for boost PFC and ADC feedback (Check sensing circuitry) |

|----------------|-------------------------------------------------------------------------|

| INCR_BUILD = 2 | Open voltage loop and closed current loop control of IL PFC             |

| INCR_BUILD = 3 | Closed voltage loop and closed current loop control of IL PFC           |

### 表 2. Incremental Build Options for PFC

### 3.3 Procedure for running the incremental builds

All software files related to this C2x controlled IL PFC system i.e., the main source files, ISR assembly files and the project file for C framework, are located in the directory

...\controlSUITE\development\_kits\ILPFC\_v1.0\ILPFC. The projects included with this software are targeted for CCSv4.

### CAUTION

There are high voltages present on the board. It should only be handled by experienced power supply professionals in a lab environment. To safely evaluate this board an isolated AC source should be used to power up the unit. Before AC power is applied to the board a voltmeter and an appropriate resistive load (only) should be attached to the output. This will discharge the bus capacitor quickly when the AC power is turned off. The board has not been tested with electronic load and so it should not be used with such load. There is no output over-current protection implemented on the board and so the user should take appropriate measures for preventing any output short circuit condition. The ILPFC board should always be started with 110Vac (60Hz). Once the board is up and running the input voltage can be changed to any other voltage within the specification.

Follow the steps in the following "Build..." sections to build and run the example included in the PFC software.

### 3.3.1 Build 1: Open Loop Boost PFC with ADC

### 3.3.1.1 Objective

The objectives of this build are as follows:

- 1. Evaluate IL PFC PWM and ADC software driver modules

- 2. Verify MOSFET gate driver circuit, voltage, and current sensing circuit

- 3. Familiarize yourself with the operation of Code Composer Studio (CCS).

Under this build the system runs in open-loop mode and so the measured ADC values are used for circuit verification and instrumentation purposes only. Steps required for building and running a project is explained next.

### 3.3.1.2 Overview

8

The signals that are sensed and input to the MCU include the following:

- 1. Line and neutral voltages (VL\_fb, VN\_fb)

- 2. PFC input current (lpfc)

- 3. DC bus voltage (Vpfc).

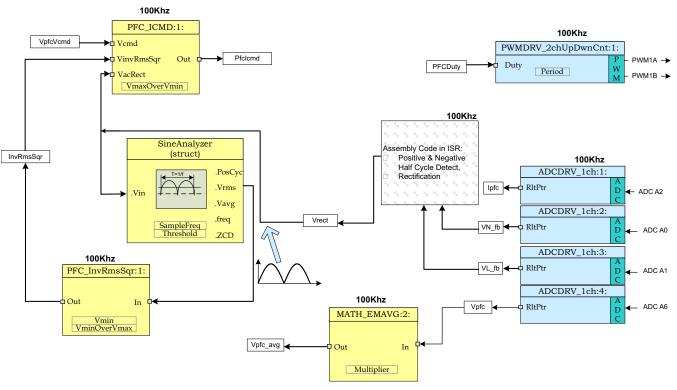

These quantities are read using the ADC driver module and are indicated in [8] 7. The ADC driver module converts the 12-bit ADC result to a 32-bit Q24 value. A few lines of code in the ISR implements the detection of input AC line half cycle (positive & negative half cycles) and the rectification of the input voltage. This generates the input rectified signal Vrect.

图 7. Build 1 Software Blocks

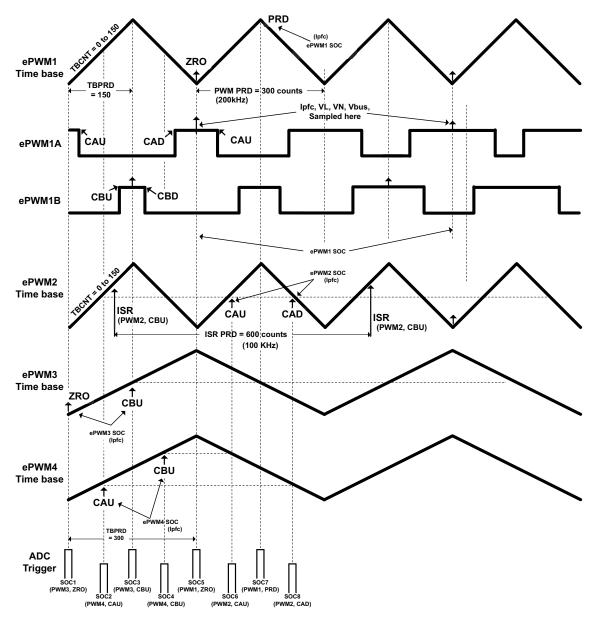

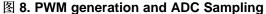

The PWM signals are generated at a frequency of 200 kHz i.e. a period of 5 us. With the controller operating at 60MHz, one count of the time base counter of ePWM1 corresponds to 16.6667ns. This implies a PWM period of 5 us is equivalent to 300 counts of the time base counter (TBCNT1). The ePWM1 module is configured to operate in up-down count mode as shown in 🕅 8. This means a time base period value of 150 (period register value) will give a total PWM period value of 300 counts (i.e. 5 us).

PFC total inductor current is sampled at the midpoint of the PWM ON pulse since the sampled value represents the average inductor current under CCM (continuous conduction mode) condition. Under DCM condition the sampled current value also represents an approximate average inductor current because of the oversampling action. PFC inductor current is also oversampled 8 times during each 10 us time period when both the PFC switches turn on once in their respective 5 us time slot (200kHz PWM). These 8 sampled values are then used to calculate the average PFC inductor current. This is illustrated in 🕅 8.

The voltage signal conversions are also initiated when the PFC switch is on. This is indicated in 😤 8. The flexibility of ADC and PWM modules on C2000 devices allow for precise and flexible ADC start of conversions. In this case the time base counters (TBCNTx) of ePWM1~ePWM4 are used as 4 time bases to generate all the start of conversion (SOC) triggers.

8 shows 8 SOC triggers are generated when:

- 1. TBCNT1 reaches zero and period

- 2. TBCNT2 reaches the preset CMPA values during up and down count

- 3. TBCNT3 reaches zero and preset CMPB value during up count

- 4. TBCNT4 reaches preset CMPA and CMPB values during up count

Systems Applications Collateral A dummy ADC conversion is also performed at TBCNT3 zero point in order to ensure the integrity of the ADC results.

8 also shows the PWM outputs generated using ePWM1 module. PFC current is converted, averaged and then saved as lpfc for PFC current loop control.

All ADC results are read in the ISR by executing the ADC driver module from the 100kHz ISR labeled as \_DPL\_ISR.

This ISR in assembly (\_DPL\_ISR) is triggered by EPWM2 on a CMPB match event on up count. CMPB is set to 80 so that the ISR is triggered only after the ADC conversions are complete. Inside the ISR PWMDRV\_2ch\_UpDwnCnt macros are executed and the PWM compare shadow registers are updated. These are loaded into the active register at the next TBCNT1 = ZERO event. Note that the ISR trigger frequency is half that of the PWM switching frequency as shown in [8] 8.

#### Software Overview

### 3.3.1.2.1 Protection

An overvoltage protection mechanism is implemented in software for this IL PFC EVM.

The sensed DC bus output voltage from the ADC input is compared against the overvoltage protection threshold set by the user. The OV threshold point for this ILPFC EVM has been set to 430V. This threshold parameter is labeled as VBUS\_OVP\_THRSHLD inside the file *InterleavedPFC-Settings.h.* In case of an OV condition the PWM outputs are shut off using the TZ (trip zone) registers. The flexibility of the trip mechanism on C2000 devices provides the possibilities for taking different actions on different trip events. In this project both PWM outputs will be driven low in case of a trip event. Both outputs are held in this state until a device reset is executed.

### 3.3.1.3 Procedure

### 3.3.1.3.1 Start CCS and Open a Project

Follow these steps to execute this build:

- Connect USB connector to the Piccolo controller board for emulation. Connect the 12V bias supply output (external bias supply provided with the PFC EVM) to JP1 and apply this bias voltage to the board by setting the switch SW1 to position "Ext". By default, the Piccolo control card jumpers (see Piccolo control card documentation) are configured such that the device boot from FLASH. Change these jumper settings to allow code execution under CCS control.

- 2. Start Code Composer Studio (CCS). In CCS, a project contains all the files and build options needed to generate an executable output file (.out) which can run on the MCU hardware. On the menu bar click: Project -> Import Existing CCS/CCE Eclipse Project and under Select root directory navigate to and select ... *controlSUITE\development\_kits\LPFC\_v1.0\LPFC* directory. Make sure that under the Projects tab ILPFC is checked. Click Finish. This project will invoke all the necessary tools (compiler, assembler & linker) for building the project.

- 3. In the project window on the left, click the plus sign (+) to the left of Project. Your project window will look like the following in 图 9:

| Edit View Navigste Project Target Tools Scripts Window | 115057 | 6.01             |                                                                                                                  |                                             |

|--------------------------------------------------------|--------|------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| (C++ Projects 🛛 🖓 🖓 🖓 🖗 📄 🏈 ▽ ¬ 🗆                      |        |                  | ILPFC-DPL-ISR.asm                                                                                                |                                             |

| SILPFC [Active - F2803x_FLASH]                         | 1 //-  |                  |                                                                                                                  |                                             |

| T 🔷 Binarias                                           | z //   | FILE:            | 2Ph ILPFC-Main.C                                                                                                 |                                             |

| 🗄 🚰 Includes                                           | 3 //   |                  | 12                                                                                                               |                                             |

| 🗄 🍃 F2803x_FLASH                                       | 4 //   | Description:     | 2-Ph Interleaved PF                                                                                              | 2                                           |

| 🗄 🚡 11/FC Sottings.h                                   | 5 //   |                  | The file drives dut                                                                                              | y on PWHIA and PWHIB using C28x             |

| 🗄 📙 SineAnalyzer.h                                     | 6 //   |                  | C28x ISR is trigger                                                                                              | ed by the PWM 2 interrupt                   |

| E & ADC_SOC_Cnf.c                                      | 7 //   |                  |                                                                                                                  |                                             |

| H DSP2ROSy_Adv:r                                       | 8 //   | Version:         | 1.0                                                                                                              |                                             |

| 🗄 🔓 DSP2803x_CodeStartBranch.asm                       | 9 //   |                  |                                                                                                                  |                                             |

| 🗄 🔓 DSP2803x_GobalVariableDets.c                       | 10 //  | Target:          | TMS320F2803x(Piccol                                                                                              | зВ),                                        |

| 🗄 🛱 DSP2803x usDelay.asm                               | 11 //  |                  |                                                                                                                  |                                             |

| 🗄 🕜 1LPFC-DevInit_F2803x.c                             | 12 //- |                  |                                                                                                                  |                                             |

| 🗃 📓 1LPFC-DPL-ISR.asıı                                 |        |                  | Instruments ?2004-2                                                                                              |                                             |

| 🗄 🕜 1LPFC-Main.c                                       | 14 //- |                  |                                                                                                                  |                                             |

| E _ PWM_1ch_UpDwnCrk_Crf.c                             |        | Revision Histor  |                                                                                                                  |                                             |

| B PWM_2ch_UpDwnCrk_Crf.c                               |        |                  |                                                                                                                  |                                             |

| PWMDRV_2ch_UpDwnCnt.asm                                |        |                  | cription / Status                                                                                                |                                             |

| 🗄 🙀 SciConmsGuí.c                                      |        |                  |                                                                                                                  |                                             |

| G DSP2813r_Headers_nnnRIOS.md                          |        |                  | N11 - File created                                                                                               |                                             |

| F28035_FLASH.CMD                                       |        |                  |                                                                                                                  |                                             |

| n di.itishi di     | 21 //  |                  |                                                                                                                  |                                             |

| S macros.ini                                           |        | PLEASE READ - US | eful notes about thi                                                                                             | a Project                                   |

| - 🖁 xds100v1_F28035.ccml (Active)Default]              | 23     |                  |                                                                                                                  |                                             |

|                                                        |        |                  | and the second | several files, the must important ones are; |

|                                                        |        | "2PH_ILPFC-Hai   |                                                                                                                  |                                             |

|                                                        | 26 //  |                  | on Initialization, P                                                                                             | eripheral config,                           |

|                                                        |        | - Applicati      |                                                                                                                  |                                             |

|                                                        | 28 //  |                  | ckground code loops                                                                                              | and lask scheduling                         |

|                                                        | 29 //  | "2PH_ILPFC-Dev   | -                                                                                                                | lock, PLL, WD, GPIO menning                 |

#### 图 9. CCS Project Window

### 3.3.1.3.2 Device Initialization, Main, and ISR Files

- 注: Do not make any changes to the source files Only Inspect

- 1. Open and inspect *InterleavedPFC-DevInit\_F2803x.c* by double clicking on the filename in the project window. Note that system clock, peripheral clock prescale, and peripheral clock enables have been setup. Next, notice that the shared GPIO pins have been configured.

- 2. Open and inspect *InterleavedPFC-Main.c.* Notice the call made to DeviceInit() function and other variable initialization. Also notice code for different incremental build options, the ISR initialization and the background for(;;) loop.

- 3. Locate and inspect the following code in the main file under initialization code specific for build 1. This is where the PWMDRV\_2ch\_UpDwnCnt and ADCDRV\_1CH blocks are connected in the control flow.

#### Software Overview

www.ti.com.cn

```

#if (INCR_BUILD == 1) // Open Loop Debug only

// Lib Module connection to "nets"

// Connect the PWM Driver input to an input variable, Open Loop System

ADCDRV_1ch_Rlt1 = &Ipfc1;

ADCDRV_1ch_Rlt2 = &Ipfc2;

ADCDRV_ICh_RIt3 = &Ipfc2;

ADCDRV_Ich_RIt3 = &Ipfc3;

ADCDRV_Ich_RIt4 = &Ipfc4;

ADCDRV_Ich_RIt5 = &Ipfc5;

ADCDRV_1ch_Rlt6 = &Ipfc6;

ADCDRV_1ch_Rlt7 = &Ipfc7;

ADCDRV_1ch_Rlt8 = &Ipfc8;

ADCDRV_1ch_R1t9 = &Vbus;

ADCDRV 1ch R1t10 = &VL fb;

ADCDRV_1ch_Rlt11 = &VN_fb;

PWMDRV_2ch_UpDwnCnt_Duty1 = &DutyA;

// Math_avg block connections - Instance 2

MATH_EMAVG_In2=&Vbus;

MATH_EMAVG_Out2=&VbusAvg;

MATH_EMAVG_Multiplier2=_IQ30(0.00025);

// INV_RMS_SQR block connections

VrectRMS = (sine_mainsV.Vrms) << 9;//Q15 --> Q24, (sine_mainsV.Vrms) is in Q15

PFC_InvRmsSqr_In1=&VrectRMS;

PFC_InvRmsSqr_Out1=&VinvSqr;

PFC_InvRmsSqr_VminOverVmax1=_IQ30(0.1956); // 80V/409V

PFC_InvRmsSqr_Vmin1=_IQ24(0.1956);

// PFC ICMD block connections

PFC_ICMD_Vcmd1 = &VbusVcmd;

PFC_ICMD_VinvSqr1=&VinvSqr;

PFC_ICMD_VacRect1=&Vrect;

PFC_ICMD_Out1=&PFCIcmd;

PFC_ICMD_VmaxOverVmin1=_IQ24(3.00); // 3.5625 <=> 285V/80V

```

4. Locate and inspect the following code in the main file under initialization code. This is where the PWMDRV\_2ch\_UpDwnCnt block is configured and initialized. This is common for all incremental builds. This PWM driver module inputs the total PWM period value of 300 and internally calculates the period register value of 150.

| <pre>// Configure ePWMs to generate ADC SOC pulses</pre>                                                                                                                                                                                                                                                          | for PFC current over sampling                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPwm1Regs.ETSEL.bit.SOCAEN = 1;                                                                                                                                                                                                                                                                                   | // Enable ePWM1 SOCA pulse                                                                                                                                                                                     |

| EPwm1Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;                                                                                                                                                                                                                                                                        | // SOCA from ePWM1 Zero event                                                                                                                                                                                  |

| EPwm1Regs.ETPS.bit.SOCAPRD = ET_1ST;                                                                                                                                                                                                                                                                              | // Trigger ePWM1 SOCA on every event                                                                                                                                                                           |

| EPwm1Regs.ETSEL.bit.SOCBEN = 1;                                                                                                                                                                                                                                                                                   | // Enable ePWM1 SOCB pulse                                                                                                                                                                                     |

| EPwm1Regs.ETSEL.bit.SOCBSEL = ET_CTR_PRD;                                                                                                                                                                                                                                                                         | // SOCB from ePWM1 PRD event                                                                                                                                                                                   |

| EPwm1Regs.ETPS.bit.SOCBPRD = ET_1ST;                                                                                                                                                                                                                                                                              | // Trigger ePWM1 SOCB on every event                                                                                                                                                                           |

| EPwm2Regs.ETSEL.bit.SOCAEN = 1;<br>EPwm2Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPA;<br>EPwm2Regs.ETPS.bit.SOCAPRD = ET_1ST;<br>EPwm2Regs.ETSEL.bit.SOCBEN = 1;<br>EPwm2Regs.ETSEL.bit.SOCBSEL = ET_CTRD_CMPA;<br>EPwm2Regs.ETPS.bit.SOCBPRD = ET_1ST;                                                                  | <pre>// Enable ePWM2 SOCA pulse // SOCA from ePWM2 CMPA up event // Trigger ePWM2 SOCA on every event // Enable ePWM2 SOCB pulse // SOCB from ePWM2 CMPA down event // Trigger ePWM2 SOCB on every event</pre> |

| <pre>// Configure ePWMs to generate ADC SOC pulses<br/>EPwm3Regs.ETSEL.bit.SOCAEN = 1;<br/>EPwm3Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;<br/>EPwm3Regs.ETPS.bit.SOCAPRD = ET_1ST;<br/>EPwm3Regs.ETSEL.bit.SOCBEN = 1;<br/>EPwm3Regs.ETSEL.bit.SOCBSEL = ET_CTRU_CMPB;<br/>EPwm3Regs.ETPS.bit.SOCBPRD = ET_1ST;</pre> | <pre>// Enable ePUM3 SOCA pulse // SOCA from ePUM3 zero event // Trigger ePUM3 SOCA on every event // Enable ePUM3 SOCB pulse // SOCB from ePUM3 CMPB up event // Trigger ePUM3 SOCB on every event</pre>      |

| <pre>EPwm4Regs.ETSEL.bit.SOCAEN = 1;</pre>                                                                                                                                                                                                                                                                        | // Enable ePWN4 SOCA pulse                                                                                                                                                                                     |

| EPwm4Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPA;                                                                                                                                                                                                                                                                       | // SOCA from ePWN4 CMPA up event                                                                                                                                                                               |

| EPwm4Regs.ETPS.bit.SOCAPRD = ET_1ST;                                                                                                                                                                                                                                                                              | // Trigger ePWN4 SOCA on every event                                                                                                                                                                           |

| EPwm4Regs.ETSEL.bit.SOCBEN = 1;                                                                                                                                                                                                                                                                                   | // Enable ePWN4 SOCB pulse                                                                                                                                                                                     |

| EPwm4Regs.ETSEL.bit.SOCBSEL = ET_CTRU_CMPB;                                                                                                                                                                                                                                                                       | // SOCB from ePWN4 CMPB up event                                                                                                                                                                               |

| EPwm4Regs.ETPS.bit.SOCEPRD = ET_1ST;                                                                                                                                                                                                                                                                              | // Trigger ePWM4 SOCB on every event                                                                                                                                                                           |

ZHCU189-April 2014

```

Software Overview

```

5. Also locate and inspect the following code in the main file under initialization code. This is where the ADCDRV\_1CH block is configured and initialized. This is also common for all incremental builds.

```

// ADC Channel Selection for IL PFC EVM

//8x Oversampling of PFC current

ChSel[0] = 4; // Dummy read for first

ChSel[1] = 4;

// A4 - IpfcA

ChSe1[2] = 4;

// A4 - IpfcA

// A4 - IpfcA

// A4 - IpfcA

ChSe1[3] = 4;

ChSel[4] = 4;

// A4 - IpfcA

ChSel[5] = 4;

// A4 - IpfcA

ChSel[6] = 4;

ChSel[7] = 4;

// A4 - IpfcA

ChSel[8] = 4;

// A4 - IpfcA

ChSel[9] = 2;

// A2 - Vbus

ChSel[10] = 10; // B2 - VL_fb

// BO - VN fb

ChSel[11] = 8;

// ADC Trigger Selection, ILPFC board

TrigSel[0] = ADCTRIG EPWM3 SOCA;

// ePWM3, ADCSOCA

TrigSel[1] = ADCTRIG EPWM3 SOCA; // ePWM3, ADCSOCA

TrigSel[2] = ADCTRIG_EPWM4_SOCA; // ePWM4, ADCSOCA

TrigSel[3] = ADCTRIG_EPWM3_SOCB; // ePWM3, ADCSOCB

TrigSel[4] = ADCTRIG EPWN4 SOCB; // ePWM4, ADCSOCB

TrigSel[5] = ADCTRIG EPWM1 SOCA; // ePWM1, ADCSOCA

TrigSel[6] = ADCTRIG EPUM2 SOCA; // ePUM2, ADCSOCA

TrigSel[7] = ADCTRIG EPWM1 SOCB;

// ePWM1, ADCSOCB

TrigSel[8] = ADCTRIG_EPWM2_SOCB;

// ePWM2, ADCSOCB

TrigSel[9] = ADCTRIG_EPWM1_SOCA; // ePWM1, ADCSOCA

```

TrigSel[10] = ADCTRIG\_EPWM1\_SOCA; // ePWM1, ADCSOCA

TrigSel[11] = ADCTRIG EPWM1 SOCA; // ePWM1, ADCSOCA

ADC\_SOC\_CNF(ChSel, TrigSel, ACQPS, 17, 0);

EPwm2Regs.CMPA.half.CMPA = 75;

EPwm4Regs.CMPA.half.CMPA = 75;

// Configure ADC

InitAdc();

AdcOffsetSelfCal();

EPwm3Regs.CMPB = 150;

EPwm4Regs.CMPB = 225;

```

// Configure ePWMs to generate ADC SOC pulses for PFC current over sampling

Promingure errors to generate and soc purses for procedulent over sampling

EPwmiRegs.ETSEL.bit.SOCAEN = 1;

// Enable ePWM1 SOCA pulse

EPwmiRegs.ETSEL.bit.SOCAPRD = ET_IST;

// Trigger ePWM1 SOCA on every event

EPwmiRegs.ETSEL.bit.SOCBEN = 1;

// Enable ePWM1 SOCB pulse

EPwmiRegs.ETSEL.bit.SOCBEN = 1;

// SOCB from ePWM1 PRD event

EPwmiRegs.ETPS.bit.SOCBPRD = ET_IST;

// Trigger ePWM1 SOCB on every event

// Enable ePWM2 SOCA pulse

EPwm2Regs.ETSEL.bit.SOCAEN = 1;

EPwm2Regs.ETSEL.bit.SOCASEL = ET_CTRU_CMPA; // SOCA from ePWM2 CMPA up event

EPwm2Regs.ETPS.bit.SOCAPRD = ET 1ST; // Trigger ePWM2 SOCA on every event

EPwm2Regs.ETSEL.bit.SOCBEN = 1; // Enable ePWM2 SOCB pulse

EPwm2Regs.ETSEL.bit.SOCBEN = 1;

EPwm2Regs.ETSEL.bit.SOCBSEL = ET_CTRD_CMPA; // SOCB from ePWM2 CMPA down event

EPwm2Regs.ETPS.bit.SOCBPRD = ET 1ST;

// Trigger ePWM2 SOCB on every event

// Configure ePWMs to generate ADC SOC pulses

EPwm3Regs.ETSEL.bit.SOCAEN = 1;

// Enable ePWM3 SOCA pulse

EPwm3Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO; // SOCA from ePWM3 zero event

EPwm3Regs.ETPS.bit.SOCAPRD = ET_1ST; // Trigger ePWM3 SOCA on every event

EPwm3Regs.ETSEL.bit.SOCBEN = 1; // Enable ePWM3 SOCB pulse

EPwm3Regs.ETSEL.bit.SOCBSEL = ET_CTRU_CMPB; // SOCB from ePWM3 CMPB up event

EPwm3Regs.ETPS.bit.SOCBPRD = ET_1ST;

// Trigger ePWM3 SOCB on every event

// Enable ePWM4 SOCA pulse

EPwm4Regs.ETSEL.bit.SOCAEN = 1;

EPwm4Regs.ETSEL.bit.SOCASEL = ET CTRU CMPA; // SOCA from ePWM4 CMPA up event

EPwm4Regs.ETPS.bit.SOCAPRD = ET_IST; // Trigger ePWM4 SOCA on every event

EPwm4Regs.ETSEL.bit.SOCBEN = 1;

// Enable ePWM4 SOCB pulse

EPwm4Regs.ETSEL.bit.SOCBSEL = ET_CTRU_CMPB;

// SOCB from ePWM4 CMPB up event

EPwm4Regs.ETPS.bit.SOCBPRD = ET_1ST;

// Trigger ePWM4 SOCB on every event

```

Open and inspect InterleavedPFC-DPL-ISR.asm. Notice the \_DPL\_Init and \_DPL\_ISR sections under build 1. This is where the PWM and ADC driver macro instantiation is done for initialization and runtime, respectively.

#### 3.3.1.3.3 Build and Load the Project

Texas

www.ti.com.cn

TRUMENTS

- 1. Select the incremental build option as 1 in the InterleavedPFC-Settings.h file.

- 注: Whenever you change the incremental build option in *InterleavedPFC-Settings.h*, always do a "Rebuild All".

- 2. Click Project -> "Rebuild All" button and watch the tools run in the build window.

- Click Target ->"Debug Active Project". CCS will ask you to open a new Target configuration file if one hasn't already been selected. If a valid target configuration file has been created for this connection you may jump to 节 3.3.1.3.4. In the New target Configuration Window type in the name of the .ccxml file for the target you will be working with (Example: xds100-F28035.ccxml). Check "Use shared location" and click Finish.

- 4. In the .ccxml file that open up select Connection as "Texas Instruments XDS100v2 USB Emulator" and under the device, scroll down and select "TMS320F28035". Click Save.

- 5. Click Targe -> -> "Debug Active Project". Select project configuration as F2803x\_FLASH. The program will be loaded into the FLASH. You should now be at the start of Main().

#### 3.3.1.3.4 Debug Environment Windows

It is standard debug practice to watch local and global variables while debugging code. There are various methods for doing this in Code Composer Studio, such as memory views and watch views. If a watch view did not open when the debug environment was launched, open a new watch view and add various parameters to it by following the procedure given below.

- 1. Click View -> Watch on the menu bar.

- 2. Click the "Watch (1)" tab at the top watch view. You may add any variables to the watch view. In the empty box in the "Name" column, type the symbol name of the variable you want to watch and press enter on keyboard. Be sure to modify the "Format" as needed. The watch view should look something like the following in 🕅 10

|                                                                                             |                                                                  |                                                                           |                                      |                                                                                         |                                            | N.S.                                                                      |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------|

| 🗒 🗅 🗟 🍇 l 🗷 % 😃 🥵 l 🔊 🗵 l 🏇 + l 🗞 + l 🚱 - l 🦻 l 🖋 l 🖉 - 🏹 - 🏷 (+                            |                                                                  |                                                                           |                                      |                                                                                         |                                            | 🖹 🅸 Debug                                                                 |

| 🏁 Debug 🛛 🛛 🙀 🔹 🕫 🐨 🐨 🐨 🕼 🌸 • 🦑 🖻 🏹 🗖                                                       | Local (1) 🥙 Watch (1)                                            | ×                                                                         |                                      | 8                                                                                       | ××                                         | 8 8 â [                                                                   |

| BridgelessPFC [F2803x_FLASH] - Texas Instruments XDS100/1 USB Emulator_0/C28xx [Project Deb | 00= VrectRMS<br>00= flag_NL_Vloop<br>00= run_flag<br>00= error_v | Value<br>-1029595277<br>1<br>-15810<br>0.0<br>115.5399276<br>-20.90805238 | 0x0000<br>0x0000<br>0x0000<br>0x0000 | ess<br>19038@Data<br>19002@Data<br>19034@Data<br>19034@Data<br>19034@Data<br>19032@Data | Type<br>long<br>int<br>int<br>long<br>long | Format<br>Natural<br>Natural<br>Q=Value(24)<br>Q=Value(24)<br>Q=Value(24) |

| < »                                                                                         |                                                                  |                                                                           |                                      |                                                                                         |                                            |                                                                           |

| BridgelessPFC-Main.c      BridgelessPFC-DPL-ISR.asm                                         |                                                                  |                                                                           | - 0                                  | 🚟 Disassembly                                                                           | (main) 8                                   | 3                                                                         |

| <pre>319 //***********************************</pre>                                        |                                                                  |                                                                           |                                      |                                                                                         | on here                                    | <b>•</b> & :                                                              |

图 10. CCS Watch View for Build 1

### 3.3.1.3.5 Using Real-Time Emulation

Real-time emulation is a special emulation feature that allows the windows within Code Composer Studio to be updated at a rate up to 10 Hz while the MCU is running. This not only allows graphs and watch views to update, but also allows the user to change values in watch or memory windows, and see the effect of these changes in the system. This is very useful when changing control law parameters on-the-fly, for example.

- 1. Enable real-time mode by hovering your mouse on the buttons on the horizontal toolbar and clicking Enable Silicon Real-time Mode (service critical interrupts when halted, allow debugger accesses while running)

button.

- A message box may appear. If so, select YES to enable debug events. This will set bit 1 (DGBM bit) of status register 1 (ST1) to a "0". The DGBM is the debug enable mask bit. When the DGBM bit is set to "0", memory and register values can be passed to the host processor for updating the debugger windows.

- 3. Click on Continuous Refresh buttons 💯 for the watch view.

#### 3.3.1.3.6 Run the Code

- 1. Run the code by using the <F8> key, or using the Run button on the toolbar, or using Target -> Run on the menu bar.

- 2. In the watch view, add the variable DutyA and set it to 0.1 (=1677721 in Q24). This variable sets the duty cycle for the PFC converter.

- 3. Apply an appropriate resistive load to the PFC system at the DC output (8k/20W, or, 4K/40W or, 2k/80W).

- 4. Slowly apply AC Power to the board. Measure and verify the DC bus voltage corresponding to applied input voltage and the duty ratio.

- 5. Use DutyA to slowly change the duty from the watch window. The boost converter output voltage should change accordingly.

- 注: Observe the output voltage carefully, the output voltage should **not** be allowed to exceed the maximum voltage rating of the board (400V).

- 6. Add the other variables such as, Vbus, VL\_fb, VN\_fb and verify the different ADC results in the watch view. For AC voltage input the sensed line and neutral voltage(VL\_fb, VN\_fb) will vary continuously in the watch window. Therefore, to verify the ADC readings and the line and neutral voltage sense circuits, the user may apply DC input voltage (20~200V) instead of AC (as stated in Step 4). In that case the PFC stage will temporarily operate in a pure dc-dc boost mode. CCS watch window below shows some of the variables under Build 1 when the input AC voltage is about 90Vrms, open loop duty is 10%, DC bus resistive load is about 4K ohm and DC bus voltage is 200V. Notice the Q-format used for each variable. Under this condition first four variables in the watch window show the AC line frequency, the RMS input voltage, the DC bus voltage and the RMS input current. The variable Gui\_PinRMS shows the input power.

| Name              | Value          | Address         | Туре | Format      |

|-------------------|----------------|-----------------|------|-------------|

| (X)= Gui_Freq_Vin | 61.0           | 0×00009003@Data | int  | Q-Value(6)  |

| (X)= Gui_VrectRMS | 89.875         | 0x00009005@Data | int  | Q-Value(6)  |

| (x)= Gui_Vbus     | 197.953        | 0x00009013@Data | int  | Q-Value(6)  |

| (X)= Gui_IrectRMS | 0.117188       | 0x00009004@Data | int  | Q-Value(10) |

| (X)= DutyA        | 0.09999996424  | 0x00009044@Data | long | Q-Value(24) |

| (×)= Ipfc_fltr    | 0.002899169922 | 0x0000904E@Data | long | Q-Value(24) |

| (×)= VbusAvg      | 0.3757413626   | 0x00009046@Data | long | Q-Value(24) |

| (X)= Gui_PinRMS   | 10.78125       | 0x00009060@Data | long | Q-Value(5)  |

| (×)= Vbus         | 0.3759765625   | 0x00009042@Data | long | Q-Value(24) |

| (X)= VbusAvg      | 0.375797689    | 0x00009046@Data | long | Q-Value(24) |

| (×)= VL_fb        | 0.2875976563   | 0x00009040@Data | long | Q-Value(24) |

| 🕪 VN_fb           | 0.1860351563   | 0x00009050@Data | long | Q-Value(24) |

7. The following oscilloscope capture shows two PWM outputs (Ch1 & Ch2) with duty ratio set to 10%. The PWM frequency is measured to be 200kHz.

- 8. Try different duty cycle values and observe the corresponding ADC results. Increase duty cycle value in small steps. Always observe the output voltage carefully, this should not be allowed to exceed the capabilities of the board. Different waveforms, like the PWM gate drive signals, input voltage and current and output voltage may also be probed and verified using an oscilloscope. Appropriate safety measures must be taken while probing these high voltage signals.

- Fully halting the MCU when in real-time mode is a two-step process. With the AC input turned off wait until the DC bus capacitor is fully discharged. First, halt the processor by using the Halt button on the toolbar, or by using Target -> Halt. Then take the MCU out of real-time mode. Finally reset the MCU.

- 10. You may choose to leave Code Composer Studio running for the next exercise or optionally close CCS.

- 11. End of Exercise

### 3.3.1.4 Build 2: IL PFC with Closed-Current Loop

### 3.3.1.4.1 Objective

The objective of this build is to verify the operation of the IL PFC under closed current loop mode.

### 3.3.1.4.2 Overview

I1 shows the software blocks used in this build. Notice that 1 additional software blocks are added to the Build 1 diagram (图 7) to implement this closed current loop system. The Sine Analyzer block calculates the RMS voltage and frequency of the input voltage. PFC InvRmsSqr block calculates the inverse of the square of the RMS input voltage. This calculated value together with the rectified voltage (Vrect) is used in the software block PFC\_ICMD to generate the reference current command Pfclcmd for the PFC current control loop. PFC\_ICMD block uses a 3rd input VpfcVcmd for controlling the magnitude of the reference current command. Since this software build implements only the PFC current loop (open voltage loop), this parameter VpfcVcmd needs to be varied from the CCS watch window in order to adjust the magnitude of the reference current and hence the PFC bus voltage. A two pole two zero (2p2z) controller is used to implement the current control loop. This is the 4th software block shown in 图 11 as CNTL\_2P2Z:1. Depending on the control loop requirements other control blocks such as a PI or a 3p3z controller can also be used.

As shown in [8] 11 the current loop control block is executed at a 100 KHz rate. CNTL\_2P2Z is a 2nd order compensator realized from an IIR filter structure. This function is independent of any peripherals and therefore does not require a CNF function call.

Software Overview

图 11. Build 2 Software Blocks

This 2p2z controller requires five control coefficients. These coefficients and the clamped output of the controller are stored as the elements of a structure named CNTL\_2P2Z\_CoefStruct1. The CNTL\_2P2Z block can be instantiated multiple times if the system needs multiple loops. Each instance can have separate set of coefficients. The CNTL\_2P2Z instance for the current loop uses the coefficients stored as the elements of structure CNTL\_2P2Z\_CoefStruct1. This way a second instantiation of CNTL\_2P2Z with a different structure, CNTL\_2P2Z\_CoefStruct2, can be used for PFC voltage loop control, as we will see in  $\ddagger 3.3.1.4.4$  with Build 3.

The controller coefficients can be changed directly by modifying the values for B0, B1, B2, A1, and A2 inside the structure CNTL\_2P2Z\_CoefStruct1. Alternately, the 2p2z controller can be expressed in PID form and the coefficients can be changed by changing the PID coefficients. The equations relating the five controller coefficients to the three PID gains are given below. For the current loop these P, I and D coefficients are named as: Pgain\_I, Igain\_I and Dgain\_I respectively. For the voltage loop, used in Build 3, these coefficients are named as: Pgain\_V, Igain\_V and Dgain\_V respectively. These coefficients are used in Q26 format.

The compensator block (CNTL\_2P2Z) has a reference input and a feedback input. The feedback input labeled as, Fdbk, comes from the ADC. The reference input labeled as, Ref, comes from PFC\_ICMD block as mentioned before. The z-domain transfer function for CNTL\_2P2Z is given by:

$$\frac{U(z)}{E(z)} = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{1 + a_1 z^{-1} + a_2 z^{-2}}$$

(1)

(2)

Software Overview

The recursive form of the PID controller is given by the difference equation:

$$u(k) = u(k-1) + b_0 e(k) + b_1 e(k-1) + b_2 e(k-2)$$

where

$$b_0 = K_p + K_i + K_d$$

$$b_1 = -K_p + K_i - 2K_d$$

•  $b_2 = K_d$

And the z-domain transfer function of this PID is:

$$\frac{U(z)}{E(z)} = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{1 - z^{-1}}$$

(3)

Comparing this with the general form, we can see that PID is a special case of CNTL\_2P2Z control where:  $a_1 = -1$  and  $a_2 = 0$  (4)

The MATH\_EMAVG (Exponential Moving Average) block calculates the average of the output DC bus voltage. The output from this block is used to detect overvoltage condition followed by a PWM shutdown.

### 3.3.1.4.3 Procedure

Follow the following steps to execute this build:

### 3.3.1.4.3.1 Build and Load Project

Follow the steps below to execute this build:

Follow the steps in  $\ddagger$  3.3.1.3.2 exactly as in build 1( $\ddagger$  3.3.1) except that in Step 6, select build 2 option instead of build 1. Then complete Step 6 as below:

1. Locate and inspect the following code in the main file under initialization code specific for build 2. This is where all the software blocks related to build 2 are connected in the control flow.

```

#if (INCR_BUILD == 2) // Closed Current Loop IL PFC, Open Volt Loop

// Lib Module connection tc

ADCDRV_ich_Rlt1 = 6Ipfc1;

ADCDRV_ich_Rlt2 = 6Ipfc2;

ADCDRV_ich_Rlt3 = 6Ipfc2;

ADCDRV_ich_Rlt4 = 6Ipfc4;

ADCDRV_ich_Rlt5 = 6Ipfc5;

ADCDRV_ich_Rlt7 = 6Ipfc7;

ADCDRV_ich_Rlt7 = 6Ipfc7;

ADCDRV_ich_Rlt7 = 6Ipfc7;

ADCDRV_ich_Rlt8 = 6Ipfc8;

ADCDRV_ich_Rlt8 = 6Ipfc8;

ADCDRV_ich_Rlt8 = 6Ipfc8;

ADCDRV_ich_Rlt10 = 6VL_fb;

ADCDRV_ich_Rlt11 = 6VN_fb;

// Lib Module connection to "nets"

//connect the 2P2Z co

onnections, for the inner Current Loop, Loop1

CNTL_2P22_Ref1 = 6PFCIend;

CNTL_2P22_Out1 = 6DutyA;

CNTL_2P22_Out1 = 6DutyA;

CNTL_2P22_Folbx1= 6Ipfc_1ltr;

CNTL_2P22_Coef1 = 6CNTL_2P22_CoefStruct1.b2;

block con

// Moth

Instance

MATH_EMAVG_In2=&Vbus;

MATH EMAVG Out2=&VbusAvg;

MATH_EMAVG_Multiplier2=_IQ30(0.00025);

NIL______NNO__INTS_SQR block connections

VrectRMS = (sine_mainsV.Vrms)<< 9;//Q15 --> Q24, (sine_mainsV.Vrms) is in Q15

PFC_InvRmsSqr_Out=&VinvSqr;

PFC_InvRmsSqr_Vmin0verVmax1=_IQ30(0.1956); // 80V/409V

PFC_InvRmsSqr_Vmin1=_IQ24(0.1956); // 80V/409V

// PFC ICMD block connections

PFC_ICMD_Vcmd1 = &VbusVcmd;

PFC_ICMD_VinvSqr1=&VinvSqr;

PFC_ICMD_VacRect1=&Vrect;

PFC_ICMD_Out1=&PFCIcmd;

PFC_ICMD_VmaxOverVmin1=_IQ24(3.00);

// 3.5625 <=> 285V/80V

PWMDRV 2ch UpDwnCnt Duty1 = &DutyA;

```

2. Open and inspect InterleavedPFC-DPL-ISR.asm. Notice the \_DPL\_Init and \_DPL\_ISR sections under

build 2. This is where all the macro instantiations under build 2 are done for initialization and runtime, respectively.

- - 注: Whenever you change the incremental build option in *InterleavedPFCSettings.h* always do a "Rebuild All"

- 4. Run the code by using the <F8> key, or using the Run button on the toolbar, or using Target -> Run on the menu bar.

- 5. In the watch view, add the variable *VpfcVcmd* and set it to 0.025 (=419430 in Q24). This variable sets the magnitude of the reference current command for the current control loop.

- 6. Apply an appropriate resistive load to the PFC system at the DC output. For example, a 8.0Kohm resistor of 40W rating can be used. This will provide a load of 18W at 380V bus voltage.

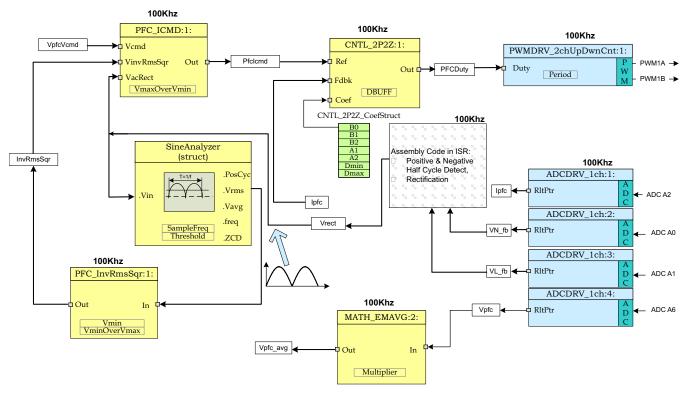

- 7. Slowly apply AC Power to the board from an isolated AC source. Monitor the DC bus voltage as the input voltage is raised slowly to 82V rms. The bus voltage now should be around 380V. Use a current probe to observe the input current. With 82V rms input, 8.0kohm resistive load and bus voltage set to 380V you should see the following waveforms. Here Ch4 is the input current, Ch1/Ch2 are the PWM outputs. With the current loop closed the input current should have the same shape of the input voltage with good power factor.

CCS watch window below shows some of the variables under Build 2 when the input AC voltage is about 82Vrms, VbusVcmd is set to 0.025, DC bus resistive load is about 8K ohm and DC bus voltage is 380V.

| .ocal (1) 🥳 Watch (1) 🔉 | 1) 🐮 Watch (1) 🗙 🕞 🥵 🥵 🍰 📑 📬 💈 |                 |      |             |  |  |

|-------------------------|--------------------------------|-----------------|------|-------------|--|--|

| Name                    | Value                          | Address         | Туре | Format      |  |  |

| (X)= Gui_Freq_Vin       | 61.0938                        | 0x0000900A@Data | int  | Q-Value(6)  |  |  |

| (X)= Gui_VrectRMS       | 80.4844                        | 0x0000900B@Data | int  | Q-Value(6)  |  |  |

| (X)= Gui_Vbus           | 380.828                        | 0x00009009@Data | int  | Q-Value(6)  |  |  |

| (X)= Gui_IrectRMS       | 0.280273                       | 0x00009010@Data | int  | Q-Value(10) |  |  |

| (X)= DutyA              | 0.2923679352                   | 0x00009046@Data | long | Q-Value(24) |  |  |

| (×)= Ipfc_fltr          | 0.01354980469                  | 0x0000904E@Data | long | Q-Value(24) |  |  |

| (×)= VbusAvg            | 0.7226557136                   | 0x00009030@Data | long | Q-Value(24) |  |  |

| (X)= Gui_PinRMS         | 23.28125                       | 0x00009084@Data | long | Q-Value(5)  |  |  |

| (×)= Vbus               | 0.7236328125                   | 0x00009054@Data | long | Q-Value(24) |  |  |

| (X)= VbusAvg            | 0.7227066755                   | 0x00009030@Data | long | Q-Value(24) |  |  |

| (×)= VL_fb              | 0.103515625                    | 0x00009052@Data | long | Q-Value(24) |  |  |

| (×)= VN_fb              | 0.2727050781                   | 0x0000907E@Data | long | Q-Value(24) |  |  |

| 👀 VbusVcmd              | 0.02499997616                  | 0x0000901E@Data | long | Q-Value(24) |  |  |

#### Software Overview

- 8. Increase *VpfcVcmd* slightly (in steps of 0.002) and observe the bus voltage settles to a higher value. Increasing *VpfcVcmd* increases the magnitude of the current reference signal and, since the PFC voltage loop is open, the bus voltage will rise. Therefore, apply caution and set the overvoltage protection threshold to 400V. This threshold parameter is labeled as VBUS\_OVP\_THRSHLD inside the file *InterleavedPFC-Settings.h*. The default value is set to 430V. Now change the input voltage or the load resistance to see the PFC operation under current control loop.

- 9. Fully halting the MCU when in real-time mode is a two-step process. With the AC input turned off wait until the DC bus capacitor is fully discharged. First, halt the processor by using the Halt button on the toolbar, or by using Target -> Halt. Then take the MCU out of real-time mode. Finally reset the MCU.

- 10. You may choose to leave Code Composer Studio running for the next exercise or optionally close CCS.

- 11. End of Exercise

### 3.3.1.4.4 Build 3: IL PFC with Closed Voltage and Current Loop

### 3.3.1.4.4.1 Objective

The objective of this build is to verify the operation of the complete IL PFC project from the CCS environment.

### 3.3.1.4.4.2 Overview

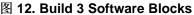

I2 shows the software blocks used in this build. Compared to build 2 in I1 this build uses an additional 2p2z control block labeled as CNTL\_2P2Z:2. This is the 2nd instantiation of the 2p2z control block in order to implement the IL PFC voltage loop control. This voltage loop controller is executed at 50kHz rate which is half the rate for current loop. The output from this control block drives the input node VpfcVcmd of the PFC\_ICMD block. This is the main difference compared to build 2 where VpfcVcmd is updated by user from CCS watch window in an open voltage loop mode.

(5)

Similar to current loop controller, this voltage loop controller, CNTL\_2P2Z:2, also requires five control coefficients. These coefficients and the clamped output of the controller are stored as the elements of a 2nd structure named CNTL\_2P2Z\_CoefStruct2. The coefficients for this controller can be changed directly by modifying the values for B0, B1, B2, A1, and A2 inside the structure CNTL\_2P2Z\_CoefStruct2, or by changing the equivalent PID gains as discussed in  $\ddagger$  3.3.1.4.

### 3.3.1.4.4.2.1 Start-Up, Inrush Current Control, and Slew-Limit

At start-up, the controller monitors the PFC DC bus voltage. When this voltage reaches a minimum level (this min level for this ILPFC EVM is set around 160Vdc) PFC action is enabled and the output DC bus slowly ramps up to the pre-set value of about 390Vdc. This output voltage level is set by the constant VBUS\_RATED\_VOLTS defined in the PFC header file *InterleavedPFC-Settings.h*. The ramp up speed is set by the parameter *VbusSlewRate* defined and implemented in the soft-start state machine task C2. This part of the software can be quickly modified to implement any other desired mode for PFC start-up.

### 3.3.1.4.4.2.2 Input Power Monitor

This ILPFC EVM has been equipped with input power monitoring feature. All the calculation for input power measurement is done inside a 10kHz ISR running the SineAnalyzer macro (图 12). This macro block takes the rectified input voltage and the rectified input current as its inputs. Then based on this information it calculates the RMS input power, RMS input voltage and RMS input current using the following equations:

$$V_{rms} = \sqrt{\left[\frac{1}{T}\int_{t}^{t+T} v^{2}(t)dt\right]} = \frac{1}{N}\sqrt{\sum_{n=1}^{N} V^{2}(n)}$$

N = T / T<sub>s</sub>

$$I_{rms} = \sqrt{\left[\frac{1}{T} \int_{t}^{t+T} f^{2}(t) dt\right]} = \frac{1}{N} \sqrt{\sum_{n=1}^{N} I^{2}(n)}$$

$$P_{rms} = \frac{1}{T} \int_{t}^{t+T} v(t) \cdot i(t) dt = \frac{1}{N} \sum_{n=1}^{N} V(n) \cdot I(n)$$

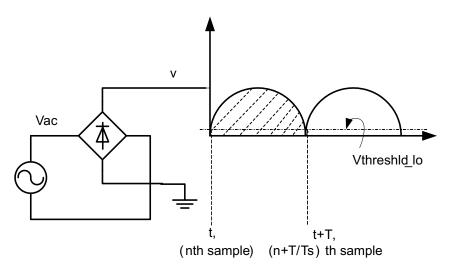

The time period T of the rectified input voltage and current is calculated by setting a low threshold voltage level for the rectified voltage signal and then by measuring the time between the consecutive points when the signal crosses this threshold level. This is illustrated in  $\mathbb{X}$  13.

图 13. RMS Input Voltage and Current Calculation Scheme

### 3.3.1.4.4.2.3 Procedure

### 3.3.1.4.4.2.4 Build and Load Project

Follow the steps below to execute this build.

Follow the steps in  $\ddagger$  3.3.1.3.1 exactly as in build 1( $\ddagger$  3.3.1) except that in Step 6 select build 3 option instead of build 1. Then complete Step 6 as below:

1. Locate and inspect the following code in the main file under initialization code specific for build 3. This is where all the software blocks related to build 3 are connected in the control flow.

```

TEXAS

INSTRUMENTS

```

```

#if (INCR_BUILD == 3) // Closed Current Loop & closed volt loop IL PFC

// Lib Module connection to "nets"

ADCDRV_1ch_Rlt1 = &Ipfc1;

ADCDRV_1ch_R1t2 = &Ipfc2;

ADCDRV 1ch Rlt3 = &Ipfc3;

ADCDRV_1ch_R1t4 = &Ipfc4;

ADCDRV_1ch_Rlt5 = &Ipfc5;

ADCDRV 1ch Rlt6 = &Ipfc6;

ADCDRV_1ch_Rlt7 = &Ipfc7;

ADCDRV 1ch Rlt8 = & Ipfc8;

ADCDRV_1ch_Rlt9 = &Vbus;

ADCDRV_1ch_R1t10 = &VL_fb;

ADCDRV 1ch Rlt11 = &VN fb;

//connect the 2P2Z connections, for the inner Current Loop, Loop1

CNTL 2P2Z Ref1 = &PFCIcmd;

CNTL 2P2Z Out1 = &DutyA;

CNTL_2P2Z_Fdbk1= &Ipfc_fltr;

CNTL 2P2Z Coef1 = &CNTL 2P2Z CoefStruct1.b2;

//connect the 2P2Z connections, for the outer Voltage Loop, Loop2

CNTL_2P2Z_Ref2 = &VbusTargetSlewed;

CNTL 2P2Z Out2 = &VbusVcmd;

CNTL 2P2Z Fdbk2= &Vbus;

CNTL_2P2Z_Coef2 = &CNTL_2P2Z_CoefStruct2.b2;

// Math avg block connections - Instance 2

MATH EMAVG In2=&Vbus;

MATH EMAVG Out2=&VbusAvg;//Average PFC bus volt calculated for OV protection

MATH_EMAVG_Multiplier2=_IQ30(0.00025);

// INV RMS SQR block connections

VrectRMS = (sine mainsV.Vrms) << 9;//Q15 --> Q24, (sine mainsV.Vrms) is in Q15

PFC InvRmsSqr In1=&VrectRMS;

PFC_InvRmsSqr_Out1=&VinvSqr;

PFC_InvRmsSqr_VminOverVmax1=_IQ30(0.1956); // 80V/409V

PFC_InvRmsSqr_Vmin1=_IQ24(0.1956);

// PFC_ICMD block connections

PFC ICMD Vcmd1 = &VbusVcmd;

PFC ICMD VinvSqr1=&VinvSqr;

PFC_ICMD_VacRect1=&Vrect;

PFC ICMD Out1=&PFCIcmd;

// 3.5625 <=> 285V/80V

PFC_ICMD_VmaxOverVmin1=_IQ24(3.00);

PWMDRV 2ch UpDwnCnt Duty1 = &DutyA;

```

- 2. Open and inspect *InterleavedPFC-DPL-ISR.asm*. Notice the \_DPL\_Init and \_DPL\_ISR sections under build 3. This is where all the macro instantiations under build 3 are done for initialization and runtime, respectively.

- 3. Select the Incremental build option as 3 in the *InterleavedPFC-Settings.h* file. Then follow steps in 节 3.3.1.3.3 and 节 3.3.1.3.5 as in build 1 in order to run the code. When all these steps are completed you should now be at the start of Main().

- 注: Whenever you change the incremental build option in *InterleavedPFC-Settings.h* always do a "Rebuild All"

- 4. Run the code by using the <F8> key, or using the Run button on the toolbar, or using Target -> Run on the menu bar.

- 5. In the watch view, add the variables *VbusTargetSlewed*, *Vbus* and set the Q-format to Q24. These variables represent the p.u. reference bus voltage and the feedback bus voltage respectively (normalized or per unit values). These will slowly increase to the setpoint value as the PFC starts up when AC power is applied.

- 6. Apply an appropriate resistive load to PFC output. For example, a 8.0Kohm resistor of 40W rating can be used. This will provide a load of about 20W at 390V bus voltage. Configure the isolated AC source to output 120V, 60Hz, AC voltage output. Use a voltmeter to monitor the DC bus voltage. Turn on the AC source output for 120Vrms. When the DC bus voltage reaches 160V, PFC action will start and the bus voltage will slowly increase to about 390V. Notice that VbusTargetSlewed and Vbus variables on

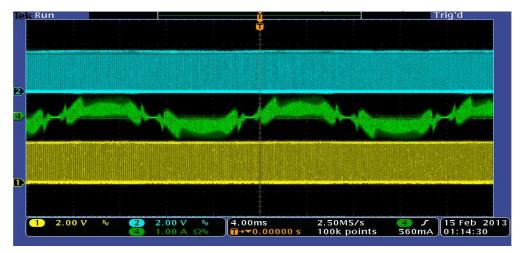

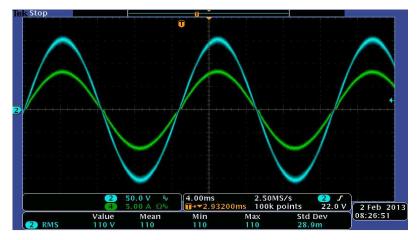

the watch window show a value of about 0.7414 (=390/526) when the Q format is set to Q24. The maximum bus voltage set by the Vbus sense resistors is about 526V that corresponds to maximum ADC input of 3.3V. Therefore, the normalized or per unit value will be about 0.7414 when the actual bus voltage is 390Vdc. CCS watch window below shows some of the variables under Build 3 when the input AC voltage is about 120Vrms, DC bus resistive load is about 8K ohm and DC bus voltage is about 390V. The variable "pfc\_on\_flag" is set to 1 when the soft-start is complete and PFC bus voltage reaches the desired set point. Use an oscilloscope with voltage and current probes to observe the input voltage and input current. With 110Vrms input, 277 ohm resistive load and bus voltage set to 390V you should see the waveforms shown below. Here Ch2 is the input voltage and Ch4 is the input current. Change the input voltage (100Vrms~260Vrms) or the load resistance (0~550W @110Vin, or, 0~700W @220Vin) to see the PFC operation under closed current and voltage control loop.

| Local (1) 🚭 Watch (1) 🛛 |               |                 |      | 🕞 🛛 🗙 💥 🤣 🥙 🏦 🖂 🖓 🖓 |

|-------------------------|---------------|-----------------|------|---------------------|

| Name                    | Value         | Address         | Туре | Format              |

| (X)= Gui_Freq_Vin       | 60.1563       | 0x0000900A@Data | int  | Q-Value(6)          |

| (X)= Gui_VrectRMS       | 119.969       | 0x0000900B@Data | int  | Q-Value(6)          |

| (X)= Gui_Vbus           | 390.359       | 0x00009009@Data | int  | Q-Value(6)          |

| (X)= Gui_IrectRMS       | 0.194336      | 0x00009010@Data | int  | Q-Value(10)         |

| (X)= DutyA              | 0.1812707782  | 0x00009042@Data | long | Q-Value(24)         |

| (X)= VbusAvg            | 0.7408962846  | 0x0000902C@Data | long | Q-Value(24)         |

| (X)= Gui_PinRMS         | 22.53125      | 0x00009084@Data | long | Q-Value(5)          |

| (x)= Vbus               | 0.7395019531  | 0x00009050@Data | long | Q-Value(24)         |

| (×)= VbusAvg            | 0.7409095764  | 0x0000902C@Data | long | Q-Value(24)         |

| (×)= VbusVcmd           | 0.02482783794 | 0x00009020@Data | long | Q-Value(24)         |

| (X)= VbusTargetSlewed   | 0.7410829067  | 0x0000907E@Data | long | Q-Value(24)         |

| (X)= pfc_on_flag        | 1             | 0x0000901B@Data | int  | Natural             |

图 14. IL PFC Input Voltage and Current at 550W Load and 110Vrms Input

- 7. Fully halting the MCU when in real-time mode is a two-step process. With the AC input turned off wait until the DC bus capacitor is fully discharged. First, halt the processor by using the Halt button on the toolbar, or by using Target -> Halt. Then take the MCU out of real-time mode. Finally reset the MCU.

- 8. You may choose to leave Code Composer Studio running for the next exercise or optionally close CCS.

- 9. End of Exercise

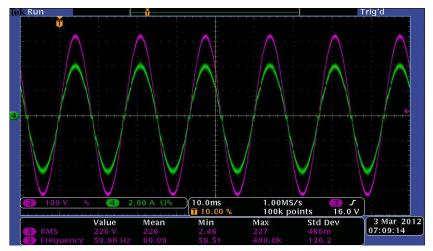

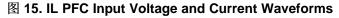

### 3.3.1.4.4.3 Additional Test Results

(1) Ch3 -Vin, Ch4-lin, Vrms=230V, Vbus=390V, Pout=700W

### 4 References

For more information, please refer to the following guides:

**ILPFC-GUI\_QSG**— A quick-start guide for quick demo of the ILPFC EVM using a GUI interface.

..\controlSUITE\development\_kits\ILPFC\~Docs\ILPFC-GUI\_QSG.pdf

**ILPFC\_Rel-1.0-HWdevPkg**— A folder containing various files related to the Piccolo-B controller card schematics and the IL PFC schematic.

..\controlSUITE\development\_kits\ILPFC\ILPFC\_HWDevPkg

F28xxx User's Guides— http://www.ti.com/f28xuserguides

### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用 的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知 识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包 含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进 行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他 法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任 何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信 息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许 可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、 无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2017 德州仪器半导体技术(上海)有限公司