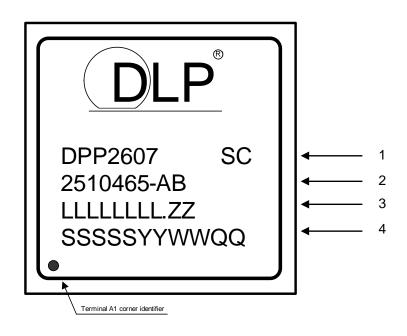

**DLPC2607**

ZHCSC07E - DECEMBER 2013-REVISED MARCH 2019

# DLPC2607 低功耗 DLP® 显示控制器

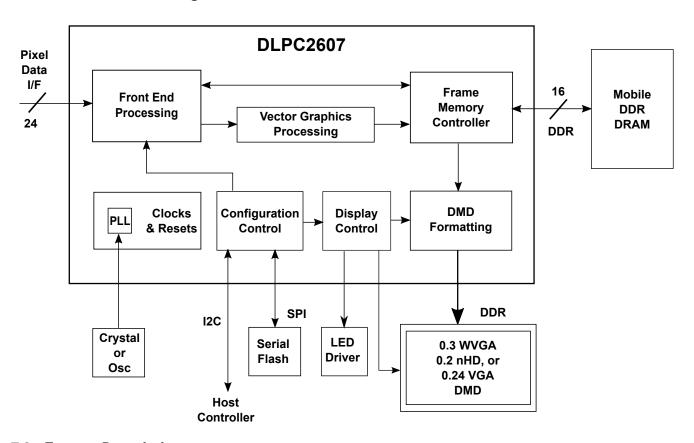

## 1 特性

- 支持 0.2 nHD、0.24 VGA 和 0.3 WVGA DMD 的可靠运行

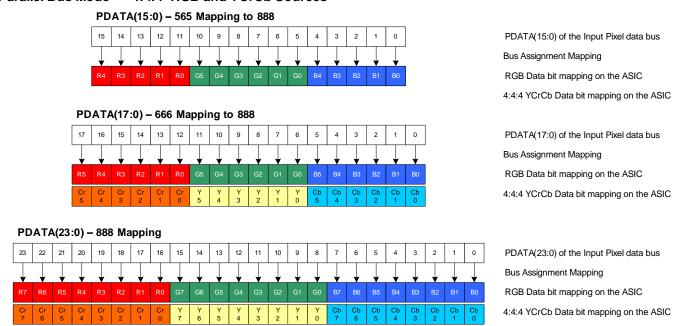

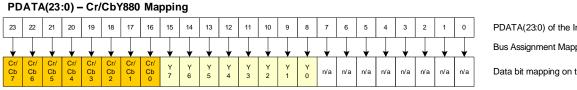

- 多模式,24 位输入像素接口:

- 支持并行或 BT656 总线协议

- 支持从 QVGA 到 WVGA 的输入大小

- 支持 1 至 60Hz 的帧速率

- 支持高达 33.5MHz 的像素时钟

- 支持竖排和横排方向

- 支持8、16、18和24位总线选项

- 支持3输入色彩位深选项:

- RGB888, YCrCb888

- RGB666, YCrCb666

- RGB565, 4:2:2 YCrCb

- 像素数据处理

- 图像大小调整(缩放)

- 帧速率转换

- 色彩坐标调整

- 自动增益控制

- 可编程后期色彩校正 (Degamma)

- 空间-时间复用(抖动显示)

- 视频处理支持:

- 色彩空间转换

- 4:2:2 至 4:4:4 色度插值

- 场缩放去隔行

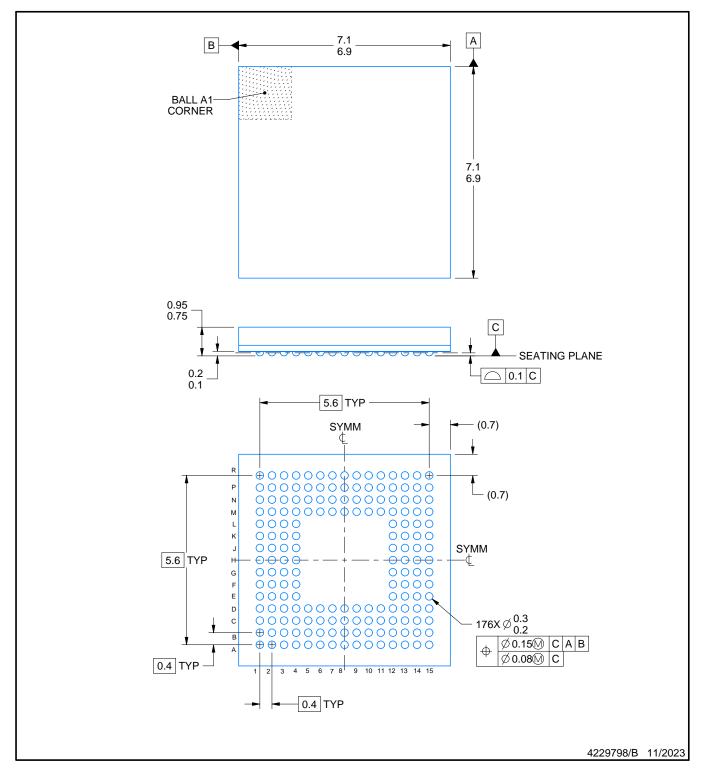

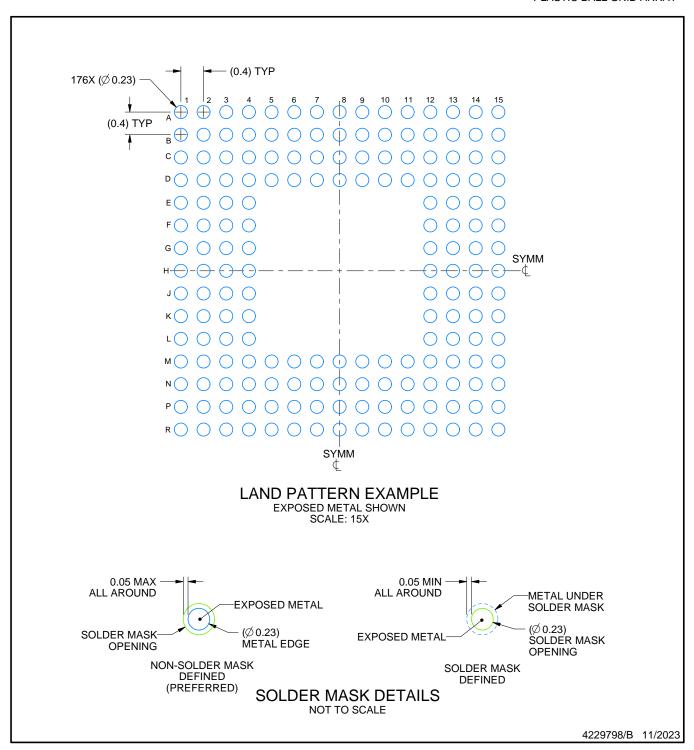

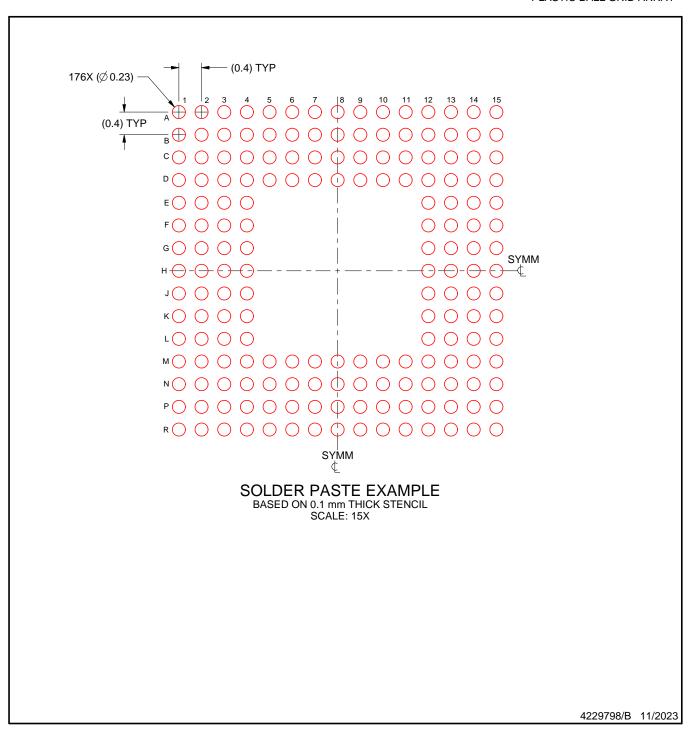

- 封装在 176 引脚, 0.4mm 焊球间距, 极细间距球 状引脚栅格阵列 (VFBGA) 封装

- 支持外部存储器:

- 166MHz 移动 DDR SDRAM

- 33.3MHz 串行闪存

- WVGA, VGA 和 nHD DMD 显示支持

- DMD 位平面生成和格式化

- 可编程位平面显示排序器(控制发光二极管 (LED) 使能和 DMD 加载)

- 76.2MHz 双倍数据速率 (DDR) DMD 接口 (I/F)

- 针对微镜的脉宽调制 (PWM):

- 断电时的自动 DMD 停止

- DMD 24 位位深

- 系统控制:

- 器件配置的 I<sup>2</sup>C 控制

- 可编程 Splash 屏幕

- 可编程 LED 电流控制

- DMD 电源和微镜驱动器控制

- DMD 水平和垂直显示图像抖动

- 显示图像旋转

- 基于闪存的配置批处理文件

- I/F 睡眠静止图像省电模式

- 测试支持:

- 内置测试信号生成

- 支持边界扫描测试的 JTAG

### 2 应用范围

- 嵌入式移动投影

- 智能手机

- 平板电脑

- 摄像机

- 笔记本电脑

- 移动附件

- 可佩戴(近眼)显示

- 电池供电投影仪

## 3 说明

DLPC2607 是一款用于电池 供电™显示应用的低功耗 DLP 数字 控制器中运行。该控制器支持 0.3 WVGA、0.24 VGA 和 0.2 nHD DMD 的可靠运行。DLPC2607 控制器提供了用于连接系统电子产品和 DMD 的便捷多功能接口,从而能够实现小尺寸、低功耗显示器。

## 器件信息<sup>(1)</sup>

| 器件型号     | 封装          | 封装尺寸(标称值)       |  |  |

|----------|-------------|-----------------|--|--|

| DLPC2607 | VFBGA (176) | 7.00mm × 7.00mm |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

# 目录

| 1 | 特性1                                                     |    | 7.2 Functional Block Diagram                | . 23 |

|---|---------------------------------------------------------|----|---------------------------------------------|------|

| 2 | 应用范围 1                                                  |    | 7.3 Feature Description                     | . 23 |

| 3 | 说明1                                                     |    | 7.4 Programming                             | . 25 |

| 4 | 修订历史记录                                                  | 8  | Application and Implementation              | 27   |

| 5 | Pin Configuration and Functions 5                       |    | 8.1 Application Information                 | . 27 |

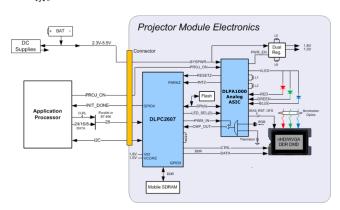

| 6 | Specifications                                          |    | 8.2 Typical Application                     | . 27 |

| U | 6.1 Absolute Maximum Ratings                            | 9  | Power Supply Recommendations                | 32   |

|   | 6.2 ESD Ratings                                         |    | 9.1 System Power Considerations             |      |

|   | 6.3 Recommended Operating Conditions                    |    | 9.2 System Power-Up and Power-Down Sequence |      |

|   | 6.4 Thermal Information                                 |    | 9.3 System Power I/O State Considerations   | . 34 |

|   | 6.5 Typical Current and Power Dissipation               |    | 9.4 Power-Up Initialization Sequence        | . 34 |

|   | 6.6 I/O Characteristics                                 |    | 9.5 Power-Good (PARK) Support               | . 35 |

|   | 6.7 Internal Pullup and Pulldown Characteristics 14     | 10 | Layout                                      |      |

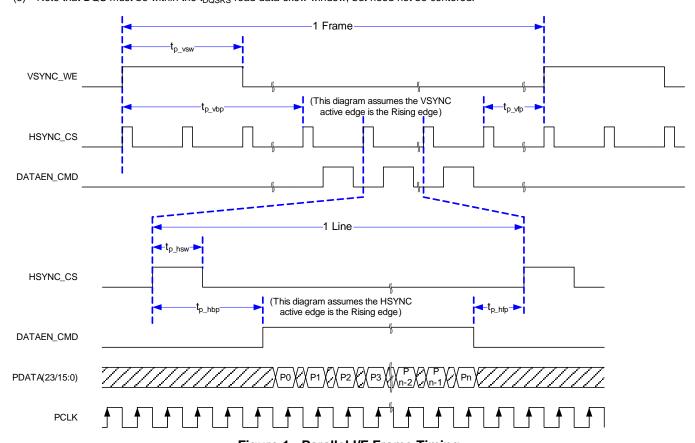

|   | 6.8 Parallel I/F Frame Timing Requirements              |    | 10.1 Layout Guidelines                      | . 36 |

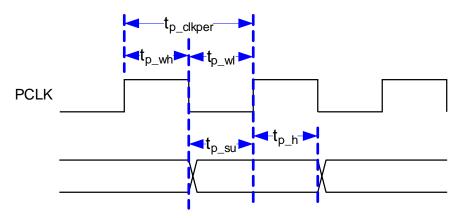

|   | 6.9 Parallel I/F General Timing Requirements            |    | 10.2 Layout Example                         |      |

|   | 6.10 Parallel I/F Maximum Parallel Interface Horizontal | 11 | 器件和文档支持                                     |      |

|   | Line Rate                                               |    | 11.1 器件支持                                   |      |

|   | 6.11 BT.656 I/F General Timing Requirements 17          |    | 11.2 社区资源                                   |      |

|   | 6.12 100- to 120-Hz Operational Limitations             |    | 11.3 商标                                     | . 44 |

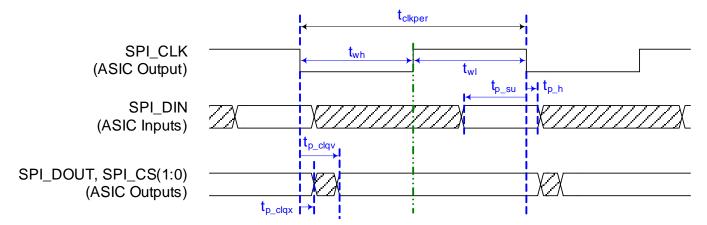

|   | 6.13 Flash Interface Timing Requirements                |    | 11.4 静电放电警告                                 | . 44 |

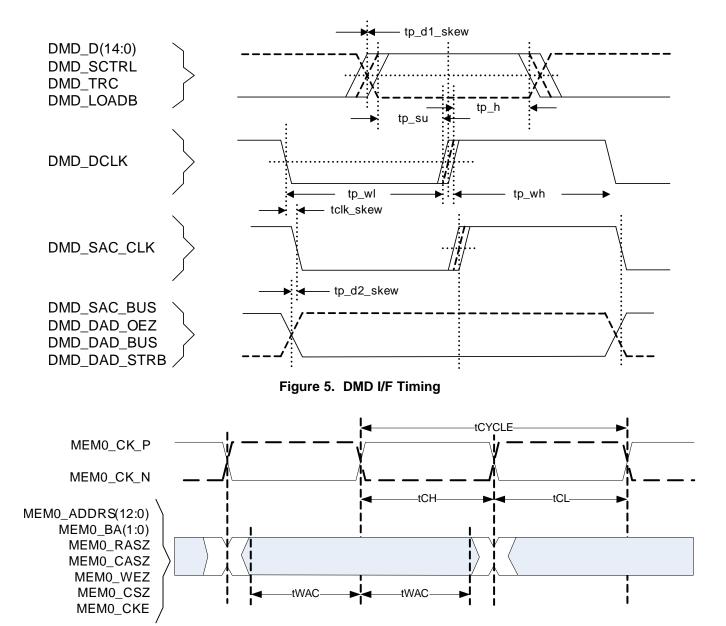

|   | 6.14 DMD Interface Timing Requirements                  |    | 11.5 术语表                                    | . 44 |

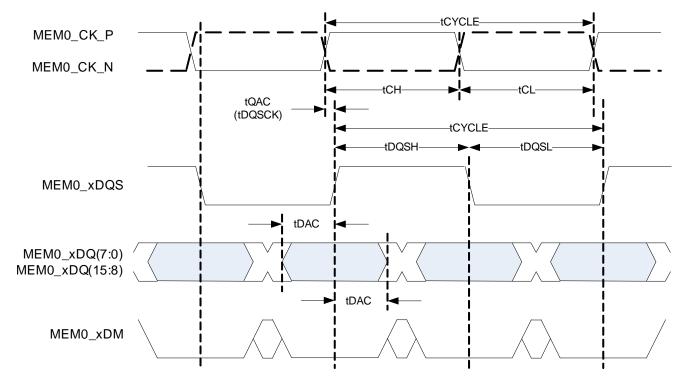

|   | 6.15 mDDR Memory Interface Timing Requirements 19       | 12 | 机械、封装和可订购信息                                 | 44   |

| 7 | Detailed Description23                                  |    | 12.1 封装选项附录                                 |      |

|   | 7.1 Overview                                            |    |                                             |      |

|   |                                                         |    |                                             |      |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Revision D (May 2017) to Revision E

# Page

| • | 已更改 将标题从"DLPC2607 DLP PICO 处理器 2607 ASIC"更改为"DLPC2607 低功耗 DLP® 显示控制器"                                               | . 1 |

|---|---------------------------------------------------------------------------------------------------------------------|-----|

| • | Added ZVB Package Bottom View                                                                                       | 5   |

| • | Changed to "Add external pullup or pulldown resistors as needed to these signals to avoid floating inputs"          | . 5 |

| • | Changed PAD1000 to DLPA1000                                                                                         | 5   |

| • | Changed to "Establish this setting"                                                                                 | 5   |

| • | Changed "low a minimum" to "low to a minimum"                                                                       | 5   |

| • | Changed "Should be pulled up to" to "Pull up to"                                                                    | 5   |

| • | Changed "Unused inputs should be pulled down" to "Pull unused inputs"                                               | 6   |

| • | Added DMD INTERFACE pin descriptions                                                                                | . 7 |

| • | Added SDRAM INTERFACE pin descriptions                                                                              | 8   |

| • | Changed "It should be connected" to "Connect".                                                                      | 9   |

| • | Changed globally "Should be left open or unconnected for typical use." to "Leave open or unconnected for typical    |     |

|   | use."                                                                                                               | 10  |

| • | Changed globally "An external pullup should not be applied to this pin" to "Do not apply an external pullup to this | 40  |

|   | pin"                                                                                                                |     |

| • | Swapped all values under I <sub>OH</sub> and I <sub>OL</sub>                                                        |     |

| • | Changed "that should be applied" to "can safely be applied"                                                         | 14  |

| • | Changed "that should be applied" to "can safely be applied"                                                         | 14  |

| • | Changed "OHand OL" to VOH and VOL to clarify meaning                                                                | 14  |

| • | Changed "VCCIO =" to "VCCIO (V)"                                                                                    |     |

| • | Changed "MAX Supported" to "Maximum Parallel Interface"                                                             | 16  |

# 修订历史记录 (接下页)

| • | Changed Changed "BT.565" to "BT.656"                                                                                                                                                                                                                                                                                                                    | 17 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Added link to ITU-R BT.656 specification                                                                                                                                                                                                                                                                                                                | 17 |

| • | Changed "NOTE:" to "The table below"                                                                                                                                                                                                                                                                                                                    | 17 |

| • | Deleted "Note that"                                                                                                                                                                                                                                                                                                                                     | 17 |

| • | Changed f <sub>clock</sub> min                                                                                                                                                                                                                                                                                                                          | 18 |

| • | Changed t <sub>p clkper</sub> min and max                                                                                                                                                                                                                                                                                                               | 18 |

| • | Changed "should support" to "supports"                                                                                                                                                                                                                                                                                                                  | 25 |

| • | Changed "Thus, those pins should be tied" to "Tie these pins"                                                                                                                                                                                                                                                                                           | 26 |

| • | Changed "1.8-, 2.5-, or 3.3-V" to "1.8 V, 2.5 V, or 3.3 V"                                                                                                                                                                                                                                                                                              | 26 |

| • | Changed "the ASIC only supports periodic sources" to "the ASIC supports periodic sources only"                                                                                                                                                                                                                                                          | 27 |

| • | Changed "multi media" to "multimedia"                                                                                                                                                                                                                                                                                                                   | 27 |

| • | Changed Device Functional Modes to System Functional Modes and moved to correct position                                                                                                                                                                                                                                                                | 27 |

| • | Added Reference to TSTPT_6 for Crystal nominal frequency                                                                                                                                                                                                                                                                                                | 28 |

| • | Changed "ASIC, and the PLL_REFCLK_O pins hould be left unconnected" to "ASIC. Leave the PLL_REFCLK_O pins unconnected"                                                                                                                                                                                                                                  | 29 |

| • | Changed "The benefit of an oscillator is that it can be made to provide a spread-spectrum clock that reduces EMI." to "An oscillator that provides a spread-spectrum clock reduces EMI."                                                                                                                                                                | 29 |

| • | Changed "can only accept" to "accepts"                                                                                                                                                                                                                                                                                                                  | 29 |

| • | Added kHz                                                                                                                                                                                                                                                                                                                                               | 29 |

| • | Changed several items in Table 7                                                                                                                                                                                                                                                                                                                        | 29 |

| • | Changed " the ODM's own risk" to "the risk of the ODM"                                                                                                                                                                                                                                                                                                  | 29 |

| • | Changed " Layout guidelines should be followed" to "Follow the layout guidelines"                                                                                                                                                                                                                                                                       | 29 |

| • | Changed "To complete DLP system is requiered" to "The DLP system requires"                                                                                                                                                                                                                                                                              | 29 |

| • | Changed "The optical engine that has the LED packages and the DMD mounted to it is typically supplied by an optical OEM who specializes in designing optics for DLP projectors." to "An optical OEM that specializes in designing optics for DLP projectors typically supplies the optical engine that has the LED packages and the DMD mounted to it." | 29 |

| • | Deleted "Note that"                                                                                                                                                                                                                                                                                                                                     | 30 |

| • | Changed "this allows these inputs to be driven high" to "This protection allows the device to drive these inputs high"                                                                                                                                                                                                                                  | 30 |

| • | Changed                                                                                                                                                                                                                                                                                                                                                 | 30 |

| • | Changed "All I/O power should remain" to "Ensure that all I/O power remains"                                                                                                                                                                                                                                                                            | 32 |

| • | Changed "is defined" to "operates as"                                                                                                                                                                                                                                                                                                                   | 35 |

| • | Changed "should alert" to "alerts"                                                                                                                                                                                                                                                                                                                      | 35 |

| • | Changed "Note that the reference clock should continue to run and RESET should remain" to "The reference clock continues to run. RESET remains"                                                                                                                                                                                                         | 35 |

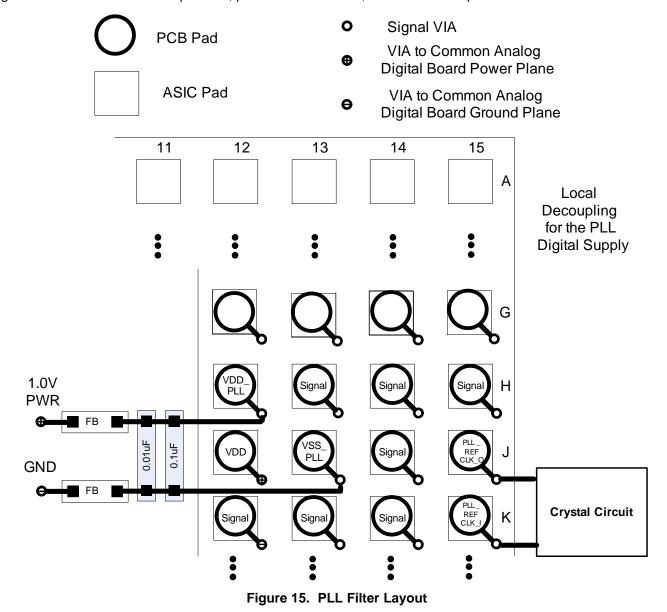

| • | Changed "At a minimum, VDD_PLL power and VSS_PLL ground pins should be isolated" to "Isolate VDD_PLL power and VSS_PLL ground pins"                                                                                                                                                                                                                     | 36 |

| • | Changed "It is important that the quiet ground and power are treated like analog signals" to "The ground and power domains are analog signals, and should be treated as such to achieve minimum noise."                                                                                                                                                 | 36 |

| • | Changed "The power and ground traces should be as short as possible" to "Ensure that the power and ground traces are as short as possible"                                                                                                                                                                                                              | 36 |

| • | Changed "and should not be expected" to "so do not expect them"                                                                                                                                                                                                                                                                                         |    |

| • | Changed "they should be" to "ensure they are"                                                                                                                                                                                                                                                                                                           |    |

| • | Changed "should be split" to "Split the"                                                                                                                                                                                                                                                                                                                |    |

| • | Changed "In addition, the SPICLK trace should be" to "Make the SPICLK trace"                                                                                                                                                                                                                                                                            |    |

| • | Changed "should be split" to "Split the"                                                                                                                                                                                                                                                                                                                |    |

|   | Changed "In addition, the SPIDOLIT trace should be" to "Make the SPIDOLIT trace"                                                                                                                                                                                                                                                                        |    |

#

Changed "on their way back" to "on the return"

Changed "They should then share" to "Make sure they share"

Changed "Variation from these recommendations may also work, but should be confirmed with PCB signal integrity

Changed "should take" to "takes" 40

Changed "should take" to "takes" 40

Changed "Specifically ... should be terminated" to "Terminate"

Changed "Specifically ... should be terminated" to "Terminate"

Changed "kept" to "maintained to a length of"

Changed "should" to "does"

## Changes from Revision C (November 2015) to Revision D

Page

# Changes from Revision B (January 2014) to Revision C

Page

## Changes from Revision A (December 2013) to Revision B

Page

• 删除了产品预览横幅 ...... 1

# Changes from Original (December 2013) to Revision A

Page

- Corrected columns for I<sub>OH</sub> and I<sub>OL</sub> in I/O Characteristics

Updated B38 I/O Type value for V<sub>OH</sub> (min) in I/O Characteristics

14

- Added additional table notes to I/O Characteristics

Added table note to Internal Pullup and Pulldown Characteristics

Corrected device reference to DLPC2607 in the notes for mDDR Memory Interface Timing Requirements

19

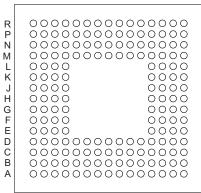

# 5 Pin Configuration and Functions

#### ZVB Package 176-Pin NFBGA Bottom View

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

## Pin Functions (1)

| PIN               |                                                          | I/O            |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------------|----------------------------------------------------------|----------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME              | NO.                                                      | POWER TYPE     |     | CLOCK SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| DEVICE INITIALIZA | DEVICE INITIALIZATION AND REFERENCE CLOCK <sup>(1)</sup> |                |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| RESETZ            | J14                                                      | VCC18          | I1  | Async        | DLPC2607 power-on reset. Self-configuration starts when a low-to-high transition is detected on this pin. All ASIC power and clocks must be stable before this reset is de-asserted (hysteresis buffer). Note that the following seven signals tri-state while RESET is asserted: DMD_PWR_EN, LEDDVR_ON, LED_SEL_0,LED_SEL_1, SPICLK, SPIDOUT, SPICSZO Add external pullup or pulldown resistors as needed to these signals to avoid floating inputs. |  |  |  |  |  |

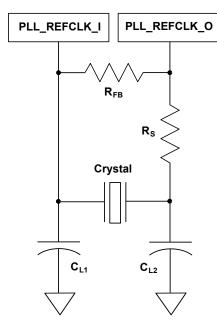

| PLL_REFCLK_I      | K15                                                      | \(CC40 (files) | 14  | N/A          | Reference clock crystal input. If an external oscillator is used in place of a crystal, then use this pin as the oscillator Input.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| PLL_REFCLK_O      | J15                                                      | VCC18 (filter) | O14 | N/A          | Reference clock crystal return. If an external oscillator is used in place of a crystal, then leave this pin unconnected (floating).                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| FLASH INTERFAC    | E <sup>(2)</sup>                                         |                |     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| SPICLK            | A4                                                       |                | O24 | N/A          | Clock for the external SPI device or devices                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| SPIDIN            | B4                                                       |                | 12  | SPICLK       | Serial data input from the external SPI device or devices                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| SPICSZ0           | A5                                                       | VCC_FLSH       | O24 | SPICLK       | Chip select 0 output for the external SPI flash device. Active low                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| SPICSZ1           | C6                                                       | 700_12011      | O24 | SPICLK       | Chip select 1 output for the external SPI DLPA1000 device. Active low                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SPIDOUT           | C5                                                       |                | O24 | SPICLK       | Serial data output to the external SPI device or devices. This pin sends address and control information as well as data when programming                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| MAIN VIDEO DATA   | AND CO                                                   | NTROL          |     | ,            |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

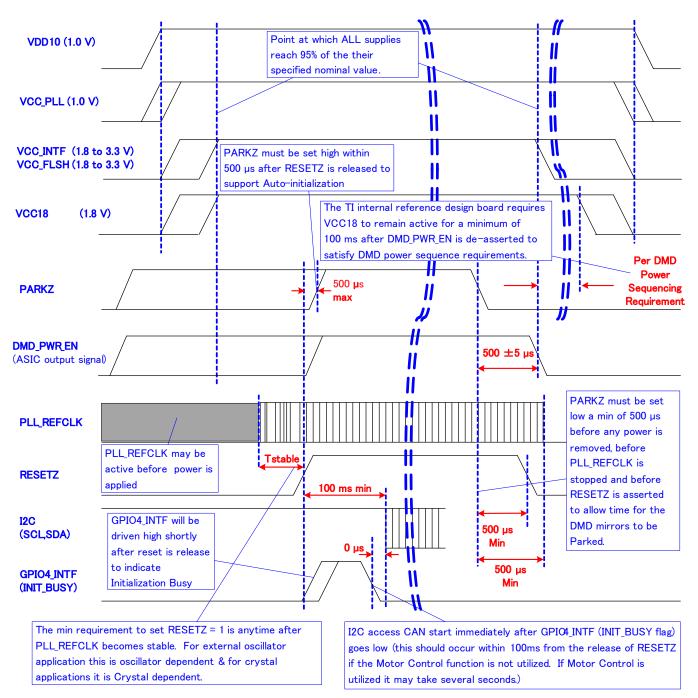

| PARK              | B8                                                       | VCC_ INTF      | 13  | Async        | DMD park control (active low) is set high to enable typical operation. Establish this setting prior to releasing RESET, or within 500 µs after releasing RESET. It should be set low to a minimum of 500 µs before any power is to be removed from the DLPC2607 (hysteresis buffer).                                                                                                                                                                  |  |  |  |  |  |

| LED_ENABLE        | A11                                                      | VCC_ INTF      | 13  | Async        | LED enable (active high input). A logic low on this signal forces LEDDRV_ON low and LED_SEL(1:0) = b00. These signals are enabled 100 ms after LED_ENABLE transitions from low to high (hysteresis buffer).                                                                                                                                                                                                                                           |  |  |  |  |  |

| DBIC_CSZ          | B10                                                      | VCC_ INTF      | 13  | SCL          | Unused/reserved: Pull up to VCC_INTF.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SCL               | A10                                                      | VCC_INTF       | B38 | N/A          | l <sup>2</sup> C clock (hysteresis buffer) bidirectional, open-drain signal. An external pullup is required. No l <sup>2</sup> C activity is permitted for a minimum of 100 ms afte PARK and RESET are set high.                                                                                                                                                                                                                                      |  |  |  |  |  |

| SDA               | C10                                                      | VCC_ INTF      | B38 | SCL          | l <sup>2</sup> C data (hysteresis buffer) bidirectional, open-drain signal. An external pullup is required.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

<sup>(1)</sup> Each device connected to the serial peripheral interface (SPI) bus must be operated off VCC\_FLSH

<sup>(2)</sup> Each device connected to the SPI bus must be operated off VCC\_FLSH

| PIN               |         | I/O       |      |                          |                                                                                                                                                                                                                                                                                                                                           |                                                                           |  |

|-------------------|---------|-----------|------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| NAME              | NO.     | POWER     | TYPE | CLOCK SYSTEM DESCRIPTION |                                                                                                                                                                                                                                                                                                                                           | PTION                                                                     |  |

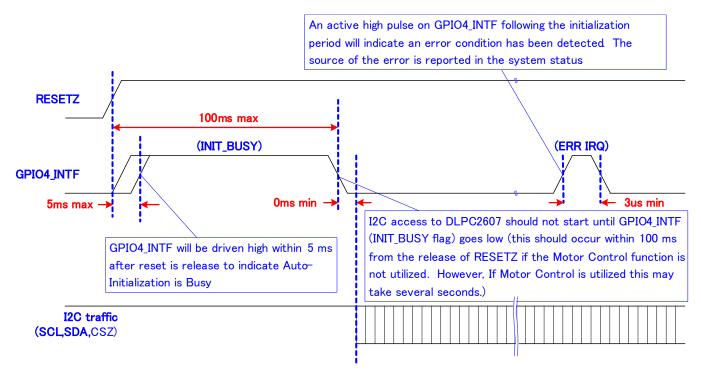

| GPIO4_INTF        | C9      | VCC_INTF  | B34  | Async                    | General purpose I/O 4 (hysteresis buffer). Primary usage is to indicate when auto-initialization is complete (also referred to as INIT-DONE, which is when GPIO4 transitions high then low following release of RESET) and to flag a detected error condition in the form of a logic high, pulsed Interrupt flag subsequent to INIT-DONE. |                                                                           |  |

| GPIO5_INTF        | В9      | VCC_ INTF | B34  | Async                    | General purpose I/O 5 (hysteresis buffer motor control with a sensor, this pin is a position sensor. For applications that us sensor, configure this pin with an output                                                                                                                                                                   | in input that is connected to the motor se non-focus motor control with a |  |

| MAIN VIDEO DATA   | AND CON | ITROL     |      |                          | PARALLEL RGB MODE                                                                                                                                                                                                                                                                                                                         | BT.656 I/F MODE                                                           |  |

| PCLK (Hysteresis) | D13     | VCC_INTF  | 13   | N/A                      | Pixel clock (3)                                                                                                                                                                                                                                                                                                                           | Pixel clock (3)                                                           |  |

| PDM_CVS_TE        | H15     | VCC_ INTF | B34  | ASYNC                    | Parallel data mask (4)                                                                                                                                                                                                                                                                                                                    | Unused (5)                                                                |  |

| VSYNC_WE          | H14     | VCC_ INTF | 13   | ASYNC                    | Vsync <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                      | Unused <sup>(5)</sup>                                                     |  |

| HSYNC_CS          | H13     | VCC_ INTF | 13   | PCLK                     | Hsync <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)                                                                |  |

| DATEN_CMD         | G15     | VCC_ INTF | 13   | PCLK                     | Data valid <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                 | Unused (5)                                                                |  |

| PDATA[0]          | G14     | VCC_ INTF | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Data0 (7)                                                                 |  |

| PDATA[1]          | G13     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Data1 (7)                                                                 |  |

| PDATA[2]          | F15     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Data2 (7)                                                                 |  |

| PDATA[3]          | F14     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Data3 (7)                                                                 |  |

| PDATA[4]          | F13     | VCC_INTF  | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Data4 (7)                                                                 |  |

| PDATA[5]          | E15     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Data5 (7)                                                                 |  |

| PDATA[6]          | E14     | VCC_INTF  | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Data6 (7)                                                                 |  |

| PDATA[7]          | E13     | VCC_INTF  | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Data7 (7)                                                                 |  |

| PDATA[8]          | D15     | VCC_ INTF | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Unused (5)                                                                |  |

| PDATA[9]          | D14     | VCC_INTF  | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Unused (5)                                                                |  |

| PDATA[10]         | C15     | VCC_INTF  | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused (5)                                                                |  |

| PDATA[11]         | C14     | VCC_ INTF | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Unused <sup>(5)</sup>                                                     |  |

| PDATA[12]         | C13     | VCC_INTF  | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused (5)                                                                |  |

| PDATA[13]         | B15     | VCC_INTF  | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused (5)                                                                |  |

| PDATA[14]         | B14     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused (5)                                                                |  |

| PDATA[15]         | A15     | VCC_ INTF | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Unused (5)                                                                |  |

| PDATA[16]         | A14     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused (5)                                                                |  |

| PDATA[17]         | B13     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused (5)                                                                |  |

| PDATA[18]         | A13     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused <sup>(5)</sup>                                                     |  |

| PDATA[19]         | C12     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused <sup>(5)</sup>                                                     |  |

| PDATA[20]         | B12     | VCC_ INTF | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Unused <sup>(5)</sup>                                                     |  |

| PDATA[21]         | A12     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused <sup>(5)</sup>                                                     |  |

| PDATA[22]         | C11     | VCC_ INTF | 13   | PCLK                     | Data (7)                                                                                                                                                                                                                                                                                                                                  | Unused <sup>(5)</sup>                                                     |  |

| PDATA[23]         | B11     | VCC_ INTF | 13   | PCLK                     | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                       | Unused (5)                                                                |  |

- Pixel clock capture edge is software programmable.

Data mask is optional for parallel bus operation. If unused, pull to ground through a resistor.

Pull unused inputs to ground through an external resistor.

VSYNC, HSYNC, and data valid polarity is software programmable.

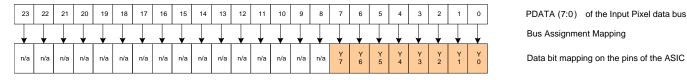

PDATA(23:0) bus mapping is pixel format and source mode dependent.

| PIN NAME NO.  |     | I/O        |             | OL OOK OVOTTER                                                                                                                                                                         | DESCRIPTION                                                                                                                                           |  |  |

|---------------|-----|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               |     | POWER TYPE |             | CLOCK SYSTEM                                                                                                                                                                           |                                                                                                                                                       |  |  |

| DMD INTERFACE |     |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D0        | M15 |            |             | DMD_DCLK                                                                                                                                                                               | DMD Data Pins. DMD Data pins are double data rate (DDR) signals that are                                                                              |  |  |

| DMD_D1        | N14 |            |             |                                                                                                                                                                                        | clocked on both edges of DMD_DCLK. All 15 DMD data signals are use to interface to the WVGA and VGA DMDs;                                             |  |  |

| DMD_D2        | M14 |            |             |                                                                                                                                                                                        | however, only 12 of the 15 are used to interface to an nHD DMD.                                                                                       |  |  |

| DMD_D3        | N15 |            |             |                                                                                                                                                                                        | The standard nHD interconnect is to utilize pins DMD_D(11:0). However, DMD D(14:3) must be used to interface to the nHD DMD when the I <sup>2</sup> C |  |  |

| DMD_D4        | P13 |            |             |                                                                                                                                                                                        | programmable option to reverse the bit-order of the DMD interface pins is                                                                             |  |  |

| DMD_D5        | P14 |            |             |                                                                                                                                                                                        | selected (DMD Bus Swap Control, I <sup>2</sup> C: 0xA7).                                                                                              |  |  |

| DMD_D6        | P15 |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D7        | R15 |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D8        | R12 |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D9        | N11 |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D10       | P11 |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D11       | R11 |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D12       | N10 | VCC18      | O58         |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D13       | P10 | VCC16      | 036         |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_D14       | R10 |            |             |                                                                                                                                                                                        |                                                                                                                                                       |  |  |

| DMD_DCLK      | N13 |            |             | N/A                                                                                                                                                                                    | DMD Data Clock (DDR)                                                                                                                                  |  |  |

| DMD_LOADB     | R13 |            |             | DMD_DCLK                                                                                                                                                                               | DMD Data Load Signal (active low). This signal requires an external pullup to VCC18.                                                                  |  |  |

| DMD_SCTRL     | R14 |            |             | DMD_DCLK                                                                                                                                                                               | DMD Data Serial Control Signal                                                                                                                        |  |  |

| DMD_TRC       | P12 |            |             | DMD_DCLK                                                                                                                                                                               | DMD Data Toggle Rate Control                                                                                                                          |  |  |

| DMD_DAD_BUS   | L13 |            |             | DMD_SAC_CLK                                                                                                                                                                            | DMD DAD Bus Data                                                                                                                                      |  |  |

| DMD_DAD_STRB  | K13 |            | DMD_SAC_CLK | DMD DAD Bus Strobe                                                                                                                                                                     |                                                                                                                                                       |  |  |

| DMD_DAD_OEZ   | M13 |            | Async       | DMD Reset Driver Output Enable (active low). To properly park the DMD, this signal requires a $30\text{-k}\Omega$ to $100\text{-k}\Omega$ external pullup resistor connected to VCC18. |                                                                                                                                                       |  |  |

| DMD_SAC_BUS   | L15 |            |             | DMD_SAC_CLK                                                                                                                                                                            | DMD SAC Bus Data                                                                                                                                      |  |  |

| DMD_SAC_CLK   | L14 |            |             | N/A                                                                                                                                                                                    | DMD SAC Bus Clock                                                                                                                                     |  |  |

| PIN            |    | I/O        |     |               |                                                  |  |

|----------------|----|------------|-----|---------------|--------------------------------------------------|--|

| NAME NO.       |    | POWER TYPE |     | CLOCK SYSTEM  | DESCRIPTION                                      |  |

| SDRAM INTERFAC | E  |            |     |               |                                                  |  |

| MEM0_CLK_P     | D1 |            | 074 | N/A           |                                                  |  |

| MEM0_CLK_N     | E1 |            | 074 |               | mDDR memory, Differential Memory Clock           |  |

| MEM0_A0        | P1 |            |     |               |                                                  |  |

| MEM0_A1        | R3 |            |     |               |                                                  |  |

| MEM0_A2        | R1 |            |     |               |                                                  |  |

| MEM0_A3        | R2 |            |     |               |                                                  |  |

| MEM0_A4        | A1 |            |     |               |                                                  |  |

| MEM0_A5        | B1 |            |     |               |                                                  |  |

| MEM0_A6        | A2 |            |     |               | mDDR memory, Multiplexed Row, and Column Address |  |

| MEM0_A7        | B2 |            |     |               |                                                  |  |

| MEM0_A8        | D2 |            |     |               |                                                  |  |

| MEM0_A9        | A3 |            | 004 | MEM OUR       |                                                  |  |

| MEM0_A10       | P2 |            | O64 | MEM_CLK       |                                                  |  |

| MEM0_A11       | В3 |            |     |               |                                                  |  |

| MEM0_A12       | D3 |            |     |               |                                                  |  |

| MEM0_BA0       | МЗ |            |     |               | mDDD maman, Dank Calast                          |  |

| MEM0_BA1       | P3 |            |     |               | mDDR memory, Bank Select                         |  |

| MEM0_RASZ P4   |    |            |     |               | mDDR memory, Row Address Strobe (active low)     |  |

| MEM0_CASZ R4   |    |            |     |               | mDDR memory, Column Address Strobe (active low)  |  |

| MEM0_WEZ       | R5 |            |     |               | mDDR memory, Write Enable (active low)           |  |

| MEM0_CSZ       | J3 | VCC18      |     |               | mDDR memory, Chip Select (active low)            |  |

| MEM0_CKE       | C1 | VCC18      |     |               | mDDR memory, Clock Enable (active high)          |  |

| MEM0_LDQS      | J2 |            | B64 | N/A           | mDDR memory, Lower Byte, R/W Data Strobe         |  |

| MEM0_LDM       | J1 |            | O64 | MEM0_LDQS     | mDDR memory, Lower Byte, Write Data Mask         |  |

| MEM0_DQ0       | N1 |            |     |               |                                                  |  |

| MEM0_DQ1       | M2 |            |     |               |                                                  |  |

| MEM0_DQ2       | M1 |            |     |               |                                                  |  |

| MEM0_DQ3       | L3 |            | DG4 | MEMO LDOS     | mDDR mamony Lawer Bute Bidirectional BAW Date    |  |

| MEM0_DQ4       | L2 |            | B64 | MEM0_LDQS     | mDDR memory, Lower Byte, Bidirectional R/W Data  |  |

| MEM0_DQ5       | K2 |            |     |               |                                                  |  |

| MEM0_DQ6       | L1 |            |     |               |                                                  |  |

| MEM0_DQ7       | K1 |            |     |               |                                                  |  |

| MEM0_UDQS      | G1 |            | B64 | N/A           | mDDR memory, Upper Byte, R/W Data Strobe         |  |

| MEM0_UDM       | H1 |            | O64 | MEM0_UDQS     | mDDR memory, Upper Byte, Write Data Mask         |  |

| MEM0_DQ8       | H2 |            |     |               |                                                  |  |

| MEM0_DQ9       | G2 |            |     |               |                                                  |  |

| MEM0_DQ10      | НЗ |            |     |               |                                                  |  |

| MEM0_DQ11      | F3 |            | DC4 | MEM0 UDQS     | mDDP mamony Unper Bute Bidirectional BAM Date    |  |

| MEM0_DQ12      | F1 |            | B64 | INIEINIO_UDQ3 | mDDR memory, Upper Byte, Bidirectional R/W Data  |  |

| MEM0_DQ13      | E2 |            |     |               |                                                  |  |

| MEM0_DQ14      | F2 |            |     |               |                                                  |  |

| MEM0_DQ15      | E3 |            |     |               |                                                  |  |

| PIN             |         | VO           |       |              | (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |  |

|-----------------|---------|--------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| NAME NO.        |         | POWER TYPE   |       | CLOCK SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |  |

| LED DRIVER INTE |         | FOWER        | IIFE  |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |  |

| GPIO1_RPWM      | N8      |              | O14   | Async        | General-purpose I/O 1 (output only). If the DLPA1000 is not used, then this output must be used as the red LED PWM signal used to control the LED current. (8) If the DLPA1000 is used, then this output can be used as a general purpose output controlled by the WPC processor.                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                               |  |

| GPIO2_GPWM      | P9      |              | O14   | Async        | General-purpose I/O 2 (output only). If the output must be used as the green LED P current. (8) If the DLPA1000 is used, then general purpose output controlled by the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WM signal used to control the LED this output can be used as a                                                |  |

| GPIO3_BPWM      | R8      |              | O14   | Async        | General-purpose I/O 3 (output only). If the output must be used as the blue LED PW current. (8) If the DLPA1000 is used, then general-purpose output controlled by the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /M signal used to control the LED this output can be used as a                                                |  |

| LED_SEL_0       | R6      |              | O14   | Async        | LED enable SELECT. Controlled by prog (hysteresis buffer).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rammable DMD sequence timing                                                                                  |  |

|                 |         |              |       |              | LED_SEL(1:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Selected LED                                                                                                  |  |

|                 |         |              |       |              | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | None                                                                                                          |  |

|                 |         | VCC18        |       |              | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Red                                                                                                           |  |

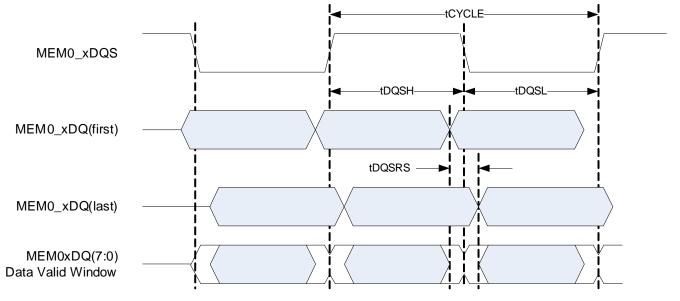

| LED SEL 1       | N6      |              | 014   | Async        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Green                                                                                                         |  |