# TI Designs 600-V Unidirectional Current, Voltage, and Power Monitoring for Solar Smart Combiner Box

# Texas Instruments

# Overview

This reference design is a non-isolated high-side current and voltage sensing design for a smart combiner box in a grounded or ungrounded system. The current sensing topology enables non-isolated sensing for high-voltage systems.

## Resources

600-V DC bus (4)

| TIDA-00639 | Design Folder  |

|------------|----------------|

| OPA333     | Product Folder |

| INA226     | Product Folder |

| LMT84      | Product Folder |

| TPS7A6533  | Product Folder |

I<sup>2</sup>C

External power supply and voltage regulator

Board

600-V DC bus (1)

#### Features

- Non-Isolated High-Side Current and Voltage Monitoring of One to Four Photovoltaic Strings

- Capable of Monitoring Voltage Within ±1% Full Scale Accuracy

- Capable of Uncalibrated Current Monitoring Within ±1.25% Full Scale Accuracy and Capable of Calibrated Current Monitoring Within ±0.75% Full Scale Accuracy

- Integrates With RS-485 Communication Board

- Option to Connect Four TIDA-00639 Boards to One MCU

#### Applications

- Smart Combiner Box

- Solar Inverter

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

1

# 1 System Overview

# 1.1 System Description

While the deployment of photovoltaic (PV) systems has grown exponentially over the past 10 years, solar energy still powers only a small percentage of the grid. The two major challenges are cost (amount per watt) and efficiency. When developing new solar technology (solar inverters, power optimizers, and so on), a system designer must increase efficiency through intelligent system and subsystem topologies that also decrease the cost per watt.

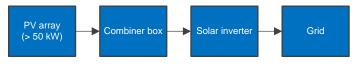

For PV arrays with a power capacity greater than 50 kW, it is necessary to combine the PV strings into a high-voltage direct current (DC) bus before the inverter. This system is known as a solar combiner box. The solar combiner box in relation to the solar power system is shown in Figure 1.

Figure 1. Solar Power System

The solar combiner box reduces the total system cost by decreasing the external cabling and copper DC buses. Solar combiner boxes are connected to one or more PV strings. One PV string is typically rated to 600-V, 1000-V, 1200-V, or 1500-V DC, and 8 to 25 A. This varies depending on the layout of the PV array and the solar power system.

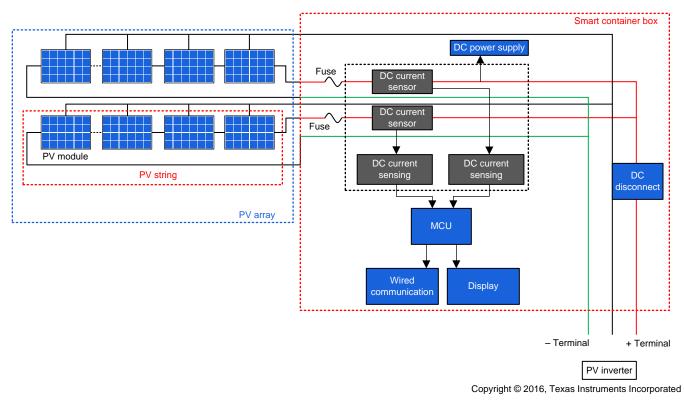

Traditionally, power monitoring occurred at a multi-string level, but now, with increasing array sizes, string level power monitoring becomes critical to immediately detect a solar panel operating at a diminished capacity and the corresponding damage. The solar combiner box became the smart combiner box when current and voltage sensing technology was moved from the solar inverter (multi-string level) to the solar combiner box. The smart combiner box with a basic feature set is displayed in Figure 2.

# Figure 2. Smart Combiner Box in PV System (1)

(1) http://www.homepower.com/articles/solar-electricity/equipment-products/pv-combiner-box-buyers-guide

The TIDA-00639 is the power sensing subsystem shown within the black dotted box in Figure 2. The board is also designed to enable connection to an MCU and RS-485 communication board, the most common form of communication in smart combiner boxes.

# 1.1.1 Power Sensing Subsystem

The input current of a smart combiner box can be measured by isolated and non-isolated current sensing methods depending on the accuracy, size, and cost restrictions. Isolated solutions are widely used in smart combiner boxes. Isolated sensors cost more than non-isolated sensors and also require an analog front end for high-precision measurements. With high-voltage considerations taken into account for the schematic design and PCB layout, non-isolated current sensing is a viable alternative with the potential to lower the system cost.

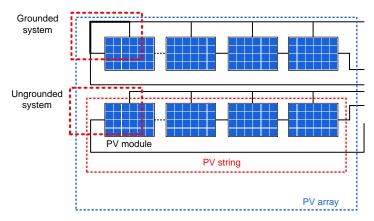

The currents of PV strings can be measured with non-isolated high-side or low-side current sensing techniques, depending on the solar power system's accuracy requirements and grounding configuration. In the United States, the National Electric Code requires PV modules or strings over 50-V DC to be a grounded system to decrease safety risks. A grounded system is defined as either the positive or negative terminal being tied directly to earth ground. <sup>(2)</sup> Low-side and high-side sensing are viable options for a grounded system. The majority of regional standards regarding solar power systems worldwide do not require PV installations to be grounded systems. Grounded and ungrounded systems are pictured in Figure 3.

Copyright © 2016, Texas Instruments Incorporated

# Figure 3. Smart Combiner Box With Ungrounded and Grounded Systems

Low-side current sensing is less expensive than high-side sensing. However, this method cannot detect load shorts in ungrounded or grounded systems and cannot account for grounding inconsistencies. High-side current sensing directly measures the current through the load (before DC combination) and can accurately measure the current in relation to a common ground, the PV string ground. When the smart combiner box is connected to a grounded system and high-accuracy current sensing is not a requirement, low-side current sensing could be the preferred option. When accuracy, load shorts, or grounding inconsistencies are a concern, high-side sensing is the preferred method. Consequently, the majority of smart combiner boxes employ high-side current sensing.

Smart combiner boxes also measure PV string voltage. Because the PV strings are connected in parallel, the string voltages will all be equal. Consequently, one voltage measurement is necessary for power monitoring. In a grounded or ungrounded system, TI's power monitor can be used for DC bus voltage and current measurements. The bus voltage and current will be measured in relation to PV string ground.

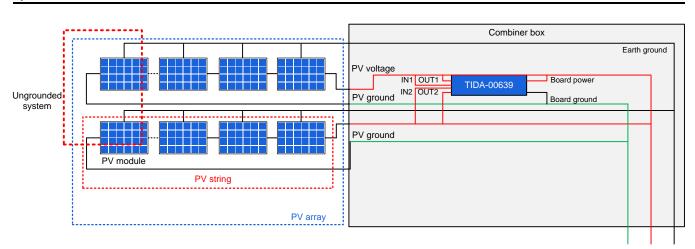

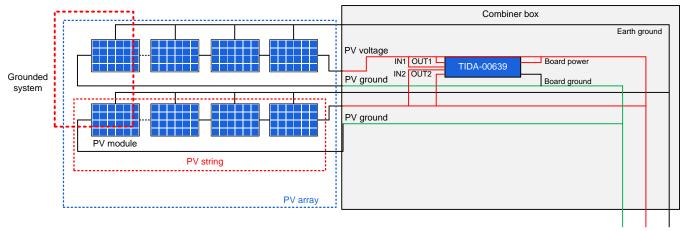

The TIDA-00639 evaluates non-isolated high-side current and voltage sensing for ungrounded and grounded systems. Figure 4 and Figure 5 depict how to connect the TIDA-00639 within a smart combiner box in an ungrounded or grounded system. The voltage and current of the PV string are sensed in relation to the negative terminal of the PV string. The TIDA-00639 measures a maximum of 15 A and 600-V DC at  $\pm$ 1% full scale.

<sup>(2)</sup> http://solarabcs.org/about/publications/reports/systemgrounding/pdfs/SystemGrounding\_studyreport.pdf

#### System Overview

Copyright © 2016, Texas Instruments Incorporated

Figure 4. TIDA-00639 in Ungrounded PV System

Copyright © 2016, Texas Instruments Incorporated

Figure 5. TIDA-00639 in Grounded PV System

# 1.2 Key System Specifications

| PARAMETER                     | SPECIFICATION     |

|-------------------------------|-------------------|

| Uncalibrated I sense accuracy | ±1.25% full scale |

| Calibrated I sense accuracy   | ±.75% full scale  |

| Uncalibrated V sense accuracy | ±1.0% full scale  |

| DC bus current                | 0.5 to 15 A       |

| DC bus minimum voltage        | 95 V              |

| DC bus maximum voltage        | 600 V             |

| Number of PV string inputs    | 4 per board       |

| Operating temperature range   | -40°C to 85°C     |

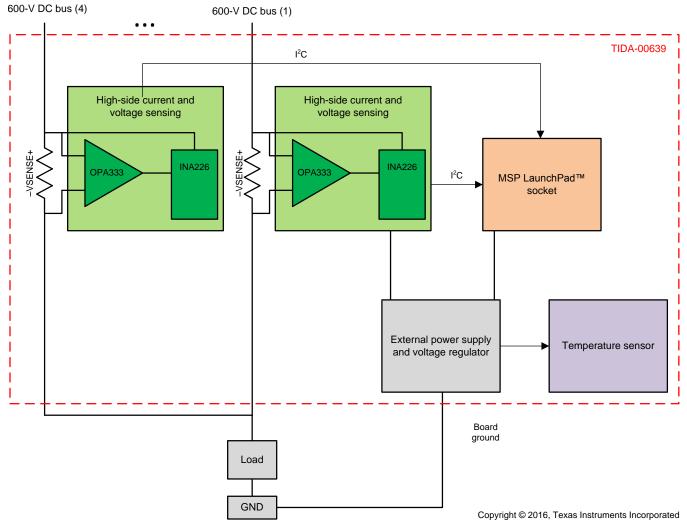

# 1.3 Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 6. TIDA-00639 Block Diagram

# 1.4 Highlighted Products

The TIDA-00639 reference design features the following devices:

- OPA333: Precision amplifier with zero drift and low offset voltage

- INA226: Current shunt and power monitor with I<sup>2</sup>C or SMBUS-compatible interface

- LMT84: Analog output temperature sensor

- TPS7A6533-Q1: 40-V LDO with ultra-low quiescent current

# 1.4.1 OPA333

- Low offset voltage: 10 μV (maximum)

- Zero drift: 0.05 μV/ºC (maximum)

- 0.01- to 10-Hz noise: 1.1  $\mu V_{PP}$

- Quiescent current: 17 μA

- Single-supply operation

- Supply voltage: 1.8 to 5.5 V

- Rail-to-rail input/output

- microSize packages: SC70 and SOT23

#### System Overview

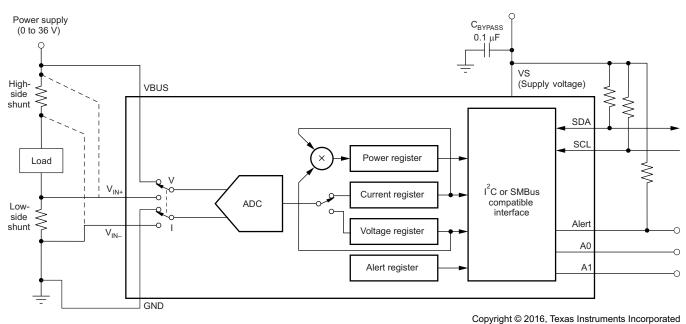

#### 1.4.2 INA226

# Figure 7. INA226 Simplified Schematic

- Senses bus voltages from 0 to 36 V

- High-side or low-side sensing

- Reports current, voltage, and power

- Configurable averaging options

- 16 programmable addresses

- Operates from 2.7- to 5.5-V power supply

- 10-pin DGS (VSSOP) package

- High accuracy:

- 0.1 % gain error (maximum)

- 10-μV offset (maximum)

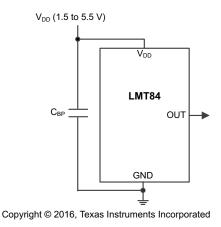

# 1.4.3 LMT84

# Figure 8. LMT84 Simplified Schematic

- AEC-Q100 Grade 0 qualified and manufactured on an automotive grade flow

- Low 1.5-V operation

- Very accurate: ±0.4°C typical

- Wide temperature range of -50°C to 150°C

- Low 5.4-μA quiescent current

- Average sensor gain of -5.5 mV/°C

- · Output is short-circuit protected

- Push-pull output with ±50-μA drive capability

- · Footprint compatible with industry-standard LM20/LM19 and LM35 temperature sensors

- · Cost-effective alternative to thermistors

- Packages:

- Small SC70 (SOT 5-lead) surface mount

- Leaded TO-92

7

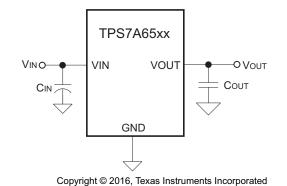

#### TPS7A6533-Q1 1.4.4

# Figure 9. TPS7A6533-Q1 Simplified Schematic

- Low dropout voltage

- 300 mV at I<sub>OUT</sub> = 150 mA

- 4- to 40-V wide input voltage range with up to 45-V wide input voltage range with up to 45-V \_ transients

- 300-mA maximum output current

- 25-µA (typical) ultra-low quiescent current at light loads \_

- 3.3- and 5-V fixed output stability capacitor

- Low input-voltage tracking

- Thermally enhanced power package

- 3-pin TO-252 (KVU/DPAK) •

- Integrated fault protection ٠

- Short-circuit and overcurrent protection •

- ٠ Thermal shutdown

# 2 System Design Theory

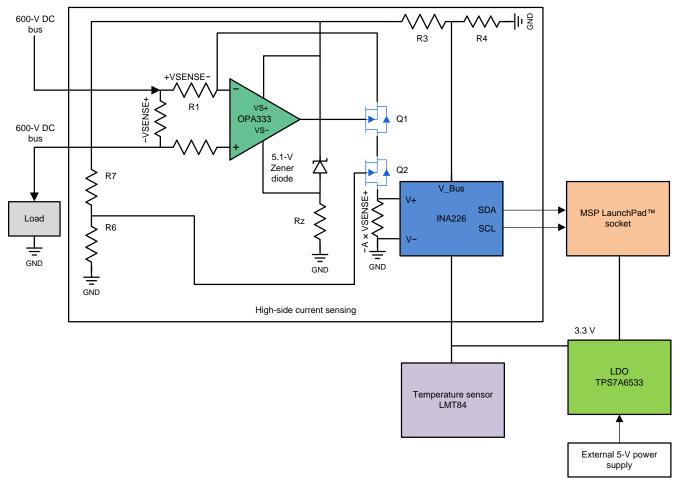

Figure 10. High-Level System Block Diagram

The TIDA-00639 is a shunt-based current and voltage sensing subsystem for a smart combiner box, as pictured in Figure 10. The shunt resistor is on the high-side of the load, directly measuring the current flowing into the load from each input. The shunt resistor was chosen to minimize heat dissipation and power losses while maximizing the voltage measured by the current sensing circuit. In order to lower the power losses to a negligible level, a shunt resistance of 1 m $\Omega$  was chosen. At maximum current, the power dissipation for one channel can be calculated as shown in the following equations.

Maximum power dissipation =

$$V_{SENSE} \times I_{SHUNT} = 15 \text{ mV} \times 15 \text{ A} = 0.225$$

(1)

% power dissipation from shunt =

$$\frac{\text{Maximum power dissipation}}{\text{Maximum total power}} \times 100 = \frac{0.225 \text{ W}}{600 \text{ V} \times 15 \text{ A}} \times 100$$

(2)

when

•

$$V_{\text{SENSE}} = R_{\text{SHUNT}} \times I_{\text{SHUNT}} = 1 \text{ m}\Omega \times 15 \text{ A} = 15 \text{ mV}$$

The 1-m $\Omega$  shunt resistor is rated at 1% tolerance and 170 ppm. This shunt resistor was chosen with cost in mind. The ppm rating was lowered to a practical level for a smart combiner box, which operates at a maximum temperature of 60°C to 85°C. To use a cost competitive shunt resistor, the tolerance was minimized at 1%. The shunt resistor's tolerance can be improved at the expense of component price or ppm rating. The shunt resistor's 1% tolerance equates to variances in channel-to-channel sensing accuracy.

9

System Design Theory

This 1-m $\Omega$  shunt resistor is paired with a signal conditioning circuit to maximize the accuracy of the current sensing circuit. The shunt resistor and sensing circuit are designed so that V<sub>SENSE</sub> across the shunt resistor is mirrored across the input resistor of the op amp. The op amp and high-voltage P-FETs are designed in a current follower configuration to drop the DC bus voltage and mirror V<sub>SENSE</sub> to the current shunt monitor, the INA226. Currently, P-FET technology is limited to 600 V, and P-FETs rather than N-FETs are necessary for the current follower topology. Consequently, two 400-V P-FETs are connected in series to drop 600 V. Low leakage FETs are necessary for this high-precision application. See Section 2.1 for more details.

The INA226 can also monitor each PV string voltage. See Section 2.2 for more details.

Smart combiner boxes are typically powered by an internal power supply from a PV string. The DC/DC power supply block is not within the scope of the TIDA-00639, so an external power supply is used. For more information about possible DC/DC converter topologies for the power supply, TI offers Power Reference Designs to evaluate power subsystems. See Section 2.3 for more details on the power supply for the TIDA-00639.

Smart combiner boxes have a temperature sensor to monitor the temperature within the box. The smart combiner box is typically outside, and it can become overheated. Monitoring the temperature is necessary to verify the internal temperature is less than the box's operating temperature. The LMT84 enables highly accurate temperature sensing, and is described in Section 2.4.

A LaunchPad<sup>™</sup> socket enables the connection of the TIDA-00639 to a TI MCU LaunchPad board. This design is further discussed in Section 2.5.

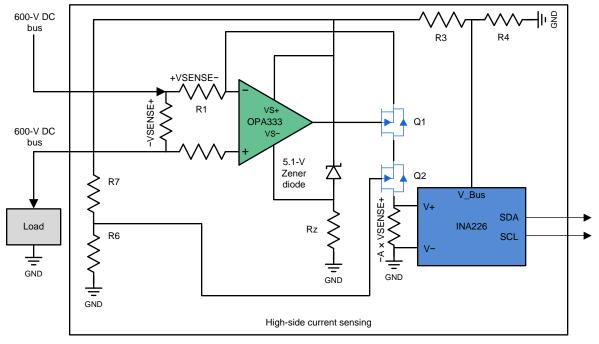

# 2.1 High-Side Current Sensing

Copyright © 2016, Texas Instruments Incorporated

Figure 11. High-Side Current Sensing Block Diagram

The voltage drop across the shunt resistor is mirrored across R1. In Figure 11, this voltage is  $V_{\text{SENSE}}$ . The op amp and P-FET, Q1, are designed in a current follower configuration. The current through R1 flows through the op amp's feedback loop and the biased P-FETs. To bias the P-FETs:

$v_{sg} \ge v_{th}$

$$v_{sd} \ge v_{sg} + v_{th}$$

(3)

(7)

The P-FET (IRFU9310PBF) was chosen for its high-voltage capability and its low v<sub>sg</sub> specification, which supports using a precision, low-voltage op amp for the drive. The IRFU9310PBF was also chosen due to the low leakage current specifications, I<sub>GSS</sub> and I<sub>DSS</sub>. The current flowing through R1, Q1, Q2, and R2 varies between 0.5 and 1.5 mA. To accurately measure the bus current, the total leakage current must be less than 1% full scale of 1.5 mA.

The OPA333 was chosen for its low offset and zero drift. The OPA333's positive and negative power supply terminals can have a maximum delta of 5.5 V. To pair the OPA333 with this P-FET configuration, the P-FET must have a  $|v_{th}| \le 5$  V. The IRFU9310PBF has a  $v_{th MAX} = -4$  V.

A 5.1-V Zener diode is used to float the OPA333 to the high-voltage rail to bias the P-FET. The Zener resistor,  $R_z$ , is sized correctly for proper biasing of the Zener diode and the op amp. The MMSZ4689TI Zener diode was chosen for its low nominal current of 50  $\mu$ A. The Zener resistor needs to accommodate the op amp and Zener diode's currents for proper biasing.

$$R_{Z} \leq \frac{Bus \ supply - V_{Z}}{I_{ZENER} + I_{OPA333}} = \frac{V_{R_{Z}}}{I_{ZENER} + I_{OPA333}} = \frac{600 \ V - 5.1 \ V}{50 \ \mu A + 25 \ \mu A} = 7.932 \ M\Omega$$

(4)

For this design,  $R_z$  is 4.08 M $\Omega$ . With a significantly lower  $R_z$ , the design can also work at lower DC bus voltages. The resistance  $R_z$  is split into six series resistors of 680 k $\Omega$  to divide the 600-V drop and ease the power dissipation requirement for each resistor.

Power rating

$$\geq \frac{V^2}{R} = \frac{\left(\frac{(600-5.1)}{6}\right)^2}{4.08 \text{ M}\Omega} = 2.409 \text{ m}$$

(5)

Choosing a lower power Zener diode and op amp will lower wattage requirements for resistors and, consequently, reduce board space and cost.

The second P-FET, Q2, is biased by a voltage divider where R7 = R6. When both P-FETs are biased, their equivalent circuits are two resistors,  $R_{sd}$ , in series. Consequently, the current flowing through R1 is equal to the current flowing through Q1, Q2, and R2. The voltage across R2 is determined by a gain factor A, where:

$$A = \frac{R2}{R1}$$

(6)

The INA226 measures the differential voltage across R2. The INA226's full scale voltage is 80 mV. When the maximum current is flowing through the shunt resistor, the voltage across R2 must be approximately 80 mV to maximize the INA226's accuracy.

$$\frac{V_{R2}}{V_{SENSE}} = \frac{R2}{R2} = \frac{80 \text{ mV}}{15 \text{ mV}} \approx 5$$

With a gain factor of 5, R2 = 50  $\Omega$  and R1 = 10  $\Omega$ .

## 2.1.1 Power Losses

For non-isolated high-side current sensing applications, heat and power dissipation are two of the primary design considerations and challenges. The two P-FETs have the largest power dissipation. Heat or power dissipation methods need to be employed if operating at high power for a long duration of time. To calculate power and heat dissipation across one transistor at a bus voltage of 600 V and a bus current of 15 A:

Power dissipation =

$$\frac{VBUS}{2} \times I_{PFET} = 300 \text{ V} \times 1.5 \text{ mA} = 0.45$$

% power dissipation from PFET =  $\frac{\text{Maximum power dissipation}}{\text{Maximum total power}} \times 100 = \frac{0.45 \text{ W}}{600 \text{ V} \times 15 \text{ A}} \times 100 = 0.005\%$

(8)

(9)

where

$$I_{PFET} = \frac{V_{SENSE}}{R1} = \frac{15 \,\text{mV}}{10 \,\Omega} = 1.5 \,\text{mA}$$

#### 2.1.2 Error Sources

High accuracy was one of the primary design requirements. The op amp has zero drift and low offset. The INA226 has low offset. Consequently, the primary source of error is the P-FET leakage, which increases at greater common-mode voltages. The current,  $I_{SD}$ , varies between 0.5 and 1.5 mA. To minimize the effects of the P-FET's inherent error, the signal current ( $I_{SD}$ ) can be increased at the cost of increased power losses, or the P-FET leakage current can be calibrated out at the cost of additional time. The TIDA-00639 is designed to minimize power losses and maximize accuracy. Consequently, the signal current is minimized, and the P-FET leakage current can be calibrated out depending on accuracy requirements.

The second source of error is the shunt resistor's tolerance rating of 1%. This source of error causes channel-to-channel variances in current sensing measurement and is further explored in Section 4.2. To minimize this error source, a shunt resistor with a higher tolerance can be chosen.

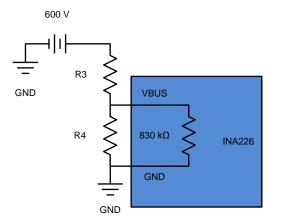

## 2.2 Non-Isolated Voltage Measurement

Copyright © 2016, Texas Instruments Incorporated

#### Figure 12. Non-Isolated Voltage Sensing Block Diagram

For grounded systems, accurate voltage monitoring can be integrated into the INA226. The INA226 can measure a maximum voltage of 36 V. The INA226's voltage monitoring is also limited by the input impedance of 830 k $\Omega$ , as seen in Figure 12. Therefore, R4 must be significantly smaller than the input impedance, so R3 and R4 divide the voltage down accurately.

In summary, the voltage divider (R3 and R4) must step down the bus voltage to  $V_{R4}$  < 36 V, and R4 << 830 k $\Omega$  (R4 = 12 k $\Omega$  and R3 = 500 k $\Omega$ ).

$$V_{R4} = V_{BUS} \times \frac{R4}{R4 + R3}$$

(10)

When the bus voltage is 600 V,  $V_{R4} = 600 \times \frac{12 \, k\Omega}{12 \, k\Omega + 500 \, k\Omega} = 14.0625 \, V$

## 2.3 Board Power Supply

The board is powered by a 5-V external supply through the terminal block input, J10. This power supply's ground terminal is connected to the PV string ground, and the terminal block input, J10, which stabilizes the PCB's ground plane. The 5-V power supply is stepped down to 3.3 V by the TPS7A6533, an LDO. The 3.3-V voltage rail powers the INA226, LMT84, and the LaunchPad socket.

## 2.4 Temperature Sensing

The LMT84 is a highly accurate temperature sensor, capable of measuring within  $\pm 0.4^{\circ}$ C. The temperature sensor also offers a wide temperature range of  $-50^{\circ}$ C to  $150^{\circ}$ C. Consequently, the smart combiner box will be able to detect if the temperature has dropped below or elevated above the operating temperature range. The accuracy of the LMT84's analog output can be evaluated on header J9.

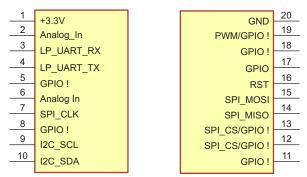

# 2.5 MCU LaunchPad Socket

Copyright © 2016, Texas Instruments Incorporated

Figure 13. LaunchPad Socket

The standard LaunchPad socket is on board to enable connection to an MCU. The LaunchPad enables I<sup>2</sup>C and UART communication.

# 2.6 Non-Isolated High-Side Sensing for 1000-V DC Bus

The high-side current sensing topology described in Section 2.1 can be redesigned to accommodate a 1000-V DC bus. The primary change is replacing Q1 and Q2 with two 600 V P-FETs. The resistor chains R6, R7, and RZ must be resized to dissipate the higher power and step down the higher voltage.

For the non-isolated voltage measurements, the resistor dividers must ensure the INA226's voltage threshold is not exceeded. The INA226's voltage bus threshold is 36 V. For this TI Design, the resistor dividers for the voltage measurements must be redesigned to drop 1000 V, and use caution in regards to the voltage and power ratings of the resistors.

With increased voltage, the components will have increased spacing on the PCB. The layout changes are addressed in Section 5.3.

The primary design challenges and concerns for a 1000-V DC design are accuracy and heat dissipation. As the voltage increases, the P-FET current leakage increases. The system designer will have two options to uphold  $\pm$ 1% full scale accuracy with a common-mode voltage of 1000 V. One option is increasing the current through Q1 and Q2 by decreasing R1 and R2. The leakage current must be less than 1% of I\_SD with a DC bus rated at 1000 V and 15 A. This is at the cost of increased power losses. The second option is calibrating out the FET current leakage with an MCU. In order to mitigate heat dissipation concerns, heat sinking technology can be used.

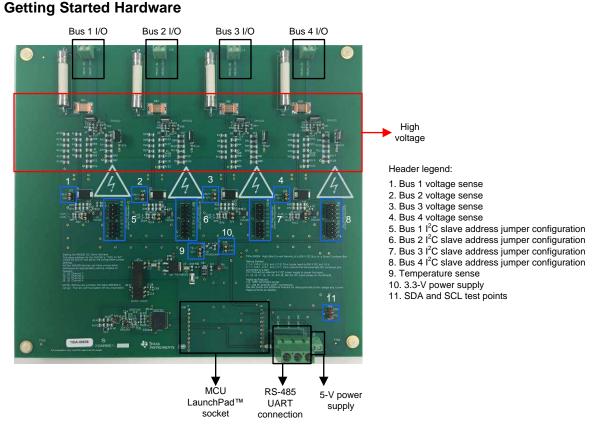

Getting Started Hardware

3

www.ti.com

Figure 14. TIDA-00639 PCB

#### 3.1 Board Setup

- 1. Connect the four high-power inputs to terminal screw blocks J11-1, J18-1, J12-1, and J17-1. These inputs are rated for 600-V DC and 16 A. If the voltage and current ratings are exceeded, the fuse will blow.

- 2. Connect the four high power outputs to the terminal screw blocks J11-2, J18-2, J12-2, and J17-2. These outputs can be tested individually or be DC combined in parallel and connected to a load rated for the output power.

- 3. Optional: Connect a LaunchPad board to the LaunchPad socket, J19. Configure the INA226 I<sup>2</sup>C slave address. The slave address for the INA226 is "1000'A1"A0'", where A0 and A1 are set by the configurable jumper settings as described in Table 2. All four INA226 devices can have unique slave addresses by appropriately placing jumpers on the headers as described in Table 3.

| Table 2. | INA226 | I <sup>2</sup> C Slave | Address | Jumper | Configuration                          |

|----------|--------|------------------------|---------|--------|----------------------------------------|

|          |        |                        |         |        | •••••••••••••••••••••••••••••••••••••• |

| JUMPER CONFIGURATION | A0 | A1 |

|----------------------|----|----|

| Pins 7-8: Ground     | 0  | 0  |

| Pins 5-6: SCL        | 11 | 11 |

| Pins 3-4: SDA        | 10 | 10 |

| Pins 1-2: VCC        | 1  | 1  |

| CHANNEL   | A0 HEADER | A1 HEADER |

|-----------|-----------|-----------|

| Channel 1 | J1        | J3        |

| Channel 2 | J5        | J7        |

| Channel 3 | J2        | J4        |

| Channel 4 | J6        | J8        |

- 4. Connect an external 5-V DC power supply must be connected to J10 to power on the TIDA-00639 board.

- 5. Begin evaluating the performance of the TIDA-00639 through the appropriate headers and test points, as described in Section 3.2.

# 3.2 Evaluation Headers and Test Points

| COMPONENT<br>DESIGNATOR                 | PIN NUMBER             | SIGNAL                          |  |  |  |

|-----------------------------------------|------------------------|---------------------------------|--|--|--|

| DC BUS CURRENT AN                       | ID VOLTAGE TEST POI    | NTS                             |  |  |  |

| J23                                     | 1                      | Ground                          |  |  |  |

|                                         | 2                      | VBUS1                           |  |  |  |

| J25                                     | 1                      | Ground                          |  |  |  |

| 525                                     | 2                      | VBUS2                           |  |  |  |

| J24                                     | 1                      | Ground                          |  |  |  |

| 524                                     | 2                      | VBUS3                           |  |  |  |

| J26                                     | 1                      | Ground                          |  |  |  |

| 520                                     | 2                      | VBUS4                           |  |  |  |

| J13                                     | 1                      | Current1-                       |  |  |  |

| 515                                     | 2                      | Current1+                       |  |  |  |

| J14                                     | 1                      | Current2-                       |  |  |  |

| J14                                     | 2                      | Current2+                       |  |  |  |

| J15                                     | 1                      | Current3-                       |  |  |  |

| 515                                     | 2                      | Current3+                       |  |  |  |

| J16                                     | 1                      | Current4–                       |  |  |  |

| 510                                     | 2                      | Current4+                       |  |  |  |

| TEMPERATURE SENSOR TEST POINT           |                        |                                 |  |  |  |

| 9                                       | 1                      | Temperature                     |  |  |  |

| 55                                      | 2                      | Ground                          |  |  |  |

| BOARD POWER TEST                        | BOARD POWER TEST POINT |                                 |  |  |  |

| J22                                     | 1                      | Ground                          |  |  |  |

| JZZ                                     | 2                      | 3.3 V                           |  |  |  |

| ISOLATED VOLTAGE MEASUREMENT TEST POINT |                        |                                 |  |  |  |

| TP2                                     | 1                      | Isolated voltage<br>(Channel 1) |  |  |  |

| I <sup>2</sup> C TEST POINT             |                        |                                 |  |  |  |

| TP3                                     | 1                      | SDA                             |  |  |  |

| TP4                                     | 1                      | SCL                             |  |  |  |

# Table 4. Evaluation Headers and Test Points

# 4 Testing and Results

# 4.1 Test Setup

# 4.1.1 Current and Voltage Accuracy Test Setup

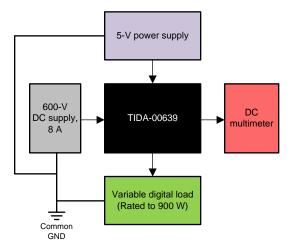

Copyright © 2016, Texas Instruments Incorporated

# Figure 15. Current and Voltage Sensing Accuracy Test Setup

A Magna power supply rated at 600-V DC and 8 A was used to connect to the terminal block inputs (J11-1, J18-1, J12-1, J17-1). The variable digital load was connected to the output of the TIDA-00639 through the terminal block outputs (J11-2, J18-2, J12-2, J17-2). The power supply and digital load simulate the DC bus connected to the solar inverter.

The 5-V external power supply is connected to the terminal block J10. The ground from the 5-V power supply is connected to the PCB ground plane, and it must also be connected to the ground of the load and 600-V DC power supply to create a common ground.

The DC multimeter is used to monitor the DC voltage corresponding to the voltage sense or current sense measurement. Table 4 calls out the header pins tested to measure the current and voltage sense accuracy. The results are described in Section 4.2.

### 4.1.2 Full Current Range Sensing Accuracy Test Setup

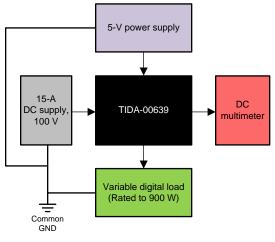

Copyright © 2016, Texas Instruments Incorporated

#### Figure 16. Full Current Range Sensing Accuracy Test Setup

A 100-V DC and 15-A power supply was used to connect to the terminal block inputs (J11-1, J18-1, J12-1, J17-1). The variable digital load was connected to the output of the TIDA-00639 through the terminal block outputs (J11-2, J18-2, J12-2, J17-2). The power supply and digital load simulate the DC bus connected to the solar inverter.

The 5-V external power supply is connected to the terminal block J10. The ground from the 5-V power supply is connected to the PCB ground plane, and it must also be connected to the ground of the load and 100-V DC power supply to create a common ground.

The DC multimeter is used to monitor the DC voltage corresponding to the voltage sense or current sense measurement. Table 4 calls out the header pins tested to measure the current and voltage sense accuracy. The results are described in Section 4.2.

# 4.2 Test Data

## 4.2.1 Current Sensing Accuracy

The current sense accuracy is dependent on the tolerances of the shunt resistor and the leakage current of the P-FETs. The drain-to-source and gate-to-source leakage currents increase as the drain-to-source voltage increases. As the current through the shunt increases, the current flowing through the P-FETs increases. As the source-to-drain current increases, the I<sub>SD</sub> percent loss due to leakage decreases. Consequently, as the DC bus current increases the current sense measurement increases in accuracy.

As designed and without calibration, the full scale error is within  $\pm 1.25\%$  full scale. There are three methods to maximize the current sense accuracy to  $\pm 1\%$  full scale and beyond:

- 1. Increasing the shunt resistor tolerance at the expense of increased component cost (Section 2)

- 2. Increasing the signal current at the expense of increased power losses (Section 4.2.1.2)

- 3. Calibrating the data at the expense of time (Section 4.2.1.3)

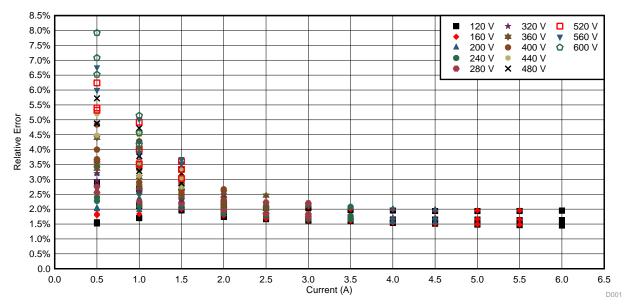

#### 4.2.1.1 Uncalibrated Accuracy

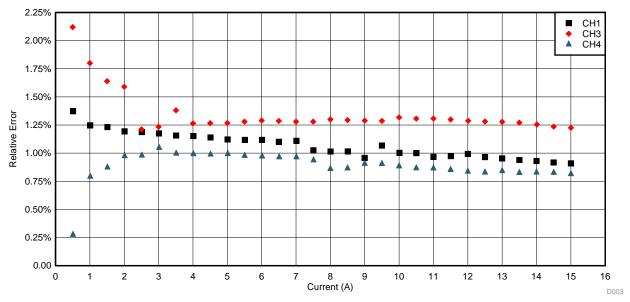

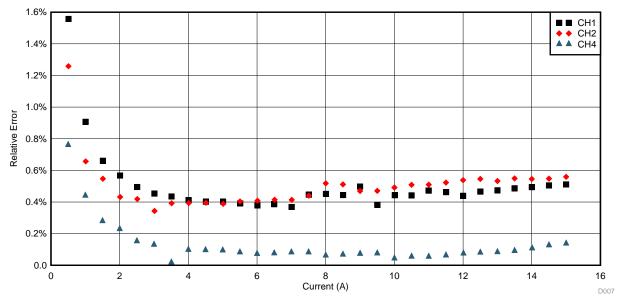

Using the test setup from Figure 15, the current sense accuracy was tested. This testing was limited to a total input power rating of 900 W and was run across three channels from two boards. The accuracy decreases with increasing voltage. As the voltage across the P-FET's source and drain increases, the leakage current increases. As the current increases, accuracy increases. The accuracy can be further improved by calibrating out the P-FET leakage losses. Figure 17 is the test results.

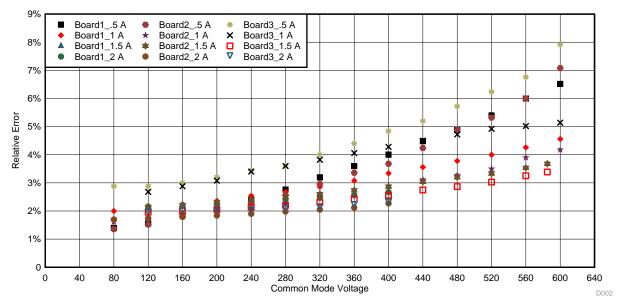

Using the test setup from Figure 15, the current sense accuracy was measured across the full common mode voltage range at four different currents (0.5 A, 1 A, 1.5 A, and 2 A). This test was run on three channels from two boards. Figure 18 is the test results. This test further proves that as the voltage increases, the accuracy decreases, and as the current increases, the accuracy increases.

Figure 17. Uncalibrated Relative Error of Current Sense Measurement versus Current

Figure 18. Uncalibrated Relative Error versus Common-Mode Voltage

#### Testing and Results

www.ti.com

Using the test setup from Figure 16, the full current range was swept across three channels. This test was run at a fixed DC bus voltage of 95 V. The current accuracy varies significantly channel to channel due to the 1% tolerance of the shunt resistor. All channels operate within  $\pm 1.25\%$  full scale accuracy. To ensure the accuracy is below  $\pm 1\%$  full scale for any channel, a universal calibration algorithm is implemented to calibrate out the P-FET leakage errors. If this error source is calibrated out but not the shunt resistor's tolerance, the accuracy will be less than 1% full scale. Consequently, one calibration equation will effectively lower the relative error for all channels, but there will still be channel-to-channel variances. Figure 19 shows the test results.

Figure 19. Uncalibrated Relative Error versus Current for 95-V DC Bus

### 4.2.1.2 Double I<sub>sp</sub> to Improve Uncalibrated Error

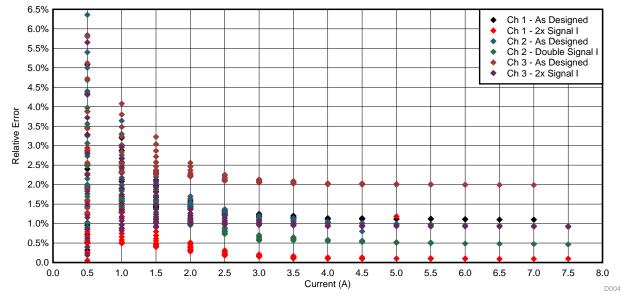

As discussed in Section 2.1.2, the primary error source is the leakage current from the P-FETs. Consequently, if the signal current through the P-FETs is increased, the leakage current's effects will be minimized. To test this theory, the signal current was doubled by changing the value of R1 from 10  $\Omega$  to 5  $\Omega$  and R2 from 50  $\Omega$  to 25  $\Omega$ . As expected, the error decreased significantly when the signal current was doubled. The test results for three channels are shown in Figure 20. The relative error is less than 1% starting at a 2.5-A DC bus. To maximize the signal current and minimize the power losses, R1 and R2 can be sized to exactly enable the desired level of accuracy.

Figure 20. Uncalibrated Relative Error of Current Sense Measurement versus Current

#### 4.2.1.3 Calibrated Error

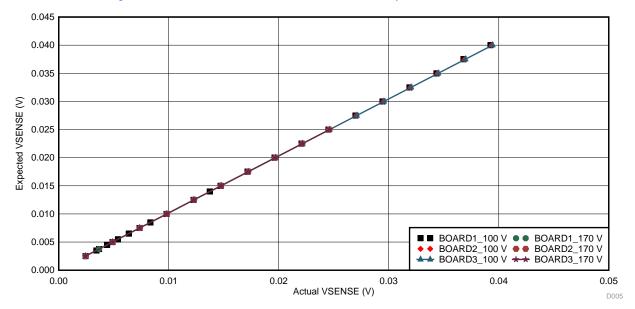

To calibrate out the P-FET leakage error, a universal calibration equation was developed based on the linear relationship between the expected current and the actual output current. Figure 21 shows the linear relationship between the expected and actual current sense measurement. Figure 22 is the relative error versus current of the data from Figure 17 after calibration. Figure 23 is the relative error versus current of the data from Figure 19 after calibration. The full scale accuracy is under ±0.75%.

Figure 21. Expected I<sub>SENSE</sub> versus Actual I<sub>SENSE</sub>

Figure 22. Relative Error versus Current With Calibration Across Full Voltage Range

Figure 23. Relative Error versus Current With Calibration Across Full Current Range

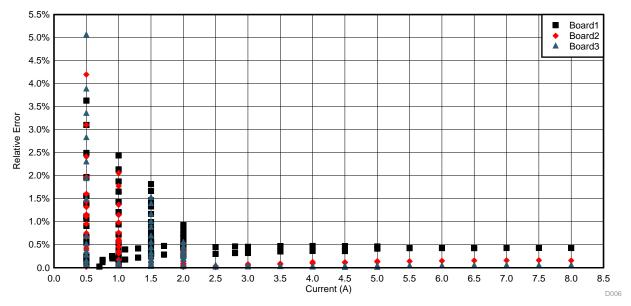

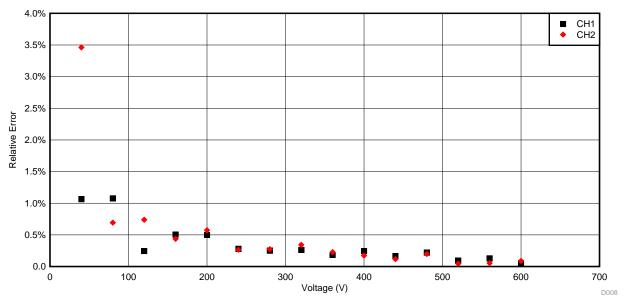

# 4.2.2 Voltage Sensing Accuracy

The INA226 is capable of measuring the DC bus voltage. The voltage measurement is designed to operate at  $\pm 1\%$  full scale accuracy. The maximum DC bus value for this design is 600 V. The voltage measurement was tested across two channels. The test results are shown in Figure 24.

Figure 24. Relative Error of Voltage Sense Measurement versus Voltage

TEXAS INSTRUMENTS

www.ti.com

#### Design Files

# 5 Design Files

#### 5.1 Schematics

To download the schematics for each board, see the design files at TIDA-00639.

## 5.2 Bill of Materials

To download the bill of materials for each board, see the design files at TIDA-00639.

# 5.3 PCB Layout Recommendations

High-voltage PCB layouts require special consideration. Take care to add space between the traces that are several volts apart. The PCB trace spacing used in this design meet the requirements specified in Table 6-1 of the IPC-2221 standard for external conductors with conformal coating over assembly. The IPC-2221 "Generic Standard on Printed Board Design" specifies spacing requirements for various types of PCB construction, coating, and applications. Consequently, there must be sufficient spacing between the components within the high-voltage portion of the board, which is physically separated from the low-voltage portion of the board (see Figure 14).

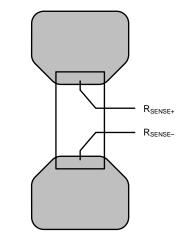

The layout of the current-sensing resistor is critical (see Figure 25). Connect the input pins (RSENSE+ and RSENSE-) to the sensing resistor using a Kelvin connection or a four-wire connection. These connection techniques ensure that only the current-sensing resistor impedance is detected between the input pins. Poor routing of the current-sensing resistor commonly results in additional resistance present between the input pins. Given the very low resistance of the current-sensing resistor, any additional high-current carrying impedance causes significant measurement errors.

Copyright © 2016, Texas Instruments Incorporated

#### Figure 25. Kelvin Connected Shunt Resistor

The PCB carries high current through the input terminals (J11-1, J18-1, J12-1, J17-1) to the shunt resistor and out through the output terminals (J11-2, J18-2, J12-2, J17-2). The traces carrying the high current were created with polygon pours and the trace widths were maximized.

Placing bypass capacitors close to the OPA333 and INA226 is also critical. This improves stability and noise immunity.

## 5.3.1 Layout Prints

To download the layout prints for each board, see the design files at TIDA-00639.

# 5.4 Altium Project

To download the Altium project files for each board, see the design files at TIDA-00639.

# 5.5 Gerber Files

To download the Gerber files for each board, see the design files at TIDA-00639.

# 5.6 Assembly Drawings

To download the assembly drawings for each board, see the design files at TIDA-00639.

# 6 References

- 1. Texas Instruments, Noise Analysis in Operational Amplifier Circuits, Application Report (SLVA043)

- 2. Texas Instruments, WEBENCH® Design Center (http://www.ti.com/webench)

# 7 About the Author

**KATELYN WIGGENHORN** is a systems and applications engineer in the Texas Instruments Grid Infrastructure team, focusing on renewable energy. Katelyn received her bachelor of science in electrical engineering from Villanova University.

# 8 General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

Always follow TI's setup and application instructions, including use of all interface components within their recommended electrical rated voltage and power limits. Always use electrical safety precautions to help ensure your personal safety and those working around you. Contact TI's Product Information Center http://support/ti./com for further information.

#### Save all warnings and instructions for future reference.

Failure to follow warnings and instructions may result in personal injury, property damage, or death due to electrical shock and burn hazards.

The term TI HV EVM refers to an electronic device typically provided as an open framed, unenclosed printed circuit board assembly. It is intended strictly for use in development laboratory environments, solely for qualified professional users having training, expertise and knowledge of electrical safety risks in development and application of high voltage electrical circuits. Any other use and/or application are strictly prohibited by Texas Instruments. If you are not suitable qualified, you should immediately stop from further use of the HV EVM.

- 1. Work Area Safety

- (a) Keep work area clean and orderly.

- (b) Qualified observer(s) must be present anytime circuits are energized.

- (c) Effective barriers and signage must be present in the area where the TI HV EVM and its interface electronics are energized, indicating operation of accessible high voltages may be present, for the purpose of protecting inadvertent access.

- (d) All interface circuits, power supplies, evaluation modules, instruments, meters, scopes and other related apparatus used in a development environment exceeding 50Vrms/75VDC must be electrically located within a protected Emergency Power Off EPO protected power strip.

- (e) Use stable and nonconductive work surface.

- (f) Use adequately insulated clamps and wires to attach measurement probes and instruments. No freehand testing whenever possible.

- 2. Electrical Safety

As a precautionary measure, it is always a good engineering practice to assume that the entire EVM may have fully accessible and active high voltages.

- (a) De-energize the TI HV EVM and all its inputs, outputs and electrical loads before performing any electrical or other diagnostic measurements. Revalidate that TI HV EVM power has been safely deenergized.

- (b) With the EVM confirmed de-energized, proceed with required electrical circuit configurations, wiring, measurement equipment connection, and other application needs, while still assuming the EVM circuit and measuring instruments are electrically live.

(c) After EVM readiness is complete, energize the EVM as intended.

# WARNING: WHILE THE EVM IS ENERGIZED, NEVER TOUCH THE EVM OR ITS ELECTRICAL CIRCUITS AS THEY COULD BE AT HIGH VOLTAGES CAPABLE OF CAUSING ELECTRICAL SHOCK HAZARD.

- 3. Personal Safety

- (a) Wear personal protective equipment (for example, latex gloves or safety glasses with side shields) or protect EVM in an adequate lucent plastic box with interlocks to protect from accidental touch.

## Limitation for safe use:

EVMs are not to be used as all or part of a production unit.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ('TI') reference designs are solely intended to assist designers ("Designer(s)") who are developing systems that incorporate TI products. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.

TI's provision of reference designs and any other technical, applications or design advice, quality characterization, reliability data or other information or services does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such reference designs or other items.

TI reserves the right to make corrections, enhancements, improvements and other changes to its reference designs and other items.

Designer understands and agrees that Designer remains responsible for using its independent analysis, evaluation and judgment in designing Designer's systems and products, and has full and exclusive responsibility to assure the safety of its products and compliance of its products (and of all TI products used in or for such Designer's products) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to its applications, it has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any systems that include TI products, Designer will thoroughly test such systems and the functionality of such TI products as used in such systems. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equivalent classifications outside the U.S.

Designers are authorized to use, copy and modify any individual TI reference design only in connection with the development of end products that include the TI product(s) identified in that reference design. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of the reference design or other items described above may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS AND OTHER ITEMS DESCRIBED ABOVE ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNERS AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS AS DESCRIBED IN A TI REFERENCE DESIGN OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TI's standard terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products. Additional terms may apply to the use or sale of other types of TI products and services.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated