## TI Designs 12-Gbps BERT Board Reference Design

# TEXAS INSTRUMENTS

#### **Design Overview**

The DS125DF1610 BERT board is a small, convenient, and low-cost alternative to a traditional bit error rate tester (BERT). The onboard DS125DF1610 retimer allows for eight channels of pattern generation and eight channels of pattern checking, exceeding the capabilities of most standard BERTs. The retimer locks to an input clock signal from either the onboard LMX2581 clock or an external reference clock and generates a pseudo-random binary sequence. The DS125DF1610 can lock to any frequency in the 9.8- to 12.5-Gbps range or any divide-by-2, divide-by-4, or divide-by-8 sub-multiples of this range.

## **Design Features**

- Eight Pattern Generation Channels

- Eight Pattern Checking Channels

- Onboard Low-Jitter Reference Clocks

- Optional External Reference Clock Inputs

- Onboard USB-to-I<sup>2</sup>C for Easy Device Programming

- Status Display LEDs

#### **Featured Applications**

- Pattern Generation up to 12.5 Gbps

- Pattern Checking up to 12.5 Gbps

#### **Design Resources**

| TIDA-00426  | Design Folder  |

|-------------|----------------|

| DS125DF1610 | Product Folder |

| LMX2581     | Product Folder |

| TCA6424     | Product Folder |

| MSP430F5529 | Product Folder |

|             |                |

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

Key System Specifications

## 1 Key System Specifications

## Table 1. Key System Specifications

| PARAMETER          | SPECIFICATIONS                                                                                                | DETAILS                                                   |

|--------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Data rates         | DS110DF1610: 8.5 Gbps to 11.3 Gbps<br>DS125DF1610: 9.8 Gbps to 12.5 Gbps<br>DS150DF1610: 12.5 Gbps to 15 Gbps | Divide-by-2 , divide-by-4, and divide-by-8 also supported |

| Output amplitude   | 350 mVppd to 1002 mVppd                                                                                       | The step size is approximately 50 mVppd                   |

| FIR                | Positive and negative precursor and postcursor, as well as de-emphasis                                        | —                                                         |

| Data patterns      | PRBS7, PRBS9, PRBS15, and PRBS31                                                                              | —                                                         |

| Input equalization | Auto-adapting CTLE and DFE                                                                                    | —                                                         |

## 2 System Description

The 12-Gbps BERT board is a small, convenient, and low-cost alternative to a traditional bit error rate tester (BERT). The onboard DS125DF1610 retimer allows for eight channels of pattern generation and eight channels of pattern checking, exceeding the capabilities of most standard BERTs. The retimer locks to an input clock signal from either the onboard LMX2581 frequency synthesizer or an external reference clock and generates one of four pseudo-random bit sequences: PRBS7, PRBS9, PRBS15 or PRBS31. The DS125DF1610 can lock to any frequency in the 9.8- to 12.5-Gbps range or any divide-by-2, divide-by-4, or divide-by-8 sub-multiples of this range.

Three pin-compatible parts may be used to generate and check different data rates:

- DS150DF1610 device allows for 12.5 Gbps to 15 Gbps (plus divide-by-2, divide-by-4, or divide-by-8 sub-rates)

- DS125DF1610 device allows for 9.8 Gbps to 12.5 Gbps (plus divide-by-2, divide-by-4, or divide-by-8 sub-rates)

- DS110DF1610 device allows for 8.5 Gbps to 11.3 Gbps (plus divide-by-2, divide-by-4, or divide-by-8 sub-rates)

## 2.1 DS125DF1610

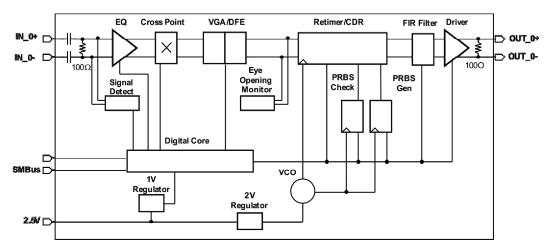

The DS125DF1610 is a sixteen-channel, multi-rate retimer with integrated signal conditioning features. The device has built-in pattern generation and checking capabilities as well as four  $4 \times 4$  non-blocking crosspoint switches.

In this design, two quads (four-channel blocks) of the retimer are used for pattern generation and two quads are used for pattern checking. Each of the pattern generation quads can lock to either an external clock input or an input from the onboard frequency synthesizer (the LMX2581 in this design). The locked inputs can be broadcasted to one or more of the quad's outputs and transformed into a pseudorandom binary sequence (PRBS) signal. The DS125DF1610 can output the following patterns: PRBS7, PRBS9, PRBS15, PRBS31, and a 16-bit custom pattern. The other two quads are used to lock to an input signal and check for bit errors.

Figure 1. DS125DF1610 Simplified Data Path Diagram

3

System Description

System Description

www.ti.com

## 2.2 LMX2581

The LMX2581 is a low-noise, wideband frequency synthesizer that integrates a delta-sigma ( $\Delta\Sigma$ ) fractional N PLL, multiple core voltage-controlled oscillator (VCO), programmable output divider, and two differential output buffers. The VCO frequency range is from 1880 MHz to 3760 MHz and can be sent directly to the output buffers or divided down by even values from 2 to 38.

In this design, the LMX2581 device provides a low-jitter input onto which the DS125DF1610 device locks. This input is a sub-multiple of the desired lock frequency. For example, for a 10.3125-Gbps signal (5.156-GHz Nyquist), the LMX2581 device may be set to output 5.156 GHz / 2 = 2.578 GHz or 5.156 GHz / 4 = 1.289 GHz.

## 2.3 TCA6424A

This 24-bit input/output (I/O) expander for the two-line bidirectional bus (I<sup>2</sup>C) has been designed to provide general-purpose remote I/O (GPIO) expansion for a microcontroller (MCU) through the I<sup>2</sup>C interface.

In this design, the TCA6424 device provides more GPIOs for the onboard MSP430<sup>™</sup> MCU from Texas Instruments (TI). These GPIOs are used for various light-emitting diode (LED) indicators for the purpose of showing which pattern generator channels have been enabled and the error status of the pattern-checking channels.

## 2.4 MSP430F5529

The MSP430F5529 is an ultra-low-power MCU with integrated USB and PHY, which supports USB 2.0 as well as many other features.

In this design, the MSP430 MCU provides a USB-to-I<sup>2</sup>C and a USB-to-MICROWIRE interface to program the devices mentioned in *Section 2.1*, *Section 2.2*, and *Section 2.3*. The USB2ANY firmware is used to interface with the device graphical user interfaces (GUIs).

3

Copyright © 2016, Texas Instruments Incorporated

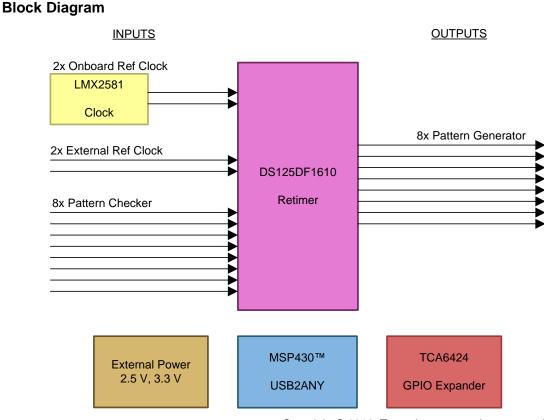

Figure 2. TIDA-00426 Block Diagram

## 3.1 Highlighted Products

The TIDA-00426 TI Design features the following devices:

- DS125DF1610

- LMX2581

- TCA6424A

- MSP430F5529

For more information on each of these devices, see their respective product folders at www.ti.com.

## 3.1.1 DS125DF1610

- Pin-compatible family

- DS150DF1610: 12.5 Gbps to 15 Gbps

- DS125DF1610: 9.8 Gbps to 12.5 Gbps

- DS110DF1610: 8.5 Gbps to 11.3 Gbps

- 4×4-analog crosspoint switch for each quad

- Fully-adaptive continuous-time linear equalizer (CTLE)

- Self-tuning decision feedback equalizer (DFE), with optional continuous adaption

- Configurable VGA

- Adjustable transmit VOD

- Adjustable three-tap transmit FIR filter

- On-chip AC coupling on receive inputs

Block Diagram

- Locks to half, quarter, and eighth data rates

- On-chip eye monitor(EOM), PRBS checker, pattern generator

- Programmable output polarity inversion

- Input signal detection, clock-and-data recovery (CDR) lock detection

- Single 2.5-V ±5% power supply

- SMBus-based register configuration

- 15-mm × 15-mm, 196-pin FCBGA package

- Operating temperature range : -20°C to 85°C

## 3.1.2 LMX2581

- Output frequency from 50 MHz to 3760 MHz

- Output frequency from 50 MHz to 3760 MHz

- Phase detector frequency up to 200 MHz

- Supports fractional and integer modes

- -229 dBc/Hz normalized PLL phase noise

- -120.8 dBc/Hz normalized PLL 1/f noise

- –137 dBc/Hz VCO phase noise at 1 MHz offset for a 2.5-GHz carrier

- 100-fs RMS jitter in integer mode

- Programmable fractional modulator order

- Programmable fractional denominator

- Three-wire serial interface and readback

- Single-supply voltage from 3.15 V to 3.45 V

## 3.1.3 TCA6424A

- Operating power-supply voltage range of 1.65 V to 5.5 V

- Allows bidirectional voltage-level translation and GPIO expansion between:

- 1.8-V SCL/SDA and 1.8-V, 2.5-V, 3.3-V, or 5-V P port

- 2.5-V SCL/SDA and 1.8-V, 2.5-V, 3.3-V, or 5-V P port

- 3.3-V SCL/SDA and 1.8-V, 2.5-V, 3.3-V, or 5-V P port

- 5-V SCL/SDA and 1.8-V, 2.5-V, 3.3-V, or 5-V P port

- I<sup>2</sup>C-to-parallel port expander

- Low standby current consumption of 1 µA

- 5-V tolerant I/O ports

- 400-kHz fast I<sup>2</sup>C bus

- Input and output configuration registers

- Polarity inversion register

٠

#### 3.1.4 MSP430F5529

- Low supply voltage range: 3.6 V down to 1.8 V

- Ultra-low-power consumption

- Active mode (AM):

- All system clocks active:

- 290 µA/MHz at 8 MHz, 3 V, flash program execution (typical)

- 150 µA/MHz at 8 MHz, 3 V, RAM program execution (typical)

- Shutdown mode (LPM4.5):

- 0.18 µA at 3 V (typical)

- Wake up from standby mode in 3.5 µs (typical)

- Flexible power management system

- Fully-integrated low-dropout regulator (LDO) with programmable regulated core supply voltage

- Supply voltage supervision, monitoring, and brownout

- Full-speed universal serial bus (USB)

- Integrated USB-PHY

- Integrated 3.3-V and 1.8-V USB power system

- Integrated 3.3-V and 1.8-V USB power system

- Eight input and eight output endpoints

#### 4 System Design Theory

The 12-Gbps BERT board uses a DS125DF1610 retimer as an eight-channel pattern generator and checker. For the retimer to be able to perform these functions, the retimer requires a clean, low-jitter source for the CDR to lock to, which is provided by the LMX2581 device or from an external source. Locking requires a clock equal to the Nyquist frequency of the desired data rate divided by 2, 4, or 8.

To optimize the output signal quality, the differential traces have been carefully designed to stay at a  $100-\Omega$  differential characteristic impedance to minimize reflections. Megtron6 material has also been used to minimize insertion loss from the board itself.

#### 5 Getting Started Hardware

#### 5.1 Board

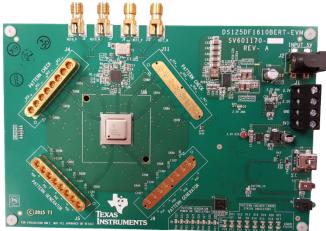

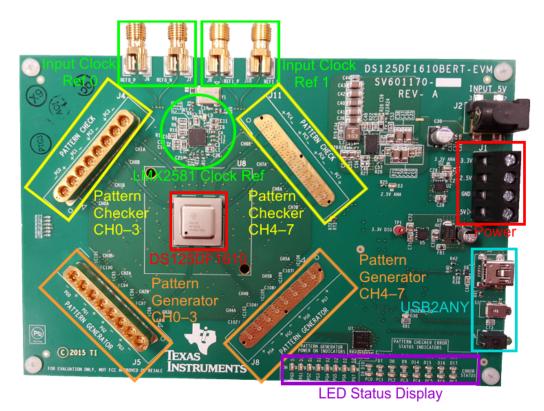

Figure 3 shows the important sections of the board. The input references for the DS125DF1610 device are highlighted in green. These references either come from the onboard LMX2581 or from the SMA connectors. The *Input Clock Ref 0* section can only be used for pattern generator channels 0 through 3 and the *Input Clock Ref 1* section can only be used for pattern generator channels 4 through 7.

The eight-pattern checking inputs are highlighted in yellow. The connectors used are Huber Suhner MXP connectors which require a mate that adapts into SMA connectors. Note that the right side (channels 4 through 7) is not populated in Figure 3.

Figure 3. DS125DF1610BERT Top View

## 5.2 Board Power Up

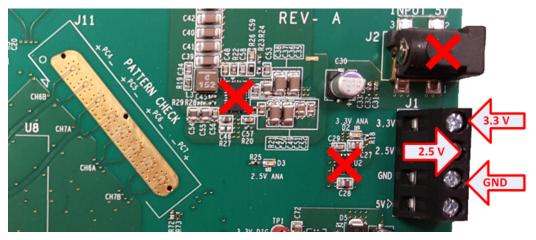

Figure 4 shows where to connect power to the terminal block of the board. Two voltages are required: 2.5 V for the DS125DF1610, device and 3.3 V for the LMX2581 device. The MSP430 MCU and TCA6424A device are powered from the USB port. If not using the LMX device as a reference to the DS125DF1610 device (and if only using external clocks in their place), the 3.3-V supply is not required. Note that this design does not have an on-board regulator option (U2 and U3 are not populated and not operational for this board design). Figure 4 shows how external power must be supplied.

Figure 4. DS125DF1610 Power Inputs

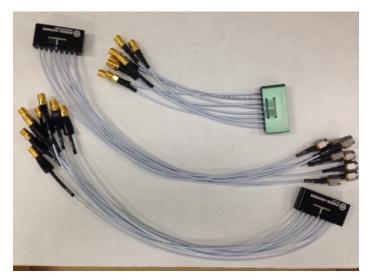

## 5.3 Cable Assemblies

The design EVM uses Huber+Suhner 1×8-MXP cable assemblies (see Figure 5). These assemblies are required to connect the pattern-generator outputs and pattern-checker inputs.

Figure 5. Huber+Suhner 1x8-MXP Cable Assemblies

Getting Started Hardware

#### 6 Getting Started Software

#### 6.1 CodeLoader 4

Install the *CodeLoader 4* software from the following link: http://www.ti.com/tool/CODELOADER. This software allows for programming of the LMX2581 device. When the board has been plugged in and this software is running, the software may ask to update the firmware of the MSP430 MCU. Follow through the prompts and update the firmware. After having updated, in the *Port Setup* tab, a device called USB2ANY appears in the drop-down menu (see Figure 6.) Clicking the *Identify* button makes the LED D9 blink to ensure that communication is in place.

| 🔛 LMX2581                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Eile Keyboard Controls Select Device Options Mode LPT/USB Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |

| Port Setup Registers Bits/Pins BurstMode PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |

| Communication Mode       Current of USB USB2ANY - 9802306F12000200 ▼ Identify         IPT For Setup       Port Address         @ LPT Por Setup       Port Address         @ LPT C LPT2       LPT3         C Data       Ground         B Data Setup       Address Conflict         Data Setup       C Data C 5 C 6 C 7 C 8 C 10 C 11 C 12 C 14         C Data Setup       C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 10 C 11 C 12 C 14         Data Set       C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 10 C 11 C 12 C 14         EE Her       Setup         C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 10 C 11 C 12 C 14         EE Her       Setup         C 1 C 2 C 3 C 4 C 5 C 9 C 7 C 8 C 10 C 11 C 12 C 14         EE       C 1 C 2 C 3 C 4 C 5 C 9 C 7 C 8 C 10 C 11 C 12 C 14         THIGGER       C 1 C 2 C 3 C 4 C 5 C 9 C 7 C 8 C 10 C 11 C 12 C 14         THIGGER       C 1 C 2 C 3 C 4 C 5 C 9 C 7 C 8 C 10 C 11 C 12 C 14 | 2                      |

| COMM Mode: USB Changed communications mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 矏 Texas Instruments // |

Figure 6. CodeLoader 4—Port Setup

Ensure that the LMX2581 has been selected by clicking the *Select Device* option in the *File* menu followed by *PLL* + *VCO* and *LMX2591*, as Figure 7 shows.

| LMX2581                          | a Cont and and a second    | And And Am                       | An An An An An                         |                        |

|----------------------------------|----------------------------|----------------------------------|----------------------------------------|------------------------|

| File Keyboard Controls           | Select Device Options Mode | <u>L</u> PT/USB <u>H</u> elp     |                                        |                        |

| Port Setup Regist                | VCO >                      | PLL                              |                                        |                        |

| Communication Mode<br>C LPT © US |                            |                                  | USB2ANY Port Setup<br>Clock Other Pins |                        |

| - LPT Port Setup                 | PLL - Fractional >         |                                  |                                        |                        |

| Port Address                     | PLL + VCO >                |                                  |                                        |                        |

| C LPT1 C LPT2                    | Transceiver                |                                  | Reserved                               |                        |

| Pin Configuration                | Clock Conditioners         | LMX2541SQ2690E                   | 10/14 Pin Connector ( Top View )       |                        |

| Clock Bit                        |                            | LMX2541SQ3030E<br>LMX2541SQ3320E |                                        |                        |

|                                  | 4 0 5 0 6 0 7 @ 8 0 1      | LMX2541SQ3740E                   | Pin 1                                  |                        |

| Data Bit                         | 4 0 5 0 6 0 7 0 8 0 1      | LMX2531LQ1146E                   |                                        |                        |

|                                  | 4, 3, 0, 7, 0, 1           | LMX2531LQ1226E                   |                                        |                        |

| LE Bit<br>C 1 @ 2 C 3 C          | 4 0 5 0 6 0 7 0 8 0 1      | LMX2531LQ1312E                   |                                        |                        |

| BUFEN                            |                            | LMX2531LQ1415E                   |                                        |                        |

| 0102030                          | 4 0 5 0 9 0 7 • 8 0        | LMX2531LQ1500E                   |                                        |                        |

| CE                               |                            | LMX2531LQ1515E                   |                                        |                        |

| 0102030                          | 4 C 5 C 9 C 7 C 8 @        | LMX2531LQ1570E                   |                                        |                        |

| TRIGGER                          | 4 @ 5 @ 9 @ 7 @ 8 @        | LMX2531LQ1650E                   |                                        |                        |

| 0102030                          | 4.00007080                 | LMX2531LQ1700E                   |                                        |                        |

|                                  |                            | LMX2531LQ1778E                   |                                        |                        |

|                                  |                            | LMX2531LQ1742                    |                                        |                        |

|                                  |                            | LMX2531LQ1910E                   |                                        |                        |

|                                  |                            | LMX2531LQ2080E                   |                                        |                        |

|                                  |                            | LMX2531LQ2265E                   |                                        |                        |

|                                  |                            | LMX2531LQ2570E                   |                                        |                        |

|                                  |                            | LMX2531LQ2820E                   |                                        |                        |

|                                  |                            | LMX2531LQ3010E                   |                                        |                        |

|                                  |                            | LMX2581                          |                                        |                        |

|                                  |                            | W                                | 1                                      |                        |

|                                  |                            |                                  |                                        |                        |

|                                  |                            |                                  |                                        |                        |

| COMM Mode: USB Chang             | ged communications mode.   |                                  |                                        | 🜵 Texas Instruments // |

Figure 7. CodeLoader 4—Select Device

When the device has been selected, navigate to the *File* menu and then the *Restore* option and select one of the files provided with the TI Design download. These files provide the necessary frequencies to lock to common data rates. Alternatively, the device may be manually configured by navigating to the *Bits/Pins* tab and *PLL* tab.

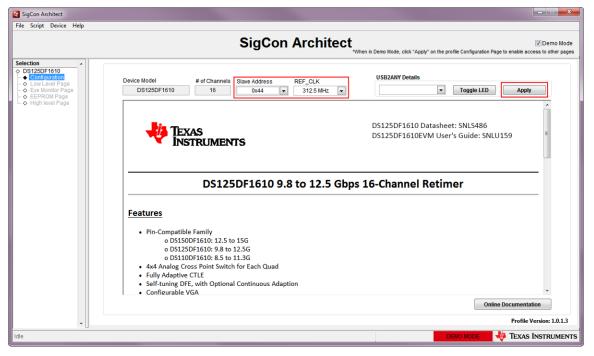

## 6.2 SigCon Architect

The SigCon Architect software can be downloaded from the following location:

http://www.ti.com/tool/sigconarchitect. This software allows programming for the DS125DF1610 device. After plugging the board in and running this software, the software may ask to update the firmware of the MSP430 MCU. Follow through the prompts and update the firmware. Run the device profile installer provided and select *Configuration* tab underneath DS125DF1610 in the *Selection* window (see Figure 8). Select a *Slave Address of 0x44* and *REF\_CLOCK* of 312.5 MHZ in the drop-down fields and click the *Apply* button.

Getting Started Software

www.ti.com

Figure 8. SigCon Architect—Configuration

Select the *Low Level Page* option in the left-side *Selection* window and click the *Load Config* button, which Figure 9 highlights with a red box. Load one of the configuration files provided based on the desired configuration (see Table 2).

| Table 2. | Configuration | Files |

|----------|---------------|-------|

|----------|---------------|-------|

| FILE NAME          | CLOCK INPUT                                        | DATA RATE    | PATTERN GENERATOR<br>OUTPUT(S) |

|--------------------|----------------------------------------------------|--------------|--------------------------------|

| LMX_10G_Config.cfg | LMX2581                                            | 10.3125 Gbps | PRBS31: All channels           |

| LMX_12G_Config.cfg | LMX2581                                            | 12 Gbps      | PRBS31: All channels           |

| EXT_10G_Config.cfg | External Input<br>Clock Ref 0 Input<br>Clock Ref 1 | 10.3125 Gbps | PRBS31: All channels           |

| EXT_12G_Config.cfg | External Input<br>Clock Ref 0 Input<br>Clock Ref 1 | 12 Gbps      | PRBS31: All channels           |

|                             |                       |         |         | Si       | gC   | on /     | ٩r  | chitect            | hen in Demo Mode | e, click "Apply" on | the profile Configurati | ion Page to enable access | Demo<br>to other |

|-----------------------------|-----------------------|---------|---------|----------|------|----------|-----|--------------------|------------------|---------------------|-------------------------|---------------------------|------------------|

| ction                       |                       |         |         |          |      |          |     |                    |                  |                     |                         |                           |                  |

| S125DF1610<br>Configuration | Block Select          |         |         |          |      |          |     |                    |                  |                     |                         |                           |                  |

| Low Level Page              | Rx/Tx 3B              |         | _       |          |      | C - H    |     |                    |                  |                     |                         |                           |                  |

| Eye Monitor Page            | Register Map          |         | -       | Expand A |      | Collapse | All |                    |                  |                     |                         |                           |                  |

| EEPROM Page                 | Block / Register Name | Address | Default | Mode     | Size | Data     | ^   |                    | Mask F           | Register Data       |                         | Mask Val                  | ue               |

| High level Page             | Shared Registers      |         |         |          |      |          | E   | Current Address    |                  |                     |                         | × F                       | F                |

|                             | 0x00                  | 0x00    | 0x00    | R        | 8    | 0x00     | _   | × 0                |                  |                     |                         |                           |                  |

|                             | 0x01                  | 0x01    | 0x71    | R        | 8    | 0x71     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x02                  | 0x02    | 0x20    | R/W      | 8    | 0x40     |     | Data               |                  |                     |                         |                           |                  |

|                             | 0x03                  | 0x03    | 0x00    | R/W      | 8    | 0x00     |     | × 0                |                  |                     |                         |                           |                  |

|                             | 0x04                  | 0x04    | 0x01    | R/W      | 8    | 0x01     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x05                  | 0x05    | 0x18    | R/W      | 8    | 0x08     |     | Write Register     |                  |                     |                         |                           |                  |

|                             | 0x06                  | 0x06    | 0x00    | R/W      | 8    | 0x00     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x07                  | 0x07    | 0x00    | R/W      | 8    | 0x05     |     | Broadcast          |                  |                     |                         |                           |                  |

|                             | 0x08                  | 0x08    | 0x00    | R        | 8    | 0x00     |     | Read Register      | Field December   | len.                |                         |                           |                  |

|                             | 0x09                  | 0x09    | 0x00    | R        | 8    | 0x00     |     | Read Register      | Field Descript   |                     |                         |                           |                  |

|                             | 0x0A                  | 0x0A    | 0x01    | R/W      | 8    | 0x01     |     | Read All           | Fie              | ld Name             | Access                  | Description               |                  |

|                             | 0x0B                  | 0x0B    | 0x00    | R/W      | 8    | 0x40     |     | Read All           | r                |                     |                         |                           |                  |

|                             | 0x0C                  | 0x0C    | 0x00    | R/W      | 8    | 0x00     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x0D                  | 0x0D    | 0x00    | R/W      | 8    | 0x5D     |     | Reset Device       |                  |                     |                         |                           |                  |

|                             | 0x0E                  | 0x0E    | 0x00    | R/W      | 8    | 0x00     |     | the set better     |                  |                     |                         |                           |                  |

|                             | 0x0F                  | 0x0F    | 0xFF    | R/W      | 8    | 0xFF     |     | Load Config        | -                |                     |                         |                           |                  |

|                             | 0x10                  | 0x10    | 0xFF    | R/W      | 8    | 0xFF     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x11                  | 0x11    | 0x00    | R        | 8    | 0x00     |     | Save Config        |                  |                     |                         |                           |                  |

|                             | Global Registers      |         |         |          | 1    |          |     |                    |                  |                     |                         |                           |                  |

|                             | 0xFC                  | 0xFC    | 0x00    | R/W      | 8    | 0x80     |     | Note: Load Config  |                  |                     |                         |                           |                  |

|                             | 0xFD                  | 0xFD    | 0x00    | R/W      | 8    | 0x00     |     | will Overwrite all |                  |                     |                         |                           |                  |

|                             | 0xFE                  | 0xFE    | 0x03    | R        | 8    | 0x03     |     | Registers.         |                  |                     |                         |                           |                  |

|                             | 0xFF                  | 0xFF    | 0x00    | R/W      | 8    | 0x00     |     |                    | -                |                     |                         |                           |                  |

|                             | E RX/TX 0A            |         |         |          | 1    |          |     |                    |                  |                     |                         |                           |                  |

|                             | 0x00                  | 0x00    | 0x00    | R/W      | 8    | 0x00     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x01                  | 0x01    | 0x00    | R        | 8    | 0x00     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x02                  | 0x02    | 0x00    | R        | 8    | 0x00     |     |                    |                  |                     |                         |                           |                  |

|                             | 0x03                  | 0x03    | 0x00    | RW       | 8    | 0x00     |     |                    |                  |                     |                         |                           |                  |

|                             |                       |         |         |          |      |          |     |                    |                  |                     |                         |                           |                  |

Figure 9. SigCon Architect—Low-Level Page

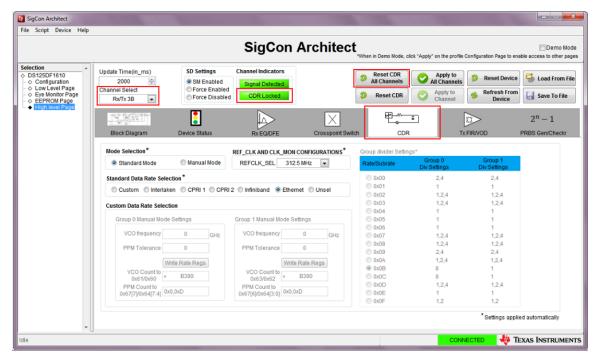

After having completed the configuration, select the *High Level Page* option in the left-side *Selection* window and then click the *CDR* tab (highlighted with a red box in Figure 10). Click the *Reset CDR All Channels* button and select a channel such as *RX/TX 3B*, which maps to the pattern generator inputs that Table 3 lists. If the input frequency has been set correctly, the channel indicator displays *CDR Locked*. This tab may also be used to select custom data rates.

Figure 10. SigCon Architect—CDR Config

#### Table 3. Channel Map

| PATTERN GENERATOR<br>CHANNEL | RETIMER CHANNEL | PATTERN CHECKER<br>CHANNEL | RETIMER CHANNEL |

|------------------------------|-----------------|----------------------------|-----------------|

| PG0                          | CH3B (Quad 1)   | PC0                        | CH0A (Quad 0)   |

| PG1                          | CH2A (Quad 1)   | PC1                        | CH1B (Quad 0)   |

| PG2                          | CH2B (Quad 1)   | PC2                        | CH0B (Quad 0)   |

| PG3                          | CH3A (Quad 1)   | PC3                        | CH1A (Quad 0)   |

| PG4                          | CH4A (Quad 2)   | PC4                        | CH6B (Quad 3)   |

| PG5                          | CH4B (Quad 2)   | PC5                        | CH7A (Quad 3)   |

| PG6                          | CH5B (Quad 2)   | PC6                        | CH6A (Quad 3)   |

| PG7                          | CH5A (Quad 2)   | PC7                        | CH7B (Quad 3)   |

Select the *TX FIR/VOD* tab (see Figure 11) and adjust the FIR taps as required. Ensure that the correct channel has been selected and click the *Apply to Channel* button.

| SigCon Architect        |                                                                          | ALLAND I                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                 |                                                                    | 1 / 1111                                                                               |                                                                          |

|-------------------------|--------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| File Script Device Help |                                                                          | Si                                                     | igCon Ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | chitect                                                                                                                                                         | Demo Mode, click "Apply"                                           | on the profile Configurati                                                             | Demo Mode                                                                |

| Selection               | Update Time(in_ms)<br>2000<br>Channel Select<br>RoTx 3B<br>Block Dlagram | SM Enabled     Force Enabled     Force Disabled     CO | A locked<br>R Locked<br>R Locked<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison<br>Comparison | Crosspoint Switch<br>Transmitter FIR/VOD Se<br>Pre Cursor Tap<br>Main Cursor<br>Post Cursor Tap<br>Co efficient abs Sum<br>DEM<br>DRV_SEL_VOD<br>Calculated VOD | eset CDR<br>IChannels<br>Reset CDR<br>CDR<br>ettings<br>Broadcast? | Apply to<br>UChannel<br>Apply to<br>Channel<br>Read Taps<br>Set Taps<br>Normalize Taps | eset Device Ucad From File<br>efresh From Levice Save To File<br>$2^n-1$ |

| Idle                    |                                                                          |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                 |                                                                    | CONNECTED                                                                              | 📕  Texas Instruments                                                     |

Figure 11. SigCon Architect—TX FIR/VOD Config

To modify the pattern, select the *PRBS Gen/Checker* tab for the desired channel and modify the pattern type or polarity. The *Enable* button turns this feature on or off (see Figure 12).

| I SigCon Architect                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Script Device Help                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                          | SigCon Architect  When in Demo Mode, click "Apply" on the profile Configuration Page to enable access to other pages                                                                                                                                                                                                                                                                                                                                                                                                         |

| Selection         ↓         Update Time(n_ms)         SD Setting           ○ Configuration         ○ Configuration         ○ Configuration         ○ SM Enal         ○ SM Enal         ○ Force En           ○ Eye Montor Page         ○ EPROM Page         ○ Force D         ○ Force D         ○ Force D | Bilded     Signal Detected       Signal Detected     All Channels       Channels     All Channels                                                                                                                                                                                                                                                                                                                                                                                                                            |

| High level Page      Block Diagram      Device Status                                                                                                                                                                                                                                                    | s Rx EQUDFE Crosspoint Switch CDR Tx FIRNOD 2 <sup>n</sup> - 1 PRBS Gen/Checkr                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PRBS Generator Configurations<br>Enable<br>Patern Type Custom Pattern<br>PRSS 7 * b 0<br>Polarity<br>Non - Invert *                                                                                                                                                                                      | PRBS Checker           Patern Type         Polarity           User Defined         Non-Invert           0         0           Capture Period         Mins           Finite         0           1         Tum ON*           1         Tum ON*           1         Error Count           2         Finite           0         4:00:00_500 PM           3:59:59:000 PM         3:59:59:500 PM           12/31/1903         12/31/1903           12/31/1903         12/31/1903           Error Count Graph         Clear Checker |

| Idle                                                                                                                                                                                                                                                                                                     | CONNECTED 👋 TEXAS INSTRUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Figure 12. SigCon Architect—PRBS Gen Config

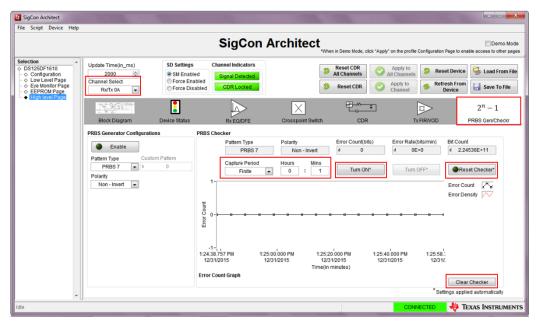

To check the bit error rate, ensure that one of the pattern generator outputs has been connected to one of the pattern checker inputs through a channel. After performing this step, select the pattern checker channel and click the *Reset CDR* button so that it locks. If the CDR does not lock, the channel may be too long or there may be an issue with the connections. Select the *PRBS Gen/Checker* tab and edit the capture period to a finite time or infinite amount of time (see Figure 13). Click the *Reset Checker* button to ensure that any errors from previous tests have been erased, and click the *Turn On* button to begin error checking. The PRBS pattern is automatically detected; if it has detected the wrong pattern, too many bit errors must be occurring. Try lowering the amount of insertion loss in the signal path and double check that the input has been configured correctly. The plot displays the number of errors over time. Click the *Clear Checker* button to clear the graph.

Figure 13. SigCon Architect—PRBS Checker Config

Getting Started Software

www.ti.com

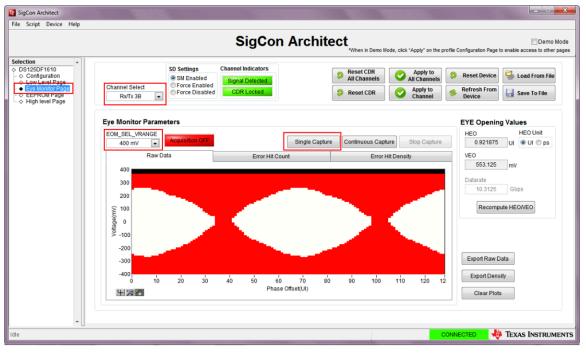

To evaluate the input signal for a given channel, select the *Eye Monitor Page* in the left-side *Selection* window. Select the desired channel and *EOM\_SEL\_VRANGE* (400 mV recommended for large inputs) and click the *Single Capture* button (see Figure 14). The graph displays the eye diagram and the horizontal eye opening (HEO) and vertical eye opening (VEO) values are also displayed, which are very useful parameters to determine the quality of the input. If the eye is very small or closed, the FIR taps at the output may be changed to compensate for insertion loss.

Figure 14. SigCon Architect—Eye Monitor Page

#### 7 Test Setup

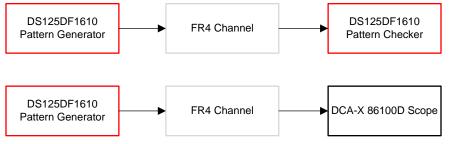

As Figure 15 shows, this board was tested with two different configurations. The first configuration is a simple loopback configuration where the DS125DF1610 device checks for bit errors for a given FR4 channel. In the second configuration, the DS125DF1610 device was connected to an oscilloscope. *Section 8* shows the oscilloscope screen captures.

Figure 15. Test Setups

Test Setup

TIDUBU5-May 2016

Test Data

#### 8 Test Data

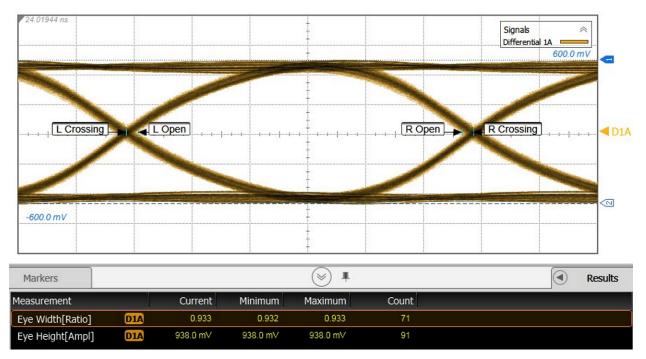

## 8.1 Eye Diagram

Figure 16 shows the output of one of the PRBS generator channels with no channel other than the board trace and cable. The pattern generator was configured for a 10.3125-Gbps signal with 1.2-Vppd and PRBS7 output, as well as a precursor tap of –2 and postcursor tap of –5.

Figure 16. PRBS7 Eye Diagram

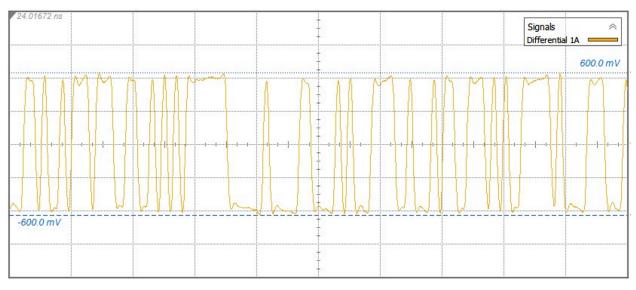

## 8.2 Time Domain Signal

Figure 17 shows the time domain signal of one of the PRBS generator channels with no channel other than the board trace and cable. The pattern generator is configured for a 10.3125-Gbps signal with 1.2 Vpp and PRBS7 output, as well as a precursor tap of –2 and postcursor tap of –5.

Figure 17. PRBS7 Time Domain Signal

## 9 Design Files

## 9.1 Schematics

To download the schematics, see the design files at TIDA-00426.

## 9.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00426.

## 9.3 PCB Layout Recommendations

The following guidelines must be followed when designing the layout:

- Decoupling capacitors must be placed as close to the VDD pins as possible. Placing them directly underneath the device is one option if the board design permits.

- High-speed differential signals must be tightly coupled, skew matched, and impedance controlled.

- Vias must be avoided when possible on the high-speed differential signals. When vias must be used, take care minimizing the via stub, either by transitioning through mostor all layers, or by back drilling.

- GND relief can be used beneath the high-speed differential signal pads to improve signal integrity by counteracting the pad capacitance.

- GND vias must be placed directly beneath the device connecting the GND plane attached to the device to the GND planes on other layers. This has the added benefit of improving thermal conductivity from the device to the board.

#### 9.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-00426.

## 9.4 Altium Project

To download the Altium project files, see the design files at TIDA-00426.

#### 9.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00426.

#### 9.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00426.

#### 10 Software Files

To download the software files, see the design files at TIDA-00426.

#### 11 References

- 1. Texas Instruments Application Report, Understanding EEPROM Programming or 10-G to 12.5-G Retimers, SNLA245, 2016

- 2. Texas Instruments Application Report, Selecting TI SigCon Devices for SFF-8431 SFP+ Applications, SNLA225, 2014

## 12 About the Author

**GUI BORBA** is an Applications Engineer at Texas Instruments, where he is responsible for defining, testing, and supporting high-speed signal conditioning and port management devices for data center switch, router, server, and wireless infrastructure systems. Gui earned his Master of Science in Electrical Engineering (MSEE) from Lehigh University in Bethlehem, Pennsylvania. In his spare time, Gui enjoys snowboarding, hiking, and swimming.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ('TI') reference designs are solely intended to assist designers ("Designer(s)") who are developing systems that incorporate TI products. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.

TI's provision of reference designs and any other technical, applications or design advice, quality characterization, reliability data or other information or services does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such reference designs or other items.

TI reserves the right to make corrections, enhancements, improvements and other changes to its reference designs and other items.

Designer understands and agrees that Designer remains responsible for using its independent analysis, evaluation and judgment in designing Designer's systems and products, and has full and exclusive responsibility to assure the safety of its products and compliance of its products (and of all TI products used in or for such Designer's products) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to its applications, it has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any systems that include TI products, Designer will thoroughly test such systems and the functionality of such TI products as used in such systems. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equivalent classifications outside the U.S.

Designers are authorized to use, copy and modify any individual TI reference design only in connection with the development of end products that include the TI product(s) identified in that reference design. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of the reference design or other items described above may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS AND OTHER ITEMS DESCRIBED ABOVE ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNERS AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS AS DESCRIBED IN A TI REFERENCE DESIGN OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TI's standard terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products. Additional terms may apply to the use or sale of other types of TI products and services.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated