**TIDA-00570 Test Results**

September 2015

# High Speed DLP Sub-system for Industrial 3D Printing and Digital Lithography

#### **About Test Results**

The High Speed DLP Sub-system for Industrial 3D Printing and Digital Lithography reference design utilizes Texas Instruments' DLP technology to deliver TI's highest performance combination of speed and resolution.

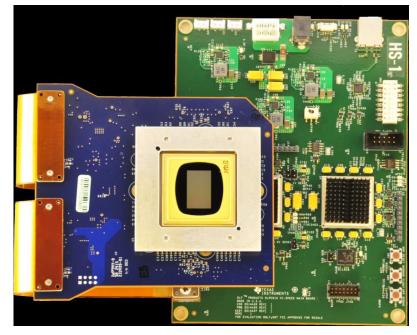

This design features multiple TI components, highlighted by the DLP9000X chipset, which incorporates the DLP9000X DMD and the DLPC910 controller. These associated devices and reference design were built and tested at TI to validate the design operation up through the 480MHz input data bus width, and that the DLPC910 could support streaming data at that data bus rate.

Figure 1 - Reference Design Boards

#### **Related Documentation From Texas Instruments**

DLP9000X Data Sheet: *DLP9000 Family of 0.9 WQXGA MVSP Type A DMDs*, TI literature number <u>DLPS036</u> DLPC910 Data Sheet: *DLPC910 Digital Controller for Advanced Light Control*, TI literature number <u>DLPS064</u> DLPR910 Data Sheet: *DLPR910 DLP*® *Configuration PROM*, TI literature number <u>DLPS065</u>

#### If You Need Assistance

Search for answers on the DLP and MEMS TI E2E Community support forums

## 1. Reference Design Goals

The goals for this reference design are two-fold: 1) to create a platform with which the DLP9000X-DLPC910 system level validation can be performed, and 2) to provide this reference design to potential customers looking to design their own Industrial 3D Printers and Digital Lithography end equipment for use as a starting point and a reference.

The reference design was created in a schematic capture tool, built, assembled, and tested. The design includes the following DLP components:

- DLPC910 Controller

- DLPR910 Configuration PROM

- DLP9000X High Speed WQXGA DMD

Other components such as power supply ICs were added to complete the reference design as necessary. The design also includes a Xilinx FPGA which is used to simulate an Application Processor that one might find in a Digital Lithography or 3D Print system. This Applications Processor is used to formulate and frame WQXGA resolution, binary (single bit) images to be sent to the inputs of the DLPC910. The DLPC910 subsequently provides this data and relevant control information to the DLP9000X DMD.

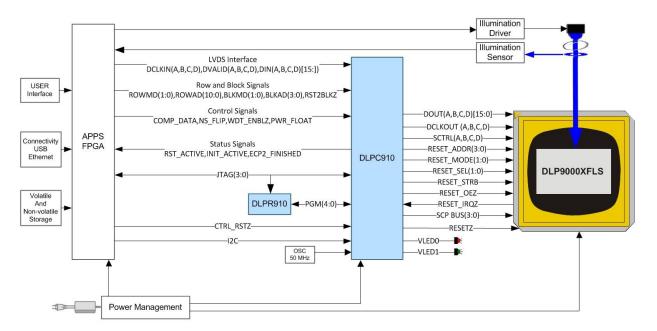

Figure 2 - Reference Design Block Diagram

In the reference design, data streams from the Applications Processor FPGA into the DLPC910 which provides the data to the DLP9000X DMD. The DLPC910 also translates control commands it receives from the Applications Processor into commands which the DMD

High Speed DLP Sub-system for Industrial 3D Printing and Digital Lithography

understands. The reference design uses test patterns in the Applications Processor to simulate the streaming of data to the DLPC910-DLP9000X as it would occur in a 3-D Printing or Digital Lithography application. In those applications, the Applications Processor FPGA would be replaced with a customer designed Application Processor and the data would relate to the actual exposures of polymers or resists as defined and implemented by the customer.

### 2. Setup and Hold Measurements

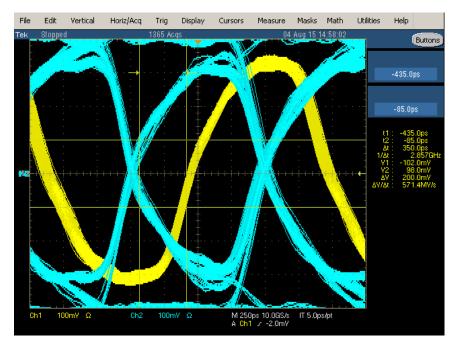

A Tektronix TDS6404 4GHz oscilloscope with P6330 differential probes was used to capture the DLP9000X input LVDS data bus timing. Multiple DMDs were used to make sure there were no measureable differences between devices which could affect input setup and hold timing.

Below is a picture of a DLP9000X input data bit setup time measurement while running the DCLK at 480MHz. The yellow signal is the DCLK from the DLPC910 and the blue signal shows multiple transitions both positive and negative for the Bus D data bit 6 from the DLPC910. Measurements were taken as close to the inputs of the DLP9000X as possible. The measured setup time of 350ps exceeds the datasheet required setup time of 200ps for the DLP9000X DMD.

Figure 3 - Measured Setup Time

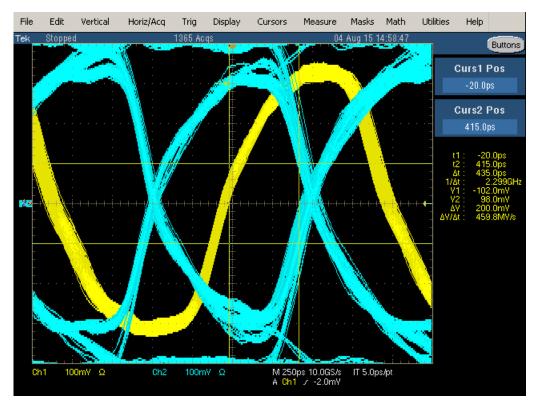

Below is a picture of a DLP9000X input data bit hold time measurement while running the DCLK at 480MHz. The yellow signal is the DCLK and the blue signal shows multiple transitions both positive and negative for the Input Data Bit 6 of Bus D. The measured hold time of 435ps exceeds the datasheet required hold time of 400ps for the DLP9000X DMD.

Figure 4 - Measured Hold Time

The data bus signal measurements detailed above were initially taken with a 5" flexible PCB connecting the DLPC910 output data bus signals on the Main Board to the DLP9000X data bus inputs on the DMD board. Follow-on measurements were also taken using 12" flexible PCBs - No measureable differences in signal setup and hold times were perceived using the 12" version.

TEXAS INSTRUMENTS TIDA-00570 High Speed DLP Sub-system for Industrial 3D Printing and Digital Lithography

### 3. Projection Testing

The DLP9000X DMD PCB of the reference design was mounted up to a modified commercial lamp-based DLP projector such that test patterns internally generated by the applications processor (Xilinx FGPA) could be projected onto a screen for visual validation. Because the DLP9000X WQXGA DMD is of such high resolution, the choice was made to project the images onto a very large wall mounted screen so that the projected patterns could be easily seen and any pattern discrepancies could be identified and debugged.

Several patterns were created within the Applications Processor FPGA. Patterns were created to best allow detection of setup and hold pixel errors or DMD data clocking errors. Figure 5 shows one of these projected patterns.

Figure 5 - Displayed Checkerboard Pattern

All patterns were single bit patterns and were sent repeatedly from the Applications Processor to the DLPC910 to the DLP9000X until a new pattern was selected. Testing covered the range of datasheet min and max parameters. DMD VCC and VCCI voltages were varied from minimum to maximum datasheet values without any errors visible in the patterns. Voltages were varied outside the data sheet specifications, thereby indicating sufficient margins for customers operating within the specification limits.

### 4. Test Summary

Through testing, we have shown that the DLP9000X and DLPC910 chipset has provided good margin for operation in a Digital Lithography or 3D Printing application. Setup and Hold times of the DMD have been met with additional margin for a typical system design. The application of multiple worst case factors during the testing should provide the additional robustness needed in these demanding industrial applications. Our reference design will provide a great starting point and direction for designers of these applications, allowing the designers to focus more on how they would like to use DLP technology instead of how to implement DLP technology.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated