# TI Designs Low Noise Power Management Reference Design for Automotive CMOS Imager Sensor and Data Serializer

#### **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help **you** accelerate your time to market.

#### **Design Resources**

| Design Folder  |

|----------------|

| Product Folder |

| Product Folder |

| Product Folder |

| Product Folder |

|                |

Ask The Analog Experts Community WEBENCH® Design Center

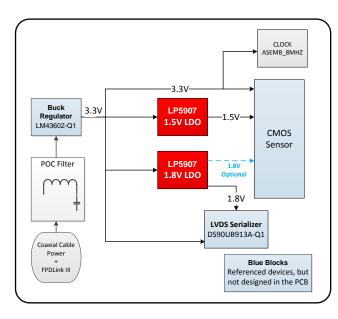

#### **Block Diagram**

#### Design Features

Space optimized power management solution for CMOS sensor and Serializer

**TEXAS INSTRUMENTS**

- Cost optimize solution

- Test data and design recommendations for power management section of the system

- Components in this design are available in Automotive AEC Q100 Qualified Grade 1.

- Input voltage nominal 12 V, range from  $V_{\text{IN}}\text{+}0.3$  V to 36 V

- Output voltage rails:3.3V, 1.8V and 1.5V

### **Featured Applications**

- Automotive imaging applications (when Q1 grade devices are used)

- Side camera

- Rear camera

- Front camera

- Non-Automotive applications

- o Webcam

- o Security Surveillance

- Machine Vision

- Medical Camera

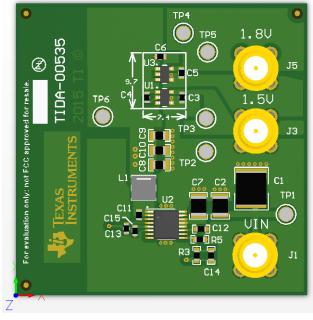

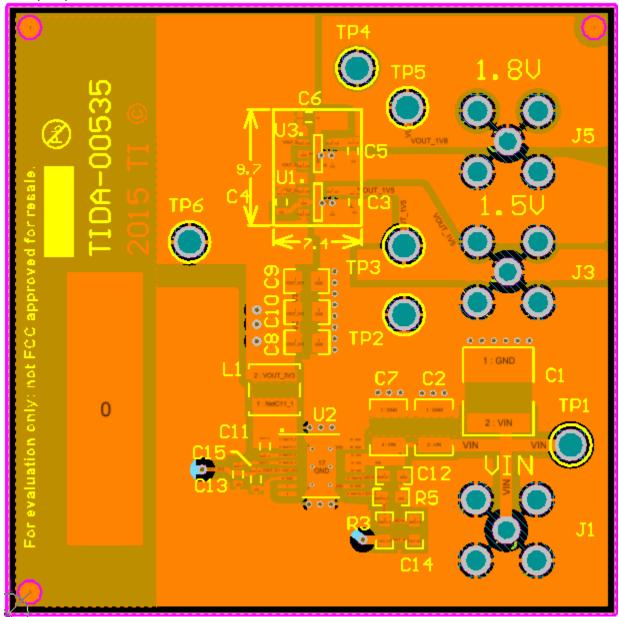

#### **Board Image**

# 1 Key System Specifications

| Table | 1 Kev | System | Specifications |

|-------|-------|--------|----------------|

|       |       | •,•••  | opeenieaeioiio |

| PARAMETER       | SPECIFICATION                    | DETAILS                |

|-----------------|----------------------------------|------------------------|

| Data Serializer | Power supply recommendations for | See <u>Section 4.2</u> |

| for automotive  | FPD-Link III SERIALIZER          |                        |

| camera system   |                                  |                        |

| CMOS image      | Power supply recommendations for | See <u>Section 4.3</u> |

| sensor          | OV10635 OmniVision HDR CMOS      |                        |

|                 | sensor                           |                        |

| Design          | Design implementation guidelines | See <u>Section 5</u>   |

| implementation  |                                  |                        |

# 2 System Description

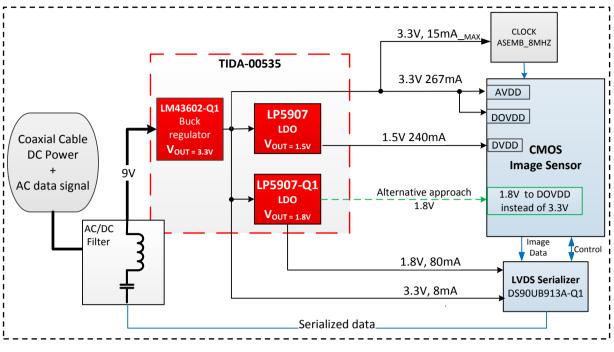

The TIDA-00535 reference design provides a power management solution for automotive imaging system using the voltage regulators LP5907-Q1, LP5907 and LM43602-Q1 to provide the appropriate voltage levels to power a CMOS high dynamic range camera, DS90UB913A-Q1 FPD-Link Serializer chipset and clock oscillator.

The TIDA-00535 is mainly focused in the power management section and provides test data, schematic, and Gerber files. This power management design can be used as a reference for automotive imaging applications as driver assistance including camera enabled systems for park assist rearview, side lane blind spot view, surrounding view and even forward facing vision. For ADAS applications it is recommended to use the Q100 certified version of the devices mentioned in this design.

The highlights for this design are:

- High system noise immunity over critical frequency range

- Cost optimized total power management solution

- Small foot print solution

Note: Advanced Driver Assistance Systems (ADAS) need to comply with the reliability and safety regulations and ASIL requirements (ISO-26262). For ADAS applications it is recommended to use Q100 certified discrete semiconductors and AEC-200 qualified passive components.

#### 3 **Device Selection Considerations**

The highlighted design considerations for the device selection are low noise, cost, and size:

#### Low noise

The possible signal noise produced by the voltage regulators was taken into account at the time of selecting the components. Voltage regulators must have a switching frequency outside of the AM band (540 KHz to 1700 KHz) as well as low noise density and high power ripple rejection over critical frequency range for higher performance.

### Cost:

Cost optimized integrated circuits (ICs) with few external components to keep a low bill of material (BOM) cost.

| Table 2 Estimated Cost for Low hoise LDOS |                          |  |  |  |

|-------------------------------------------|--------------------------|--|--|--|

| PART NUMBER                               | APPROXIMATED PRICE (USD) |  |  |  |

| LP5907 (1.5V)                             | \$0.14 @ 1K cost         |  |  |  |

| LP5907-Q1 (1.8V)                          | \$0.16 @ 1K cost         |  |  |  |

| 2 Input capacitor                         | ~\$0.03                  |  |  |  |

| 2 optional <sup>1</sup> output            | ~\$0.03                  |  |  |  |

| capacitor                                 |                          |  |  |  |

| Total                                     | ~\$0.36                  |  |  |  |

Table 2 Estimated Cast for Low paice LDOs

| PART NUMBER                         | APPROXIMATED PRICE (USD) |

|-------------------------------------|--------------------------|

| LM43602-Q1 (3.3V)                   | \$2.07 @ 1K cost         |

| 11 <sup>2</sup> external components | ~\$0.98                  |

| Total                               | ~\$3.05                  |

### AEC Q100 Qualified Grade 1:

AEC Q100 Qualified stands for qualified in accordance with AEC-Q100 industry standard. Texas Instruments Q1 graded devices are developed to meet the requirements of reliability stress test defined by Automotive Electronics Council.

All the components in the system might have to comply with AEC-Q100 standard depending on the location and application. The LP5907-Q1 is available with fixed output voltages from 1.2 V to 4.5 V in 25 mV steps. Contact Texas Instruments Sales for specific voltage option needs.

#### **Component Footprint:**

The imaging sensors in automobiles are usually confine in small areas like bumpers, rear mirrors casing, side mirrors casing, etc. For this reason the total solution must be discrete in size for placement flexibility. The voltage regulators used in this design have small packages. The LP5907 comes in a DSBGA (0.675 mm x 0.675 mm) package, but depending on the location and application it might be necessary to use the LP5907-Q1 with the SOT-23 package which is AEC-Q100 certified.

| Table 4 Power Management Components Footprint |             |                    |  |  |

|-----------------------------------------------|-------------|--------------------|--|--|

| PART NUMBER                                   | PACKAGE     | IC SIZE (NOMMINAL) |  |  |

| LP5907-Q1 (1.5V)                              | SOT-23      | 2.90 mm x 1.60 mm  |  |  |

| LP5907 (1.8V)                                 | SOT-23      | 2.90 mm x 1.60 mm  |  |  |

| LM43602-Q1 (3.3)                              | HTSSOP (16) | 5.1 mm x 6.6 mm    |  |  |

<sup>1</sup> There is no strict requirement about location of the output cap, a cap <10cm away, at the input of the supplied part will be sufficient. 2 Based on the fundamental parts for operation, additional caps might be required to optimize transient behavior and regulation.

TIDUA54 - June 2015 Low Noise Power Management Reference Design for Automotive CMOS Imager Sensor and Data Serializer Copyright © 2015, Texas Instruments Incorporated

### 4 Block Diagram

As mentioned in previous section the main focus of this document is to provide test data and design parameters for the 1.5 V and 1.8 V regulated output voltage rails. These rails power the critical systems in the CMOS image sensor and data Serializer.

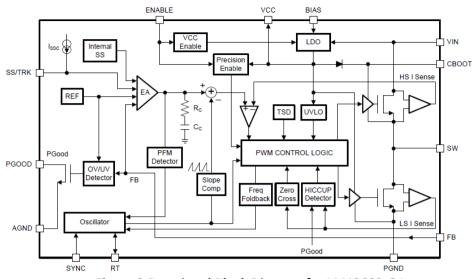

**Figure 1** gives a high level block diagram of the complete system. The red block represents the focus component of this document.

The blue blocks represent other TI components and grey block are non TI components. Blue and grey components are mentioned in this document and their power requirements are explained and taken into consideration to define the system power requirements; however those components were not design into the TIDA-00535 evaluation board and some of their application specific requirements are not mentioned, it is recommended to review their datasheet for additional application implementation requirements.

The green dotted line connecting DOVDD of the CMOS imager to a 1.8V voltage supply rail represents an alternative power configuration.

### 4.1 Highlighted TI Products

TIDA-00535 features the following Texas Instruments (TI) low noise voltage regulator and high efficiency synchronous regulator. These devices were chosen taking into account the power requirements of typical CMOS sensor and data Serializer components.

LP5907-Q1: 250mA, Ultra-Low Noise Low-Dropout Regulator

LM43602-Q1: SIMPLE SWITCHER® 3.5V to 36V, 500mA Synchronous Step-Down Voltage Converter

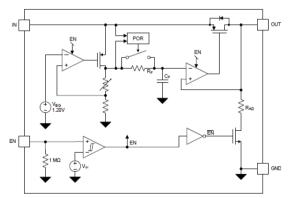

### 4.1.1 LP5907-Q1

The LP5907-Q1 is a linear regulator capable of supplying 250-mA output current. Designed to meet the requirements of RF and analog circuits, the LP5907-Q1 device provides low noise, high PSRR, low quiescent current and low line or load transient response. Using new innovative design techniques, the LP5907-Q1 offers class-leading noise performance without a noise bypass capacitor and the ability for remote output capacitor placement, the remote capacitor feature can save board space by using the capacitor of the supplied part.

The device is designed to work with a  $1-\mu$ F input and a  $1-\mu$ F output ceramic capacitor (no separate noise bypass capacitor is required).

Two of these low noise regulators were used to step down the 3.3 V output voltage of the DC/DC converter to 1.5 V and 1.8 V.

Alternative linear regulators:

**LP5907**: Same functionality as LP5907-Q1 but smaller package and not Q1 graded for non-automotive camera applications.

**LP3990**:  $V_{OUT} = 1.2 V$ , 1.8 V, 2.8 V; smaller package but lower output current of 150 mA. **LP3892**:  $V_{OUT} = 1.2 V$ , 1.8 V, 2.8. Higher maximum output current of 1.5 A, but requires a  $V_{BIAS}$  of 5V **LP3990Q**:  $V_{OUT} = 2.8$ ,  $I_{OUT} = 150$ ; some data serializers can be powered with 2.8V input voltage.

Figure 2 LP5907-Q1 Functional Block Diagram

### 4.1.2 LM43602-Q1

The LM43602-Q1 SIMPLE SWITCHER<sup>\*</sup> regulator is an easy-to-use synchronous step-down DC-DC converter capable of driving up to 2 A of load current from an input voltage ranging from 3.5 V to 36 V (42 V abs max). The LM43602-Q1 provides exceptional efficiency, output accuracy and dropout voltage in a very small solution size. An extended family is available in 0.5 A, 1 A, and 3 A load current options in pin-to-pin compatible packages. Peak current mode control is employed to achieve simple control loop compensation and cycle-by-cycle current limiting. Optional features such as programmable switching frequency, synchronization, and power-good flag, precision enable, internal soft-start, extendable soft-start, and tracking provide a flexible and easy to use platform for a wide range of applications. Discontinuous conduction and automatic frequency modulation at light loads improve light load efficiency. The family requires few external components and terminal arrangement allows simple, optimum PCB layout. Protection features include thermal shutdown, V<sub>cc</sub> under voltage lockout, cycle-by-cycle current limit, and output short circuit protection. The LM43602-Q1 device is available in the HTSSOP / PWP 16-pin leaded package (5.1 mm × 6.6 mm × 1.2 mm).

Main care-about for an alternative DC/DC step down voltage converters are:

- Converter with internal FETs or module for minimum external component count

- Input transient tolerance of minimum 36V

- Synchronous regulator for high efficiency

- At least 1 A of source current

- Good thermal dissipation

- Q100 reliability graded

- Small foot print

DIM

Figure 3 Functional Block Diagram for LM43602-Q1

| Table 5 Pin Function for LM43602-Q1 |

|-------------------------------------|

|                                     |

| PIN    |        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |  |  |

|--------|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NUMBER | TTPET               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |  |  |

| SW     | 1,2    | Р                   | Switching output of the regulator. Internally connected to both power MOSFETs. Connect to<br>power inductor.                                                                                                                                                                                                                                      |  |  |

| CBOOT  | 3      | Р                   | Boot-strap capacitor connection for high-side driver. Connect a high quality 470 nF capacitor<br>from CBOOT to SW.                                                                                                                                                                                                                                |  |  |

| VCC    | 4      | Р                   | Internal bias supply output for bypassing. Connect bypass capacitor from this pin to AGND.<br>Do not connect external loading to this pin. Never short this pin to ground during operation.                                                                                                                                                       |  |  |

| BIAS   | 5      | Р                   | Optional internal LDO supply input. To improve efficiency, it is recommended to tie to $V_{OUT}$ when 3.3 V $\leq V_{OUT} \leq 28$ V, or tie to an external 3.3 V or 5 V rail if available. When used, place a bypass capacitor (1 to 10 $\mu$ F) from this pin to ground. Tie to ground when not in use. BIAS pin voltage should not exceed VIN. |  |  |

| SYNC   | 6      | A                   | Clock input to synchronize switching action to an external clock. Use proper high speed termination to prevent ringing. Connect to ground if not used.                                                                                                                                                                                            |  |  |

| RT     | 7      | A                   | Connect a resistor $R_T$ from this pin to AGND to program switching frequency. Leave floating for 500 kHz default switching frequency.                                                                                                                                                                                                            |  |  |

| PGOOD  | 8      | A                   | Open drain output for power-good flag. Use a 10 k $\Omega$ to 100 k $\Omega$ pull-up resistor to logic rail or other DC voltage no higher than 12 V.                                                                                                                                                                                              |  |  |

| FB     | 9      | A                   | Feedback sense input pin. Connect to the midpoint of feedback divider to set V <sub>OUT</sub> . Do not short this pin to ground during operation.                                                                                                                                                                                                 |  |  |

| AGND   | 10     | G                   | Analog ground pin. Ground reference for internal references and logic. Connect to system ground.                                                                                                                                                                                                                                                  |  |  |

| SS/TRK | 11     | A                   | Soft-start control pin. Leave floating for internal soft-start slew rate. Connect to a capacitor to<br>extend soft start time. Connect to external voltage ramp for tracking.                                                                                                                                                                     |  |  |

| EN     | 12     | A                   | Enable input to the internal LDO and regulator. High = ON and low = OFF. Connect to VIN, or to VIN through resistor divider, or to an external voltage or logic source. Do not float.                                                                                                                                                             |  |  |

| VIN    | 13,14  | Р                   | Supply input pins to internal LDO and high side power FET. Connect to power supply and bypass capacitors $C_{\rm IN}$ . Path from VIN pin to high frequency bypass $C_{\rm IN}$ and PGND must be as short as possible.                                                                                                                            |  |  |

| PGND   | 15,16  | G                   | Power ground pins, connected internally to the low side power FET. Connect to system ground, PAD, AGND, ground pins of $C_{IN}$ and $C_{OUT}$ . Path to $C_{IN}$ must be as short as possible.                                                                                                                                                    |  |  |

| PAD    | 17     | _                   | Low impedance connection to AGND. Connect to PGND on PCB. Major heat dissipation path<br>of the die. Must be used for heat sinking to ground plane on PCB.                                                                                                                                                                                        |  |  |

(1) P = Power, G = Ground, A = Analog

### 4.2 Other TI parts

### 4.2.1 <u>DS90UB913A-Q1</u>

FPD-Link III with Power-Over-Coax

The DS90UB913A-Q1 is a 25-100MHz 10/12- Bit DC-Balanced FPD-Link III Serializer with Bidirectional Control Channel. The DS90UB913A/DS90UB914A chipset offers a FPD-Link III interface with a high-speed forward channel and a bidirectional control channel for data transmission over a single differential pair. The DS90UB913A-Q1/914A-Q1 chipsets incorporate differential signaling on both the high-speed forward channel and bidirectional control channel data paths. The Serializer/Deserializer pair is targeted for connections between imagers and video processors in an ECU (Electronic Control Unit). This chipset is ideally suited for driving video data requiring up to 12 bit pixel depth plus two synchronization signals along with bidirectional control channel bus.

**Key Specifications**

- 1.8-V, 2.8-V or 3.3-V-Compatible Parallel Inputs on Serializer

- Single Power Supply at 1.8 V

- Coaxial or Single Differential Pair Interconnect

- 25-MHz to 100-MHz Input Pixel Clock Support

- Programmable Data Payload:

- $\circ$  ~ 10-bit Payload up to 100 MHz ~

- 12-bit Payload up to 75 MHz

- Embedded Clock with DC-Balanced Coding to Support AC-Coupled Interconnects

- Automotive Grade Product: AEC-Q100 Grade 2 Qualified

- Small Serializer Footprint (5 mm × 5 mm)

### 5 Design Considerations

### 5.1 Remote Power Delivery

This section gives an overview of two widely known and used methods to power devices in remotely location. When providing power to remote device using long cables it is important to use electromagnetic interference (EMI) best design practices to avoid noise coupling and data distortion.

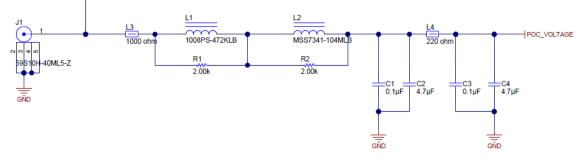

### 5.1.1.1 Power Feed through Coaxial Cable

The system input voltage is expected to be 12V nominal from the engine control unit (ECU) which is deliver via power over coaxial (POC) along with a single ended data path carrying two data channels, the backward channel with frequency bandwidth of 1 MHz to 4 MHz and a forward channel Carrying the coded and serialized data from the imager with a frequency bandwidth from about 70 MHz to 700 MHz. The unused data pin (DOUT–, RIN–) should have a 0.047-µF capacitor in series and terminated with a 50- $\Omega$  resistor.

Two filters needs to be implemented at the power receiver side, one low pass filter for the DC signal, and a high pass filter for the AC signal carrying the data.

### 1. High pass filter (DC voltage)

The high pass filter needs to block the DC signal and have low impedance at the band of interest to allow the AC signal to pass without corrupting the data.

A simple 0.1uF 603 capacitor with low parasitic inductance and low equivalent series resistance will do the work.

### 2. Low pass filter (AC signal)

The second section needs to allow the DC voltage to pass without interfering with the data path and also have to block any noise coming from the voltage management system. This circuitry is more complex because it requires an inductor to block the high frequencies and inductors are less ideal than capacitor and come in bigger sizes. To avoid interference with the data path the filter must have impedance 20X higher than the characteristic impedance; in the case of  $50\Omega$  cox line the impedance must be greater than  $1k\Omega$  from 1 MHz up to 700 MHz.

Taking the above information into account it is recommended to use two inductors in series to compensate for the resonant frequency and parasitic capacitance of the inductors. A 100  $\mu$ H in series with a 4.7 $\mu$  inductor will have overall impedance greater than 1 k $\Omega$  from 1MHz to 1 GHz. A resistor can be placed in parallel with each inductor to keep the inductance from spiking too high. A ferrite bead is can be added for filtering out coupled Electro-Magnetic Interference (EMI) in the coaxial cable. The capacitors are simply bulk capacitance to reduce current ripple to the input of the power supplies.

Chose and adequate saturation current because usually the value specified in the inductor data sheet means when the inductance value has fallen by 10 % and it will then behave as a capacitor. Use magnetically shielded inductor and do not route any tracks under the component to avoid any magnetic coupling with adjacent components or conductor traces, also shielded inductors have lower DC resistance than an unshielded inductor, this translate to lower wire heating losses which is related to power coper loses.

Figure 4 Power over coaxial cable

For more information about power over coaxial filter design please refer to TI application report <u>Sending Power over Coax in DS90UB913A Designs (SNLA224)</u>

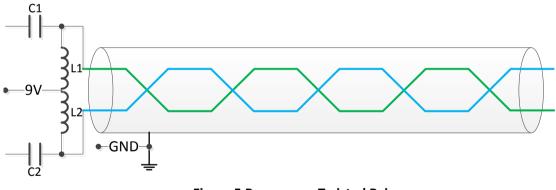

### 5.1.2 Power Feed through Shielded Twisted Pair Cable

The basic concept to deliver power through a shielded twisted pair (TPS) is similar to power over coaxial, the goal is to transmit DC voltage along with the high speed bidirectional data transmitter signal through the same media.

The main concern is to isolate the forward and backward high frequency signal from the DC voltage. The DC voltage is extracted from the center of a power feed inductor (Bias Injection Choke) like the KA4909-AL, and the AC signal can be decoupled using capacitors in series with the differential lines.

Figure 5 Power over Twisted Pair

For detail information about delivering power to remote device using differential pair please refer to the <u>Combine power feed and data link via cable for remote peripherals</u> technical document.

### 5.2 Data Serializer Power Supply Requirements

This section provides power requirements of a typical Serializer; the DS90UB913A-Q1 FPD-Link III Serializer is used as an example.

For detail information about digital/analog pin configuration and application implementation please refer to the DS90UB913A-Q1 datasheet (<u>SNLS443B</u>)

### 5.2.1 DS90UB913A -Q1 Voltage Pins

| NAME                                                  | PIN    | VOLTAGE                                        | FILTERING          | DESCRIPTION                                                                                                                                                    |  |

|-------------------------------------------------------|--------|------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                       | NUMBER |                                                | COMPONENTS         |                                                                                                                                                                |  |

| VDDPLL                                                | 10     | 1.8 V                                          | 0.01μ, 0.1μ, 4.7μF | Power, PLL Power, 1.8 V ±5%. Analog                                                                                                                            |  |

| VDDT                                                  | 11     | 1.8 V                                          | 0.01µ, 0.1µ, 4.7µF | Power, Tx Analog Power, 1.8V ±5%.<br>Analog                                                                                                                    |  |

| VDDCML                                                | 14     | 1.8 V                                          | 0.01µ, 0.1µ, 4.7µF | Power, CML & Bidirectional Channel<br>Driver Power, 1.8 V ±5%. Analog                                                                                          |  |

| VDDD                                                  | 28     | 1.8 V                                          | 0.01µ, 0.1µ,       | Power, Digital Power, 1.8 V ±5%.<br>Digital                                                                                                                    |  |

| VDDIO or<br>3.3 V ±10%.                               | 25     | 1.8 V ±5%<br>or<br>2.8±10%<br>or<br>3.3 V ±10% | 0.01μ, 0.1μ,       | Power, Power for I/O stage. The single-<br>ended inputs and SDA, SCL are<br>powered from VDDIO. VDDIO Digital<br>can be connected to a 1.8 V ±5% or<br>2.8±10% |  |

| VSS ground<br>plane (GND)<br>with at least<br>9 vias. | DAP    | GND                                            |                    | Ground, DAP must be grounded. DAP<br>is the large metal contact at the<br>bottom side, located at the center of<br>the WQFN package. Connected to the          |  |

#### Table 6 DS90UB913A-Q1 Power Connections

### 5.2.2 DS90UB913A-Q1 Power up Requirements

The DS90UB913A-Q1 requires delaying the PDB  $V_{DC}$  after all other power supplies have settled to the recommended operating voltage. An external RC network can be connected to the PDB pin to ensure PDB arrives after all the VDD has stabilized.

A delay to the power up sequence can be implemented with either a simple RC circuit or by implanting a robust supply voltage supervisor like the <u>TPS3836E18-Q1</u> with 10ms/200ms selectable delay time.

### 5.2.3 DS90UB913A-Q1 Input Voltage Requirements

Table 8 shows the power requirements for the DS90UB913A-Q1

|       | Table 7 Worst Case Current Consumption |                       |            |  |

|-------|----------------------------------------|-----------------------|------------|--|

| NAME  | CONDITIONS                             | CURRENT [mA]          | POWER [mW] |  |

| VDDT  | RL=100 Ω                               | I <sub>DDT</sub> = 84 | 151        |  |

|       | VDDn = 1.80 V,                         |                       |            |  |

|       | VDDIO = 3.6 V                          |                       |            |  |

|       | f = 75 MHz, 12-bit                     |                       |            |  |

|       | high frequency mode Default Registers  |                       |            |  |

| VDDIO | RL=100 Ω                               | $I_{DDIOT} = 8$       | 28.8       |  |

|       | VDDIO = 3.6 V                          |                       |            |  |

|       | f = 75 MHz, 12-bit                     |                       |            |  |

|       | high frequency mode Default Registers  |                       |            |  |

### Table 7 Worst Case Current Consumption

Table 9 shows the input voltage tolerance of the DS90UB913A-Q1, the input voltage has to be stable within the maximum and minimum voltage limits to avoid erroneous operation.

| Table & Bester Bs15/( Q1 input Voltage Volera |         |               |  |  |

|-----------------------------------------------|---------|---------------|--|--|

| NAME                                          | VOLTAGE | TOLERANCE     |  |  |

| VDDT                                          | 1.8V    | ±5% (±75mV)   |  |  |

| VDDIO                                         | 3.3V    | ±10% (±330mV) |  |  |

#### Table 8 DS90UB913A-Q1 Input Voltage Tolerance

### 5.3 CMOS Image Sensor Power Supply Requirements

This section provides power requirements of a typical CMOS sensor. The <u>OV10635</u> HD HDR imager CMOS sensor from OmniVision is used as an example to show the power requirements of a typical CMOS sensor.

For detail information about digital/analog pin configuration and application implementation please refer to <u>OV10635</u> datasheet it can be obtained from <u>OmniVision Technologies corp</u>.

### 5.3.1 CMOS Image Sensor Power Considerations

The analog supply voltage for most CMOS sensors used in cameras ranges from 1.5 to 3.3V. A clean voltage supply is required for these voltage rails.

| Table 5 Civios Ovidoss Sensor Fower Supply requirements |       |         |                       |            |

|---------------------------------------------------------|-------|---------|-----------------------|------------|

| PARAMETER                                               | NAME  | VOLTAGE | CURRENT [mA]          | POWER [mW] |

| Core Voltage                                            | DVDD  | 1.5V    | 160                   | 240 mW     |

| Analog power                                            | AVDD  | 3.3V    | @3.3V:                | 267 mW     |

| I/O Power and                                           | DOVDD | 3.3V    | I <sub>TYP</sub> = 81 |            |

|                                                         |       | or      |                       |            |

|                                                         |       | 1.8V    |                       |            |

### Table 9 CMOS OV10635 Sensor Power Supply requirements

#### Table 10 CMOS OV10635 sensor input voltage tolerances

| NAME  | VOLTAGE | TOLERANCE   |

|-------|---------|-------------|

| DVDD  | 1.5V    | ±5% (±75mV) |

| AVDD  | 1.8V    | ±5% (±75mV) |

| DOVDD | 3.3V    | @3.3V ±10%  |

|       | or      | @1.8V ±5%   |

|       | 1.8V    |             |

The DOVDD can be powered either from 3.3V or 1.8V

### 5.4 Total Power Supply Requirements

The table 6 provides the total typical power requirement for the Serializer, CMOS image sensor and a typical 8 MHz clock oscillator.

| VOLTAGE | CMOS SENSOR [mW] | SERIALIZER [mW] | ASEMB_8MHZ <sup>3</sup> (Clock) | TOTAL POWER [mW] |

|---------|------------------|-----------------|---------------------------------|------------------|

| 1.5V    | 240              | N/A             | N/A                             | 240              |

| 1.8V    | N/A              | 151             | N/A                             | 151              |

| 3.3V    | 267              | 28.8            | 27 mW_ <sub>MAX</sub>           | 323              |

|         | TOTAL            |                 |                                 | 714              |

#### **Table 11 Total Power Requirements**

From the details mentioned in the previous sections we can conclude that the most critical voltage rails with tight voltage limits are the 1.5 V and 1.8 V, these voltage rails have a tolerance of  $\pm$ 5%. Table 7 shows the system voltage requirements and minimum and maximum voltage limits.

|   | VOLTAGE | CURRENT (mA) | V <sub>MIN</sub> | V <sub>MAX</sub> |

|---|---------|--------------|------------------|------------------|

|   | 1.5V    | 160          | 1.42             | 1.57             |

| ſ | 1.8V    | 84           | 1.72             | 1.87             |

|   | 3.3V    | 104          | 2.97             | 3.63             |

#### **Table 12 Total Power Requirements**

TIDUA54 - June 2015

<sup>&</sup>lt;sup>3</sup> Information about <u>ASEMB 8MHZ</u> was obtained from datasheet (<u>LINK)</u>

### 6 Design Implementation Guidelines

The following system considerations apply only for the conditions of this design. For different conditions it is essential to verify the ratings and operating conditions on the datasheets of the parts mentioned in this design. If the parameters does not fit the application consider one of the alternative parts on section 3 or perform and easy parametric search at <a href="http://www.ti.com">http://www.ti.com</a>

### 6.1 Linear Regulator

The LP5907 requires at least a 1  $\mu$ F capacitor at the OUT pin, but there are no strict requirements about the location of the capacitor in regards to the pin. In practical designs the output capacitor may be located up to 10 cm away from the LDO. This means that there is no need to have a capacitor close to the output pin, a remote capacitor at the supplied device will be sufficient. The remote capacitor feature helps to minimize the number of capacitors in the system.

The recommendation is to keep parasitic wiring inductance less than 35 nH. For the applications with fast load transients, it is recommended to use an input capacitor equal to or larger to the sum of the capacitance at the output node for the best load transient performance.

Adding higher capacitor values will reduces the transient response, but also increases the response time for the output voltage to reach the nominal voltage.

### 6.1.1 Thermal Performance

The permissible power dissipation for any package is a measure of the capability of the device to pass heat from the power source, the junctions of the IC, to the ultimate heat sink, the ambient environment. Thus, the power dissipation is dependent on the ambient temperature and the thermal resistance across the various interfaces between the die junction and ambient air.

The actual power being dissipated in the device can be represented by Equation 1

$$P_D = (V_{IN} - V_{OUT}) \times I_{LOAD}$$

(1)

$T_{A-MAX}$  is dependent on the maximum operating junction temperature ( $T_{J-MAX-OP} = 125$ °C), the maximum allowable power dissipation in the device package in the application ( $P_{D-MAX}$ ), and the junction-to ambient thermal resistance of the part/package in the application (R  $\theta$  JA), as given by Equation 2

$$T_{A_{MAX}} = -(\theta_{JA} \times P_D) + T_{J_{MAX}}$$

(2)

The typical ambient temperature of the 1.5 V and 1.8 V LDO was calculated using Equation 1 and Equation 2.

| INPUT VOLTAGE | OUTPUT<br>VOLTAGE | Load Current | THEORETICAL T <sub>A-MAX</sub> |

|---------------|-------------------|--------------|--------------------------------|

| 3.3 V         | 1.5 V             | 84 mA        | 94° C                          |

| 3.3 V         | 1.8 V             | 160 mA       | 133° C                         |

The computed  $T_{A\_MAX}$  can be consider as a highly conservative scenario, because a system board rarely approximates the test JEDEC board used to determine  $R_{\theta JA}$ . The PCB board layout strongly influences the thermal dissipation of the device; an optimized layout will have a lower  $R_{\theta JA}$  than the JEDEC which means that will have a higher  $T_{A\_MAX}$ .

For detail information about how to design an optimized board for lower thermal resistance please refer to application report (<u>SNVA183B</u>)

Low Noise Power Management Reference Design for Automotive CMOS Imager Sensor and Data Serializer Copyright © 2015, Texas Instruments Incorporated

### 6.2 Step Down Voltage Converter Implementation

This section gives a high-level description of the compensation components of the LM43602-Q1 synchronous step down voltage converter. For function and description of the device pins mentioned in this section please refer to section 3.2.2.

| Table 15 Design parameters |             |  |

|----------------------------|-------------|--|

| PARAMETER                  | VALUE       |  |

| V <sub>IN</sub>            | 12V nominal |  |

| V <sub>OUT</sub>           | 3.3V        |  |

| I <sub>OUT_MAX</sub>       | 2 A         |  |

| Switching frequency        | 500 KHz     |  |

| Table 13 Design | parameters |

|-----------------|------------|

|-----------------|------------|

### 6.2.1 Switching Frequency

To avoid interference with the AM radio band, all switching frequencies need to either be greater than 1700 kHz or lower than 540 kHz.

To set the switching frequencies in the LM43602-Q1 a resistor needs to be connected from  $R_T$  pin to ground. The following equation can be used to calculate the  $R_T$  value

$R_{T}(k\Omega) = 40200 / Freq (kHz) - 0.6$

Table 14 shows resistors values that will set the switching frequency to a frequency outside of the AM band.

| F <sub>s</sub> (KHz) | R <sub>τ</sub> (KΩ) |

|----------------------|---------------------|

| 200                  | 200                 |

| 350                  | 115                 |

| 500                  | 80.6 or open        |

| 2000                 | 19.6                |

| 2200                 | 17.8                |

#### **Table 14 Resistor Values to Set Switching Frequency**

### 6.2.2 Output Voltage Selection

For an output voltage of 3.3 V and greater, the BIAS pin can be connected to the output in order to increase light load efficiency.

The output voltage is set by an external resistor divider network, comprised of top feedback resistor ( $R_{FBT}$ ) and bottom feedback resistor ( $R_{FBB}$ ). It is recommends to set the value of the  $R_{FBT}$  to 100 k $\Omega$  to minimize ground current, the  $R_{FBB}$  can be calculated using the equation below

$$R_{FBB} = \frac{V_{FB}}{V_{OUT} - V_{FB}} \times R_{FBT}$$

(3)

A 43.2 k $\Omega$  resistor can be used for R<sub>FBB</sub> to set the output voltage to 3.3 V.

TIDUA54 - June 2015

**Note:** This section gives an overview of the application implementation for LM43602-Q1, but for further details and information about the device performance, implementation, applications and component selections please refer to datasheet (<u>SNVSA83A</u>)

)

### 6.2.3 Inductor Selection

The main principles to select the appropriate inductor are inductance, peak to peak ripple current, maximum load current, frequency of operation and the converter duty cycle. Higher inductance gives lower ripple current and hence lower output voltage ripple with the same output capacitors. Lower inductance could result in smaller, less expensive component, and faster transient response.

The following equation can be used to calculate the correct inductor for a system with 12V input voltage and 3.3V output voltage and 2A peak current.

Converter duty cycle

$$D = \frac{V_{OUT}}{V_{IN}}$$

(4)

Inductance range:

$$\frac{(V_{IN} - V_{OUT}) \times D}{0.4 \times F_S \times I_{L_MAX}} \le L \le \frac{(V_{IN} - V_{OUT}) \times D}{0.2 \times F_S \times I_{L_MAX}}$$

(5)

Peak to peak inductor current ripple has to be within 20% and 40%

$\Delta \mathbf{i}_{\mathrm{L}} = \frac{(V_{IN} - V_{OUT}) \times D}{L \times F_{\mathrm{S}}} \tag{6}$

Inductors ripple current ratio:

$$r = \frac{\Delta i_{\rm L}}{I_{OUT}} \tag{7}$$

Terms key  $\Delta$  iL = Peak to peak ripple current D = Duty cycle r = Ripple current ratio F<sub>s</sub>= Switching frequency

A 6.8  $\mu$ H mid-range inductor from the calculated inductance range of equation (2) will provide an adequate current ripple.

### 6.2.4 Compensation capacitors

### **Boot strap capacitor**

Every LM43602-Q1 design requires a bootstrap capacitor, CBOOT. The recommended bootstrap capacitor value is 0.47  $\mu$  F and rated at 6.3 V or higher. The bootstrap capacitor is located between the SW pin and the CBOOT pin. The bootstrap capacitor must be a high-quality ceramic type with X7R or X5R grade dielectric for temperature stability.

### **VCC Capacitor**

The VCC capacitor is located at the output voltage of the internal LDO. To insure stability of the part, place a minimum of  $2.2 \mu$ F, 10V capacitor from this pin to ground.

### **BIAS Capacitors**

The LM43602-Q1 integrates an internal LDO to generate VCC for control circuitry and MOSFET drivers. The nominal voltage for VCC is 3.2 V. The VCC pin is the output of the LDO must be properly bypassed. A high quality ceramic capacitor with 2.2  $\mu$ F to 10  $\mu$ F capacitance and 6.3 V or higher rated voltage should be placed as close as possible to VCC and grounded to the exposed PAD and ground pins. The VCC output pin should not be loaded, left floating, or shorted to ground during operation. Shorting VCC to ground during operation may cause damage to the LM43602-Q1.

#### **Input Capacitors**

The LM43602-Q1 device requires high frequency input decoupling capacitor(s) and a bulk input capacitor, depending on the application. The typical recommended value for the high frequency decoupling capacitor is between 4.7  $\mu$ F to 10  $\mu$ F. A high-quality ceramic type X5R or X7R with low equivalent series resistance (ESR) is recommended.

#### **Output Capacitor**

Capacitors with small ESR and large capacitance are desired for applications with fast large load transients to improve load regulation. A good known technique to avoid using big capacitors is to place a couple of smaller capacitors in parallel; this will lower the ESR and compensate for their independent resonant frequency.

The following equation gives an approximation for an absolute minimum output cap required:

$$C_{OUT} > \frac{1}{F_{S} \times \Delta V_{OUT}/I_{OUT}} \times \left[ \left( \frac{r^{2}}{12} \times (1 + (1 - \mathbf{D})) + ((1 - \mathbf{D}) \times (1 + r)) \right) \right]$$

(8)

Along with this for the same requirement, the max ESR should be calculated as per the following inequality:

$$\text{ESR} < \frac{1-D}{F_{\text{S}} \times C_{\text{OUT}}} \times \left(\frac{1}{r} 0.5\right)$$

(9)

A general guideline for COUT range is that COUT should be larger than the minimum required output capacitance calculated by Equation 8, and smaller than 10 times the minimum required output capacitance or 1 mF. In applications with VOUT less than 3.3 V, it is critical that low ESR output capacitors are selected. This will limit potential output voltage overshoots as the input voltage falls below the device normal operating range. To optimize the transient behavior a feed-forward capacitor could be added in parallel with the upper feedback resistor. For this design example, three 47  $\mu$ F,10 V, X7R ceramic capacitors are used in parallel.

#### **Feedforward capacitor**

To improve the phase boost an external feedforward capacitor  $C_{FF}$  can be added in parallel with  $R_{FBT}$ .  $C_{FF}$  is chosen such that phase margin is boosted at the crossover frequency without  $C_{FF}$ . A simple estimation for the crossover frequency without  $C_{FF}$  (f<sub>x</sub>) is shown in the following equation, assuming Cout has very small ESR.

$$\mathbf{f}_{\mathbf{x}} = \frac{4.35}{V_{OUT} \times C_{OUT}} \tag{10}$$

Indicates that the crossover frequency is geometrically centered on the zero and pole frequencies caused by the CFF capacitor. A 330 pF COG capacitor will be sufficient for the given parameters.

$$C_{FF} = \frac{1}{2\pi f_x} \times \frac{1}{\sqrt{R_{FBT} \times (\frac{R_{FBT}}{R_{FBB}})}}$$

(11)

### 8 Test Data

The test data in this section only applies to the parameters mentioned in this document for alternative configuration it is recommended to review the datasheet of the cited devices. This section provides test results for the LP5907-Q1.

### 8.1 Test Equipment

The following table shows the test equipment used in the upcoming sections.

| Table 15 Test equipment |                    |  |

|-------------------------|--------------------|--|

| Test equipment          | Part number        |  |

| Oscilloscope            | Agilent DPO4014B   |  |

| Linear voltage supply   | Agilent E3631A     |  |

| Multimeter              | Agilent E34401A    |  |

| Network Analyzer        | Agilent E5061B ENA |  |

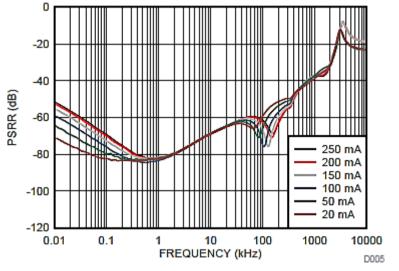

### 8.2 Power Supply Ripple Rejection

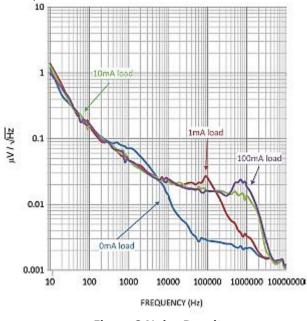

The output voltage ripple rejection ratio is calculated by comparing the regulated output voltage of the LP5907-Q1 with the input voltage ripple over a frequency range of 10Hz to 10MHz.

### Test parameters:

$$\begin{split} &C_{\text{IN}} = C_{\text{OUT}} = 1 \mu \text{F} \\ &V_{\text{IN}} = V_{\text{OUT}} + 1 \text{V} \\ &V_{\text{IN}\_AC} = \text{Sweep from 10Hz to 1MHz} \\ &\text{Room Temperature} = 25^{\circ} \text{C} \\ &\text{EN pin tied to } V_{\text{IN}} \end{split}$$

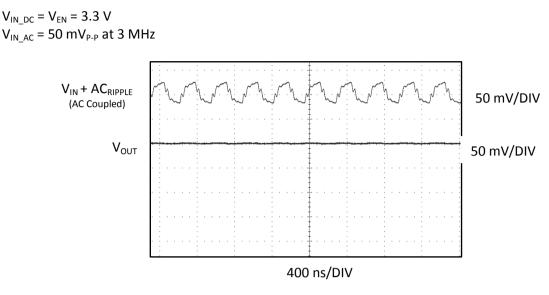

Figure 6 Power Supply Ripple Rejection

Figure 7 shows the clean regulated output voltage of the LP5907 when a ripple voltage of 50mV  $+3.3V_{DC}$  signal is applied at the LP5907 input pin.

Figure 7 Input voltage ripple versus regulated Vout

### 8.3 Noise density

Output noise voltage is the root mean square (RMS) output noise voltage over a given range of frequencies (10 Hz to 100 kHz) under the conditions of a constant output current and a ripple-free input voltage.

The graph below shows the output noise at various load conditions.

**Figure 8 Noise Density**

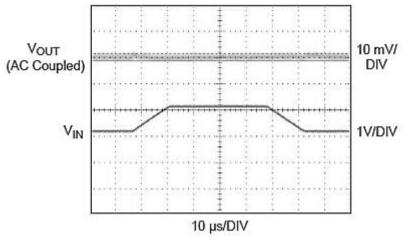

### 8.4 Line Transient and Regulation

The LP5907-Q1 line regulation test is defined as the change in output voltage from nominal value resulting from a change in input voltage.

**Figure 9 Line Transient Regulation**

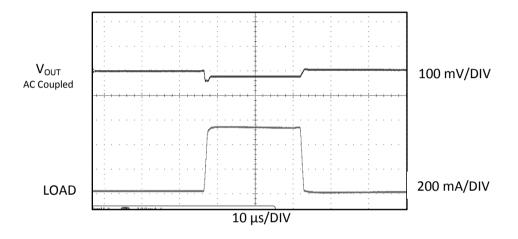

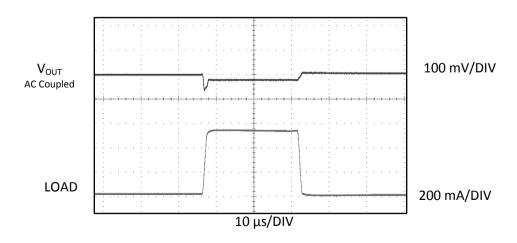

### 8.5 Load transient test

Load transient regulation is defined as the change in output voltage from nominal value as the load current suddenly increases.

### 8.5.1 Load Transient/Regulation LP5907\_1.5

### **Test parameters**

$$\label{eq:vour} \begin{split} v_{\text{OUT}} &= 1.5 V \\ v_{\text{IN}} &= 3.3 V \\ C_{\text{IN}} &= C_{\text{OUT}} = 1 \ \mu\text{F} \\ \text{Room Temperature} \end{split}$$

Load delta = 0 mA  $\leftarrow \rightarrow$  250 mA

Figure 10 LP5907-Q1\_1.5 Load Transient

### 8.5.2 Load Transient/Regulation LP5907-Q1\_1.8

### **Test parameters**

$$\label{eq:vour} \begin{split} v_{\text{OUT}} &= 1.8 V \\ v_{\text{IN}} &= 3.3 V \\ C_{\text{IN}} &= C_{\text{OUT}} = 1 \ \mu\text{F} \\ \text{Room Temperature} \end{split}$$

Load = 0 mA  $\leftarrow \rightarrow$  250 mA

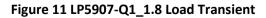

### 8.5.3 Load Transient/Regulation LM43602-Q1

**Test parameters**

V<sub>IN</sub> = 12V  $V_{OUT} = 3.3V$  $F_s = 500 \text{ kHz}$  $I_{Load} = 0 A \leftrightarrow 1A$

100 µs/DIV

Figure 12 LM43602-Q1 Load Transient

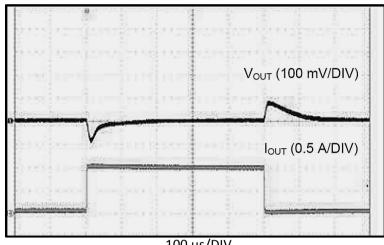

### 8.6 Power up

The LP5907-Q1 takes about 60 µs from zero voltages to reach 90% of the nominal output voltage.

### **Test parameters:**

$C_{IN} = C_{OUT} = 1 \mu F$  $V_{IN} = V_{OUT} + 1V$

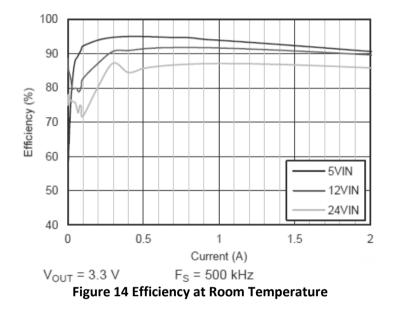

## 8.7 LM43602 Efficiency

Whit a load of 1A and 12V input and 5V output the LM43602-Q1 has an efficiency of 94% at room temperature.

### Test parameters

$v_{OUT} = 12V$  $v_{IN} = 5V$ Switching frequency = 500 KHz Room Temperature

### 9 Design Files

### 9.1 Schematics

To download the Schematics for each board, see the design files at <a href="http://www.ti.com/tool/TIDA-00535">http://www.ti.com/tool/TIDA-00535</a>

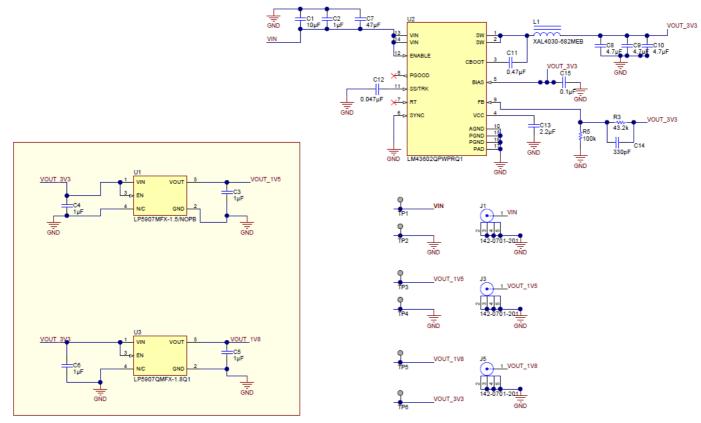

Figure 15 TIDA-00535 Schematic

### 9.2 Bill of Materials

To download the Bill of Materials, see the design files at <u>http://www.ti.com/tool/TIDA-00535</u>

**Note:** The Integrated circuits in this design are available in Automotive AEC Q100 Qualified Grade 1. All passives and other components selected in this design may not be qualified for automotive applications. The user is required to verify that all components in the design meet the qualification and safety requirements for their specific application.

### 9.3 Layout Guidelines

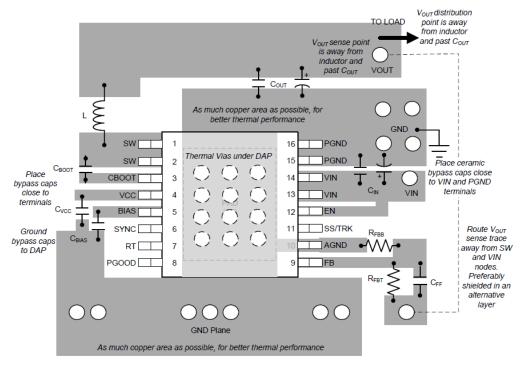

### 9.3.1 LM43602-Q1

Figure 16 LM43602-Q1 Layout Guidelines

- Place ceramic high frequency bypass C<sub>IN</sub> as close as possible to the LM43602-Q1 VIN and PGND pins. Grounding for both the input and output capacitors should consist of localized top side planes that connect to the PGND pins and PAD.

- Place bypass capacitors for VCC and BIAS close to the pins and ground the bypass capacitors to device ground.

- Minimize trace length to the FB pin net. Both feedback resistors, RFBT and RFBB should be located close to the FB pin. Place Cff directly in parallel with RFBT. If Vout accuracy at the load is important, make sure Vout sense is made at the load. Route Vout sense path away from noisy nodes and preferably through a layer on the other side of a shieldig layer.

- Use ground plane in one of the middle layers as noise shielding and heat dissipation path.

- Have a single point ground connection to the plane. The ground connections for the feedback, soft-start, and enable components should be routed to the ground plane. This prevents any switched or load currents from flowing in the analog ground traces. If not properly handled, poor grounding can result in degraded load regulation or erratic output voltage ripple behavior.

- Make VIN, VOUT and ground bus connections as wide as possible. This reduces any voltage drops on the input or output paths of the converter and maximizes efficiency.

- Provide adequate device heat-sinking. Use an array of heat-sinking vias to connect the exposed pad to the ground plane on the bottom PCB layer. If the PCB has multiple copper layers, these thermal vias can also be connected to inner layer heat-spreading ground planes. Ensure enough copper area is used for heat-sinking to keep the junction temperature below 125°C.

TIDUA54 - June 2015

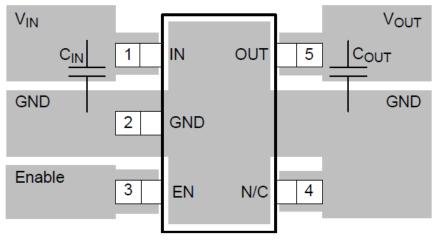

### 9.3.2 LP5907

Best performance is achieved by placing  $C_{IN}$  and  $C_{OUT}$  on the same side of the PCB as the LP5907, and as close as is practical to the package. The ground connections for  $C_{IN}$  and  $C_{OUT}$  should be back to the LP5907 ground pin using as wide, and as short, of a copper trace as is practical.

Connections using long trace lengths, narrow trace widths, and/or connections through vias should be avoided. These will add parasitic inductances and resistance that results in inferior performance especially during transient conditions

Figure 17 LP5907 Layout Guidelines

### 9.4 PCB Design Files

To download the PCB design files, see the design files at <a href="http://www.ti.com/tool/TIDA-00535">http://www.ti.com/tool/TIDA-00535</a>

- Gerber's and NC drills

- Layers prints

Figure 18 TIDA-00535 Top Layer Print

### 10 References

- 1. Texas Instruments, Reference Design, TIDA-00098 Aptina Automotive Camera Module, TIDU239, 2014

- 2. Texas Instruments, Reference Design, TIDA-00262 Optimized Automotive 1M Pixel Camera Module Design, <u>TIDU468</u>, 2014

- 3. Texas Instruments, Automotive Camera Module Power and Serializer Reference Design, <u>TIDU226</u>, 2014

- 4. Texas Instruments Application Report, Sending Power Over Coax in DS90UB913A Designs, <u>SNLA224</u>, 2014

- 5. Texas Instruments, Reference Design, PMP9351, Automotive camera module power and Serializer reference design, <u>PMP9351</u>, 2014

- EE-Times, Design How-To Combine power feed and data link via cable for remote peripherals, <u>1279219</u>, 2011

### 11 Terminology

TI Glossary: SLYZ022 This glossary lists and explains terms, acronyms, and definitions.

### 12 About the Author

#### **Antony Pierre Carvajales**

Antony is an Applications Engineer in the mobile power devices RF power group at Texas Instruments Inc.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated