# Technical Article Get Connected: Failsafe Bias Those Contentious Buses!

## **Michael Peffers**

Welcome back to the Get Connected blog series on Analog Wire. In my previous post, I discussed how to use low-voltage differential signal (LVDS) transceivers as a high-speed comparator in a few different applications. In this post, I'll cover failsafe biasing of differential buses and how to implement failsafe biasing in your next design.

Bus topologies that implement more than one driver and receiver on the bus – known as multipoint – present challenges to system designers given their difference from a point-to-point bus topology. (To review bus topology architectures, see my previous blog post, "LVDS for multipoint applications.") In multipoint applications, bus contention and idle bus conditions can cause collisions or communication glitches on the bus during normal operation. Bus contention occurs when more than one driver is active while the bus is in an indeterminate state;

1

idle bus conditions occur when all of the drivers are in the off or Hi-Z state. The implementation of a failsafe biasing network addresses both of these situations.

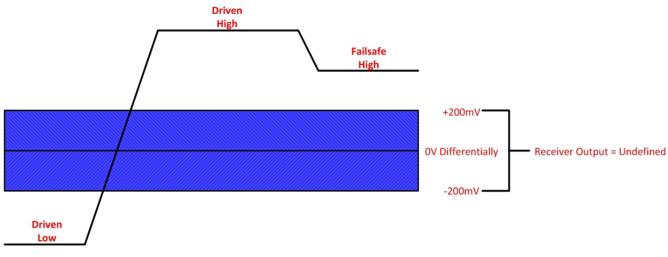

A bus that implements failsafe biasing only has two logic states in which it can exist – high and low –while a bus without failsafe biasing can exist in unknown states. An active driver will drive the bus high and low or bias it to a known state through the failsafe biasing network. Without a failsafe biasing network, the bus will reside in an unknown state in which the receiver output is invalid; noise can couple through the transceiver, causing false transitions. Figure 1 shows the possible states of a typical RS-485 bus with and without failsafe biasing.

#### Figure 1. RS-485 Bus States

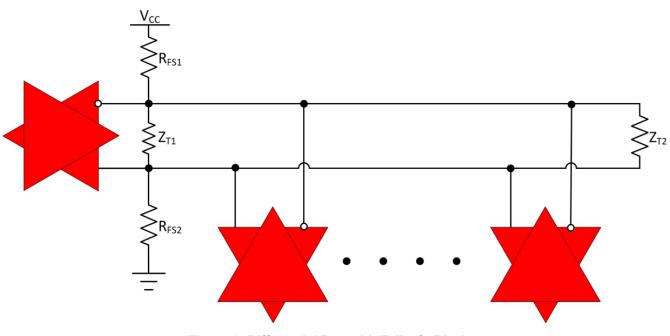

Failsafe bias resistor values are based on the maximum receiver threshold levels of the transceiver devices used in the end application, like the SN65LBC180 RS-485 transceiver. Typically for a RS-485 network the receiver input threshold level is  $\pm 200$ mV and for an LVDS network it is  $\pm 50$ mV. In addition to the receiver threshold levels, the termination resistors R<sub>FS1</sub> and R<sub>FS2</sub> should be equal, as that provides symmetrical loading for the drivers. The equivalent resistance of R<sub>FS1</sub>, Z<sub>T1</sub> and R<sub>FS2</sub> should match the characteristic impedance of the twisted-pair cable or printed circuit board (PCB) trace to maintain signal integrity (Z<sub>T1</sub>||(R<sub>FS1</sub> + R<sub>FS2</sub>). Z<sub>T2</sub> should also match the characteristic impedance of the network, also to maintain signal integrity, by reducing reflections on the network. Figure 2 shows a multipoint bus topology with failsafe biasing implemented.

For more information on failsafe biasing, please see the application note, FAILSAFE Biasing of Differential Buses. Leave a comment below if you'd like to hear more about anything discussed in this post, or if there's an interface topic you'd like to see in the future.

## **Additional Resources**

- Read more posts in the Get Connected series.

- Check out the RS-485 full duplex evaluation module with failsafe biasing option for further bench testing.

- Find out more about TI's RS-485 product portfolio.

3

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated