# Technical Article How LILO LDOs Increase System Efficiency

# Texas Instruments

#### Mark Sellers

High efficiency for power supplies has historically been attributed to switching controllers or converters, whereas designers assume that linear regulators (LDOs) have bad efficiency. But linear regulator topologies have changed to where single n-channel p-channel n-channel (NPN)/p-channel n-channel p-channel (PNP) or p-channel metal-oxide semiconductor (PMOS)/n-channel MOS (NMOS) pass transistors can help achieve very low dropout voltages.

There have been three main power-supply trends in portable systems: decreasing bus voltages, compressed voltage conversions and decreasing quiescent current ( $I_Q$ ). These trends have led to the development of low-input low-output (LILO) LDOs.

As bus voltages have decreased, so have the minimum input voltage requirements for LDOs. As the bus rails dropped below 1.5V, the traditional LDO topology began reaching its limits because the input voltage rail powers all of the internal circuitry. The gradually decreasing input voltage led to the increased popularity of LILO LDOs.

LILO LDOs use an NMOS pass transistor and a bias rail to achieve low dropout. The advantage of using an NMOS pass transistor is that it has a lower drain-to-source resistance ( $R_{DS(on)}$ ) than a PMOS. It also needs a positive gate-to-source voltage (VGS) to operate. As a result of this topology, the bias rail is supplied by a higher voltage and powers most of the LDO's internal circuitry, so the LDO can operate at lower input voltages.

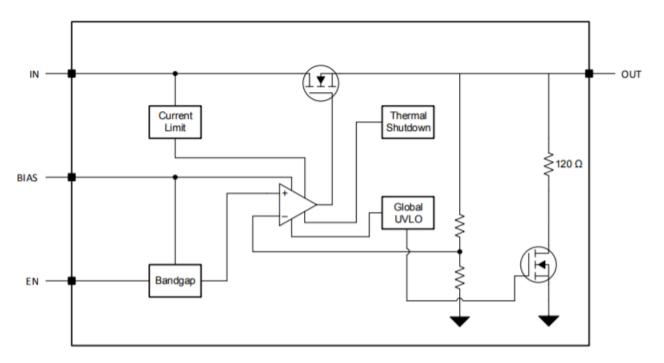

One of the main benefits of the NMOS transistor is the low  $R_{DS(on)}$ , which allows for a smaller dropout per unit area than the PMOS transistor, enabling smaller dropout voltages while maintaining a small size. Figure 1 shows the typical topology of an NMOS LDO from this diagram it can be seen that a Bias pin is required for this LDO to function properly.

1

#### Figure 1. Nmos Ldo Topology

As I said, the two advantages of LILO LDOs are lower input voltages and decreased dropout voltages. The latter advantage enables an increase in efficiency that is comparable to that of switch-mode power supplies. For all power supplies, you can calculate efficiency using #none# as a function of the input and output power:

$$\eta = \frac{P_{OUT}}{P_{IN}} * 100\%$$

(1)

For a LILO LDO like the TPS7A10, you can calculate the efficiency using Figure 2, since the LDO has both a bias rail and an input voltage rail:

$$\eta = \frac{P_{OUT}}{P_{IN}} * 100\% = \frac{V_{OUT} * I_{OUT}}{V_{IN} * I_{IN} + V_{BIAS} * I_{BIAS}} * 100\%$$

Figure 2. (2)

If the load current is much greater than the I<sub>Q</sub> efficiency equation can be simplified, as shown in Figure 3:

$$\eta pprox rac{V_{OUT}}{V_{IN}} st 100\%$$

#### Figure 2. (3)

You can see that the quickest way to increase efficiency in LDOs is to make the input and output voltage closer together by decreasing the dropout voltage.

In portable electronics, it is very common to have LDO-powered sensors because a switching converter generates too much noise. Designers will use low-I<sub>Q</sub> LDOs, believing that they increase the battery life of the system as the load is being pulsed. This is not necessarily the most efficient solution; however, as large power dissipation during the time where the load is on can cause drastically decreased efficiency.

<sup>2</sup> How LILO LDOs Increase System Efficiency

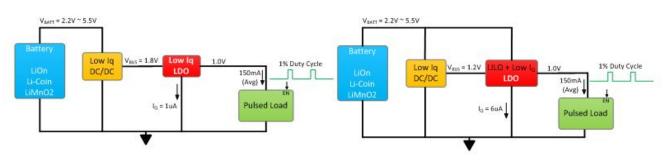

Figure 4 shows two common power configurations for implementing a portable system. One uses a generic low-I<sub>Q</sub> LDO and the other uses a low-I<sub>Q</sub> LILO LDO. Comparing the power dissipation between the two solutions, the generic low-I<sub>Q</sub> LDO dissipates 2.7mW, while the LILO LDO dissipates 1.8mW (see Table 1). Using the LILO LDO increased the efficiency from 55% to 82%, even though the total I<sub>Q</sub> is higher on the LILO LDO.

Figure 2. A low-l<sub>Q</sub> Ldo vs. a Lilo Ldo

| System Details       |                      | Low IQ LDO | LiLo LDO |    |

|----------------------|----------------------|------------|----------|----|

| Voltage Rails        | VBATT                | 3.6        | 3.6      | V  |

|                      | LDO V <sub>IN</sub>  | 1.8        | 1.2      | V  |

|                      | LDO V <sub>OUT</sub> | 1.0        | 1.0      | V  |

| Duty Cycle           | Duty Cycle           | 1          | 1        | %  |

| Load Current<br>+ IQ | I <sub>LOAD</sub>    | 0.15       | 0.15     | A  |

|                      | IQ V <sub>IN</sub>   | 1          | 1.6      | μA |

|                      | IQ V <sub>BIAS</sub> | 0          | 6        | μA |

|                      | PDISS LOAD           | 1.5        | 1.5      | mW |

| Power                | PDISS, LDO           | 1.2        | 0.3      | mW |

| Dissipaton           | PDISS, OFF           | 0.002      | 0.023    | mW |

|                      | PDISS, Total         | 2.702      | 1.823    | mW |

| Efficiency           | Eff, Total           | 55.5       | 82.3     | %  |

Table 1. Efficiency Calculations

As you can see, there is a clear benefit to implementing LILO LDOs in portable applications if battery life and efficiency are your main concerns. Reducing the differential between the input and output voltage enables these LDOs to achieve efficiencies greater than 80%. Once you understand this, you can select the proper LDO for your application.

### Additional Resources

- Read the blog post, "LDO basics: dropout."

- Learn more LDO basics in the LDO basics blog series.

- Check out the Low Dropout Regulators Quick Reference Guide.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated