# Reduction of Power Consumption for TMS570LS3137

Christian Herget and Viktor Schneigelberger

### **ABSTRACT**

This application report describes methods to reduce the power consumption of the Hercules<sup>™</sup>-based microcontrollers and gives indications for the reduction that can be achieved.

All examples and values are based on the TMX570LS3137BZWT microcontroller and are measured on the TI internal silicon checkout board.

### **Measurement Notes**

The measurements were done on non-production silicon and not under controlled environment conditions (unregulated room temp, unregulated humidity). The used measurement equipment was high industry standard. All values in this application report might differ from silicon to silicon, with the used measurement equipment and are superset by the values in the corresponding device-specific data sheets.

# Contents

| 1 | Meas  | urement Setup                                                                 | 2  |

|---|-------|-------------------------------------------------------------------------------|----|

| 2 | Powe  | er Down Functions                                                             | 3  |

|   | 2.1   | Peripheral Power Down                                                         | 3  |

|   | 2.2   | Clock Domains                                                                 | 6  |

|   | 2.3   | Clock Sources                                                                 | 7  |

|   | 2.4   | Power Domains                                                                 | 8  |

|   | 2.5   | Flash Banks                                                                   | ę  |

|   | 2.6   | Low-Power Mode                                                                | 10 |

| 3 | Hints | and Tips                                                                      | 11 |

|   | 3.1   | Terminate Unused GPIOs                                                        | 11 |

|   | 3.2   | Reduce CPU Clock                                                              |    |

|   | 3.3   | Disable Unused Peripherals                                                    | 11 |

|   |       | List of Figures                                                               |    |

| 1 | Perip | heral Central Resource Control Register Implementation                        | 3  |

| 2 | Clock | Domain Diagram                                                                | 6  |

| 3 | Curre | ent Reduction Versus HCLK on TMS570LS3137                                     | 11 |

|   |       | List of Tables                                                                |    |

| 1 | Clock | Domain Frequencies                                                            | 2  |

| 2 | Overa | all Current Consumption                                                       | 2  |

| 3 | Pros  | and Cons of the Different Power Down Functions                                | 3  |

| 4 | Perip | heral Select Definition                                                       | 2  |

| 5 | Perip | hery and Their Peripheral Select, Peripheral Memory and Memory Initialization | 2  |

| 6 |       | heral Select Reduction                                                        |    |

| 7 | Clock | Domains and Their Domain Number                                               | 6  |

| 8 | Clock | Domain Disable Reduction                                                      | 7  |

Hercules is a trademark of Texas Instruments.

Cortex is a trademark of ARM Limited.

ARM is a registered trademark of ARM Limited.

All other trademarks are the property of their respective owners.

Measurement Setup www.ti.com

| 9  | Clock Sources and Their Source Number          | 7  |

|----|------------------------------------------------|----|

| 10 | Power Domains and Their Corresponding Register | 8  |

| 11 | Power Domain Disable Reduction                 | 9  |

| 12 | Flash Bank Fallback Power Register             | 9  |

| 13 | Flash Bank Sleep Mode Reduction                | 10 |

| 14 | Low-Power Modes                                | 10 |

| 15 | Low-Power Mode Consumption                     | 10 |

# 1 Measurement Setup

The measurements were done on a TI internal silicon checkout board with a non-production TMX570LS3137BZWT microcontroller. The ambient temperature and humidity was unchecked and unregulated.

The current consumption of each power rail (1.2 V core + PLL and 3.3 V IO + Flash + ADC) was measured with two Keithley 2000 multimeters, the currents were directly measured through the multimeters.

The microcontroller startup and peripheral initialization were done with the hardware abstraction layer code generator (HALCoGen) v3.01.00 generated functions. All peripheral, as possible, were setup as GIO functional. All GIO pins were set as output and to drive low level. There was no activity on the peripherals. The used CPU frequency (HCLK) was 160 MHz with a 16 MHz oscillator as source. With these, an overall current consumption of about 160 mA for the 1.2 V rail and 70 mA for the 3.3 V was measured.

The reduction of the CPU frequency (HCLK) for the current consumption versus frequency measurements (Section 3.2) was done by reducing the PLL1 frequency. This means that the frequency of all other clock domains connected to PLL1 also was reduced.

Table 1 and Table 2 show the approximate current consumption and clock domain frequencies based on the setup described above for both devices.

**Table 1. Clock Domain Frequencies**

| Clock Domain and<br>Source | Source     | Frequency [MHz] | Maximum Frequency<br>[MHz] |

|----------------------------|------------|-----------------|----------------------------|

| OSC                        | Crystal    | 16.0            | 20.0                       |

| PLL1                       | OSC x 10   | 160.0           |                            |

| PLL2                       | OSC x 6.25 | 160.0           |                            |

| HCLK                       | PLL1       | 160.0           | 180.0                      |

| GCLK                       | HCLK       | 160.0           | 180.0                      |

| VCLK1                      | PLL1 / 2   | 80.0            | 100.0                      |

| VCLK2                      | PLL1 / 2   | 80.0            | 100.0                      |

| VCLK3                      | PLL1 / 2   | 80.0            | 100.0                      |

| AVCLK1                     | VCLK       | 80.0            | 100.0                      |

| AVCLK2                     | VCLK       | 80.0            | 100.0                      |

| AVCLK4                     | VCLK / 2   | 50.0            | 50.0                       |

| RTICLK                     | VCLK       | 80.0            | 100.0                      |

**Table 2. Overall Current Consumption**

| Powe                  | r Rail <sup>(1)</sup>                                                           | TMX570LS3137BZWT |

|-----------------------|---------------------------------------------------------------------------------|------------------|

| Core + PLL [mA]       | I <sub>CC</sub> + I <sub>CCPLL</sub>                                            | 158.8            |

| IO + Flash + ADC [mA] | I <sub>CCIO</sub> + I <sub>CCAD</sub> + I <sub>CCREFHI</sub> + I <sub>CCP</sub> | 69.2             |

<sup>(1)</sup> Rails are divided into 1.2 V and 3.3 V rail and are called as stated in the left column in the rest of this document.

www.ti.com Power Down Functions

## 2 Power Down Functions

Possible features to reduce the power consumption are:

- Peripheral Power Down

- · Clock Domain Disable

- Local Peripheral Power Down

- Power Domain Disable

- Clock Source Disable

- · Flash Bank Suspend

- Low-Power Mode

The peripheral power down, clock domain disable, and local peripheral power down features disable the clock going to the peripheral modules or the RAM's. This reduces the power consumption to its static state value.

The power domain disable feature switches of the supply voltage for a group of modules. With this feature the modules in the power domain will not consume any more power, but this is only available for a group of modules.

The clock sourced disable feature allows disabling the internal clock generation (PLL and LPO) if they are not needed.

The Flash bank suspend feature switch Flash banks into suspend modes. This reduces the power consumption of the Flash module.

The low-power mode feature is a combination of the clock domain disable, clock source disable, and Flash bank suspend features. Also, it sets the core into idle mode.

Table 3 lists the pros and cons of the different power down functions for the peripheral modules.

Table 3. Pros and Cons of the Different Power Down Functions

|                | Pros                                                                   | Cons                                                        |

|----------------|------------------------------------------------------------------------|-------------------------------------------------------------|

| Clock disable  | Available for each single peripheral module and memory                 | Power consumption is only reduced to its steady state value |

| Supply disable | As the supply is completely switched off, no power consumption at all. | Only seven powered domains are available                    |

## 2.1 Peripheral Power Down

The device has 32 peripheral select (PS) and each PS has a size of 1 KB. Depending on the module, the full, half or quarter of a PS can be used. So there are four quadrants for each PS. Each quadrant can be enabled or disabled using the set of Peripheral Central Resource Control Register (PCR): Peripheral Power-Down Set Register (PSPWRDWNSETx) and Peripheral Power-Down Clear Register (PSPWRDWNCLRx). Figure 1 shows the register implementation.

Figure 1. Peripheral Central Resource Control Register Implementation

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| PS7 | PS7 | PS7 | PS7 | PS6 | PS6 | PS6 | PS6 | PS5 | PS5 | PS5 | PS5 | PS4 | PS4 | PS4 | PS4 |

| Q3  | Q2  | Q1  | Q0  |

| 45  | 4.4 | 40  | 40  | 44  | 40  | 0   | 0   | 7   | 0   | -   |     | 0   | 0   |     |     |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | U   |

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| PS3 | PS3 | PS3 | PS3 | PS2 | PS2 | PS2 | PS2 | PS1 | PS1 | PS1 | PS1 | PS0 | PS0 | PS0 | PS0 |

This arrangement is the same for bits of PS8 to PS31.

Power Down Functions www.ti.com

Table 4 shows how the peripheral select is defined.

**Table 4. Peripheral Select Definition**

| Peripheral Select |    | Start Address | End Address |

|-------------------|----|---------------|-------------|

| PS7               |    | 0xFFF7E000    | 0xFFF7E3FF  |

| PS6               |    | 0xFFF7E400    | 0xFFF7E7FF  |

| PS5               |    | 0xFFF7E800    | 0xFFF7EBFF  |

| PS4               |    | 0xFFF7EC00    | 0xFFF7EFFF  |

| PS3               |    | 0xFFF7F000    | 0xFFF7F3FF  |

| PS2               |    | 0xFFF7F400    | 0xFFF7F7FF  |

| PS1               |    | 0xFFF7F800    | 0xFFF7FBFF  |

| PS0               | Q0 | 0xFFF7FC00    | 0xFFF7FCFF  |

|                   | Q1 | 0xFFF7FD00    | 0xFFF7FDFF  |

|                   | Q2 | 0xFFF7FE00    | 0xFFF7FEFF  |

|                   | Q3 | 0xFFF7FF00    | 0xFFF7FFF   |

PS 8 – 31 follows this scheme.

Table 5 shows which PS is used to select a peripheral module and MSINENA, which is used to initialize RAM, that is associated to the peripheral.

Table 5. Periphery and Their Peripheral Select, Peripheral Memory and Memory Initialization

| Module Address Range           | TMS570LS0x32   | TMS570LS12x7            | TMS570LS3137            |

|--------------------------------|----------------|-------------------------|-------------------------|

| FTU                            | -              | PS[23] Q[0, 1]          | PS[23] Q[0, 1]          |

| 0xFFF7A000 - 0xFFF7A1FF        |                | MSINENA[13]             | MSINENA[13]             |

| HTU1                           | PS[22] Q[0]    | PS[22] Q[0]             | PS[22] Q[0]             |

| 0xFFF7A400 - 0xFFF7A4FF        | MSINENA[4]     | MSINENA[4]              | MSINENA[4]              |

| HTU2                           | -              | PS[22] Q[1]             | PS[22] Q[1]             |

| 0xFFF7A500 - 0xFFF7A5FF        |                | MSINENA[16]             | MSINENA[16]             |

| N2HET1                         | PS[17] Q[0]    | PS[17] Q[0]             | PS[17] Q[0]             |

| 0xFFF7B800 - 0xFFF7B8FF        | MSINENA[3]     | MSINENA[3]              | MSINENA[3]              |

| N2HET2                         | -              | PS[17] Q[1]             | PS[17] Q[1]             |

| 0xFFF7B900 - 0xFFF7B9FF        |                | MSINENA[15]             | MSINENA[15              |

| GIO                            | PS[16] Q[0]    | PS[16] Q[0]             | PS[16] Q[0]             |

| 0xFFF7BC00 - 0xFFF7BCFF        | -              | -                       |                         |

| MibADC1                        | PS[15] Q[0, 1] | PS[15] Q[0, 1]          | PS[15] Q[0, 1]          |

| 0xFFF7C000 - 0xFFF7C1FF        | MSINENA[8]     | MSINENA[8]              | MSINENA[8]              |

| MibADC2                        | -              | PS[15] Q[2, 3]          | PS[15] Q[2, 3]          |

| 0xFFF7C200 - 0xFFF7C3FF        |                | MSINENA[14]             | MSINENA[14]             |

| FlexRay                        | -              | PS[12] + PS[13]         | PS[12] + PS[13]         |

| 0xFFF7C800 - 0xFFF7CFFF        |                | Q[0,1,2,3] + Q[0,1,2,3] | Q[0,1,2,3] + Q[0,1,2,3] |

| I2C<br>0xFFF7D400 - 0xFFF7D4FF | -              | PS[10] Q[0]             | PS[10] Q[0]             |

| DCAN1                          | PS[8] Q[0, 1]  | PS[8] Q[0, 1]           | PS[8] Q[0, 1]           |

| 0xFFF7DC00 - 0xFFF7DDFF        | MSINENA[5]     | MSINENA[5]              | MSINENA[5]              |

| DCAN2                          | PS[8] Q[2, 3]  | PS[8] Q[2, 3]           | PS[8] Q[2, 3]           |

| 0xFFF7DE00 - 0xFFF7DFFF        | MSINENA[6]     | MSINENA[6]              | MSINENA[6]              |

| DCAN3                          | -              | PS[7] Q[0, 1]           | PS[7] Q[0, 1]           |

| 0xFFF7E000 - 0xFFF7E1FF        |                | MSINENA[10]             | MSINENA[10]             |

| LIN<br>0xFFF7E400 - 0xFFF7E4FF | PS[6] Q[0]     | PS[6] Q[0]              | PS[6] Q[0]              |

| SCI<br>0xFFF7E500 - 0xFFF7E5FF | -              | PS[6] Q[1]<br>-         | PS[6] Q[1]              |

| MibSPI1                        | PS[2] Q[0, 1]  | PS[2] Q[0, 1]           | PS[2] Q[0, 1]           |

| 0xFFF7F400 - 0xFFF7F5FF        | MSINENA[7]     | MSINENA[7]              | MSINENA[7]              |

www.ti.com Power Down Functions

Table 5. Periphery and Their Peripheral Select, Peripheral Memory and Memory Initialization (continued)

| Module Address Range                | TMS570LS0x32       | TMS570LS12x7                 | TMS570LS3137                 |

|-------------------------------------|--------------------|------------------------------|------------------------------|

| SPI2<br>0xFFF7F600 - 0xFFF7F7FF     | PS[2] Q[2, 3]<br>- | PS[2] Q[2, 3]<br>-           | PS[2] Q[2, 3]                |

| MibSPI3<br>0xFFF7F800 - 0xFFF7F9FF  | -                  | PS[1] Q[0, 1]<br>MSINENA[11] | PS[1] Q[0, 1]<br>MSINENA[11] |

| SPI3<br>0xFFF7F800 - 0xFFF7F9FF     | PS[1] Q[0, 1]<br>- | -                            | -                            |

| SPI4<br>0xFFF7FA00 - 0xFFF7FBFF     | -                  | PS[1] Q[2, 3]                | PS[1] Q[2, 3]                |

| MibSPI5<br>0xFFF7FC00 - 0xFFF7FDFF" | -                  | PS[0] Q[0, 1]<br>MSINENA[12] | PS[0] Q[0, 1]<br>MSINENA[12] |

|                                     |                    |                              |                              |

For more information, see the *Device Memory Map* section of the device-specific data sheet.

NOTE: Every access to a register of a module where clock supply is disabled will reactivate the clock supply as long as the access continues.

#### 2.1.1 Example Disabling MibSPI1

The corresponding PS decodes all addresses between 0xFFF7F400 and 0xFFF7F7FF. MIBSPI1 and SPI2 are mapped to this PS2 as following:

- PS2 quadrant 0 and quadrant 1 are for MibSPI1 for a total of 512 bytes

- PS2 quadrant 2 and quadrant 3 are for SPI2 for a total of 512 bytes

To disable the MibSPI1, bits 8 and 9 of the Peripheral Power-Down Set Register 0 (PSPWRDWNSET0) have to be set.

NOTE: Disabling a module that has a memory can produce an error when the Memory Initialization Enable Register (MSINENA) of the Memory Hardware Initialization Control Registers is not adjusted.

The preferred method should be to disable both the peripheral and the memory initialization.

For more information, see the Auto-Initialization of Device Memories section of the device-specific data manual.

#### 2.1.2 Results

Table 6 shows the approximate current reduction in mA based on the setup described in Section 1, which can be achieved by switching the clock supply to a peripheral module off.

**Table 6. Peripheral Select Reduction**

| Power Rail             | FTU | HTU | N2HET | GIO | MibADC | FlexRay | I2C | DCAN | LIN | SCI | MibSPI |

|------------------------|-----|-----|-------|-----|--------|---------|-----|------|-----|-----|--------|

| Core + PLL [mA]        | 1.8 | 0.4 | 7.5   | 0.2 | 0.4    | 2.1     | 0.3 | 0.2  | 0.5 | 0.3 | 1.3    |

| IO + Flash<br>ADC [mA] | 0.0 | 0.0 | 0.0   | 0.0 | 6.0    | 0.0     | 0.0 | 0.0  | 0.0 | 0.0 | 0.0    |

Power Down Functions www.ti.com

# 2.2 Clock Domains

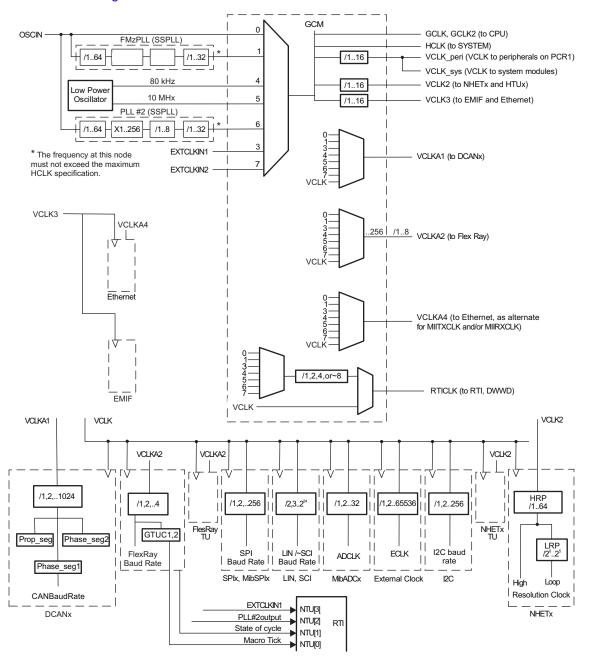

The clocking on the device is divided into multiple clock domains for flexibility in control as well as clock source selection. Figure 2 and Table 7 shows the available clock domains.

Figure 2. Clock Domain Diagram

**Table 7. Clock Domains and Their Domain Number**

| Clock Domain | Domain Number |

|--------------|---------------|

| GCLK / GCLK2 | 0             |

| HCLK         | 1             |

| VCLK         | 2             |

| VCLK2        | 3             |

| VCLK3        | 8             |

www.ti.com Power Down Functions

Table 7. Clock Domains and Their Domain Number (continued)

| Clock Domain | Domain Number |

|--------------|---------------|

| AVCLK1       | 4             |

| AVCLK2       | 5             |

| AVCLK3 (1)   | 10            |

| AVCLK4       | 11            |

| RTICLK       | 6             |

<sup>(1)</sup> Not available on TMS570.

Each clock domain can be independently enabled or disabled using the set of registers: Clock Domain Disable Register (CDDIS), Clock Domain Disable Set Register (CDDISSET) and the Clock Domain Disable Clear Register (CDDISCLR).

Each bit in these registers corresponds to the clock domain number. For example:

Setting bit 1 in the CDDIS or CDDISSET registers disables the HCLK clock domain.

All clock domains are enabled by default, or upon a system reset, or whenever a wake up condition is detected.

**NOTE:** The clock domain is turned off only when every module that uses the HCLK domain is in idle or disabled.

For more information, see the Clock Domains chapter of the device-specific technical reference manual.

### 2.2.1 Results

Table 8 shows the approximate current reduction in mA based on the setup described in Section 1, which can be achieved by switching a clock domain off.

**Table 8. Clock Domain Disable Reduction**

| Power Rail                  | VCLK | VCLK2 | VCLK3 | AVCLK1 | AVCLK2 | AVCLK4 | RTICLK1 | HCLK | GCLK |

|-----------------------------|------|-------|-------|--------|--------|--------|---------|------|------|

| Core + PLL<br>[mA]          | 27.2 | 17.8  | 9.9   | 4.7    | 7.2    | 5.0    | 4.8     | 4.6  | 4.6  |

| IO + Flash<br>+<br>ADC [mA] | 12.3 | 0.4   | 21.8  | 0.4    | 0.4    | 0.3    | 0.4     | 0.4  | 0.4  |

# 2.3 Clock Sources

Table 9 shows the available clock sources.

**Table 9. Clock Sources and Their Source Number**

| Clock Source      | Source Number |

|-------------------|---------------|

| OSCIN             | 0             |

| PLL 1             | 1             |

| (Not implemented) | 2             |

| EXTCLKIN 1        | 3             |

| LF LPO            | 4             |

| HF LPO            | 5             |

| PLL 2             | 6             |

| EXTCLKIN 2        | 7             |

Power Down Functions www.ti.com

Each clock source can be independently enabled or disabled using the set of registers: Clock Source Disable Register (CSDIS), Clock Source Disable Set Register (CSDISSET), and the Clock Source Disable Clear Register (CSDISCLR).

Each bit in these registers corresponds to the clock source number. For example:

Setting bit 1 in the CSDIS or CSDISSET registers disables the PLL#1.

NOTE: The clock source is only disabled once there is no active clock domain that is using the clock source. So, the application has to first disable all of the clock domains that are using the clock source or switch them to another clock source.

The Clock Source Valid Status Register (CSVSTAT) indicates the current clock source stats. On the TMS570LS3137 microcontrollers, the clock sources 0, 4 and 5 are enabled by default.

**NOTE:** By default, the clock monitoring circuit is enabled and checks for the main oscillator frequency to be within a certain range using the HF LPO as a reference. If the main oscillator or the HF LPO are disabled with the clock monitoring still enabled, the clock monitor will indicate an oscillator fault. The clock monitoring must be disabled before disabling the main oscillator or the HF LPO clock source.

For more information, see the Clock Sources chapter of the device-specific technical reference manual.

#### **Power Domains** 2.4

The core logic is divided into several domains that can be independently turned on or off based on the application's requirements.

NOTE: The microcontrollers only support static switching of the power domains. That is, the power domains can be turned ON or OFF one time during device initialization. Once configured, it is not allowed to change the state of a power domain without first asserting a system reset.

Table 10 shows the available core power domains.

Table 10. Power Domains and Their Corresponding Register

| <b>Power Domain</b> | Modules                                                                                         | Register                                 |

|---------------------|-------------------------------------------------------------------------------------------------|------------------------------------------|

| PD1                 | Cortex-R4F CPU, Flash interface, TCRAM interface, clock control, basic peripheral set, 64KB RAM | Always on                                |

| PD2                 | EGTM, RTP, DMM, ETMR4, FuseFarm, CSTPIU, POM                                                    | PDCLKDISREG[0]<br>LOGICPDPWRCTRL0[27-24] |

| PD3                 | N2HET2, HTU2, SPI4, MIBADC2, DCAN3, SCI, I2C, DCC2                                              | PDCLKDISREG[1]<br>LOGICPDPWRCTRL0[19-16] |

| PD4                 | FlexRay, FTU                                                                                    | PDCLKDISREG[2]<br>LOGICPDPWRCTRL0[11-8]  |

| PD5                 | Ethernet, EMIF                                                                                  | PDCLKDISREG[3]<br>LOGICPDPWRCTRL0[3-0]   |

| RAM_PD1             | 64 KB RAM                                                                                       | MEMPDPWRCTRL0[27-24]                     |

| RAM_PD2             | 64 KB RAM                                                                                       | MEMPDPWRCTRL0[19-16]                     |

| RAM_PD3             | 64 KB RAM                                                                                       | MEMPDPWRCTRL0[11-8]                      |

PD1 is an "always-ON" power domain, which cannot be turned off. PD2 - PD5 can be turned off by doing the following steps:

- 1. Set the corresponding bit in the Power Domain Clock Disable Register (PDCLKDISREG) to disable all clocks to the power domain.

- 2. Write 0xA to the corresponding position in the Logic Power Domain Control Register (LOGICPDPWRCTRL0) to power down the domain.

www.ti.com Power Down Functions

3. Optional: Poll for LOGICPDPWRSTATx to become "00". The power domain is now powered down.

A power domain with only SRAM macros does not have a clock input, so the sequence is shorter. This applies to RAM\_PD1 - RAM PD3:

- 1. Write 0xA to the corresponding position in the Memory Power Domain Control Register 0 (MEMPDPWRCTRL0) to power down the domain.

- 2. Optional: Poll for MEMPDPWRSTATx to become "00". The power domain is now powered down.

NOTE: The logic in the modules that are powered down loses its power completely. Any access to modules that are powered down results in an abort being generated. When power is restored, the modules power-up to their default states (after normal power-up). No register or memory contents are preserved in the core domains that are turned off.

#### 2.4.1 Results

Table 11 shows the approximate current reduction in mA based on the setup described in Section 1, which can be achieved by switching a power domain off.

**Table 11. Power Domain Disable Reduction**

| Power Rail            | PD2 | PD3  | PD4 | PD5  | RAM_PD |

|-----------------------|-----|------|-----|------|--------|

| Core + PLL [mA]       | 8.6 | 11.5 | 9.3 | 10.7 | 4.7    |

| IO + Flash + ADC [mA] | 0.4 | 5.8  | 0.4 | 21.8 | 0.4    |

#### Flash Banks 2.5

Flash is divided into three banks that can be independently switched to active, standby, and sleep mode based on the time since the last access. The time and the mode can be set using the set of the Flash control register: Flash Bank Fallback Power Register (FBFALLBACK) and Flash Bank Access Control Register (FBAC).

Table 12 shows the Flash bank fallback mode implementation.

Table 12. Flash Bank Fallback Power Register

| Field    | Value | Description  |

|----------|-------|--------------|

| BANKPWR0 | 0h    | Sleep mode   |

|          | 1h    | Standby mode |

|          | 3h    | Active mode  |

This arrangement is the same for the other banks.

After the last access to a Flash bank, the active grave time counter starts to count down before putting the bank into one of the fallback power modes as determined by the FBFALLBACK register. This active grave time can be assigned in the BAGP field of the Flash bank access control register.

**NOTE:** The active grave time value must be greater than 1 when the fallback mode is not active.

For more information, see the Flash module chapter of the device-specific technical reference manual.

Power Down Functions www.ti.com

### 2.5.1 Results

Table 13 shows the approximate current reduction in mA based on the setup described in Section 1, which can be achieved by switching a Flash bank to sleep mode.

Table 13. Flash Bank Sleep Mode Reduction

| Power Rail            | Bank 0 | Bank 1 | Bank 7 |  |

|-----------------------|--------|--------|--------|--|

| Core + PLL [mA]       | 0.0    | 0.0    | 0.0    |  |

| IO + Flash + ADC [mA] | 10.2   | 5.2    | 7.9    |  |

# 2.6 Low-Power Mode

The ARM® Cortex™-R4F CPU has internal power management logic, and requires a dedicated instruction to be used in order to enter a low-power mode. This is the Wait For Interrupt (WFI) instruction. When a WFI instruction is executed, the Cortex-R4F core flushes its pipeline, flushes all write buffers, and completes all pending bus transactions. At this time the core indicates to the system that the clock to the core can be stopped. This indication is used by the Global Clock Module (GCM) to turn off the CPU clock domain (GCLK) if the CDDIS register bit 0 is set. Table 14 shows the low-power modes.

**Table 14. Low-Power Modes**

|        | Active Clock Source | Active Clock Domain | Wake Up Options    |

|--------|---------------------|---------------------|--------------------|

| Doze   | Main oscillator     | RTICLK              | RTI, GIO, CAN, SCI |

| Snooze | LF LPO              | RTICLK              | RTI, GIO, CAN, SCI |

| Sleep  | None                | None                | GIO, CAN, SCI      |

The typical software sequence to enter a low-power mode is as follows:

- 1. Program the Flash banks fallback modes to be "sleep". The Flash banks start switching from active to sleep mode only after the banks are not accessed for at least a duration defined by the Active Grace Period (AGP) parameter configured for the banks.

- 2. Disable the clock sources that are not required to be kept active. A clock source does not get disabled until all clock domains using that clock source are disabled first or are configured to use an alternate clock source.

- 3. Disable the clock domains that are not required to be kept active. A clock domain does not get disabled until all modules using that clock domain are disabled or in idle.

- 4. Idle the Cortex-R4F core. To idle the core uses the WFI instruction.

### 2.6.1 Results

Table 15 shows the approximate current in mA based on the setup described in Section 1, which will be consumed after switching to a low-power mode.

**Table 15. Low-Power Mode Consumption**

| Power Rail            | Normal | Snooze | Doze | Sleep |

|-----------------------|--------|--------|------|-------|

| Core + PLL [mA]       | 158.0  | 17.3   | 17.3 | 1.7   |

| IO + Flash + ADC [mA] | 68.9   | 8.7    | 8.7  | 1.6   |

| Wake up time [us]     | _      | 18.0   | 18.0 | 800.0 |

www.ti.com Hints and Tips

# 3 Hints and Tips

Some hints and tips to reduce the power consumption are listed and discussed in this section.

### 3.1 Terminate Unused GPIOs

When an unused port pin is left undefined or non-terminated, the floating voltage or shoot-through current on the pin can increase the overall current consumption. To avoid this, each and every port on the device needs to be initialized and terminated. Unused pins should be set as output and drive low level.

# 3.2 Reduce CPU Clock

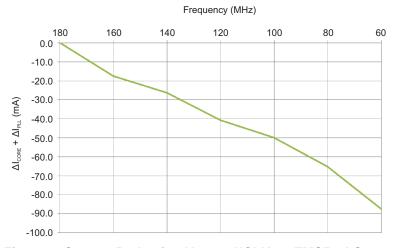

A higher clock frequency results a faster charge reversal, this increases the overall current consumption. The highest frequency for the application should be used instead of using the highest 'available' frequency. Figure 3 shows the current reduction versus HCLK for TMS570LS3137, the VLCK:HCLK ratio was fixed to 1:2 during these measurements. For more information regarding the setup, see Section 1.

Figure 3. Current Reduction Versus HCLK on TMS570LS3137

# 3.3 Disable Unused Peripherals

When an unused peripheral is left activated, it is still powered. To avoid unnecessary power consumption, all unused peripherals should be disabled.

### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

### Products Applications

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers DI P® Products Consumer Electronics www.dlp.com www.ti.com/consumer-apps

DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface Medical www.ti.com/medical interface.ti.com Logic logic.ti.com Security www.ti.com/security

Power Mgmt <u>power.ti.com</u> Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>