# LM3627x Layout Guidelines

Travis Eichhorn

#### ABSTRACT

This document describes the optimized layout for the LM3627x family of white LED backlight + LCD display bias power IC's. The goal of utilizing a good layout is to minimize the PCB trace inductance in the high di/dt current paths, to limit capacitive coupling from high dV/dt nodes onto other traces, and to ensure proper GND connections. The layout described here is not the only method for arranging the external components around the device. There can be alternative methods; however, this layout is proven and will most likely provide the best operation of the device due to the optimization of PCB trace inductance and the suggested grounding method. The land patterns used in this layout guide do not imply any specific size or type of component. They are there to simply show the placement of the component in its optimum position with respect to the IC. The LM36274 is a versatile white LED backlight + LCD bias power source and therefore the size and value of the components can vary greatly depending on the operating conditions.

#### Contents

| 1 | Typical Application Circuit | 2 |

|---|-----------------------------|---|

| 2 | Layout Procedure            | 3 |

#### List of Figures

| 1  | Typical Application Circuit                                  | 2  |

|----|--------------------------------------------------------------|----|

| 2  | Backlight Output Capacitor Placement                         | 3  |

| 3  | Schottky Diode Placement                                     | 3  |

| 4  | Backlight Inductor Placement                                 | 4  |

| 5  | Backlight Inductor Input Bypass Capacitor Placement (CIN_BL) | 5  |

| 6  | BIAS Boost Output Capacitor Placement (COUT_LCM)             | 6  |

| 7  | BIAS Boost Inductor Placement (L_LCM)                        | 7  |

| 8  | BIAS Boost Input Capacitor Placement (CIN_LCM)               | 8  |

| 9  | Flying Capacitor Placement (CFLY)                            | 9  |

| 10 | Inverting Charge Pump Output Capacitor Placement (CNEG)      | 10 |

| 11 | Positive LDO Output Capacitor Placement (CPOS)               | 11 |

| 12 | IN Bypass Capacitor Placement (CIN)                          | 12 |

| 13 | Connecting to the Mid Layer GND Plane                        | 13 |

| 14 | Connecting AGND to the Power Ground (BL_GND and LCM_GND)     | 14 |

| 15 | Via's Connecting BL_GND/LCM_GND to Mid Layer Plane           | 15 |

| 16 | Connecting Backlight Output Sense                            | 16 |

|    |                                                              |    |

### Trademarks

All trademarks are the property of their respective owners.

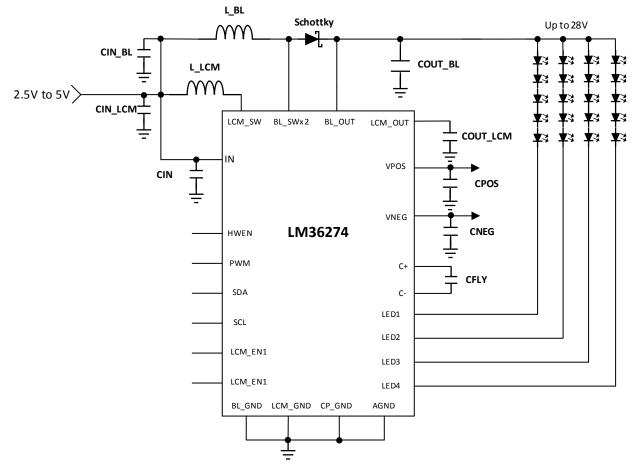

# **1** Typical Application Circuit

Figure 1 shows the typical application circuit for the LM36274 with the component names used in this layout guideline document.

Figure 1. Typical Application Circuit

#### 2 Layout Procedure

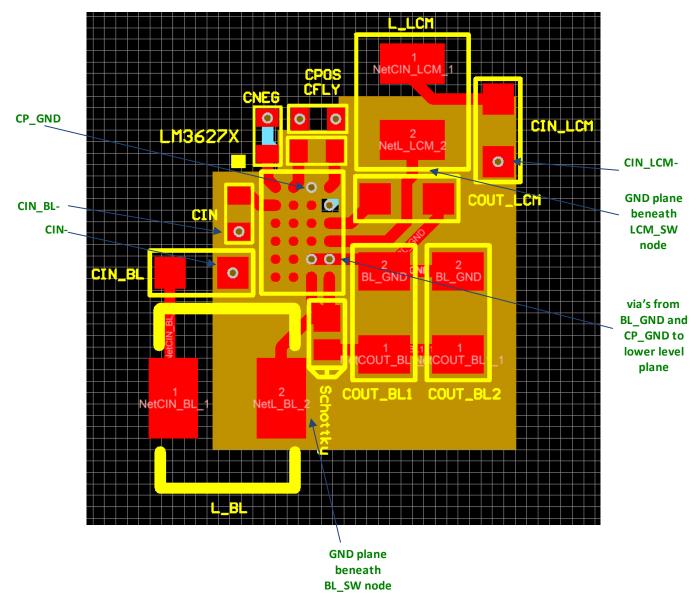

The 15 steps in the following sections detail the step-by-step procedure for connecting the external components around the IC beginning with the most important component to the least. Because the backlight boost carries the highest peak current and highest voltage, the layout guidelines begin with the placement of the backlight boost components, most specifically the backlight boost output capacitor.

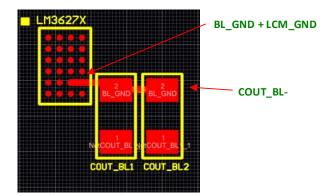

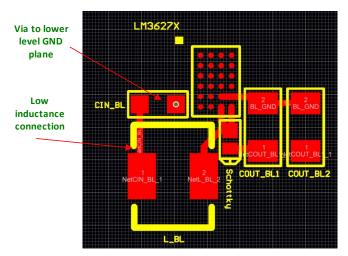

### 2.1 Backlight Output Capacitor (COUT\_BL)

First, place COUT\_BL (or the parallel combination of multiple capacitors) on the same layer as the LM3627X. COUT\_BL will carry the highest dl/dt in the circuit. The dl can be up to the peak current of the backlight boost (1.8 A) and dt is around 1ns, therefore a low inductance placement of this component is the most critical. Low inductance means avoiding vias and placing COUT\_BL as close as possible to GND and the Schottky diode cathode. The GND side of COUT\_BL (COUT\_BL-) must connect as close as possible to the BL\_GND and LCM\_GND bump connection at the IC. The positive terminal (COUT\_BL+) is placed so that the Schottky diode cathode and COUT\_BL+ have the shortest possible connection.

Figure 2 shows the placement of two parallel capacitors. Having a single capacitor is possible given the single capacitor provides enough capacitance at the operating voltage and temperature. See the LM3627x data sheets for the recommended capacitor values.

Figure 2. Backlight Output Capacitor Placement

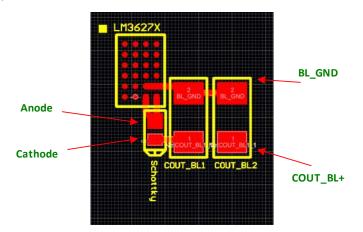

### 2.2 Schottky Diode

Place the Schottky diode on the same layer as COUT\_BL and as close as possible to the (COUT+ terminal and the BL\_SW bump). The same discontinuous inductor current that goes through COUT\_BL also conducts through the Schottky. Therefore, having a short connection from BL\_SW to Schottky anode and from Schottky cathode to COUT\_BL+ minimizes the PCB inductance and minimizes any high frequency voltage spikes.

Figure 3. Schottky Diode Placement

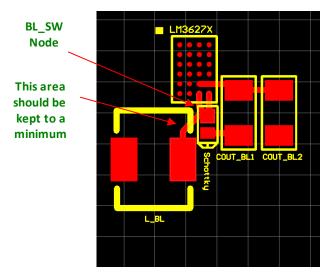

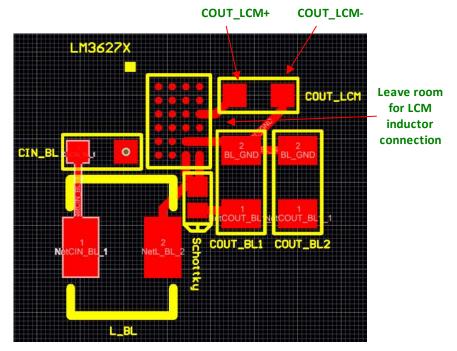

#### 2.3 Backlight Inductor Placement

Connect the backlight inductor (L\_BL) to the backlight switching node (Schottky anode and BL\_SW bump connection). The connection from L\_BL to BL\_SW should be as small in area as possible in order to reduce possible capacitive coupling to nearby traces and to minimize the capacitance at BL\_SW to as little as possible. Any extra capacitance at this node will be extra switching loss in the backlight circuit.

The BL\_SW capacitive switching loss is  $\frac{1}{2} \times C_{\text{SW(TOTAL)}} \times V_{\text{OUT}}^2 \times f_{\text{SW}}$ , so even 20 pF of extra capacitance can account for over 7 mW, which can lead to a 2% efficiency reduction at light loads.

**Figure 4. Backlight Inductor Placement**

# 2.4 Backlight Inductor Input Bypass Capacitor (CIN\_BL)

Connect an input bypass capacitor (CIN\_BL) as close to L\_BL(IN) as possible. A close connection to L\_BL(IN) are for two main reasons:

- First, CIN\_BL reduces the effect of any inductance seen between the backlight inductor and the input source (VBATT). Inductance between VBATT and the backlight inductor can lead to higher than expected current ripple at the input of L\_BL. This ripple comes as a result of an under damped LC circuit between VBATT and L\_BL. This underdamped (high Q) circuit can have a resonant frequency near to the switching frequency of the boost.

- 2. Second, CIN\_BL will filter the input ripple generated from the BIAS portion of the LM3627X. When the BIAS portion of the LM3627X is used, it operates in a PFM mode for much of the VPOS and VNEG loading (except high currents). This PFM mode causes a low frequency burst, with a load dependent frequency. This can generate a low frequency voltage ripple at VIN which can appear as a fast line transient at the backlight input. A closely placed CIN\_BL will reduce this input disturbance and help prevent noise from being generated on the backlight output. This bypass capacitor works together with CIN\_LCM, and when L\_BL and L\_LCM are place close together the inductors can share their input bypass capacitor

The GND side of CIN\_BL can connect down to a lower layer GND plane where it will return back to the BL\_GND, LCM\_GND connection.

Figure 5. Backlight Inductor Input Bypass Capacitor Placement (CIN\_BL)

#### Layout Procedure

### 2.5 BIAS Boost Output Capacitor (COUT\_LCM)

Place the BIAS Boost output capacitor positive terminal (COUT\_LCM+) as close as possible to the LCM\_OUT bump and connect the BIAS boost output capacitor negative terminal as close as possible to (COUT\_LCM-). Close placement of this capacitor minimizes the inductance seen in series with COUT\_LCM. This path carries the discontinuous LCM boost inductor current which can have a high di/dt. The di can be as high as the peak inductor current of the LCM\_BOOST (around 1A) and dt can be < 1 ns. Reducing the inductance in series with this discontinuous current minimizes the high frequency voltage spike generated at LCM\_OUT.

Figure 6. BIAS Boost Output Capacitor Placement (COUT\_LCM)

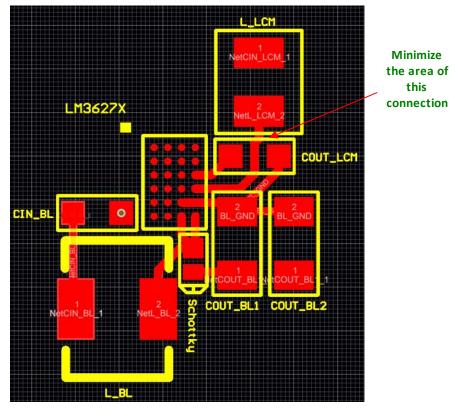

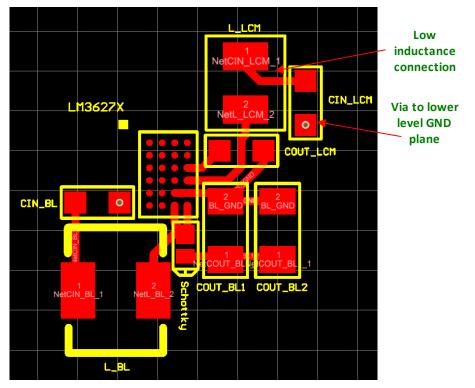

# 2.6 BIAS Boost Inductor (L\_LCM)

Connect the LCM inductor (L\_LCM) to the LCM\_SW bump. The connection from L\_LCM to LCM\_SW should be as small in area as possible in order to reduce possible capacitive coupling to nearby traces and to minimize the capacitance at LCM\_SW to as little as possible. The same reasoning that applies to the L\_BL also applies to L\_LCM with regards to extra PCB capacitance and efficiency reduction.

Figure 7. BIAS Boost Inductor Placement (L\_LCM)

# 2.7 BIAS Boost Input Capacitor (CIN\_LCM)

Connect an input bypass capacitor (CIN\_LCM) as close as possible to the input of L\_LCM. (CIN\_LCM+) must connect very close to the inductor input. The GND side of CIN\_LCM can via down to the lower lavel GND plane. CIN\_LCM is necessary for two reasons:

- First, CIN\_LCM reduces the effect of any inductance seen between the BIAS inductor and the input source (VBATT). Inductance between VBATT and L\_LCM can lead to higher than expected current ripple at the inductor input. This ripple comes as a result of an underdamped LC circuit between VBATT and the inductor. This underdamped (high Q) circuit can have a resonant frequency near to the switching frequency of the boost.

- 2. Second, CIN\_LCM helps filter the input ripple generated from the BIAS boost of the LM3627X. When the BIAS portion of the LM3627X is used, it operates in a PFM mode for much of the VPOS and VNEG loading (except high currents). This PFM mode causes a low frequency burst, with a load dependent frequency. This can generate a low frequency voltage ripple at VIN. A closely placed CIN\_LCM reduces this input disturbance and help prevent noise from being generated on the input. This bypass capacitor works together with CIN\_BL. If L\_BL and L\_LCM are place close together the inductors can share a single input bypass capacitor.

Figure 8. BIAS Boost Input Capacitor Placement (CIN\_LCM)

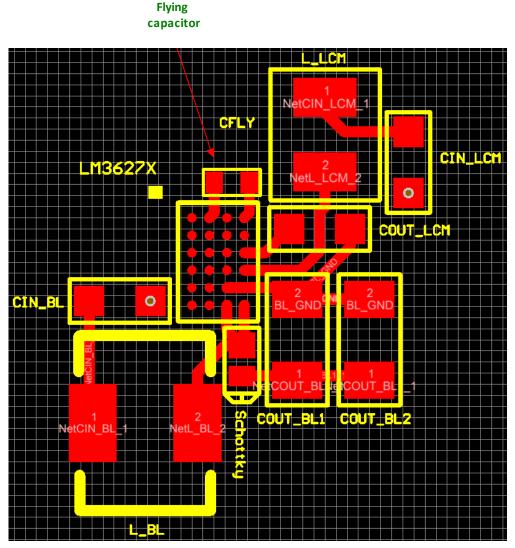

# 2.8 Flying Capacitor (CFLY)

Connect the flying capacitor for the negative charge pump as close as possible to the C- and C+ bumps. The flying capacitor can have a high di/dt (up to 1A/ns). Minimizing the connections from the C+ and Cbumps minimizes this inductance and reduce the conducted noise. Additionally, limiting this connection length limits the area of the PCB trace and thus minimize the added PCB capacitance and help maximize efficiency in th BIAS supply.

Figure 9. Flying Capacitor Placement (CFLY)

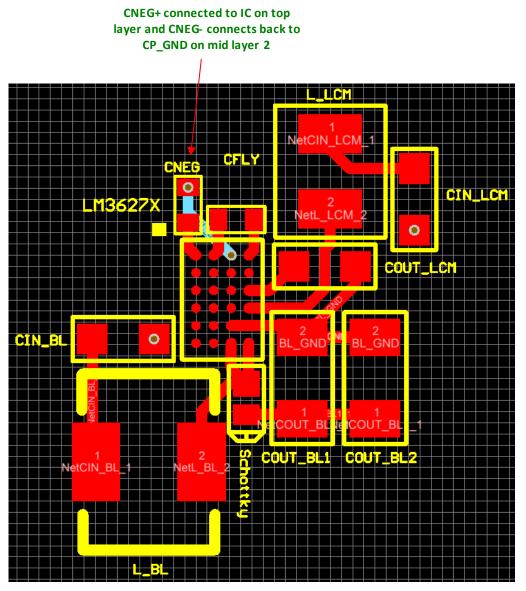

### 2.9 VNEG Output Capacitor (CNEG)

Connect the inverting charge pump output capacitor (CNEG) as close as possible to the NEG bump. This capacitor can see relatively high di/dt when VNEG is active. Limiting the connection from NEG to CNEG+ limits the high frequency noise generated from the charge pump onto the VNEG line. The GND side of this capacitor can via down and connect back to CP\_GND through a lower level layer. The connection from CNEG- to CP\_GND should be routed as short as possible.

Figure 10. Inverting Charge Pump Output Capacitor Placement (CNEG)

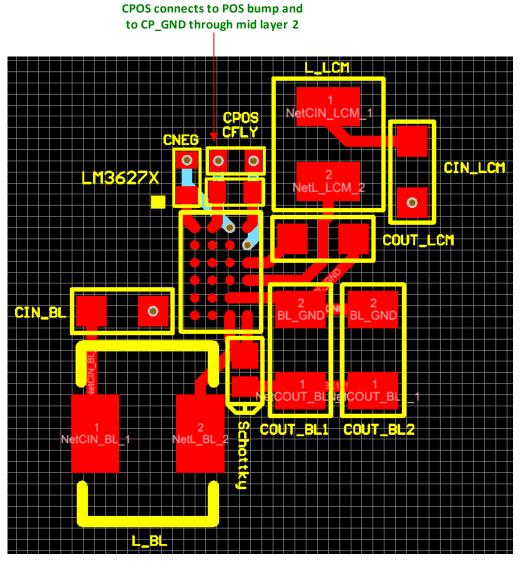

# 2.10 Positive LDO Output Capacitor(CPOS)

Connect CPOS as close to the part as possible. CPOS can connect to the POS bump and to CP\_GND through vias on a lower level plane. This is the least critical component in the BIAS power path because of its continuous output and GND current, although close placement of this capacitor to the IC minimizes the trace area of the CPOS+ and CPOS- connection and help reduce any possible conducted noise generated due to the LCM BIAS boost switching and capacitively coupled noise from LCM\_SW.

Figure 11. Positive LDO Output Capacitor Placement (CPOS)

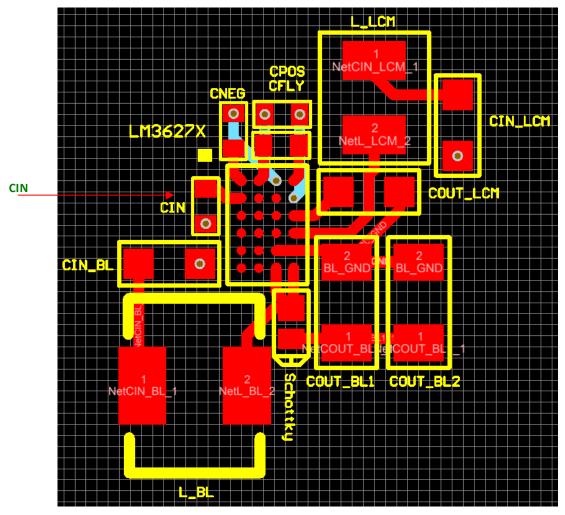

### 2.11 Input Bypass Capacitor (CIN)

Connect the input bypass capacitor CIN as close as possible to IN. CIN+ connects directly to the IN bump of the device. CIN– can via down to the lower level GND plane. This capacitor provides for a low impedance path for the driver circuits in the LM3627x; therefore, placing CIN very close to the device ensures the lowest impedance source for the fast di/dt required for the IC's FET drivers.

Figure 12. IN Bypass Capacitor Placement (CIN)

#### Layout Procedure

#### www.ti.com

### 2.12 Mid Layer Ground Plane

Connect CIN\_BL–, CIN–, CP\_GND, BL\_GND, LCM\_GND, and CIN\_LCM– to a lower level GND plane. This GND plane should go directly underneath the BL\_SW and the LCM\_SW. This creates a distributed PCB capacitance directly underneath the high dV/dt switching nodes and provides for a low impedance to GND for these high frequency voltages. Additionally, placing the GND plane directly beneath the BL\_SW and LCM\_SW prevents any traces from being placed underneath these high dV/dt nodes, which can lead to unwanted capacitive coupling and interference.

Figure 13. Connecting to the Mid Layer GND Plane

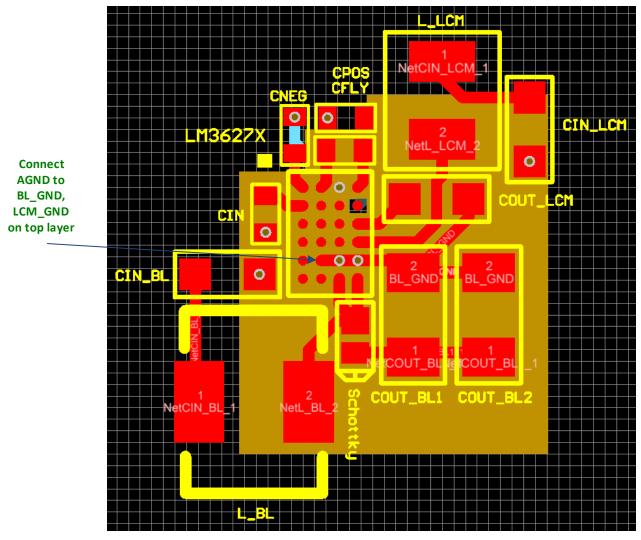

#### 2.13 AGND Connection

13. Connect AGND to the LCM\_GND, and BL\_GND. AGND can connect directly to LCM\_GND on the top layer (as shown in Figure 14) or AGND can connect directly to the lower level GND plane along with LCM\_GND and BL\_GND. The important thing to ensure is that the return current of the power devices (COUT\_BL, COUT\_LCM, CIN\_BL, CIN\_LCM, CIN, and CP\_GND have a low impedance path back to BL\_GND and LCM\_GND. This path should not share any current between AGND and the LCM\_GND/BL\_GND connection.

Figure 14. Connecting AGND to the Power Ground (BL\_GND and LCM\_GND)

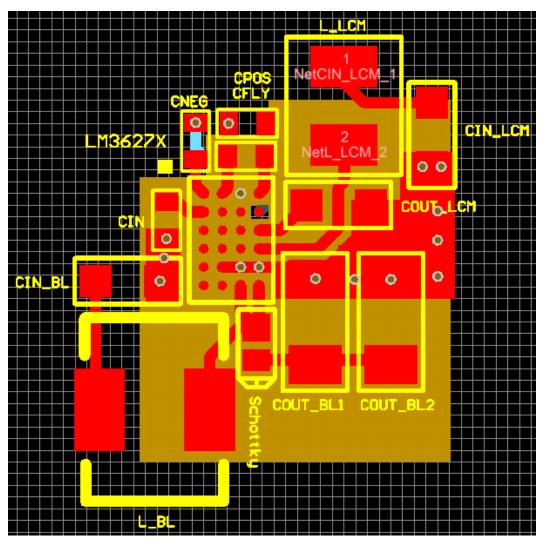

# 2.14 Adding More Vias

Add more via's to further decrease the impedance between the top layer GND nodes and the mid layer GND plane.

Figure 15. Via's Connecting BL\_GND/LCM\_GND to Mid Layer Plane

Layout Procedure

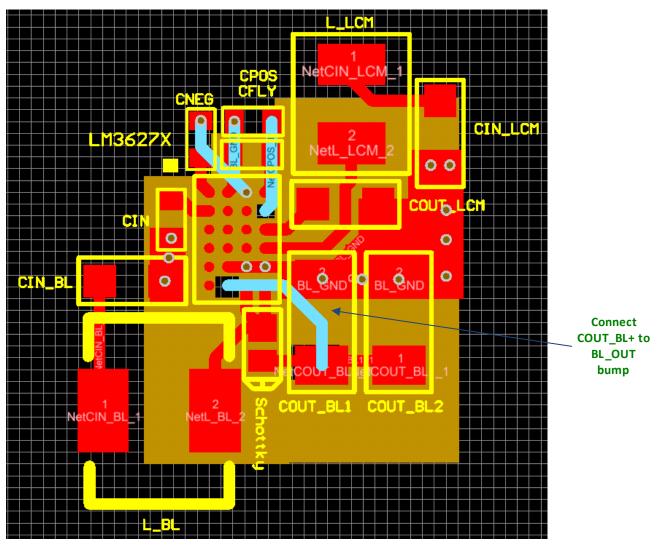

### 2.15 Connect BL\_OUT to COUT\_BL+

Connect the positive terminal of the backlight output capacitor to the BL\_OUT bump. BL\_OUT serves as the sense for overvoltage (OVP). BL\_OUT is a high impedance input, so a short connection is not critical. However placing the lower level GND plane beneath the BL\_OUT to COUT\_BL+ trace prevents coupling from BL\_SW.

Figure 16. Connecting Backlight Output Sense

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated