# AN-2259 LM3556 1.5A Synchronous Boost LED Flash Driver w/ High-Side Current Source Evaluation Board

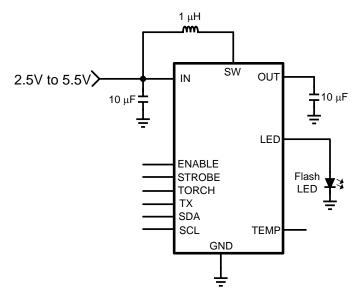

# **1** Typical Application Drawing

Table 1. Bill of Materials

| Item | Designator                         | Description                                                         | RoHS | Manufacturer     | Part Number         |

|------|------------------------------------|---------------------------------------------------------------------|------|------------------|---------------------|

| 1    | AA                                 | Printed Circuit Board                                               | Y    | ТІ               | 551600772-001 REV A |

| 2    | CIN, COUT                          | CAP, CERM, 10µF, 6.3V, +/-<br>20%, X5R, 0603                        | Y    | MuRata           | GRM188R60J106ME47D  |

| 3    | D1                                 | White LED                                                           | Y    | Philips Lumileds | LXCL-EYW4           |

| 4    | J1, J5, J10, J14,<br>J16, J17, J18 | Header, TH, 100mil, 2x1,<br>Gold plated, 230 mil above<br>nsulator  |      | Samtec, Inc.     | TSW-102-07-G-S      |

| 5    | J2, J4                             | Header, TH, 100mil, 4x1,<br>Gold plated, 230 mil above<br>insulator | Y    | Samtec, Inc.     | TSW-104-07-G-S      |

| 6    | J3, J6, J7, J8, J9                 | Header, TH, 100mil, 3x1,<br>Gold plated, 230 mil above<br>insulator | Y    | Samtec, Inc.     | TSW-103-07-G-S      |

| 7    | J11                                | Conn Jack Banana Insulated Nylon Black                              | Y    | Emerson Johnson  | 108-0903-001        |

| 8    | J12                                | Conn Jack Banana Insulated Nylon Red                                | Y    | Emerson Johnson  | 108-0902-001        |

| 9    | L1                                 | TOKO Inductor                                                       | Y    | ТОКО             | FDSD3012-1R0        |

| 10   | REN, RSCL, RSDA                    | RES, 1.00kΩ, 1%, 0.1W,<br>0603                                      | Y    | Vishay-Dale      | CRCW06031K00FKEA    |

| 11   | SW1                                | Four Terminal SPST Push<br>Button                                   | Y    | Panasonic        | EVQ-PD05M           |

AN-2259 LM3556 1.5A Synchronous Boost LED Flash Driver w/ High-Side Current Source Evaluation Board

| ltem | Designator | Description                                                         | RoHS | Manufacturer      | Part Number     |  |  |  |  |  |  |  |

|------|------------|---------------------------------------------------------------------|------|-------------------|-----------------|--|--|--|--|--|--|--|

| 12   | TH1        | Thermistor NTC, 100k $\Omega$ , 5%, 0402                            | Y    | MuRata            | NCP15WL104J03RC |  |  |  |  |  |  |  |

| 13   | U1         | 1.5A Flash LED Driver                                               | Y    | Texas Instruments | LM3556TME       |  |  |  |  |  |  |  |

| 14   | USBTOANY   | Header, TH, 100mil, 5x2,<br>Gold plated, 230 mil above<br>insulator | Y    | Samtec, Inc.      | TSW-105-07-G-D  |  |  |  |  |  |  |  |

#### Table 1. Bill of Materials (continued)

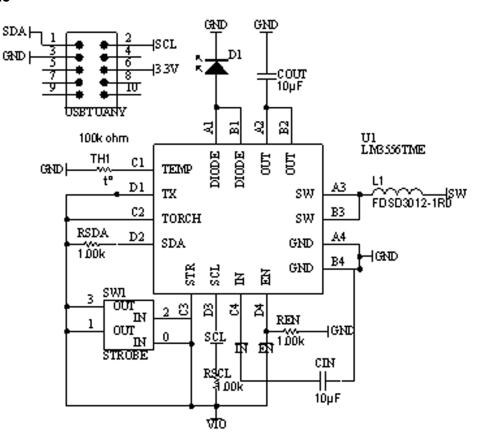

#### 2 **Schematic**

#### 3 LM3556 Evaluation Board Layout

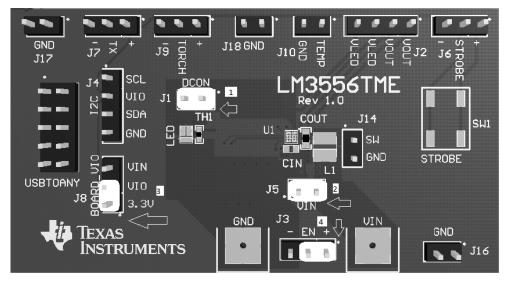

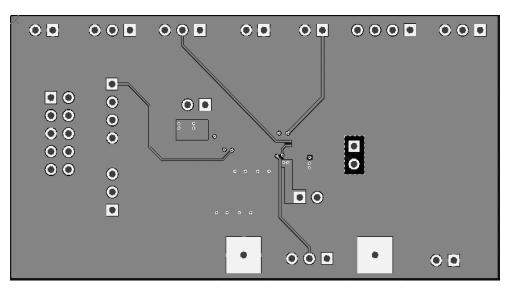

Figure 1. LM3556 Evaluation Board

To operate the LM3556 1.5A Single Flash LED Driver System with I2C Compatible Interface, the following jumpers will have to be connected.

Jumper 1: This in shown in Figure 1 as 1. This connects the LED to the part. If this jumper is not present, the part will run into an OVP fault.

Jumper 2: This is shown in Figure 1 as 2. This connects the inductor to the supply voltage to make sure the part is able to switch during the boost phase. This also hooks in the bypass capacitor at the input to the supply voltage. The part should never be allowed to turn on without this jumper.

Jumper 3: This is shown in Figure 1 as 3. This pulls up the SDA and SCL voltages to either be 3.3V or the supply voltage (Vin).

Jumper 4: This is shown in Figure 1 as 4. This pulls the Enable pin in the part to the supply voltage.

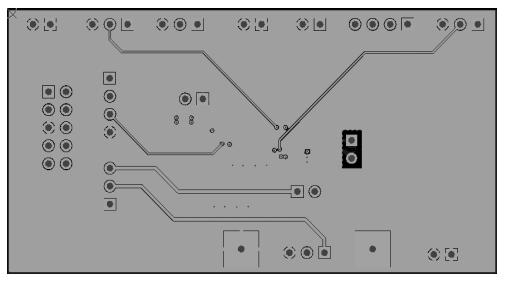

Figure 2. Top Layer

Figure 3. Mid-Layer 1

Figure 4. Mid-Layer 2

Figure 5. Bottom Layer (unmirrored)

# 4 Board Operation

#### 4.1 GUI

Following is a screenshot image of the GUI that could be used to operate the LM3556 IC. The register description follows the GUI.

| LM3556                                                                                 |                                                                                                  |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Enable Register (0x0A)<br>NTC TX Ext Strobe Torch Pin PreCharge                        | Write Enable Register TX                                                                         |

| Configuration Register (0x07)<br>Edg/LVL Strobe Pol Torch Pol Tx Polarity TX L         | evel IVFM En NTC Ind UVL0                                                                        |

| Californ Bey and Filter Time Iuxuul                                                    | Control Register (0x09)<br>ch Current Flash Current TSD                                          |

| 1 v 50mV v 2.9V v 00=Repo                                                              | Adjust Mode<br>tt Mode<br>TM Register                                                            |

| NTC Level NTC Trip Thr NTC Bias Curr                                                   | ator Ramp Time Register (0x03)<br>nd Ramp Up Ind Ramp Down<br>ims I 16ms V<br>Write Ind Register |

| Torch Ramp Current (0x06)<br>Ramp Up Ramp Down<br>16ms 16ms 31A<br>Write Ramp Register | es Register (0x08)<br>T Flash Ramp Time FTO<br>1024us V 300ms V<br>Write FLash Feat Register     |

Figure 6. GUI Startup

# 5 Register Descriptions

| Register Name                             | Internal Hex Address | Power On/RESET Value <sup>(1)</sup> |  |

|-------------------------------------------|----------------------|-------------------------------------|--|

| Silicon Revision and Filter Time Register | 0x00                 | 0x04                                |  |

| IVFM Mode Register                        | 0x01                 | 0x80                                |  |

| NTC Settings Register                     | 0x02                 | 0x12                                |  |

| Indicator Ramp Time Register              | 0x03                 | 0x00                                |  |

| Indicator Blinking Register               | 0x04                 | 0x00                                |  |

| Indicator Period Count Register           | 0x05                 | 0x00                                |  |

| Torch Ramp Time Register                  | 0x06                 | 0x00                                |  |

| Configuration Register                    | 0x07                 | 0x78                                |  |

| Flash Features Register                   | 0x08                 | 0xD2                                |  |

| Current Control Register                  | 0x09                 | 0x0F                                |  |

| Enable Register                           | 0x0A                 | 0x00                                |  |

| Flags Register                            | 0x0B                 | 0x00                                |  |

<sup>(1)</sup> All unused bits are internally pulled HIGH.

6 AN-2259 LM3556 1.5A Synchronous Boost LED Flash Driver w/ High-Side Current Source Evaluation Board

# 5.1 Silicon Revision and Filter Time Register (0x00)

| Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3                                                                                              | Bit 2 | Bit 1                                  | Bit 0 |

|-------|-------|-------|--------------|----------------------------------------------------------------------------------------------------|-------|----------------------------------------|-------|

| RFU   | RFU   | RFU   | '00' = 1/2 o | <b>M Filter Times</b><br>f the Current Step Time<br>'01' = 256 μs<br>'10' =512 μs<br>11' = 1024 μs |       | ilable for Silicon<br>urrent Value = ' |       |

# 5.2 Input Voltage Flash Monitor (IVFM) Mode Register (0x01)

| Bit 7                    | Bit 6                         | Bit 5                                                              | Bit 4 | Bit 3                                                                                                                                     | Bit 2 | Bit 1                                     | Bit 0 |

|--------------------------|-------------------------------|--------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------|-------|

| 1 = UVLO EN<br>(default) | 00 = 50 m<br>01 = 1<br>10 = 1 | <b>sis Level</b><br>V (default)<br>00 mV<br>50 mV<br>esis Disabled |       | -D (Down) Thresh<br>000 = 2.9V (default<br>001 = 3.0V<br>010 = 3.1V<br>011 = 3.2V<br>100 = 3.3V<br>101 = 3.4V<br>110 = 3.5V<br>111 = 3.6V |       | 00 = Report M<br>01 = Stop an<br>10 = Dov |       |

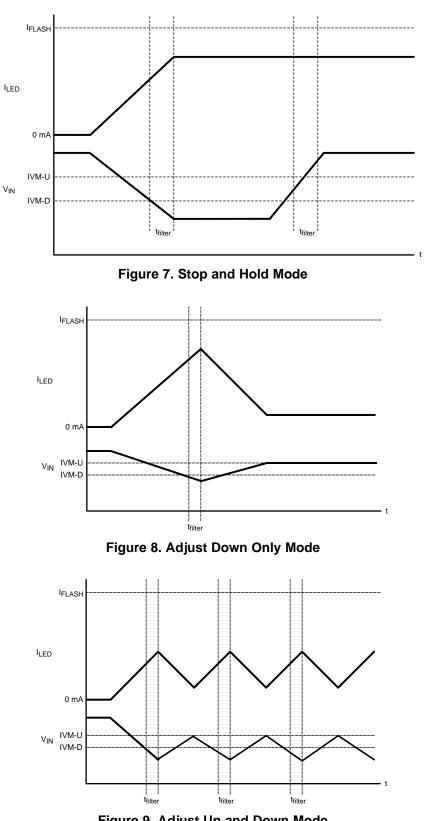

- **00 = Report Mode**—Sets IVFM Flag in Flags Register upon crossing IVM-D Line Only. Does not adjust current.

- 01 = Stop and Hold Mode— Stops Current Ramp and Holds the level for the remaining flash if V<sub>IN</sub> crosses IVM-D Line. Sets IVFM Flag in Flags Register upon crossing IVM-D Line.

- 10 = Down Mode—Adjusts current down if V<sub>IN</sub> crosses IVM-D Line and will stop decreasing once V<sub>IN</sub> rises above the IVM-D line + the IVFM hysteresis setting. The LM3556 will decrease the current throughout the flash pulse anytime the input voltage falls below the IVM-D line, and not just once. The flash current will not increase again until the next flash. Sets IVFM Flag in Flags Register upon crossing IVM-D Line.

- **11 = Up and Down Mode**—Adjusts current down if  $V_{IN}$  crosses IVM-D Line and adjusts current up if  $V_{IN}$  rises above the IVM-D line + the IVFM hysteresis setting. In this mode, the current will continually adjust with the rising and falling of the input voltage throughout the entire flash pulse. Sets IVFM Flag in Flags Register upon crossing IVM-D Line.

- UVLO EN— If enabled and VIN drops below 2.8V, the LM3556 will enter standby and set the UVLO flag in the Flags Register. Enabled = '1', Disabled = '0' IVM-U = IVM-D + IVFM Hysteresis

Figure 9. Adjust Up and Down Mode

# 5.3 NTC Settings Register (0x02)

| Bit 7 | Bit 6 | Bit 5                                                                                            | Bit 4 | Bit 3                                                                                                                                                    | Bit 2 | Bit 1                                                 | Bit 0                         |

|-------|-------|--------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------|-------------------------------|

| RFU   | RFU   | NTC Event<br>Level<br>0 = Go to<br>Standby<br>(default)<br>1 = Reduce<br>to Min Torch<br>Current |       | TC Trip Thresholds<br>000 = 200 mV<br>001 = 300 mV<br>010 = 400 mV<br>011 = 50 mV<br>0 = 600 mV (default<br>101 = 700 mV<br>110 = 800 mV<br>111 = 900 mV |       | NTC Bias C<br>00 = 2<br>01 = 3<br>10 = 75 μ<br>11 = 1 | 25 μΑ<br>50 μΑ<br>A (default) |

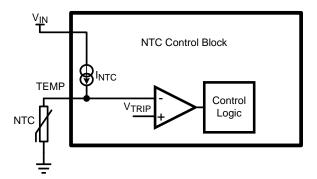

# Figure 10. NTC Control Block

The TEMP node is connected to an NTC resistor as shown in above. A constant current source from the input is connected to this node. Any change in the voltage because of a change in the resistance of the NTC resistor is compared to a set  $V_{TRIP}$ . The trip thresholds are selected by Bits[4:2] of the NTC Register. The output of the Control Logic upon an NTC trip is selected through Bit[5].

# 5.4 Indicator Ramp Time Register (0x03)

| Bit 7 | Bit 6 | Bit 5 | Bit 4                                                                                                                                             | Bit 3 | Bit 2 | Bit 1                                                                                                                                             | Bit 0 |

|-------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| RFU   | RFU   |       | ator Ramp-Up T<br>000 = 16 ms (defa<br>001 = 32 ms<br>010 = 64 ms<br>011 = 128 ms<br>100 = 256 ms<br>101 = 512 ms<br>110 = 1.024s<br>111 = 2.048s |       |       | tor Ramp-Down<br>100 = 16 ms (defar<br>001 = 32 ms<br>010 = 64 ms<br>011 = 128 ms<br>100 = 256 ms<br>101 = 512 ms<br>110 = 1.024s<br>111 = 2.048s | ( ) / |

# 5.5 Indicator Blinking Register (0x04)

| Bit 7 | Bit 6          | Bit 5       | Bit 4 | Bit 3                            | Bit 2    | Bit 1     | Bit 0 |  |  |

|-------|----------------|-------------|-------|----------------------------------|----------|-----------|-------|--|--|

|       | N <sub>B</sub> | BLANK       |       | Pulse Time (t <sub>PULSE</sub> ) |          |           |       |  |  |

|       | 0000 = 0       | 0 (default) |       |                                  | 0000 = 0 | (default) |       |  |  |

|       | 000            | 1 = 1       |       |                                  | 0001 =   | 32 ms     |       |  |  |

|       | 001            | 0 = 2       |       |                                  | 0010 =   | 64 ms     |       |  |  |

|       | 001            | 1 = 3       |       |                                  | 0011 =   | 92 ms     |       |  |  |

|       | 010            | 0 = 4       |       |                                  | 0100 =   | 128 ms    |       |  |  |

|       | 010            | 1 = 5       |       | 0101 = 160  ms                   |          |           |       |  |  |

|       | 011            | 0 = 6       |       | 0110 = 196 ms                    |          |           |       |  |  |

|       | 011            | 1 = 7       |       | 0111 = 224 ms                    |          |           |       |  |  |

|       | 100            | 0 = 8       |       | 1000 = 256 ms                    |          |           |       |  |  |

|       | 100            | 1 = 9       |       | 1001 = 288 ms                    |          |           |       |  |  |

|       | 1010           | 0 = 10      |       | 1010 = 320 ms                    |          |           |       |  |  |

|       | 1011           | 1 = 11      |       | 1011 = 352 ms                    |          |           |       |  |  |

|       | 1100           | 0 = 12      |       | 1100 = 384 ms                    |          |           |       |  |  |

|       | 110            | 1 = 13      |       | 1101 = 416 ms                    |          |           |       |  |  |

|       | 111(           | 0 = 14      |       | 1110 = 448 ms                    |          |           |       |  |  |

|       | 1111           | 1 = 15      |       | 1111 = 480 ms                    |          |           |       |  |  |

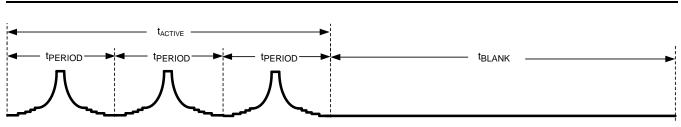

# 5.6 Indicator Period Count Register (0x05)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RFU   | RFU   | RFU   | RFU   | RFU   |       |       |       |

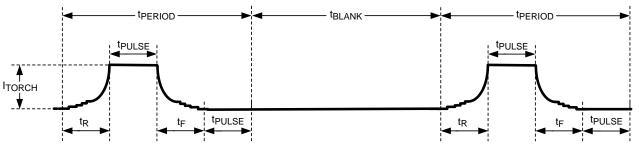

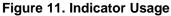

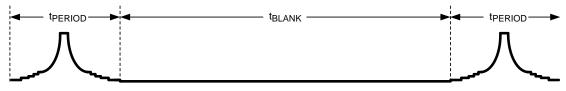

- 1. Number of periods ( $t_{PERIOD} = t_R + t_F + t_{PULSE} \times 2$ )

- 2. Active Time ( $t_{ACTIVE} = t_{PERIOD} \times N_{PERIOD}$ )

- 3. Blank Time ( $t_{\text{BLANK}} = t_{\text{ACTIVE}} \times N_{\text{BLANK}}$ )

#### Figure 12. Single Pulse with Dead Time

Figure 13. Multiple Pulse with Dead Time

# 5.7 Torch Ramp Time Register (0x06)

| Bit 7 | Bit 6 | Bit 5 | Bit 4                                                                                                                                               | Bit 3 | Bit 2 | Bit 1                                                                                                                                               | Bit 0 |

|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| RFU   | RFU   |       | orch Ramp-Up Ti<br>000 = 16 ms (defau<br>001 = 32 ms<br>010 = 64 ms<br>011 = 128 ms<br>100 = 256 ms<br>101 = 512 ms<br>110 = 1.024s<br>111 = 2.048s |       |       | rch Ramp-Down T<br>000 = 16 ms (defau<br>001 = 32 ms<br>010 = 64 ms<br>011 = 128 ms<br>100 = 256 ms<br>101 = 512 ms<br>110 = 1.024s<br>111 = 2.048s |       |

# 5.8 Configuration Register (0x07)

| Bit 7                                                 | Bit 6                                                                       | Bit 5                                                                      | Bit 4                                                                   | Bit 3                                                              | Bit 2                                                   | Bit 1                                              | Bit 0                                                          |

|-------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|

| Strobe<br>Usage<br>0 = Edge<br>(default)<br>1 = Level | Strobe Pin<br>Polarity<br>0 = Active<br>Low<br>1 = Active<br>High (default) | Torch Pin<br>Polarity<br>0 = Active<br>Low<br>1 = Active<br>High (default) | TX Pin<br>Polarity<br>0 = Active<br>Low<br>1 = Active<br>High (default) | <b>TX Event Level</b><br>0 = Off<br>1 = Torch<br>Current (default) | IVFM Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | NTC Mode<br>0 = Normal<br>(default)<br>1 = Monitor | Indicator<br>Mode<br>0 = Internal<br>(default)<br>1 = External |

Strobe Usage—Level or Edge. Flash will follow Strobe timing if Level and internal timing if Edge.

Strobe Polarity—Active High or Active Low Select.

Torch Polarity—Active High or Active Low Select.

TX Polarity—Active High or Active Low Select.

- **TX Event Level**—Transition to Torch Current Level or Off if TX event occurs.

- **NOTE:** The TX Event Level "Off" setting is designed to only force a shutdown during a flash event. When Torch or Indicator Mode is enabled, and a TX event occurs with the TX Event Level set to "Off", the LM3556 does not shut down. The TX flag bit (bit7 in the Section 5.12) will be set, and the mode bits (bit0 and bit1 in Section 5.11) get locked out until the fault register is cleared via an I<sup>2</sup>C read. Because a TX event is periodic and frequently occurring, clearing the fault register becomes more difficult. Depending on the I<sup>2</sup>C read/write speed and TX event frequency, it may be necessary to set the TX enable bit (bit6 in the Section 5.11) to a '0' before clearing the fault register to prevent future flag sets.

**IVFM Enable**—Enables Input Voltage Flash Monitoring.

NTC Mode—Monitor Mode (Report Only) or Normal Mode (Reduce Current or Shutdown).

Indicator Mode—Externally generated via TORCH Pin or internally generated PWM.

#### 5.9 Flash Features Register (0x08)

| Bit 7                  | Bit 6 | Bit 5                     | Bit 4 | Bit 3        | Bit 2                  | Bit 1 | Bit 0 |

|------------------------|-------|---------------------------|-------|--------------|------------------------|-------|-------|

|                        |       | Flash Ramp Time           |       |              | Flash Time-Out Time    |       |       |

| 000 = 256 µs           |       |                           |       | 000 = 100 ms |                        |       |       |

| Inductor Current Limit |       | 001 = 512 µs              |       |              | 001 = 200 ms           |       |       |

| 00 =1.7A               |       | 010 = 1.024  ms (default) |       |              | 010 = 300 ms (default) |       |       |

| 01 = 1.9A              |       | 011 = 2.048 ms            |       |              | 011 = 400  ms          |       |       |

| 10 = 2.5A              |       | 100 = 4.096 ms            |       |              | 100 = 500 ms           |       |       |

| 11 = 3.1A (default)    |       | 101 = 8.192 ms            |       |              | 101 = 600 ms           |       |       |

|                        |       | 110 = 16.384 ms           |       |              | 110 = 700 ms           |       |       |

|                        |       | 111 = 32.768 ms           |       |              | 111 = 800 ms           |       |       |

# 5.10 Current Control Register (0x09)

| Bit 7 | Bit 6                                     | Bit 5                                                                                                                                             | Bit 4 | Bit 3 | Bit 2                                                                                                                                                                                 | Bit 1                                                                                                                                                                                                  | Bit 0 |

|-------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| RFU   | 000 =<br>00<br>01<br>07<br>10<br>10<br>10 | orch Current<br>46.88 mA (defaul<br>01 =93.75 mA<br>0 =140.63 mA<br>11 = 187.5 mA<br>0 =234.38 mA<br>1 = 281.25 mA<br>0 = 328.13 mA<br>11 =375 mA | t)    |       | $\begin{array}{r} 0000 = \\ 0001 = \\ 0010 = \\ 0011 = \\ 0100 = \\ 0101 = \\ 0110 = \\ 0110 = \\ 1000 = \\ 1000 = \\ 1010 = 1\\ 1011 = \\ 1100 = 1\\ 1101 = \\ 1110 = 1 \end{array}$ | Current<br>93.75 mA<br>187.5 mA<br>281.25 mA<br>= 375 mA<br>468.75 mA<br>562.5mA<br>656.25 mA<br>= 750 mA<br>843.75 mA<br>937.5 mA<br>031.25 mA<br>1125 mA<br>218.75 mA<br>406.25 mA<br>0 mA (default) |       |

# 5.11 Enable Register (0x0A)

| Bit 7                                                  | Bit 6                                                        | Bit 5                                                            | Bit 4                                                           | Bit 3                                                                | Bit 2                                                                | Bit 1                         | Bit 0                                                   |

|--------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------|---------------------------------------------------------|

| NTC Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | TX Pin<br>Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | STROBE Pin<br>Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | TORCH Pin<br>Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | PreCharge<br>Mode Enable<br>0 = Normal<br>(default)<br>1 = PreCharge | Pass-Mode<br>Only Enable<br>0 = Normal<br>(default)<br>1 = Pass Only | 00 = Stand<br>01 = In<br>10 = | s: M1, M0<br>by (default)<br>idicator<br>Torch<br>Flash |

#### 5.11.1 Enable Register (8 Bits)

NTC EN—Enables NTC Block.

**TX EN**—Allows TX events to change the current.

Strobe EN—Enables Strobe Pin to start a Flash Event.

**Torch EN**—Enables Torch Pin to start a Torch Event.

PreCharge Mode EN—Enables Pass Mode to pre-charge the output cap.

Pass-Only Mode EN—Only allows Pass Mode and disallows Boost Mode.

**NOTE:** If Pass-Only Mode is enabled during any LED mode (Indicator, Torch or Flash), it will remain enabled until the LM3556 enters the standby state regardless of whether the Pass-Only Mode bit is reset or not during the following command.

#### 5.11.2 Two-Mode Bits

#### 00-Standby- Off

01-Indicator— Sets Indicator Mode. Default Indicator Mode uses external pattern on TORCH Pin.

- **10–Torch** Sets Torch Mode with ramping. If Torch EN = 0, Torch will start after I<sup>2</sup>C-compatible command.

- **11–Flash** Sets Flash Mode with ramping. If Strobe EN = 0, Flash will start after I<sup>2</sup>C-compatible command.

# 5.12 Flags Register (0x0B)

| Bit 7                          | Bit 6                          | Bit 5               | Bit 4                      | Bit 3                     | Bit 2                                        | Bit 1                                            | Bit 0                             |

|--------------------------------|--------------------------------|---------------------|----------------------------|---------------------------|----------------------------------------------|--------------------------------------------------|-----------------------------------|

| <b>TX Event</b><br>0 = Default | <b>NTC Trip</b><br>0 = Default | IVFM<br>0 = Default | <b>UVLO</b><br>0 = Default | <b>OVP</b><br>0 = Default | LED or<br>VOUT Short<br>Fault<br>0 = Default | <b>Thermal</b><br><b>Shutdown</b><br>0 = Default | Flash Time-<br>out<br>0 = Default |

**TX Event Flag**—TX Event occurred.

NTC Trip Flag—NTC Threshold crossed.

**IVFM Flag**—IVFM block reported and/or adjusted LED current.

**UVLO Fault**—UVLO Threshold crossed.

**OVP Flag**—Over-voltage Protection tripped. Open Output cap or open LED.

**LED Short Fault**—LED Short detected.

Thermal Shutdown Fault—The LM3556 die temperature reached thermal shutdown value.

Time-Out Flag—Flash Timer tripped

**NOTE:** Faults require a read-back of the "Flags Register" to resume operation. Flags report an event occurred, but do not inhibit future functionality. A read-back of the Flags Register will only be updated again if the fault or flags is still present upon a restart.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated