# Quick-Start Methods in Simulating the DAC38RF8x Input/Output Buffer Information Specification (IBIS) Model

Abdallah Obidat

## 1 Introduction

Input/output Buffer Information Specification (IBIS) models are used to simulate digital electrical interfaces. These models can be categorized into two main categories: traditional and algorithmic modeling interface (AMI). AMI is typically used for SerDes channel simulation, and is different from the traditional IBIS model, which is the focus of this document. These models are simple ASCII text files that contain buffer voltage-current (V-I) characteristics and output voltage over-time (V-T) characteristics. In the model file, the individual digital pins and their respective signal type, model name, and parasitic RLC values are all listed. Notes and other information may be included as well.

Typical models include single-ended or differential input, output, I/O, and tristate among others. One advantage of IBIS models over simulation programs with integrated circuit emphasis (SPICE) models is that IBIS models do not model the actual silicon or transistor-level circuitry of the integrated circuit (IC), so proprietary information regarding the IC is not revealed. Simulation time is greatly reduced compared to SPICE simulation for this same reason.

IBIS models are used in Signal Integrity (SI) simulation. Single-ended input and output models are used to simulate one pin at a time, while differential models simulate a pair of complementary pins. Simulating circuits that employ IBIS models can be achieved using a number of programs, however Advanced System Design (ADS) and HyperLynx are used to explore a simplified example of an SI simulation.

# 2 Simulation Overview

# 2.1 Example Circuit

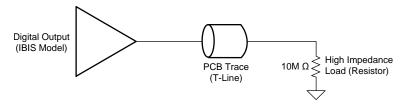

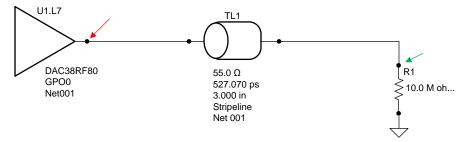

Figure 1 shows a circuit simulated in ADS and HyperLynx.

Figure 1. ADS and HyperLynk Simulated Circuit

In this example, the GPO0 pin of the DAC38RF80 device drives a high-impedance node. The length of the PCB trace between the pin and load is set to 3 inches. This trace is a stripline that is fully embedded in dielectric material. Also, the characteristic impedance of the trace is approximately 50  $\Omega$ . In a practical simulation, additional parasitic factors may also be modeled and the pin may drive a digital receiver, rather than a purely-resistive high-impedance load.

All trademarks are the property of their respective owners.

### 3 Simulation Description

#### 3.1 ADS Simulation

ADS offers a wide range of simulation tools, including the ability to simulate IBIS models. The following steps describe the process to simulate the previous example.

- 1. After creating a new workspace and a new schematic, select Signal Integrity IBIS from the palette drop-down menu and place an IBIS\_O model on the schematic.

- 2. Connect the PC and PU nodes to each other with a wire.

- 3. Connect the GC and PD nodes to each other with a wire, and then to ground.

- 4. Select Sources-Time Domain from the palette drop-down menu.

- 5. Place a V\_DC model on the schematic.

- 6. Place a Pulse model on the schematic and configure according to Figure 2.

| Edit Instance Parameters                                                                    | X                              |

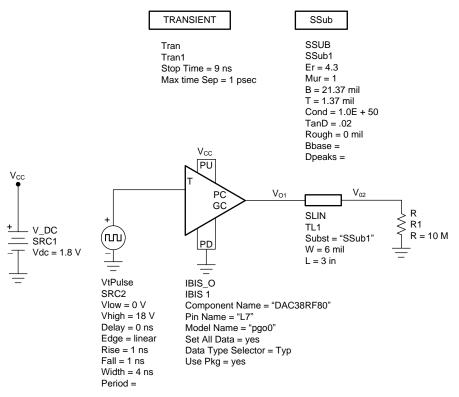

|---------------------------------------------------------------------------------------------|--------------------------------|

| Library name: ads_sources<br>Cell name: VtPulse<br>View name: symbol<br>Instance name: SRC2 |                                |

| Select Parameter                                                                            | Parameter Entry Mode           |

| Vlow=0 V                                                                                    | Standard                       |

| Vhigh=1.8 V                                                                                 |                                |

| Delay=0 nsec                                                                                | Vlow                           |

| Edge=linear                                                                                 | 0 V                            |

| Rise=1 nsec                                                                                 | Equation Editor                |

| Fall=1 nsec                                                                                 |                                |

| Width=4 nsec                                                                                | Tune/Opt/Stat/DOE Setup        |

| Period=                                                                                     |                                |

| SaveCurrent=yes -                                                                           | Display parameter on schematic |

| Add Cut Paste                                                                               | Component Options Reset        |

| Vlow:Initial voltage                                                                        |                                |

|                                                                                             |                                |

| OK Apply                                                                                    | Cancel Help                    |

#### Figure 2. Pulse Source Configuration

- 7. Connect the positive node of the DC voltage source to the PU and PC nodes, and connect the negative node to ground.

- 8. Connect the positive node of the pulse source to the T node of the IBIS\_O model, and connect the negative node to ground.

- 9. Select Lumped-Components and place a resistor on the schematic.

- 10. Set the resistor value to  $10 \text{ M}\Omega$ .

2

11. Select TLines-Stripline from the palette drop-down menu.

- 12. Place a SSUB and SLIN model onto the schematic.

- 13. Set the width of the transmission line to 6 mil and its length to 3 in.

- 14. Connect the output of the IBIS\_O model to one end of the transmission line and connect the other end to the 10  $M\Omega$  resistor.

- 15. Ground the other end of the resistor.

- 16. Configure the transmission line substrate according to Figure 3.

| ibrary name: ads_tines<br>iell name: SSUB<br>fiew name: symbol                                                                                                  |     |                                  |        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|--------|--|

| nstance name: SSub1                                                                                                                                             |     |                                  |        |  |

| Select Parameter                                                                                                                                                |     | Parameter Entry Mode             |        |  |

| Er=4.3                                                                                                                                                          |     | Standard                         | •      |  |

| Mur=1<br>B=21.37 mil                                                                                                                                            |     | Er                               |        |  |

| T=1.37 mil                                                                                                                                                      |     | 4.3                              | None • |  |

| Cond=1.0E+50<br>TanD=.02                                                                                                                                        | 111 | Equation Editor                  |        |  |

| Cond1="cond:drawing"                                                                                                                                            |     | Tune/Opt/Stat/DOE Setup          |        |  |

| Cond2="cond2:drawing"<br>DielectricLossModel=Svensson/Djordjevic<br>FreqForEpsrTanD=1.0 GHz<br>LowFreqForTanD=1.0 KHz<br>HighFreqForTanD=1.0 THz<br>Rough=0 mil |     | ✓ Display parameter on schematic |        |  |

| Add Cut Paste<br>Er:Relative dielectric constant                                                                                                                |     | Component Options                | Reset  |  |

| OK Apply                                                                                                                                                        | _   | Cancel                           | Help   |  |

Figure 3. Stripline Substrate Configuration

- 17. Double-click on the IBIS model.

- 18. Click on the Select IBIS File button and then browse to the location on the PC containing the DAC38RF80 IBIS file. Select the file and click OK.

- 19. Navigate to the Pin tab, verify that GPO0 is highlighted, then click OK.

20. Select Simulation-Transient from the palette drop-down menu and configure it as shown in Figure 4.

| Time Setup | Integration                                                               | Conv          | olution                      | Convergen 4 |

|------------|---------------------------------------------------------------------------|---------------|------------------------------|-------------|

|            | Output Times<br>Start time<br>Stop time<br>Max time step<br>Min time step | 0.0<br>9<br>1 | nsec<br>nsec<br>psec<br>None | •           |

|            | Limit timeste                                                             | p for Trans   | mission Line                 |             |

Figure 4. Transient Simulation Parameters

21. Name the net just before the transmission line, and name the net just after it as well.

22. Click on the Simulation icon. Figure 5 shows the complete circuit.

#### Figure 5. Signal Integrity Simulation Circuit – ADS

## 3.1.1 ADS Simulation – Results

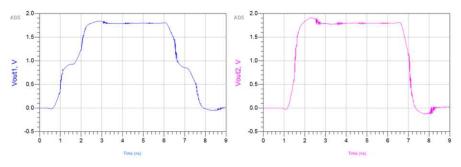

Figure 6 and Figure 7 show the results of ADS simulation.

Figure 6. Signal at Driver Pin (Left) and Load (Right) – ADS

Simulation Description

Figure 7. Overlay of Signal at Driver Pin (Blue) and Load (Magenta) – ADS

# 3.2 HyperLynx Simulation

6

HyperLynx is another tool used to simulate IBIS models. The following steps describe the process to simulate the previous example.

- 1. From the menu bar, select File  $\rightarrow$  New Free Form Schematic  $\rightarrow$  SI (or SI/PI).

- 2. Using the menu bar, navigate to Setup  $\rightarrow$  Options  $\rightarrow$  Directories.

- 3. In the Set Directories window that appears, click on the Edit button near the model-library file path section.

- 4. Browse to the directory in which the IBIS file is stored and then click on the Add button.

- 5. From the palette containing the schematic models, select the single-ended IC and place it on the schematic.

- 6. Place a single, horizontal, transmission line on the schematic.

- 7. Place a resistor on the schematic.

- 8. Connect the output of the IC to one end of the transmission line.

- 9. Connect the other end of the transmission line to the resistor.

- 10. Connect the other end of the resistor to ground.

- 11. Set the value of the resistor to  $10 \text{ M}\Omega$ .

- 12. Double-click on the transmission line and in the Transmission Line Type section, and then select Stripline.

- 13. Navigate to the Values tab and configure the transmission line as shown in Figure 8, then click OK.

| ransmission-Line Type Values Los | 55     |                                                                                             |

|----------------------------------|--------|---------------------------------------------------------------------------------------------|

|                                  |        | Electrical properties                                                                       |

| Beference Play                   | ne     | Z0 = 55.0 ohms                                                                              |

| T                                | ie .   | Delay = 527.1 ps                                                                            |

| 'HL'                             |        | L = 29.0 nH                                                                                 |

| TRACE                            | r-     | C = 9.6 pF                                                                                  |

| H2 DIELECTRIC                    |        | R = 0.251 ohms                                                                              |

|                                  | 1917   | Rs = 1.128 mOhm/m-sqrt(Hz)                                                                  |

| Reference Pla                    | ne     | Gd = 15.814 pS/m-Hz                                                                         |

|                                  |        | Hints                                                                                       |

| Length - L:                      | 3.000  | R is computed at the temperature specified in the<br>Options/Preferences dialog.            |

| Conductor thickness - T:         | 1.00   | Click Advanced to change the bulk resistance                                                |

| Width - W:                       | 6.00   | or temperature coefficient.                                                                 |

| Dielectric height - H1:          | 10.00  | If you have many traces on one PCB, the<br>"stackup" type may be better to use. See Help fr |

| Dielectric height - H2:          | 10.00  | details.                                                                                    |

| Dielectric constant - Er.        | 4.30   |                                                                                             |

| Loss tangent - Lt                | 0.0200 | Advanced                                                                                    |

|                                  |        |                                                                                             |

Figure 8. Stripline Configuration

- 14. Double-click on the IBIS model.

- 15. Click the Select button, then select the DAC38RF80 model, which should be selectable in the Libraries list.

- **NOTE:** After the DAC38RF80 model is selected, the Devices list should only show DAC38RF80.

16. Select GPO0 from the Signal list, then click OK.

- **NOTE:** If Steps 2 to 4 were not correctly completed, then the Libraries list will not show the DAC38RF80 file.

- 17. Verify that the Output option is selected in the Buffer Settings section and then click OK.

- 18. Click on the Interactive Simulation icon. Figure 9 shows the complete circuit.

# Figure 9. Signal Integrity Simulation Circuit – HyperLynx

19. In the Stimulus section, select Per Net/Pin and click on the Assign button.

Simulation Description

www.ti.com

- 20. When the Assign Stimulus window opens, click on Edit Stimulus.

- 21. Create a Pulse by configuring the stimulus, as shown in Figure 10.

| Sequence:            | Pulse               | •          |  | Initial state: | Low | • |

|----------------------|---------------------|------------|--|----------------|-----|---|

| 1 0                  |                     |            |  |                |     |   |

|                      |                     |            |  |                |     |   |

|                      |                     |            |  |                |     |   |

| imulus<br>Bit interv |                     | ns         |  |                |     |   |

| Bit interv           | val: 4<br>ote: 0.25 | ns<br>Gbps |  |                |     |   |

Figure 10. Stimulus Configuration

- 22. Before clicking OK, save the stimulus as a separate file, to a known directory, because the default stimulus cannot be edited.

- 23. Using the menu bar, navigate to Setup  $\rightarrow$  Options  $\rightarrow$  Directories.

- 24. In the Set Directories window that appears, click on the Edit button in the stimulus file path section.

- 25. Browse to the directory in which the IBIS file is stored and then click on the Add button.

- 26. After returning to the Assign Stimulus window, the newly created stimulus file may be selected from the Stimulus drop-down list.

- 27. Click OK and then click Start Simulation.

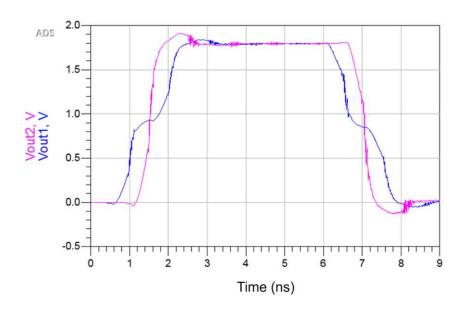

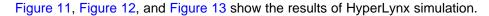

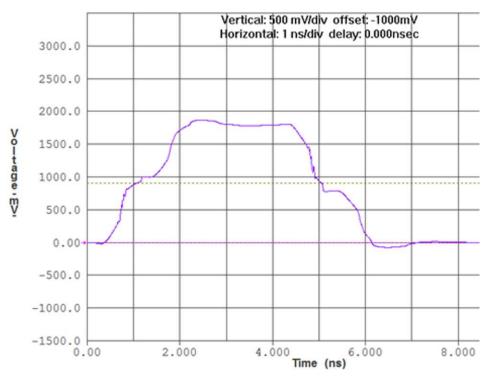

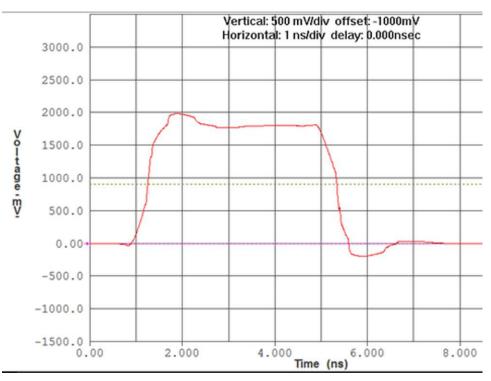

## 3.2.1 HyperLynx Simulation – Results

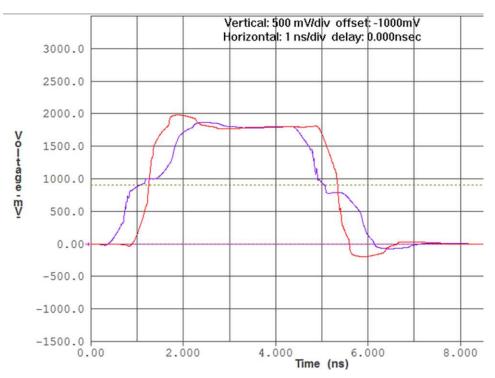

Figure 13. Overlay of Signal at Driver Pin (Purple) and Load (Red) – HyperLynx

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated