# Product Overview Separate Digital Voltage Nodes

Systems can have multiple digital voltages that are similar in value which need to be separated for optimal performance. For example, an incoming 3.3-V signal may need to communicate with an internally regulated 3.3-V device, and the two may vary separately from 3 V to 3.6 V. In this case, true isolation is not required, however separation of the voltage nodes will prevent issues from the voltage mismatch.

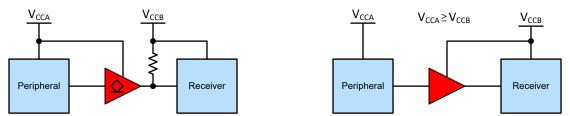

Left: block diagram for open-drain buffer. Right: block diagram for push-pull buffer.

#### Figure 1. Separate Voltage Nodes Block Diagrams

### **Design Considerations**

- Input thresholds are referenced to the buffer's supply voltage

- · Output voltage for open-drain devices can be selected by changing the pull-up resistor supply connection

- Output voltage for push-pull devices is equal to the buffer's supply voltage

- For traces longer than 12 cm (4760 mil) see Drive Transmission Lines With Logic

- [FAQ] How does a slow or floating input affect a CMOS device?

- [FAQ] Where do I find maximum power dissipation for a device?

- Ask a question on our *E2E<sup>™</sup> forum*

### **Recommended Parts**

| Part Number      | AEC-Q100 | V <sub>CC</sub> Range | Channels | Features                                                                                                    |

|------------------|----------|-----------------------|----------|-------------------------------------------------------------------------------------------------------------|

| SN74LVC1G34      |          | 1.65 V – 5.5 V        | 1        | Over-voltage tolerant inputs<br>Partial power down (loff)<br>Balanced high-drive CMOS outputs (up to 32 mA) |

| SN74LVC1G17-Q1   | ✓        | 1.65 V – 5.5 V        | 1        | Schmitt-trigger input<br>Over-voltage tolerant input<br>Partial power down (loff)                           |

| SN74LVC1G07      |          | 1.65 V – 5.5 V        | 1        | Open-drain output                                                                                           |

| SN74LVC1G07-Q1   | 1        |                       |          | Over-voltage tolerant input and output<br>Partial power down (loff)                                         |

| SN74LV244A       |          |                       |          | Over-voltage tolerant inputs                                                                                |

| SN74LV244A-Q1    | 1        | 2 V – 5.5 V           | 8        | Partial power down (loff)<br>Balanced high-drive CMOS outputs (up to 16 mA)                                 |

| SN74LVC16244A    |          |                       |          | Over-voltage tolerant inputs                                                                                |

| SN74LVC16244A-Q1 | 1        | 1.65 V – 3.6 V        | 16       | Partial power down (loff)<br>Balanced high-drive CMOS outputs (up to 24 mA)                                 |

For more devices, browse through the *online parametric tool* where you can sort by desired voltage, channel numbers, and other features.

1

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated