ZHCS401-OCTOBER 2011

#### -200mA, 超低噪音, 负电源线性稳压器 -36V,

### 特性

- 输入电压范围: -3 V 至 -36 V

- 噪音:

- 14µV<sub>RMS</sub> (20Hz 至 20kHz)

- 15.1µV<sub>RMS</sub> (10Hz 至 100kHz)

- 电源纹波抑制:

- 72dB (120Hz)

- ≥ 55dB (10Hz 至 700kHz)

- 可调输出电压: -1.18V to -35V •

- 最大输出电流: 200mA

- 压差: 216 mV (在 100 mA 电流下)

- 采用 ≥ 2.2 µF 陶瓷电容器时可保持稳定

- CMOS 逻辑电平兼容型使能引脚

- 内置、固定、电流限制及热关断保护功能

- 采用具有高散热性能的 MSOP-8 PowerPAD™ 封 装

应用范围

- 用于运算放大器、DAC、ADC 和其它高精度模拟 电路的供电轨

- 音频

- 后置 DC/DC 转换器稳压及纹波滤除

- 测试和测量 •

- **RX, TX,** 和 **PA** 电路 •

- 工业仪器仪表 ٠

- 基站和电信基础设施 •

- -12V 和 -24V 工业总线

支持国防、航天和医疗应用

- 受控基线

- 一个组装/测试场所 ٠

- 一个制造场所

- 在军用温度范围内 (-55°C/125°C)工作 ٠

- 产品生命周期有所延长 •

- 拓展的产品变更通知

- 产品可追溯性

#### 说明

TPS7A3001 是一款负高电压 (-36 V)、超低噪声(15.1µV<sub>RMS</sub>, 72dB PSRR) 线性稳压器,此稳压器能提供 200 mA 的最大负载电流。

这些线性稳压器包括 CMOS 逻辑电平兼容使能引脚和可编程电容器软启动功能,此功能可实现定制的电源管理方 案。 其它特点包括内置的限流及热关断保护功能,此功能用于在故障情况下对器件及系统的保护。

TPS7A3001 采用双极型技术设计而成,并且非常适合于高准确度、高精度的仪器仪表应用。在此类应用中,规整 的电源电压对于系统性能的最大化至关重要)。这种设计使其成为功率运算放大器、模数转换器 (ADC)、数模转换 器 (DAC) 及其它高性能模拟电路的最佳选择。

此外,TPS7A3001 线性稳压器也适合于后置 DC/DC 转换器的稳压操作。 通过滤除 DC/DC 开关转换所固有的输 出电压纹波,可在灵敏仪器仪表、测试和测量、音频和射频的应用中将系统性能最大化。

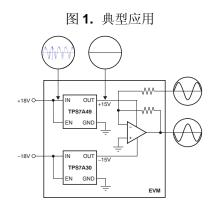

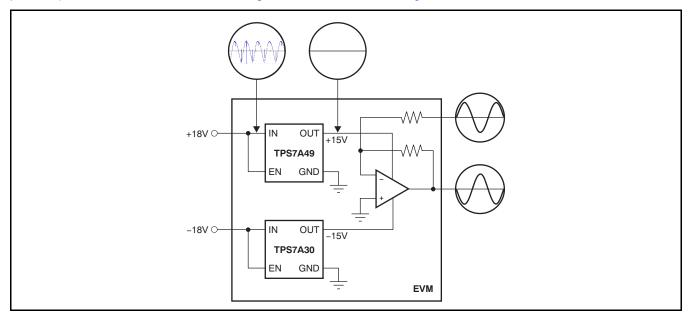

对于需要正向和负向高性能轨的应用,请考虑TI的正向高电压、超低噪音线性稳压器 TPS7A49xx 系列产品。

**A**A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

ZHCS401-OCTOBER 2011

用于高性能模拟电路的后置 DC/DC 转换器调节

## **TPS7A3001-EP**

#### www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| ORDERING INFORMATION <sup>(1)</sup> |         |                          |                     |                |  |  |  |  |  |

|-------------------------------------|---------|--------------------------|---------------------|----------------|--|--|--|--|--|

| Tj                                  | PACKAGE | ORDERABLE PART<br>NUMBER | TOP-SIDE<br>MARKING | VID NUMBER     |  |  |  |  |  |

| –55°C to 125°C                      | DGN     | TPS7A3001MDGNTEP         | PXCM                | V62/11619-01XE |  |  |  |  |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

Over operating free-air temperature range (unless otherwise noted).

|                                |                                            | VALUE   | VALUE              |      |  |

|--------------------------------|--------------------------------------------|---------|--------------------|------|--|

|                                |                                            | MIN     | MAX                | UNIT |  |

|                                | IN pin to GND pin                          | -36     | +0.3               | V    |  |

|                                | OUT pin to GND pin                         | -33     | +0.3               | V    |  |

|                                | OUT pin to IN pin                          | -0.3    | +36                | V    |  |

|                                | FB pin to GND pin                          | -2      | +0.3               | V    |  |

| Voltage                        | FB pin to IN pin                           | -0.3    | +36                | V    |  |

|                                | EN pin to IN pin                           | -0.3    | +36                | V    |  |

|                                | EN pin to GND pin                          | -36     | +36                | V    |  |

|                                | NR/SS pin to IN pin                        | -0.3    | +36                | V    |  |

|                                | NR/SS pin to GND pin                       | -2      | +0.3               | V    |  |

| Current                        | Peak output                                | Interna | Internally limited |      |  |

| T                              | Operating virtual junction, T <sub>J</sub> | -55     | +135               | °C   |  |

| Temperature                    | Storage, T <sub>stg</sub>                  | -65     | +150               | °C   |  |

|                                | Human body model (HBM)                     |         | 1500               | V    |  |

| Electrostatic discharge rating | Charged device model (CDM)                 |         | 500                | V    |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum rated conditions for extended periods may affect device reliability.

### THERMAL INFORMATION

|                       |                                              | TPS7A3001 |        |  |

|-----------------------|----------------------------------------------|-----------|--------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGN       | UNITS  |  |

|                       |                                              | 8 PINS    |        |  |

| $\theta_{JA}$         | Junction-to-ambient thermal resistance       | 69.3      |        |  |

| $\theta_{JC(top)}$    | Junction-to-case(top) thermal resistance     | 40.3      |        |  |

| $\theta_{JB}$         | Junction-to-board thermal resistance         | 39.0      | °C 111 |  |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 2.4       | °C/W   |  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 38.7      |        |  |

| $\theta_{JC(bottom)}$ | Junction-to-case(bottom) thermal resistance  | 17.8      |        |  |

(1) 有关传统和新的热度量的更多信息,请参阅 /C 封装热度量 应用报告 SPRA953。

#### ZHCS401-OCTOBER 2011

### ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

At  $T_J = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $|V_{IN}| = |V_{OUT(NOM)}| + 1.0V$  or  $|V_{IN}| = 3.0V$  (whichever is greater),  $V_{EN} = V_{IN}$ ,  $I_{OUT} = 1$ mA,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{NR/SS} = 0$ nF, and the FB pin tied to OUT, unless otherwise noted.

|                                                                   | PARAMETER                            | TEST CONDITIONS                                                                                                                                                                                                       | MIN             | TYP    | MAX       | UNIT              |

|-------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-----------|-------------------|

| V <sub>IN</sub>                                                   | Input voltage range                  |                                                                                                                                                                                                                       | -36.0           |        | -3.0      | V                 |

| V <sub>REF</sub>                                                  | Internal reference                   | V <sub>NR/SS</sub> = V <sub>REF</sub>                                                                                                                                                                                 | -1.22           | -1.184 | -1.142    | V                 |

|                                                                   | Output voltage range <sup>(2)</sup>  | $ V_{IN}  \ge  V_{OUT(NOM)}  + 1.0V$                                                                                                                                                                                  | -35.0           |        | $V_{REF}$ | V                 |

| V <sub>OUT</sub>                                                  | Nominal accuracy                     | $T_{J} = +25^{\circ}C,  V_{IN}  =  V_{OUT(NOM)}  + 0.5V$                                                                                                                                                              | -1.5            |        | +1.5      | %V <sub>OUT</sub> |

| •001                                                              | Overall accuracy                     | $ V_{OUT(NOM)}  + 1.0V \le  V_{IN}  \le 35V$<br>1mA $\le I_{OUT} \le 200$ mA                                                                                                                                          | -2.85           |        | +2.85     | %V <sub>OUT</sub> |

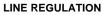

| $\left \frac{\Delta V_{OUT}(\Delta V_{IN})}{V_{OUT(NOM)}}\right $ | Line regulation                      | $T_J = +25^{\circ}C,  V_{OUT(NOM)}  + 1.0V \le  V_{IN}  \le 35V$                                                                                                                                                      |                 | 0.14   |           | %V <sub>OUT</sub> |

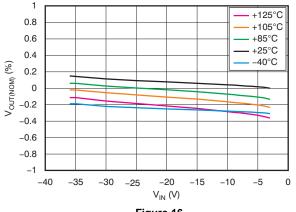

| $\frac{\Delta V_{OUT}(\Delta I_{OUT})}{V_{OUT(NOM)}}$             | Load regulation                      | $T_J = +25^{\circ}C, 1mA \le I_{OUT} \le 200mA$                                                                                                                                                                       |                 | 0.04   |           | %V <sub>OUT</sub> |

| N7 1                                                              | Dramout veltage                      | $V_{IN} = 95\% V_{OUT(NOM)}, I_{OUT} = 100mA$                                                                                                                                                                         |                 | 216    |           | mV                |

| IVDO Dropout voltage   Luce Current limit                         |                                      | $V_{IN} = 95\% V_{OUT(NOM)}, I_{OUT} = 200 \text{mA}$                                                                                                                                                                 |                 | 325    | 600       | mV                |

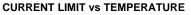

| I <sub>LIM</sub>                                                  | Current limit                        | V <sub>OUT</sub> = 90% V <sub>OUT(NOM)</sub>                                                                                                                                                                          | 220             | 330    | 500       | mA                |

|                                                                   | Crown di current                     | I <sub>OUT</sub> = 0mA                                                                                                                                                                                                |                 | 55     | 100       | μA                |

| I <sub>GND</sub>                                                  | Ground current                       | I <sub>OUT</sub> = 100mA                                                                                                                                                                                              |                 | 950    |           | μA                |

|                                                                   | Chutdaura augustu august             | V <sub>EN</sub> = +0.4V                                                                                                                                                                                               |                 | 1.0    | 3.0       | μA                |

| ISHDN                                                             | Shutdown supply current              | $V_{EN} = -0.4V$                                                                                                                                                                                                      |                 | 1.0    | 3.0       | μA                |

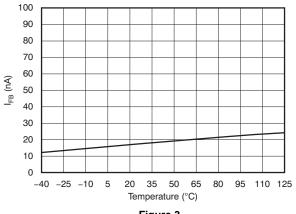

| I <sub>FB</sub>                                                   | Feedback current <sup>(3)</sup>      |                                                                                                                                                                                                                       |                 | 14     | 100       | nA                |

|                                                                   |                                      | $V_{EN} =  V_{IN}  =  V_{OUT(NOM)}  + 1.0V$                                                                                                                                                                           |                 | 0.48   | 1.0       | μA                |

| I <sub>EN</sub>                                                   | Enable current                       | $V_{IN} = V_{EN} = -35V$                                                                                                                                                                                              |                 | 0.51   | 1.0       | μA                |

|                                                                   |                                      | $V_{IN} = -35V, V_{EN} = +15V$                                                                                                                                                                                        |                 | 0.50   | 1.2       | μA                |

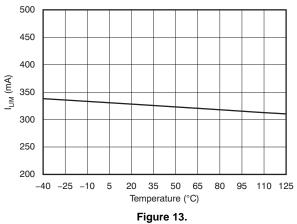

| V <sub>+EN_HI</sub>                                               | Positive enable high-level voltage   | $T_J = -55^{\circ}C \text{ to } +125^{\circ}C$                                                                                                                                                                        | +2.0            |        | +15       | V                 |

| V <sub>+EN_LO</sub>                                               | Positive enable low- level voltage   |                                                                                                                                                                                                                       | 0               |        | +0.4      | V                 |

| V_en_hi                                                           | Negative enable high-level voltage   |                                                                                                                                                                                                                       | V <sub>IN</sub> |        | -2.0      | V                 |

| V_ <sub>EN_LO</sub>                                               | Negative enable low- level voltage   |                                                                                                                                                                                                                       | -0.4            |        | 0         | V                 |

|                                                                   |                                      | $ \begin{array}{l} V_{\text{IN}} = -3V, \ V_{\text{OUT(NOM)}} = V_{\text{REF}}, \ C_{\text{OUT}} = 10 \mu\text{F}, \\ C_{\text{NR/SS}} = 10 n\text{F}, \ BW = 10 \text{Hz} \ \text{to} \ 100 \text{kHz} \end{array} $ |                 | 15.1   |           | μV <sub>RMS</sub> |

| V <sub>NOISE</sub>                                                | Output noise voltage                 | $V_{IN} = -6.2V, V_{OUT(NOM)} = -5V, C_{OUT} = 10\mu F, C_{NR/SS} = C_{BYP}^{(4)} = 10nF, BW = 10Hz to 100kHz$                                                                                                        |                 | 17.5   |           | μV <sub>RMS</sub> |

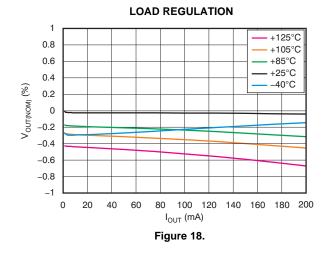

| PSRR                                                              | Power-supply rejection ratio         |                                                                                                                                                                                                                       |                 | 72     |           | dB                |

| т                                                                 |                                      | Shutdown, temperature increasing                                                                                                                                                                                      |                 | +170   |           | °C                |

| T <sub>SD</sub>                                                   | Thermal shutdown temperature         | Reset, temperature decreasing                                                                                                                                                                                         |                 | +150   |           | °C                |

| TJ                                                                | Operating junction temperature range |                                                                                                                                                                                                                       | -55             |        | +125      | °C                |

(1)

At operating conditions,  $V_{IN} \le 0V$ ,  $V_{OUT(NOM)} \le V_{REF} \le 0V$ . At regulation,  $V_{IN} \le V_{OUT(NOM)} - |V_{DO}|$ .  $I_{OUT} > 0$  flows from OUT to IN. To ensure stability at no load conditions, a current from the feedback resistive network equal to or greater than 5µA is required.  $I_{FB} > 0$  flows into the device.  $C_{BYP}$  refers to a bypass capacitor connected to the FB and OUT pins. (2)

(2) (3) (4)

ZHCS401-OCTOBER 2011

www.ti.com.cn

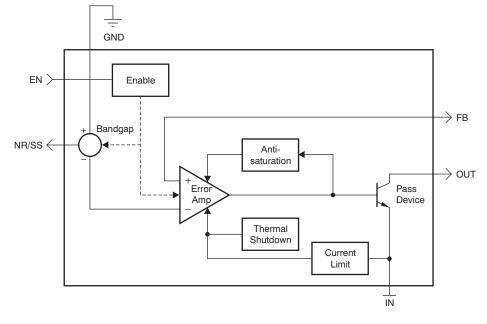

**DEVICE INFORMATION**

### FUNCTIONAL BLOCK DIAGRAM

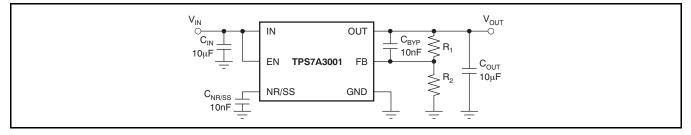

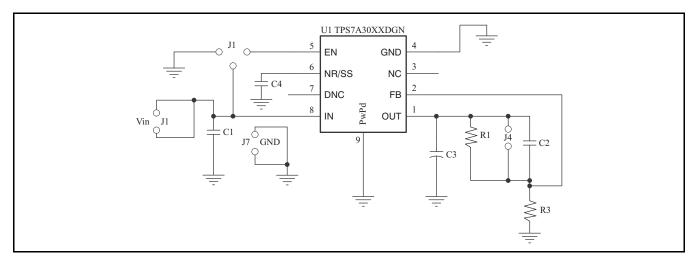

## **TYPICAL APPLICATION CIRCUIT**

### Maximize PSRR Performance and Minimize RMS Noise

ZHCS401-OCTOBER 2011

www.ti.com.cn

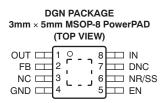

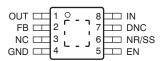

### **PIN CONFIGURATION**

| DGN PACKAGE |  |  |  |  |  |  |

|-------------|--|--|--|--|--|--|

| MSOP-8      |  |  |  |  |  |  |

| (TOP VIEW)  |  |  |  |  |  |  |

#### **PIN DESCRIPTIONS**

| NAME                  | NO.                                                                                                            | DESCRIPTION                                                                                                                                                                                                                                                                       |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| OUT                   | 1                                                                                                              | Regulator output. A capacitor $\ge 2.2\mu$ F must be tied from this pin to ground to assure stability.                                                                                                                                                                            |  |  |  |

| FB                    | FB 2 This pin is the input to the control-loop error amplifier. It is used to set the output voltage of the de |                                                                                                                                                                                                                                                                                   |  |  |  |

| NC                    | 3                                                                                                              | Not internally connected. This pin must either be left open or tied to GND.                                                                                                                                                                                                       |  |  |  |

| GND 4 Ground          |                                                                                                                | Ground                                                                                                                                                                                                                                                                            |  |  |  |

| EN 5                  |                                                                                                                | This pin turns the regulator on or off. If $V_{EN} \ge V_{+EN\_HI}$ or $V_{EN} \le V_{-EN\_HI}$ , the regulator is enabled.<br>If $V_{+EN\_LO} \ge V_{EN} \ge V_{-EN\_LO}$ , the regulator is disabled. The EN pin can be connected to IN, if not used. $ V_{EN}  \le  V_{IN} $ . |  |  |  |

| NR/SS6DNC7IN8PowerPAD |                                                                                                                | Noise reduction pin. Connecting an external capacitor to this pin bypasses noise generated by the internal bandgap. This capacitor allows RMS noise to be reduced to very low levels and also controls the soft-start function.                                                   |  |  |  |

|                       |                                                                                                                | DO NOT CONNECT. Do not route this pin to any electrical net, not even GND or IN.                                                                                                                                                                                                  |  |  |  |

|                       |                                                                                                                | Input supply                                                                                                                                                                                                                                                                      |  |  |  |

|                       |                                                                                                                | Must either be left open or tied to GND. Solder to printed circuit board (PCB) plane to enhance thermal performance.                                                                                                                                                              |  |  |  |

# **TPS7A3001-EP**

ZHCS401-OCTOBER 2011

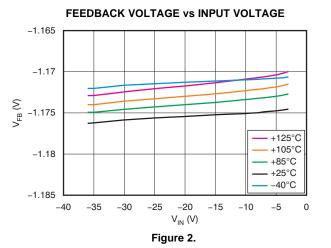

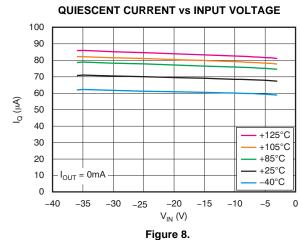

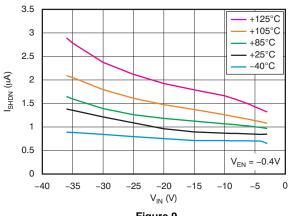

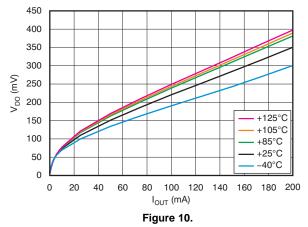

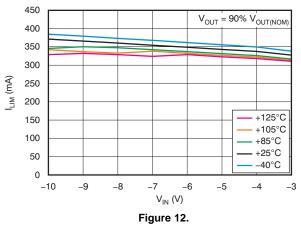

**TYPICAL CHARACTERISTICS**

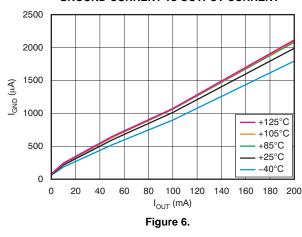

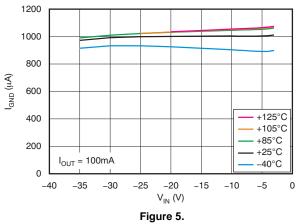

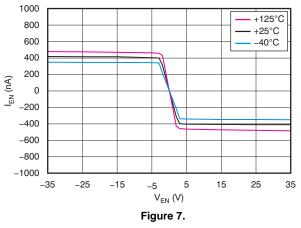

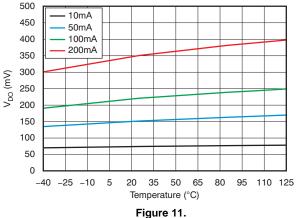

At  $T_J = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $|V_{IN}| = |V_{OUT(NOM)}| + 1.0V$  or  $|V_{IN}| = 3.0V$  (whichever is greater),  $V_{EN} = V_{IN}$ ,  $I_{OUT} = 1mA$ ,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{NR/SS} = 0$ nF, and the FB pin tied to OUT, unless otherwise noted.

**EXAS**

www.ti.com.cn

**ISTRUMENTS**

FEEDBACK CURRENT vs TEMPERATURE

**GROUND CURRENT vs INPUT VOLTAGE** 2500 0mA  $T_J = +25^{\circ}C$ 10mA 2000 50mA 100mA 200mA 1500 I<sub>GND</sub> (μA) 1000 500 0 -40 -35 -30 -25 -20 -15 -10 -5 0  $V_{\rm IN}~(V)$

**GROUND CURRENT vs OUTPUT CURRENT**

**GROUND CURRENT vs INPUT VOLTAGE**

**ENABLE CURRENT vs ENABLE VOLTAGE**

EXAS **ISTRUMENTS**

www.ti.com.cn

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $|V_{IN}| = |V_{OUT(NOM)}| + 1.0V$  or  $|V_{IN}| = 3.0V$  (whichever is greater),  $V_{EN} = V_{IN}$ ,  $I_{OUT} = 1mA$ ,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{NR/SS} = 0$ nF, and the FB pin tied to OUT, unless otherwise noted.

SHUTDOWN CURRENT vs INPUT VOLTAGE

Figure 9.

**DROPOUT VOLTAGE vs OUTPUT CURRENT**

**CURRENT LIMIT vs INPUT VOLTAGE**

**DROPOUT VOLTAGE vs TEMPERATURE**

## **TPS7A3001-EP**

ZHCS401-OCTOBER 2011

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $|V_{IN}| = |V_{OUT(NOM)}| + 1.0V$  or  $|V_{IN}| = 3.0V$  (whichever is greater),  $V_{EN} = V_{IN}$ ,  $I_{OUT} = 1mA$ ,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{NR/SS} = 0$ nF, and the FB pin tied to OUT, unless otherwise noted.

#### Figure 14.

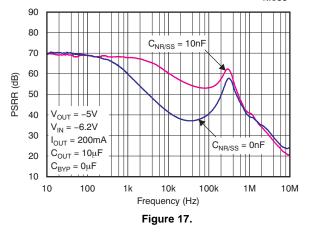

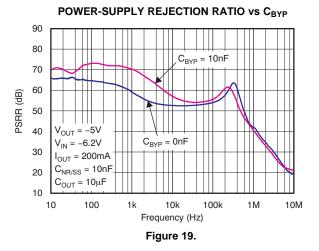

POWER-SUPPLY REJECTION RATIO vs C<sub>NR/SS</sub>

#### ZHCS401-OCTOBER 2011

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $|V_{IN}| = |V_{OUT(NOM)}| + 1.0V$  or  $|V_{IN}| = 3.0V$  (whichever is greater),  $V_{EN} = V_{IN}$ ,  $I_{OUT} = 1mA$ ,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{NR/SS} = 0$ nF, and the FB pin tied to OUT, unless otherwise noted.

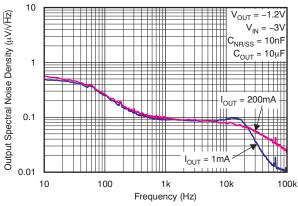

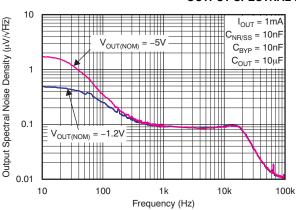

#### **OUTPUT SPECTRAL NOISE DENSITY vs OUTPUT CURRENT**

|                  | RMS NOISE      |                 |  |  |  |

|------------------|----------------|-----------------|--|--|--|

| Ι <sub>ουτ</sub> | 10Hz to 100kHz | 100Hz to 100kHz |  |  |  |

| 1mA              | 15.13          | 14.73           |  |  |  |

| 200mA            | 17.13          | 16.71           |  |  |  |

Figure 20.

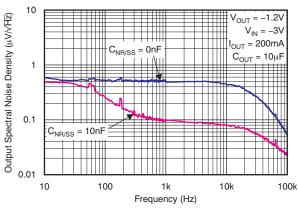

#### OUTPUT SPECTRAL NOISE DENSITY vs CNR/SS

|                    | RMS NOISE      |                 |  |  |  |  |

|--------------------|----------------|-----------------|--|--|--|--|

| C <sub>NR/SS</sub> | 10Hz to 100kHz | 100Hz to 100kHz |  |  |  |  |

| 0nF                | 80.00          | 79.83           |  |  |  |  |

| 10nF               | 17.29          | 16.81           |  |  |  |  |

Figure 21.

#### OUTPUT SPECTRAL NOISE DENSITY vs VOUT(NOM)

|                       | RMS NOISE      |                 |  |  |  |  |

|-----------------------|----------------|-----------------|--|--|--|--|

| V <sub>OUT(NOM)</sub> | 10Hz to 100kHz | 100Hz to 100kHz |  |  |  |  |

| –5V                   | 17.50          | 15.04           |  |  |  |  |

| -1.2V                 | 15.13          | 14.73           |  |  |  |  |

Figure 22.

## **TPS7A3001-EP**

ZHCS401-OCTOBER 2011

www.ti.com.cn

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_J = -55^{\circ}$ C to +125°C,  $|V_{IN}| = |V_{OUT(NOM)}|$  + 1.0V or  $|V_{IN}| = 3.0$ V (whichever is greater),  $V_{EN} = V_{IN}$ ,  $I_{OUT} = 1$ mA,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{NR/SS} = 0$ nF, and the FB pin tied to OUT, unless otherwise noted.

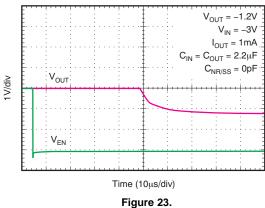

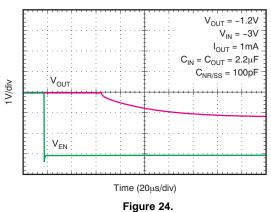

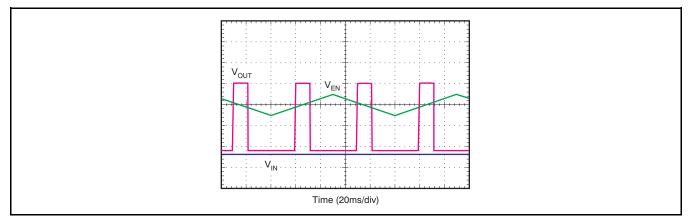

CAPACITOR-PROGRAMMABLE SOFT START

#### CAPACITOR-PROGRAMMABLE SOFT START

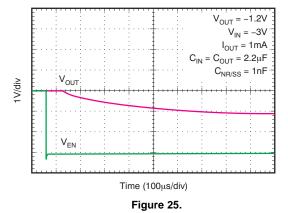

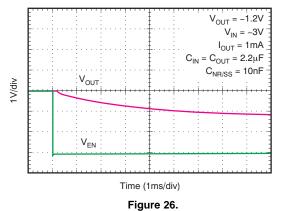

#### CAPACITOR-PROGRAMMABLE SOFT START

#### CAPACITOR-PROGRAMMABLE SOFT START

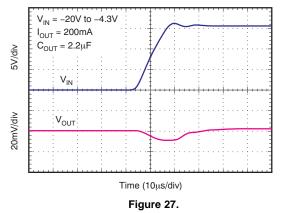

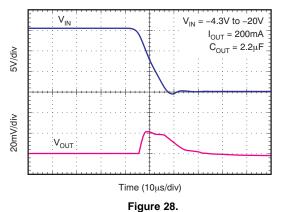

#### LINE TRANSIENT RESPONSE

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCS401-OCTOBER 2011

#### **TYPICAL CHARACTERISTICS (continued)**

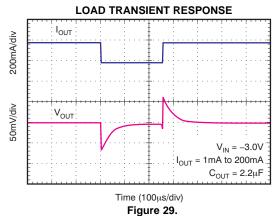

At  $T_J = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $|V_{IN}| = |V_{OUT(NOM)}| + 1.0V$  or  $|V_{IN}| = 3.0V$  (whichever is greater),  $V_{EN} = V_{IN}$ ,  $I_{OUT} = 1mA$ ,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $C_{NR/SS} = 0$ nF, and the FB pin tied to OUT, unless otherwise noted.

ZHCS401-OCTOBER 2011

## THEORY OF OPERATION

### **GENERAL DESCRIPTION**

The TPS7A3001 belongs to a family of new generation linear regulators that use an innovative bipolar process to achieve ultralow-noise and very high PSRR levels at a wide input voltage range. These features, combined with a high thermal performance MSOP-8 with PowerPAD package make this device ideal for high-performance analog applications.

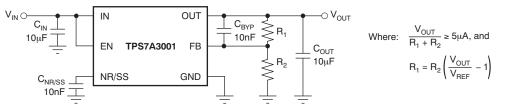

## ADJUSTABLE OPERATION

The TPS7A3001 has an output voltage range of -1.174 to -35V. The nominal output voltage of the device is set by two external resistors, as shown in Figure 30.

Figure 30. Adjustable Operation for Maximum AC Performance

$R_1$  and  $R_2$  can be calculated for any output voltage range using the formula shown in Equation 1. To ensure stability under no load conditions, this resistive network must provide a current equal to or greater than 5 $\mu$ A.

$$R_{1} = R_{2} \left( \frac{V_{OUT}}{V_{REF}} - 1 \right), \text{ where } \frac{V_{OUT}}{R_{1} + R_{2}} \ge 5\mu A \tag{1}$$

If greater voltage accuracy is required, take into account the output voltage offset contributions because of the feedback pin current and use 0.1% tolerance resistors.

## ENABLE PIN OPERATION

The TPS7A3001 provides a dual polarity enable pin (EN) that turns on the regulator when  $|V_{EN}| > 2.0V$ , whether the voltage is positive or negative, as shown in Figure 31.

This functionality allows for different system power management topologies:

- Connecting the EN pin directly to a negative voltage, such as  $V_{IN}$ , or

- Connecting the EN pin directly to a positive voltage, such as the output of digital logic circuitry.

Figure 31. Enable Pin Positive/Negative Threshold

#### ZHCS401-OCTOBER 2011

#### **CAPACITOR RECOMMENDATIONS**

Low ESR capacitors should be used for the input, output, noise reduction, and bypass capacitors. Ceramic capacitors with X7R and X5R dielectrics are preferred. These dielectrics offer more stable characteristics. Ceramic X7R capacitors offer improved over-temperature performance, while ceramic X5R capacitors are the most cost-effective and are available in higher values.

Note that high ESR capacitors may degrade PSRR.

#### INPUT AND OUTPUT CAPACITOR REQUIREMENTS

This negative, high-voltage linear regulator achieves stability with a minimum input and output capacitance of  $2.2\mu$ F; however, it is highly recommended to use a  $10\mu$ F capacitor to maximize ac performance.

#### NOISE REDUCTION AND BYPASS CAPACITOR REQUIREMENTS

Although noise reduction and bypass capacitors ( $C_{NR/SS}$  and  $C_{BYP}$ , respectively) are not needed to achieve stability, it is highly recommended to use 0.01µF capacitors to minimize noise and maximize ac performance.

#### MAXIMUM AC PERFORMANCE

In order to maximize noise and PSRR performance, it is recommended to include  $10\mu$ F or higher input and output capacitors, and  $0.01\mu$ F noise reduction and bypass capacitors, as shown in Figure 30. The solution shown delivers minimum noise levels of  $15.1\mu$ V<sub>RMS</sub> and power-supply rejection levels above 55dB from 10Hz to 700kHz; see Figure 19 and Figure 20.

#### **OUTPUT NOISE**

The TPS7A3001 provides low output noise when a noise reduction capacitor (C<sub>NR/SS</sub>) is used.

The noise reduction capacitor serves as a filter for the internal reference. By using a  $0.01\mu$ F noise reduction capacitor, the output noise is reduced by almost 80% (from  $80\mu$ V<sub>RMS</sub> to  $17\mu$ V<sub>RMS</sub>); see Figure 21.

TPS7A3001 low output voltage noise makes it an ideal solution for powering noise-sensitive circuitry.

#### **POWER-SUPPLY REJECTION**

The 0.01µF noise reduction capacitor greatly improves TPS7A3001 power-supply rejection, achieving up to 20dB of additional power-supply rejection for frequencies between 110Hz and 400KHz.

Additionally, ac performance can be maximized by adding a  $0.01\mu$ F bypass capacitor (C<sub>BYP</sub>) from the FB pin to the OUT pin. This capacitor greatly improves power-supply rejection at lower frequencies, for the band from 10Hz to 200kHz; see Figure 19.

The very high power-supply rejection of the TPS7A3001 makes it a good choice for powering high-performance analog circuitry, such as operational amplifiers, ADCs, DACS, and audio amplifiers.

#### TRANSIENT RESPONSE

As with any regulator, increasing the size of the output capacitor reduces over/undershoot magnitude but increases duration of the transient response.

#### ZHCS401-OCTOBER 2011

### **APPLICATION INFORMATION**

#### POWER FOR PRECISION ANALOG

One of the primary TPS7A3001 applications is to provide ultralow noise voltage rails to high-performance analog circuitry in order to maximize system accuracy and precision.

In conjunction with its positive counterpart, the TPS7A49xx family of positive high-voltage linear regulators, this negative high voltage linear regulator provides ultralow noise positive and negative voltage rails to high-performance analog circuitry, such as operational amplifiers, ADCs, DACs, and audio amplifiers.

Because of the ultralow noise levels at high voltages, analog circuitry with high-voltage input supplies can be used. This characteristic allows for high-performance analog solutions to optimize the voltage range, maximizing system accuracy.

### POST DC/DC CONVERTER FILTERING

Most of the time, the voltage rails available in a system do not match the voltage specifications demanded by one or more of its circuits; these rails must be stepped up or down, depending on specific voltage requirements.

DC/DC converters are the preferred solution to step up or down a voltage rail when current consumption is not negligible. They offer high efficiency with minimum heat generation, but they have one primary disadvantage: they introduce a high-frequency component, and the associated harmonics, on top of the dc output signal.

This high-frequency component, if not filtered properly, degrades analog circuitry performance, reducing overall system accuracy and precision.

The TPS7A3001 offers a wide-bandwidth, very-high power-supply rejection ratio. This specification makes it ideal for post dc/dc converter filtering, as shown in Figure 32. It is highly recommended to use the maximum performance schematic shown in Figure 30. Also, verify that the fundamental frequency (and its first harmonic, if possible) is within the bandwidth of the regulator PSRR, shown in Figure 19.

Figure 32. Post DC/DC Converter Regulation to High-Performance Analog Circuitry

### AUDIO APPLICATIONS

Audio applications are extremely sensitive to any distortion and noise in the audio band from 20Hz to 20kHz. This stringent requirement demands clean voltage rails to power critical high-performance audio systems.

The very-high power-supply rejection ratio (> 55dB) and low noise at the audio band of the TPS7A3001 maximize performance for audio applications; see Figure 19.

ZHCS401-OCTOBER 2011

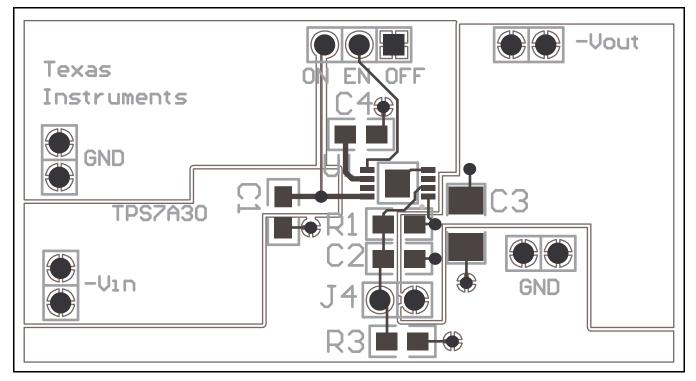

### LAYOUT

### PACKAGE MOUNTING

Solder pad footprint recommendations for the TPS7A3001 are available at the end of this product datasheet and at www.ti.com.

#### BOARD LAYOUT RECOMMENDATIONS TO IMPROVE PSRR AND NOISE PERFORMANCE

To improve ac performance such as PSRR, output noise, and transient response, it is recommended that the board be designed with separate ground planes for IN and OUT, with each ground plane connected only at the GND pin of the device. In addition, the ground connection for the output capacitor should connect directly to the GND pin of the device.

Equivalent series inductance (ESL) and equivalent series resistance (ESR) must be minimized in order to maximize performance and ensure stability. Every capacitor ( $C_{IN}$ ,  $C_{OUT}$ ,  $C_{NR/SS}$ ,  $C_{BYP}$ ) must be placed as close as possible to the device and on the same side of the printed circuit board (PCB) as the regulator itself.

Do not place any of the capacitors on the opposite side of the PCB from where the regulator is installed. The use of vias and long traces is strongly discouraged because they may impact system performance negatively and even cause instability.

If possible, and to ensure the maximum performance denoted in this product datasheet, use the same layout pattern used for TPS7A30 evaluation board, available at www.ti.com.

#### THERMAL PROTECTION

Thermal protection disables the output when the junction temperature rises to approximately +170°C, allowing the device to cool. When the junction temperature cools to approximately +150°C, the output circuitry is enabled. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the dissipation of the regulator, protecting it from damage as a result of overheating.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heatsink. For reliable operation, junction temperature should be limited to a maximum of +125°C. To estimate the margin of safety in a complete design (including heatsink), increase the ambient temperature until the thermal protection is triggered; use worst-case loads and signal conditions. For good reliability, thermal protection should trigger at least +35°C above the maximum expected ambient condition of your particular application. This configuration produces a worst-case junction temperature of +125°C at the highest expected ambient temperature and worst-case load.

The internal protection circuitry of the TPS7A3001 has been designed to protect against overload conditions. It was not intended to replace proper heatsinking. Continuously running the TPS7A3001 into thermal shutdown degrades device reliability.

#### POWER DISSIPATION

The ability to remove heat from the die is different for each package type, presenting different considerations in the PCB layout. The PCB area around the device that is free of other components moves the heat from the device to the ambient air. Using heavier copper increases the effectiveness in removing heat from the device. The addition of plated through-holes to heat dissipating layers also improves the heatsink effectiveness.

Power dissipation depends on input voltage and load conditions. Power dissipation ( $P_D$ ) is equal to the product of the output current times the voltage drop across the output pass element, as shown in Equation 2:

$$\mathsf{P}_{\mathsf{D}} = (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \mathsf{I}_{\mathsf{OUT}}$$

(2)

#### SUGGESTED LAYOUT AND SCHEMATIC

Layout is a critical part of good power-supply design. There are several signal paths that conduct fast-changing currents or voltages that can interact with stray inductance or parasitic capacitance to generate noise or degrade the power-supply performance. To help eliminate these problems, the IN pin should be bypassed to ground with a low ESR ceramic bypass capacitor with a X5R or X7R dielectric.

ZHCS401-OCTOBER 2011

The GND pin should be tied directly to the PowerPAD under the IC. The PowerPAD should be connected to any internal PCB ground planes using multiple vias directly under the IC.

It may be possible to obtain acceptable performance with alternate PCB layouts; however, the layout shown in Figure 33 and the schematic shown in Figure 34 have been shown to produce good results and are meant as a guideline.

Figure 33. PCB Layout Example

Figure 34. Schematic for PCB Layout Example

### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                 |              | (4/5)          |         |

| TPS7A3001MDGNTEP | ACTIVE | HVSSOP       | DGN     | 8    | 250     | RoHS & Green | (6)<br>NIPDAU | Level-2-260C-1 YEAR | -55 to 125   | PXCM           | Samples |

| TPS7A4700RGWR    | ACTIVE | VQFN         | RGW     | 20   | 3000    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | PXSQ           | Samples |

| TPS7A4700RGWT    | ACTIVE | VQFN         | RGW     | 20   | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | PXSQ           | Samples |

| TPS7A4701RGWR    | ACTIVE | VQFN         | RGW     | 20   | 3000    | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | 7A4701         | Samples |

| TPS7A4701RGWT    | ACTIVE | VQFN         | RGW     | 20   | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | 7A4701         | Samples |

| V62/11619-01XE   | ACTIVE | HVSSOP       | DGN     | 8    | 250     | RoHS & Green | NIPDAU        | Level-2-260C-1 YEAR | -55 to 125   | PXCM           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

www.ti.com

11-Dec-2020

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **GENERIC PACKAGE VIEW**

# PowerPAD VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

3 x 3, 0.65 mm pitch

**DGN 8**

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4225482/A

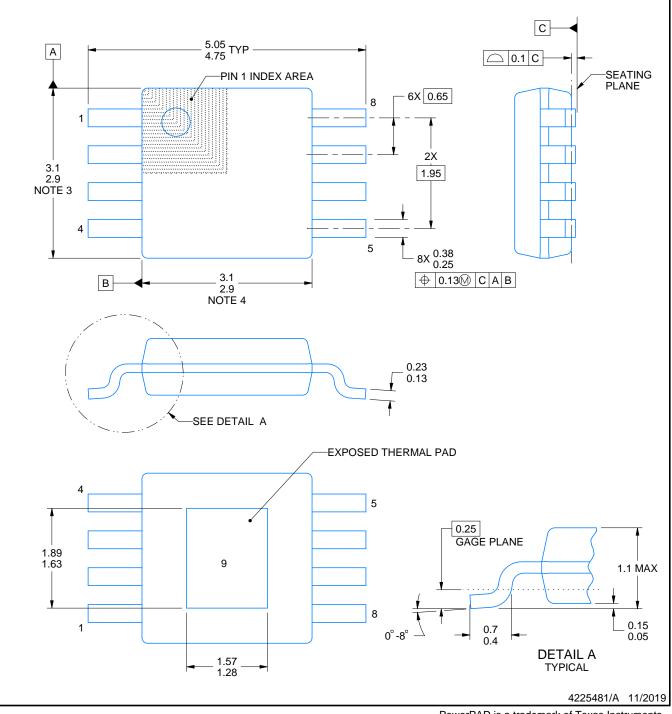

# **DGN0008D**

# **PACKAGE OUTLINE**

# PowerPAD<sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

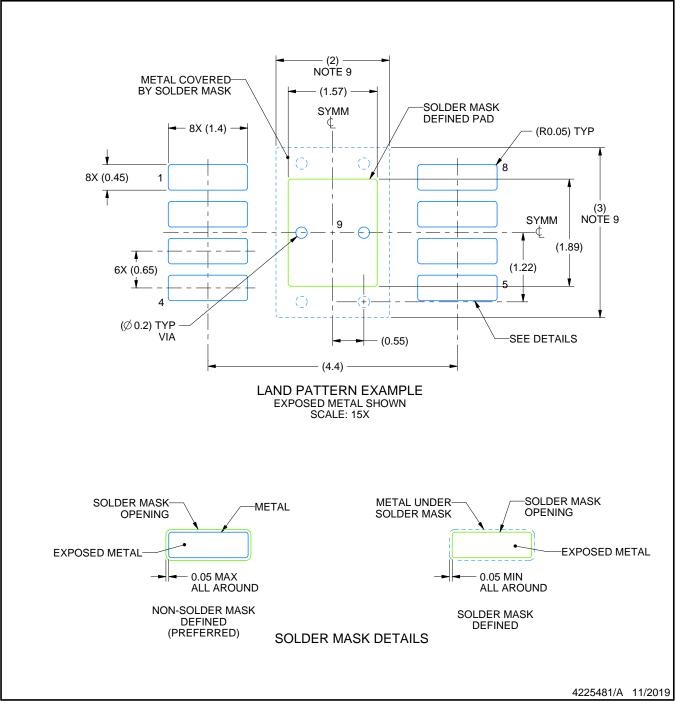

# **DGN0008D**

# **EXAMPLE BOARD LAYOUT**

# PowerPAD<sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown

- on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

# DGN0008D

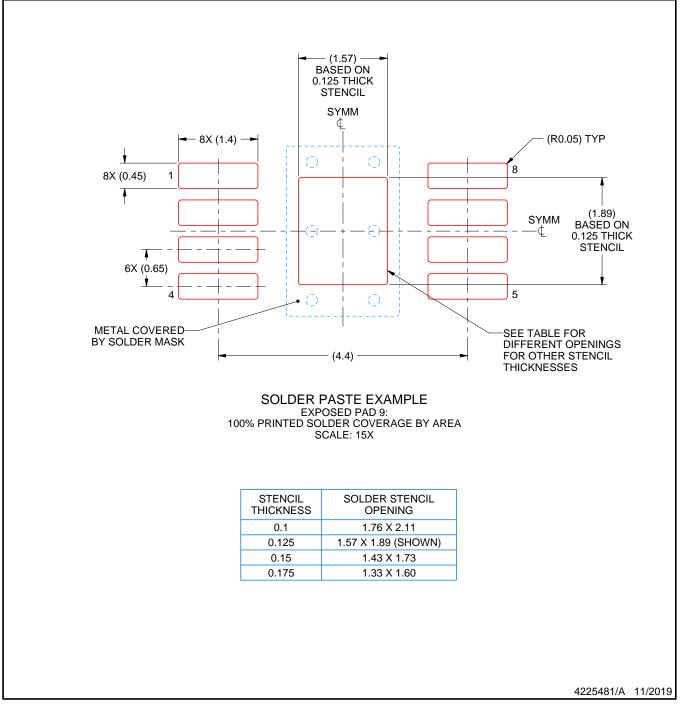

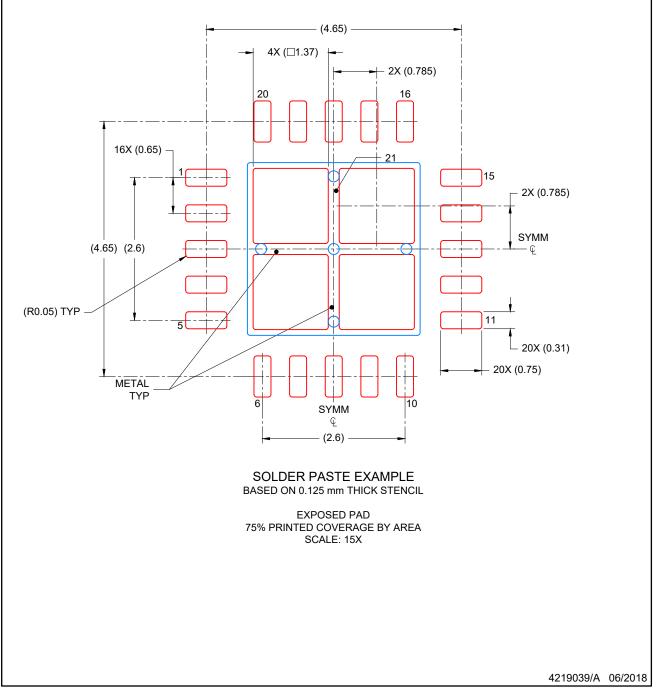

# **EXAMPLE STENCIL DESIGN**

# PowerPAD<sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 11. Board assembly site may have different recommendations for stencil design.

# **RGW 20**

5 x 5, 0.65 mm pitch

# **GENERIC PACKAGE VIEW**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

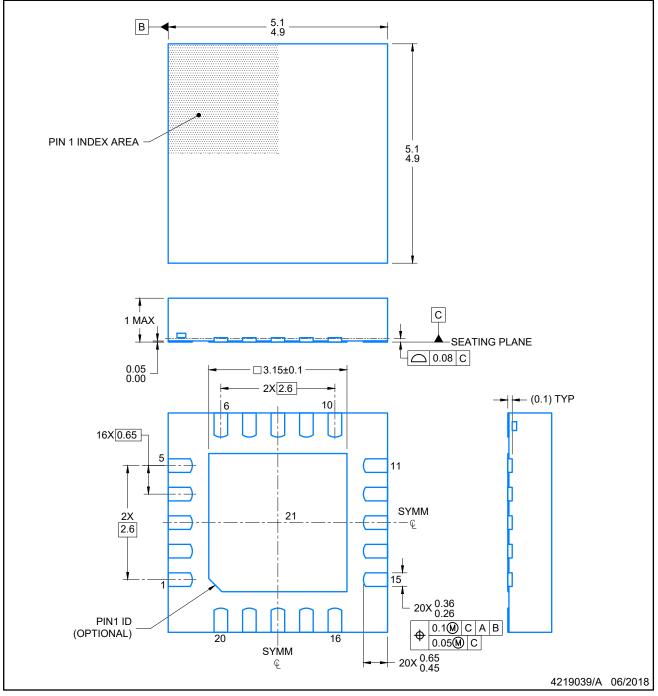

# **RGW0020A**

# **PACKAGE OUTLINE**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

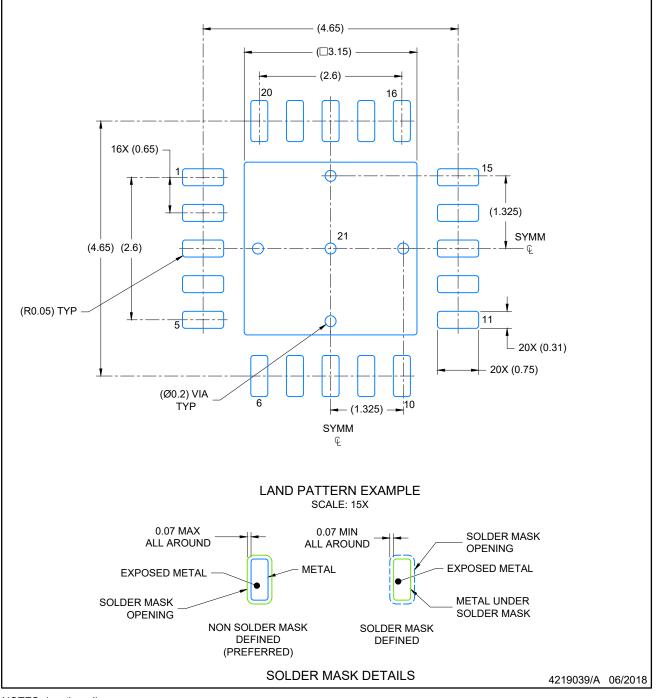

# **RGW0020A**

# **EXAMPLE BOARD LAYOUT**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# **RGW0020A**

## **EXAMPLE STENCIL DESIGN**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司