TPS54362-HT

ZHCSA98-SEPTEMBER 2012

# 具有低 lq 的 1A, 48V 降压 DC/DC 转换器

查询样品: TPS54362-HT

#### 特性

- 在工作电压范围为 3.6V 至 48V 时可耐受高达 60V 的瞬态电压

- 带有外部组件(L和C)的异步开关模式稳压器, 负载电流高达1A(最大值)

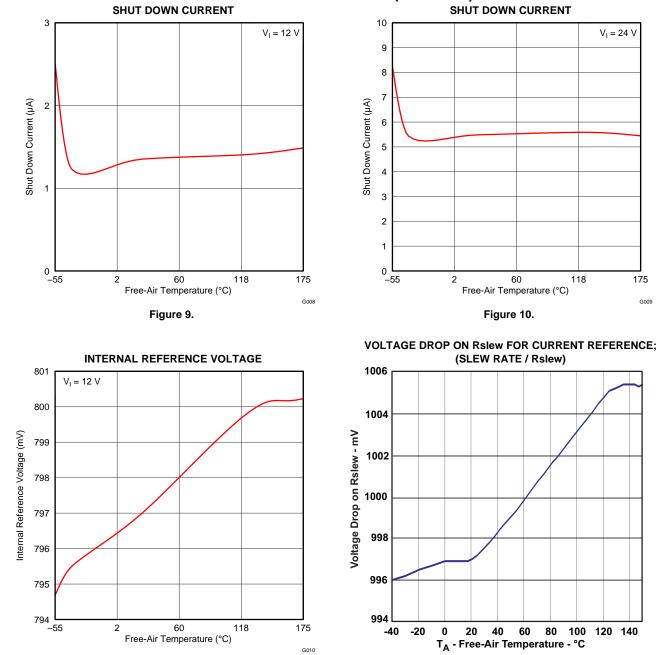

- 0.8V±1.5% 电压基准

- 200kHz 至 2.2MHz 开关频率

- 针对开/关状态的高压容限启用输入

- 启用周期上的软启动

- 内部电源开关上的转换率控制

- 用于同步的外部时钟输入

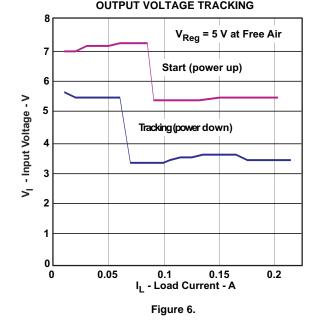

- 轻输出负载期间(静态电流典型值 = 65µA)的脉 冲跳跃模式 (PFM)(LPM 运行)

- 宽带误差放大器的外部补偿

- 内部欠电压闭锁 UVLO

- 可编程复位加电延迟

- 针对快速负瞬态的复位功能滤波时间

- 可编程过压输出监控

- 可编程欠电压输出监视,确保当输出低于设置的阈 值时复位

- 开关电流限制保护

#### 说明

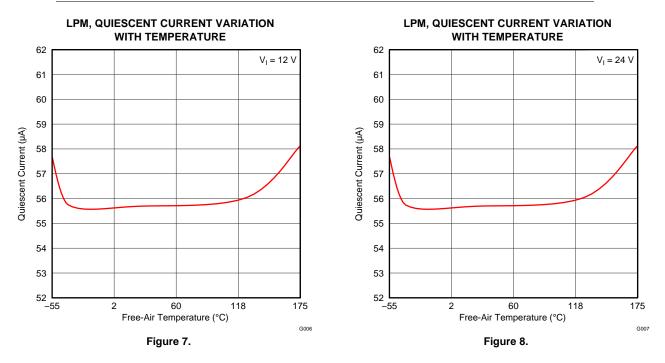

**TPS54362** 是一款具有电压监控器的降压开关模式电源。 集成输入电压线路前馈拓扑结构改进了电压模式降压稳压器的线路瞬态稳压。 此稳压器有一个逐周期电流限制。 无负载情况下的脉冲跳跃模式运行将电源电流减少至 65μA。 通过使用使能引脚,可将关断电源电流减少至 1μA。

当标称输出下降至低于外部电阻分压器网络设定的阀值时,一个开漏复位信号对此情况进行显示。输出电压启动斜 坡由一个软启动电容器控制。当输入电源斜坡低至 2.6V 时,一个内部欠压关断被激活。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

- 场效应晶体管 (FET) 的短路和过流保护

- 封装: 20 引脚散热薄型小外形尺寸封装 (HTSSOP)

PowerPAD™

## 应用范围

- 潜孔钻孔

- 高温环境

#### 支持极端温度环境下的应用

- 受控基线

- 一个组装和测试场所

- 一个制造场所

- 支持极端(-55℃至175℃)温度范围

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

- 德州仪器(TI)高温产品利用高度优化的硅(芯 片)解决方案,此解决方案对设计和制造工艺进行 了提升以在扩展的温度范围内大大地提高性能。

## **TPS54362-HT** ZHCSA98-SEPTEMBER 2012

www.ti.com.cn

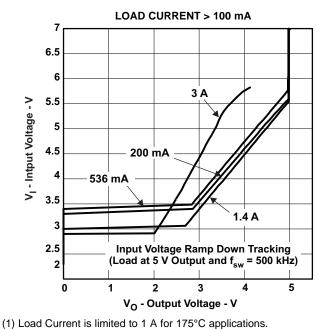

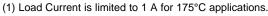

<sup>(1)</sup> 对于 175°C 应用,负载电流被限制在 1A。

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| ORDERING | INFORMATION <sup>(1)</sup> |

|----------|----------------------------|

|----------|----------------------------|

| Tj             | PACKAGE | PART NUMBER  | TOP-SIDE MARKING |

|----------------|---------|--------------|------------------|

| –55°C to 175°C | PWP     | TPS54362HPWP | 54632H           |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

|                                            |                                                     | VALUE                           | UNIT |

|--------------------------------------------|-----------------------------------------------------|---------------------------------|------|

|                                            | EN                                                  | -0.3 to 60                      | V    |

|                                            | VIN                                                 | -0.3 to 60                      |      |

|                                            | VReg                                                | -0.3 to 20                      |      |

|                                            | LPM                                                 | -0.3 to 5.5                     |      |

| Input voltage                              | OV_TH                                               | -0.3 to 5.5                     |      |

|                                            | RST_TH                                              | -0.3 to 5.5                     |      |

|                                            | SYNC                                                | -0.3 to 5.5                     |      |

|                                            | VSENSE                                              | -0.3 to 5.5                     |      |

| Output voltage                             | BOOT                                                | -0.3 to 65                      | V    |

|                                            | PH                                                  | -0.3 to 60                      |      |

|                                            |                                                     | -2 for 30 ns                    |      |

|                                            |                                                     | -1 for 200 ns                   |      |

|                                            |                                                     | -0.85 at T <sub>A</sub> = -55°C |      |

|                                            |                                                     | -0.5 at T <sub>A</sub> = 175°C  |      |

|                                            | RT                                                  | -0.3 to 5.5                     |      |

|                                            | RST                                                 | -0.3 to 5.5                     |      |

|                                            | Cdly                                                | –0.3 to 8                       |      |

|                                            | SS                                                  | –0.3 to 8                       |      |

|                                            | COMP                                                | –0.3 to 7                       |      |

| Temperature                                | Operating virtual junction temperature range, $T_J$ | -55 to 185                      | °C   |

|                                            | Storage temperature range, T <sub>S</sub>           | -55 to 185                      | °C   |

| Electrostatic discharge HBM <sup>(2)</sup> |                                                     | 2                               | kV   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to ground.

(2) The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin

Texas Instruments

www.ti.com.cn

#### **RECOMMENDED OPERATING CONDITIONS**

|                  |                                                                  | MIN | MAX  | UNIT |

|------------------|------------------------------------------------------------------|-----|------|------|

| VI               | Unregulated Buck supply input voltage (VIN, EN)                  | 3.6 | 48   | V    |

| $V_{\text{Reg}}$ | Regulator voltage range                                          | 0.9 | 18   | V    |

| $V_{\text{Reg}}$ | Power up in Low Power Mode (LPM) or Discontinuous Mode (DCM)     | 0.9 | 5.5  | V    |

|                  | Bootstrap Capacitor (BOOT)                                       | 3.6 | 56   | V    |

|                  | Switched outputs (PH)                                            | 3.6 | 48   | V    |

|                  | Logic level inputs (RST, VSENSE, OV_TH, RST_TH, Rslew, SYNC, RT) | 0   | 5.25 | V    |

|                  | Logic level inputs (SS, Cdly, COMP)                              | 0   | 6.5  | V    |

| TJ               | Operating junction temperature range <sup>(1)</sup>              | -55 | 175  | °C   |

(1) This assumes  $T_A = T_J - Power dissipation \times \theta J_A$  (Junction to Ambient).

#### THERMAL INFORMATION

|                    |                                                             | TPS54362 |                |

|--------------------|-------------------------------------------------------------|----------|----------------|

|                    | THERMAL METRIC <sup>(1)</sup>                               | PWP      | UNITS          |

|                    |                                                             | 20 PINS  |                |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 37.5     |                |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 21.4     |                |

| $\theta_{JB}$      | Junction-to-board thermal resistance <sup>(4)</sup>         | 18.5     | 8 <b>0</b> AA4 |

| ΨJT                | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.5      | °C/W           |

| $\Psi_{JB}$        | Junction-to-board characterization parameter <sup>(6)</sup> | 18.2     |                |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 1.1      |                |

(1) 有关传统和新的热 度量的更多信息,请参阅*IC 封装热度量*应用报告, SPRA953。 (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然 对流条件下的结至环 境热阻。

(3) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但 可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

(4) 按照 JESD51-8 中的说明,通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结板热阻。

结至顶部特征参数, ψ<sub>JT</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该参 (5) 数以便获得 θιΔ。

结至电路板特征参数, ψ<sub>JB</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该 (6) 参数以便获得 θ<sub>JA</sub>。 (7) 通过在外露(电源)焊盘上进行冷板测试仿真来获得 结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准 测试,但可在 ANSI SEMI

标准 G30-88 中能找到内容接近的说明。

## DC ELECTRICAL CHARACTERISTICS

$V_{IN}$  = 7 V to 48 V, EN =  $V_{IN}$ ,  $T_J$  = -55°C to 175°C (unless otherwise noted)

|                          | PARAMETER                                                    | TEST CONDITIONS                                                                           | $T_{J} = -4$ | T <sub>J</sub> = -40°C to 125°C |       | T <sub>J</sub> = -5 | 5°C to 17 | 75°C  | UNIT |

|--------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|---------------------------------|-------|---------------------|-----------|-------|------|

|                          |                                                              |                                                                                           | MIN          | TYP                             | MAX   | MIN                 | TYP       | MAX   |      |

| INPUT P                  | OWER SUPPLY                                                  |                                                                                           | -            |                                 |       |                     |           |       |      |

|                          |                                                              | Normal mode-Buck mode after initial start up                                              | 3.6          |                                 | 48    | 3.6                 |           | 48    |      |

|                          |                                                              | Low power mode:                                                                           |              |                                 |       |                     |           |       |      |

| V <sub>IN</sub>          | Supply voltage on VIN line                                   | Falling threshold (LPM disabled)                                                          |              | 8                               |       |                     | 8         |       | V    |

|                          |                                                              | Rising threshold (LPM activated)                                                          |              | 8.5                             |       |                     | 8.5       |       |      |

|                          |                                                              | High voltage threshold (LPM disabled)                                                     | 25           | 27                              | 30    | 25                  | 27        | 30    |      |

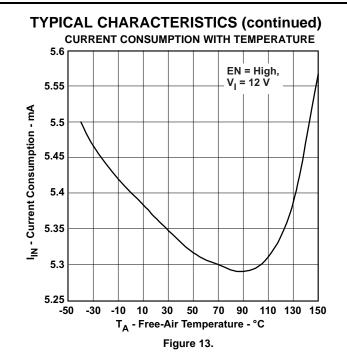

| Iq <sub>-Normal</sub>    | Quiescent current normal mode                                | Open loop test – max duty cycle<br>V <sub>IN</sub> = 7 V to 48 V                          |              | 5                               | 10    |                     | 5         | 10    | mA   |

|                          | Quiescent current; low                                       | $I_{LOAD} < 1 \text{ mA}, V_{IN} = 12 \text{ V}$                                          |              | 65                              | 75    |                     | 65        | 88    | μA   |

| I <sub>q-LPM</sub>       | power mode                                                   | $I_{LOAD} < 1 \text{ mA}, V_{IN} = 24 \text{ V}$                                          |              |                                 | 85    |                     |           | 98    | μA   |

|                          | Obutdaura                                                    | EN = 0 V, device is OFF, $V_{IN}$ = 24 V                                                  |              | 5.5                             | 10    |                     | 8.5       | 16    |      |

| I <sub>SD</sub> Shutdown |                                                              | EN = 0 V, device is OFF, $V_{IN}$ = 12 V                                                  |              | 1                               | 4     |                     | 2.5       | 7.5   | μA   |

| TRANSI                   | TION TIMES (LOW POWER -                                      | NORMAL MODES) <sup>(1)</sup>                                                              |              |                                 |       |                     |           |       |      |

| t <sub>d1</sub>          | Transition delay between<br>normal mode to low power<br>mode | $V_{IN} = 12 \text{ V},  V_{Reg} = 5 \text{ V},  I_{LOAD} = 1 \text{ A to } 1 \text{ mA}$ |              | 100                             |       |                     | 100       |       | μs   |

| t <sub>d2</sub>          | Transition delay between<br>low power mode to normal<br>mode | $V_{IN}$ = 12 V, $V_{Reg}$ = 5 V I <sub>LOAD</sub> = 1 mA to 1 A                          |              | 5                               |       |                     | 5         |       | μs   |

| SWITCH                   | MODE SUPPLY; V <sub>Reg</sub>                                |                                                                                           |              |                                 |       |                     |           |       |      |

| V <sub>Reg</sub>         | Regulator output                                             | V <sub>SENSE</sub> = 0.8 V ref                                                            | 0.9          |                                 | 18    | 0.9                 |           | 18    | V    |

| V <sub>SENSE</sub>       | Feedback voltage                                             | $V_{Reg}$ = 0.9 V to 18 V, $V_{IN}$ = 7 V to 48 V                                         | 0.788        | 0.8                             | 0.812 | 0.770               | 0.8       | 0.830 | V    |

| R <sub>DS(on)</sub>      | Internal switch resistance                                   | Measured across VIN and PH, $I_{Load}$ = 500 mA                                           |              |                                 | 500   |                     |           | 600   | mΩ   |

| I <sub>CL</sub>          | Switch current limit cycle by cycle                          | V <sub>IN</sub> = 12 V                                                                    | 4            | 6                               | 8     | 4                   | 6         | 8     | А    |

| t <sub>ON-Min</sub>      | Duty cycle pulse width                                       |                                                                                           |              | 100                             |       |                     | 100       |       |      |

| t <sub>OFF-Min</sub>     |                                                              |                                                                                           |              | 200                             |       |                     | 200       |       | ns   |

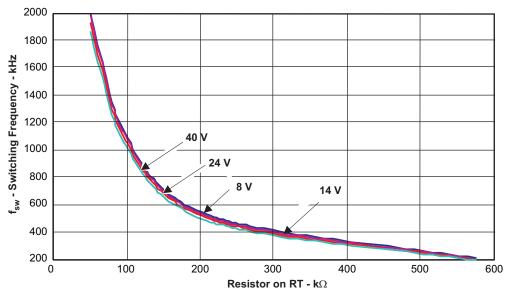

|                          | Switch mode frequency                                        | Set using external resistor on RT pin                                                     | 0.2          |                                 | 2.2   | 0.2                 |           | 2.2   | MHz  |

| f <sub>SW</sub>          | Internal oscillator frequency                                |                                                                                           | -10          |                                 | 10    | -22                 |           | 22    | %    |

| I <sub>Sink</sub>        | Start up condition                                           | OV_TH = 0 V, V <sub>Reg</sub> = 10 V                                                      |              |                                 | 1     |                     |           | 1     | mA   |

| I <sub>Limit</sub>       | Prevent overshoot                                            | 0 V < OV_TH < 0.8 V, V <sub>Reg</sub> = 10 V                                              |              |                                 | 80    |                     |           | 80    | mA   |

(1) This test is for characterization only

TPS54362-HT

ZHCSA98-SEPTEMBER 2012

www.ti.com.cn

## DC ELECTRICAL CHARACTERISTICS

$V_{IN}$  = 7 V to 48 V, EN =  $V_{IN}$ ,  $T_J$  = -55°C to 175°C (unless otherwise noted)

|                        | PARAMETER                                         | TEST CONDITIONS                                                                                                                                       | $T_{J} = -4$ | 0°C to 1 | 25°C  | T <sub>J</sub> = -5 | 5°C to 17 | 75°C  | UNI |

|------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|-------|---------------------|-----------|-------|-----|

|                        |                                                   |                                                                                                                                                       | MIN          | ТҮР      | MAX   | MIN                 | TYP       | MAX   |     |

| ENABLE (I              | EN)                                               |                                                                                                                                                       |              |          |       |                     |           |       |     |

| V <sub>IL</sub>        | Low input threshold                               |                                                                                                                                                       |              |          | 0.7   |                     |           | 0.7   | V   |

| V <sub>IH</sub>        | High input threshold                              |                                                                                                                                                       | 1.7          |          |       | 1.7                 |           |       | V   |

|                        |                                                   | EN = 60 V                                                                                                                                             |              | 100      | 135   |                     | 110       | 200   | μA  |

| l <sub>lkg</sub>       | Leakage into EN terminal                          | EN = 12 V                                                                                                                                             |              | 8        | 15    |                     | 10        | 20    | μA  |

| RESET DE               | LAY (Cdly)                                        | L                                                                                                                                                     | I            |          |       |                     |           |       |     |

| lo                     | External capacitor charge current                 | EN = high                                                                                                                                             | 1.4          | 2        | 2.6   | 1.3                 | 2         | 2.8   | μA  |

| V <sub>Threshold</sub> | Switching threshold                               | Output voltage in regulation                                                                                                                          |              | 2        |       |                     | 2         |       | V   |

| V <sub>IL</sub>        | Low input threshold                               | V <sub>IN</sub> = 12 V                                                                                                                                |              |          | 0.7   |                     |           | 0.7   | V   |

| V <sub>IH</sub>        | High input threshold                              | V <sub>IN</sub> = 12 V                                                                                                                                | 1.7          |          |       | 1.7                 |           |       | V   |

| l <sub>ikg</sub>       | Leakage into LPM terminal                         | LPM = 5 V                                                                                                                                             |              | 65       | 95    |                     | 65        | 95    | μA  |

| RESET OU               | JTPUT (RST)                                       |                                                                                                                                                       |              |          |       |                     |           |       |     |

| t <sub>rdly</sub>      | POR delay timer                                   | Based on Cdly capacitor, Cdly = 4.7 nF                                                                                                                | 3.6          |          | 7     | 3.3                 |           | 8     | m   |

| RST_TH                 | Reset threshold for V <sub>Reg</sub>              | Check RST output                                                                                                                                      | 0.768        |          | 0.832 | 0.768               |           | 0.832 | V   |

| t <sub>nRSTdly</sub>   | Filter time                                       | Delay before RST is asserted low                                                                                                                      | 10           | 20       | 35    | 9.3                 | 20        | 35    | με  |

| I <sub>SS</sub>        | Soft-start source current                         |                                                                                                                                                       | 40           | 50       | 60    | 40                  | 50        | 60    | μA  |

| SYNCHRO                | NIZATION (SYNC) <sup>(1)</sup>                    |                                                                                                                                                       | 1            |          |       |                     |           | 1     |     |

|                        | V <sub>IL</sub>                                   |                                                                                                                                                       |              |          | 0.7   |                     |           | 0.7   |     |

| V <sub>SYNC</sub>      | V <sub>IH</sub>                                   |                                                                                                                                                       | 1.7          |          |       | 1.7                 |           |       | V   |

| l <sub>ikg</sub>       | Leakage                                           | SYNC = 5 V                                                                                                                                            |              | 65       | 95    |                     | 65        | 95    | μA  |

| SYNC                   | Input clock                                       | $\begin{split} V_{\text{IN}} &= 12 \text{ V},  V_{\text{Reg}} = 5 \text{ V}, \\ f_{\text{SW}} &< f_{\text{ext}} < 2 \times f_{\text{SW}} \end{split}$ | 180          |          | 2200  | 180                 |           | 2200  | kH  |

| SYNC <sub>trans</sub>  | External clock to internal<br>clock               | No external clock, $V_{IN}$ = 12 V, $V_{Reg}$ = 5 V                                                                                                   |              | 32       |       |                     | 32        |       |     |

| STINCtrans             | Internal clock to external<br>clock               | External clock = 1 MHz, $V_{IN}$ = 12 V, $V_{Reg}$ = 5 V                                                                                              |              | 2.5      |       |                     | 2.5       |       | μs  |

| SYNC <sub>CLK</sub>    | Min duty cycle                                    |                                                                                                                                                       | 30           |          |       | 30                  |           |       | %   |

| STRUCCLK               | Max duty cycle                                    |                                                                                                                                                       |              |          | 70    |                     |           | 70    | 70  |

| Rslew                  |                                                   |                                                                                                                                                       |              |          |       |                     |           |       |     |

|                        | Rslew = 50 k $\Omega$                             |                                                                                                                                                       |              | 20       |       |                     | 20        |       | /   |

| Rslew                  | Rslew = 10 k $\Omega$                             |                                                                                                                                                       |              | 100      |       |                     | 100       |       | μA  |

| OVERVOL                | TAGE SUPERVISORS (OV_1                            | ГН)                                                                                                                                                   |              |          |       |                     |           |       |     |

| OV_TH                  | Threshold for V <sub>Reg</sub> during overvoltage | Internal switch is turned OFF                                                                                                                         | 0.768        |          | 0.832 | 0.768               |           | 0.832 | V   |

| UV_IN                  | V <sub>Reg</sub> = 5 V                            | Internal pull down on V <sub>Reg</sub> , with<br>OV_TH = 1 V                                                                                          |              | 70       |       |                     | 70        |       | m/  |

(1) The SYNC input clock can have a maximum frequency of 2x the programmed clock frequency up to a maximum value of 1.1MHz.

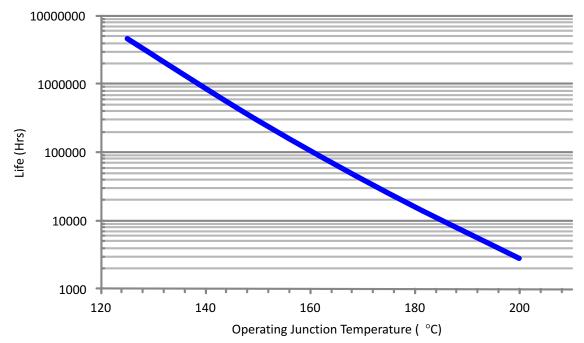

- (1) See data sheet for absolute maximum and minimum recommended operating conditions.

- (2) Silicon operating life design goal is 10 years at 105°C junction temperature (does not include package interconnect life).

- (3) The predicted operating lifetime vs. junction temperature is based on reliability modeling using electromigration as the dominant failure mechanism affecting device wearout for the specific device process and design characteristics.

- (4) This device is qualified for 1000 hours of continuous operation at maximum rated temperature.

#### Figure 1. Electromigration Fail Mode Derating Chart

TEXAS INSTRUMENTS

www.ti.com.cn

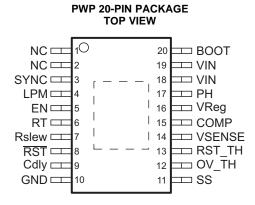

#### **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| PIN    |     |     | DESCRIPTION                                                                                                                                                                    |  |  |

|--------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO. | I/O | DESCRIPTION                                                                                                                                                                    |  |  |

| NC     | 1   | NC  | Connect to ground                                                                                                                                                              |  |  |

| NC     | 2   | NC  | Connect to ground                                                                                                                                                              |  |  |

| SYNC   | 3   | I   | External synchronization clock input to override the internal oscillator clock. An internal pull down resistor of $62k\Omega$ (typical) is connected to the ground.            |  |  |

| LPM    | 4   | I   | Low-power mode control using digital input signal. An internal pull down resistor of $62k\Omega$ (typical) is connected to the ground.                                         |  |  |

| EN     | 5   | I   | Enable pin, internally pulled up. Must be externally pulled up or down to enable/disable the device.                                                                           |  |  |

| RT     | 6   | 0   | External resistor to ground to program the internal oscillator frequency.                                                                                                      |  |  |

| Rslew  | 7   | 0   | External resistor to ground to control the slew rate of internal switching FET.                                                                                                |  |  |

| RST    | 8   | 0   | Active low, open drain reset output connected to external bias voltage through a resistor, asserted high after the device starts regulating.                                   |  |  |

| Cdly   | 9   | 0   | External capacitor to ground to program power on reset delay.                                                                                                                  |  |  |

| GND    | 10  | 0   | Ground pin, must be electrically connected to the exposed pad on the PCB for proper thermal performance.                                                                       |  |  |

| SS     | 11  | 0   | External capacitor to ground to program soft start time.                                                                                                                       |  |  |

| OV_TH  | 12  | I   | Sense input for overvoltage detection on regulated output, an external resisitor network is connected between VReg and ground to program the overvoltage threshold.            |  |  |

| RST_TH | 13  | I   | Sense input for overvoltage detection on regulated output, an external resisitor network is connected between VReg and ground to program the reset and undervoltage threshold. |  |  |

| VSENSE | 14  | I   | Inverting node of error amplifier for voltage mode control                                                                                                                     |  |  |

| COMP   | 15  | 0   | Error amplifier output to connect external compensation components.                                                                                                            |  |  |

| VReg   | 16  | I   | Internal low-side FET to load output during startup or limit overshoot.                                                                                                        |  |  |

| PH     | 17  | 0   | Source of the internal switching FET                                                                                                                                           |  |  |

| VIN    | 18  | I   | Unregulated input voltage. Pin 18 and pin 19 must be connected externally.                                                                                                     |  |  |

| VIN    | 19  | I   | Unregulated input voltage. Pin 18 and pin 19 must be connected externally.                                                                                                     |  |  |

| BOOT   | 20  | 0   | External bootstrap capacitor to PH to drive the gate of the internal switching FET.                                                                                            |  |  |

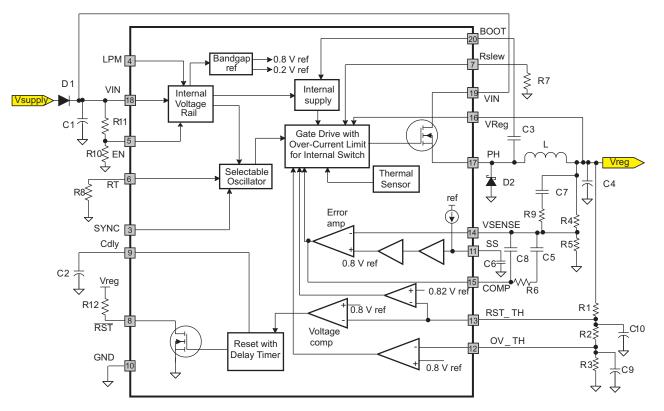

#### FUNCTIONAL BLOCK DIAGRAM

TEXAS INSTRUMENTS

www.ti.com.cn

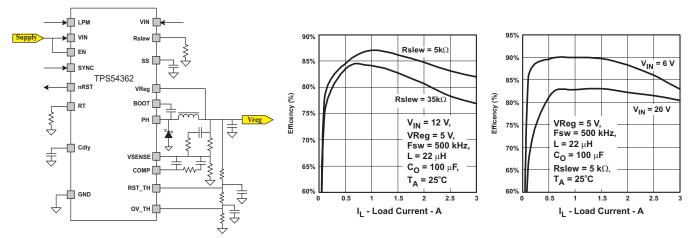

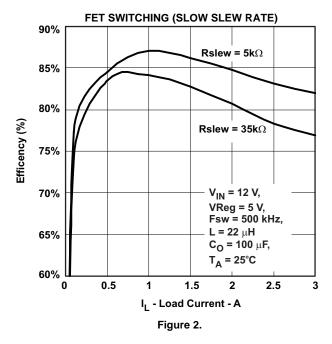

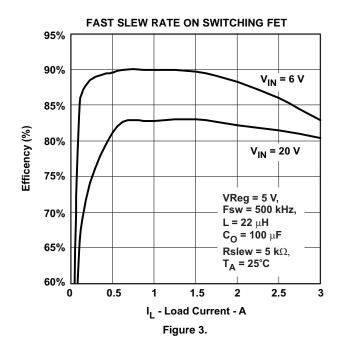

## **TYPICAL CHARACTERISTICS**

#### Efficiency Data of Power Supply

Figure 5.

TPS54362-HT ZHCSA98-SEPTEMBER 2012

www.ti.com.cn

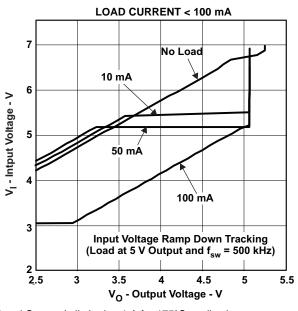

#### TYPICAL CHARACTERISTICS (continued) OUTPUT VOLTAGE TRACKING

#### NOTE

Tracking: The input voltage at which the output voltage drops approximately -0.7 V of the regulated voltage or for low input voltages (tracking function) over the load range.

Start: The input voltage required to achieve the 5V regulation on power up with the stated load currents.

Figure 11.

**TYPICAL CHARACTERISTICS (continued)**

**TPS54362-HT** ZHCSA98-SEPTEMBER 2012

175

G009

www.ti.com.cn

$V_1 = 24 V$

**ISTRUMENTS**

EXAS

Figure 12.

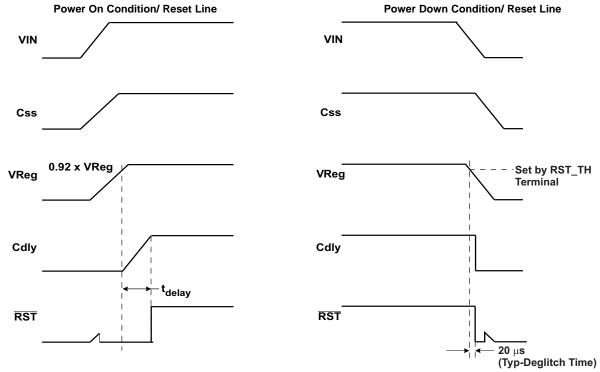

#### OVERVIEW

The TPS54362 is a 60V, 1A dc/dc step down (buck) converter using voltage-control mode scheme. The device features supervisory function for power-on-rest during system power on. Once the output voltage has exceeded the threshold set by RST\_TH, a delay of 1ms/nF (based on capacitor value on RSTDLY terminal) is invoked before RST line is released high. Conversely on power down, once the output voltage falls below the same set threshold, the RST is pulled low only after a de-glitch filter of approximately 20µs (typ) expires. This is implemented to prevent RST from being triggered due to fast transient line noise on the output supply.

An overvoltage monitor function, is used to limit output voltage to the threshold set by OV\_TH. Both the RST\_TH and OV\_TH monitoring voltages are set to be a pre-scale of the output voltage, and thresholds based on the internal bias voltages of the voltage comparators (0.8V typical).

Detection of undervoltage on the output is based on the RST\_TH setting and will invoke RST line to be asserted low. Detection of over-voltage on the output is based on the OV\_TH setting and will NOT invoke the RST line to be asserted low. However, the internal switch is commanded to turn OFF.

In systems where power consumption is critical, low power mode is implemented to reduce the non-switching quiescent current during light load conditions. The PFM operation is determined when the system enters discontinuous current mode (DCM) for at least 100µs. The operation of when the device enters discontinuous mode is dependent on the selection of external components.

#### DETAILED DESCRIPTION

The TPS54362 is a DC/DC Converter using a voltage-control mode scheme with an input voltage feed-forward technique. The device can be programmed for a range of output voltages with a wide input voltage range. Below are details with regard to the pin functionality.

#### INPUT VOLTAGE

The VIN pin is the input power source for the TPS54362. This pin must be externally protected against voltage level greater than 60V and reverse battery. In Buck Mode the input current drawn from this pin is pulsed, with fast rise and fall times. Therefore, this input line requires a filter capacitor to minimize noise. Additionally, for EMI considerations, an input filter inductor may also be required.

#### FUNCTION MODE

| FUNCTION | OPERATING VOLTAGE<br>RANGE | OUTPUT CURRENT CAPABILITY                                                                                                        | COMMENTS                                                                                                                                                                   |

|----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Buck     | 3.6V to 48V                | VReg = 0.9V to 18V and $I_{Load}$ Up to 1A;<br>however, at higher output power the part<br>is derated for max temperature rating | Optimum performance: VIN/VReg ratios<br>should always be set such that min required<br>duty cycle pulse (ton min) >150ns. The min off<br>time is 250ns for ALL conditions. |

#### **OUTPUT VOLTAGE VReg**

The output voltage VReg is generated by the converter supplied from the battery voltage VIN and the external components (L, C). The output is sensed through an external resistor divider and compared with an internal reference voltage.

The value of the adjustable output voltage in Buck Mode is selectable between 0.9V and 18V by choosing the external resistors, according to the relationship:

$VReg = V_{ref} (1 + R4/R5)$

(1)

(2)

Where R5 and R4 are feedback resistors.

$V_{ref} = 0.8V$  (typical)

The internal reference voltage has a  $\pm 1.5\%$  tolerance. The overall output voltage tolerance will be dependent on the external feedback resistors. To determine the overall output voltage tolerance, use the following relationship:

$$tol_{VReg} = tol_{Vref} + (R4/(R4 + R5)) \times (tol_{R4} + tol_{R5})$$

Where R4 and R5 are feedback resistors.

$V_{ref} = 0.8V$  (typical)

The VReg pin is also internally connected to a load of  $100\Omega$ , which is turned ON in the following conditions:

- During startup conditions, when the device is powered up with no-load, or whenever EN is toggled, the internal load connected to VReg pin is turned ON for about 100 µs to charge the bootstrap capacitor to provide gate drive voltage to the switching transistor.

- During normal operating conditions, when the regulated output voltage exceeds the overvoltage threshold (preset by external resisitors R1, R2, and R3), the internal load is turned ON, and this pin is pulled down to bring the regulated output voltage down.

Typically an output capacitor within the range of 10-400µF is used. This terminal will have a filter capacitor with low ESR characteristics in order to minimize output ripple voltage.

#### **OSCILLATOR FREQUENCY: (RT)**

Oscillator frequency is selectable by means of a resistor placed at the RT pin. The switching frequency (Fsw) can be set in the range 200 kHz – 2200 kHz. In addition, the switching frequency can be imposed externally by a clock signal (Fext) at the SYNC pin with Fsw < Fext< 2xFsw. In this case the external clock overrides the switching frequency determined by the RT pin and the internal oscillator is clocked by the external synchronization clock.

Figure 14. Switching Frequency vs Resistor Value

#### SYNCHRONIZATION (SYNC)

This is an external input signal to synchronize the switching frequency using an external clock signal. The synchronization input will over-ride the internally fixed oscillator signal. The synchronization signal has to be valid for approximately 2 clock cycles (pulses) before the transition is made for synchronization with the external frequency input. If the external clock input does NOT transition low or high for  $32\mu$ S (typ), the system will default to the internal clock set by the RT pin. The SYNC input clock can have a maximum frequency of 2X the programmed clock frequency up to a maximum value of 2.2MHz

#### ENABLE / SHUTDOWN:(EN)

The Enable pin provides electrical on/off control of the regulator. Once the Enable pin voltage exceeds the threshold voltage, the regulator starts operation and the internal soft start begins to ramp. If the Enable pin voltage is pulled below the threshold voltage, the regulator stops switching and the internal soft start resets. Connecting the pin to ground or to any voltage less than 0.7V disables the regulator and activate the shutdown mode. This pin must have an external pull up or pull down to change the state of the device.

Copyright © 2012, Texas Instruments Incorporated

## **RESET DELAY (Cdly)**

The Reset delay pin sets the desired delay time to assert the RESET pin high after the supply has exceeded the programmed VReg\_RST voltage. The delay may be programmed in the range of 2.2ms to 200ms using capacitors in the range of 2.2nF to 200nF. The delay time is calculated using the following equation:  $PORdly = 1ms / nF \times C$ , Where C = capacitor on Cdly pin (3)

#### **RESET PIN (nRST)**

The RESET pin is an open-drain output. The power-on reset output is asserted low until the output voltage exceeds the programmed VReg\_RST voltage threshold and the reset delay timer has expired. Additionally, whenever the ENABLE pin is low or open, RESET is immediately asserted low regardless of the output voltage. There is a reset filter timer to prevent reset being invoked due to short negative transients on the output line.

#### **BOOST CAPACITOR (BOOT)**

This capacitor provides the gate drive voltage for the Internal MOSFET switch. X7R or X5R grade dielectrics are recommended due to their stable values over temperature. Boost cap may need to be tweaked lower for low Vreg and/or high frequencies applications. The cap may need to be tweaked higher for high Vreg and/or low frequencies applications. (e.g. 100nF for 500kHz/5V and 220n for 500kHz/8V.)

#### SOFT START (SS)

On powerup or after a short circuit event , the following conditions are recommended:

- 1. VIN VReg > 2.5V

- 2. Load current < 1A, until  $\overline{RST}$  goes high.

- 3. In discontinuous mode or LPM (i.e., light loads), in addition to 1), Vreg < 5.5V also applies.

- 4. Equation 4 should be satisfied. This condition also applies when there is a short circuit on the output.

$$\frac{1.55 \times \text{Css}}{50 \times 10^{-6}} < \frac{30 \times 10^{-6}}{\text{D} \times \text{I}_{\text{LOAD}}} \times \sqrt{\frac{\text{C}_{\text{O}}}{\text{L}}}$$

(4)

Where:

$D = V_O/V_{IN}$  duty cycle.

(5)

TPS54362-HT

ZHCSA98-SEPTEMBER 2012

Css = 1 nF to 220 nF, providing the above equations are satisfied.

L is inductance of inductor.

## LOW POWER MODE (LPM)

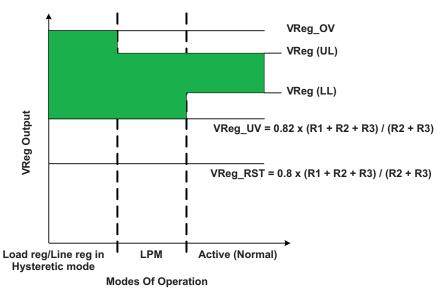

The TPS54362 enters automatically low power mode once the regulation goes into discontinuous mode. The internal control circuitry for any transition from Low Power Mode to High Power Mode occurs within 5 $\mu$ s (typ). In low power mode, the converter operates as a hysteretic controller with the threshold limits set by VReg\_UV = 0.82 x (R1 + R2 + R3 / (R2 + R3), for the lower limit and ~VReg for the upper limit. To ensure tight regulation in the low power mode, R2 and R3 values are set accordingly.

The device operates with both automatic and digital controlled low power mode. The digital low power mode can over-ride the automatic low power mode function by applying the appropriate signal on the LPM terminal. The part goes into active or normal mode for at least 100µs, whenever RST\_TH or VREG\_UV is tripped. In active mode or normal mode, ALL blocks including OV function are enabled.

In LPM mode, OV function is disabled.

Active or Normal Mode: When part is in DCM with LPM=High or in CCM with LPM=High or Low LPM: When part is in DCM with LPM = Low

#### Automatic and Digital

LPM high: device forced normal mode, fixed frequency, even at light load current (part will do pulse skipping to keep output voltage in regulation at light loads)

LPM low or open: device will automatically change between normal and low power mode dependent on load current

#### BUCK MODE LOW POWER MODE OPERATION

When operating in low power mode (Buck reg), and if the output is shorted to ground, a reset is asserted.

The low power mode operation is initiated once the converter enters discontinuous mode of operation.

#### **EXTERNAL LPM OPERATION**

The low power mode (LPM) is active low, if there is an open on this terminal the IC enters the low power mode (internal pull down).

To allow low power mode operation, the load current has to be low and the LPM terminal is set to ground.

To inhibit low power mode, the microcontroller has to drive the terminal high, and the converter is not in discontinuous mode of operation.

Part can ONLY power-up in LPM/DCM if, VReg < 5.5V AND VIN-VReg > 2.5V.

In active mode. the part powers-up when VIN > 3.6V (min).

Note: In LPM, the OV\_TH circuit is not enabled.

Active or Normal Mode: When the device is in CCM or DCM with LPM = High

LPM: When the device is in DCM with LPM = Low

#### SHORT CIRCUIT PROTECTION

The TPS54362 features an output short-circuit protection. Short-circuit conditions are detected by monitoring the RST\_TH, and when the voltage on this node drops below 0.2V, the switching frequency is decreased and current limit is folded back to protect the device. The switching frequency is fold back to approximately 25kHz and the current limit is reduced to 30% of the current limit typical value.

#### **OVERCURRENT PROTECTION**

Overcurrent protection is implemented by sensing the current through the NMOS switch FET. The sensed current is then compared to a current reference level representing the overcurrent threshold limit. If the sensed current exceeds the overcurrent threshold limit, the overcurrent indicator is set true. The system will ignore the overcurrent indicator for the leading edge blanking time at the beginning of each cycle to avoid any turn-on noise glitches.

Once overcurrent indicator is set true, overcurrent protection is triggered. The MOSFET is turned off for the rest of the cycle after a propagation delay. The overcurrent protection scheme is called cycle-by-cycle current limiting. If the sensed current continues to increase during cycle-by-cycle current limiting, the temperature of part will start rising, the TSD will kick in and shut down switching until part cools down.

#### **SLEW RATE CONTROL (Rslew)**

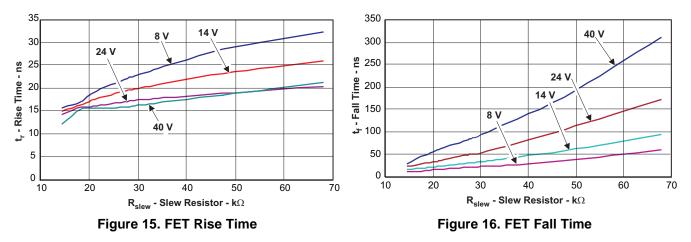

This pin controls the switching slew rate of the internal power NMOS. The slew rate will be set by an external resistor with a slew rate range shown below for rise and fall times. The range of rise time  $t_r = 15$ ns to 35ns, and fall time  $t_f = 15$ ns to 200ns, with Rslew range of 10k to 50k (see plots below).

#### **REGULATION VOLTAGE (VSENSE)**

This pin is used to program the regulated output voltage based on a resistor feedback network monitoring the  $V_0$  output voltage. The selected ratio of R4 to R5 will set the VReg voltage.

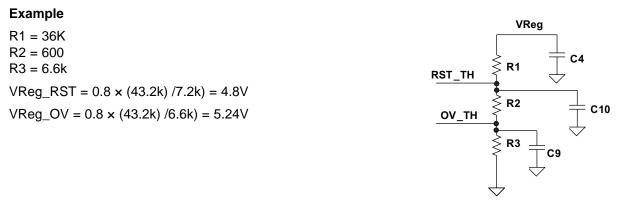

#### **RESET THRESHOLD (RST\_TH)**

This pin is programmable for setting the output accuracy for the low power mode (LPM) to set the undervoltage monitoring of the regulated output voltage (VReg\_UV), and the voltage to initiate a rest output signal (VReg\_RST). The resistor combination of R1 to R3 is used to program the threshold for detection of undervoltage. Voltage bias on R2 + R3 sets the Reset threshold.

Undervoltage for transient and Low Power Mode Operation:

$VReg_UV = 0.82V \times (R1 + R2 + R3 / (R2 + R3))$ (6) Reset Threshold = VReg\_RST = 0.8V × (R1 + R2 + R3 / (R2 + R3)) (7)

Recommended range: 70% to 92% of the regulation voltage.

#### OVERVOLTAGE SUPERVISOR for V<sub>Reg</sub> (OV\_TH)

This pin is programmable to set the overvoltage monitoring of the regulated output voltage. The resistor combination of R1 to R3 is used to program the threshold for detection of overvoltage. The bias voltage of R3 sets the OV threshold and the output voltage accuracy in hysteretic mode during transient events.

Overvoltage ref =  $VReg_OV = 0.8V \times (R1 + R2 + R3) / (R3)$ ,

Recommended range: 106% to 110% of the regulation voltage

#### NOISE FILTER ON RST\_TH AND OV\_TH TERMINALS

There is some noise sensitivity on the RST\_TH and OV\_TH pins and capacitance is added to filter this noise. The noise is more pronounced with fast falling edges on the PH pin. So the smaller the Rslew resistor (minimum recommended value is  $10k\Omega$ ) the more capacitance may be required on RST\_TH and OV\_TH. Users should use the smallest capacitance necessary, because larger values will increase the loop response time and degrade short circuit protection and transient response. The upper limit is determined by the 2µs maximum time constant seen on the OVTH/RSTTH when VReg = 0 V (i.e. [R2 + R3]x[C9 + C10] < 2µs). The noise in the RST\_TH / OV\_TH resistor chain may change with PCB layout or application set-up, so the RST\_TH and/or the OVTH capacitor may not be needed in all applications. Users can place the footprint and only populate it, if necessary.

Typical cap values for RST\_TH/OV\_TH caps are between 10 pf to 100 pf range for total resistance on RSTH/OVTH divider of < 200 k $\Omega$ .

#### OUTPUT TOLERANCES BASED ON MODES OF OPERATION

(8)

TEXAS INSTRUMENTS

## TPS54362-HT

ZHCSA98-SEPTEMBER 2012

www.ti.com.cn

| Mode Of Operation | V <sub>O</sub> - Lower Limit     | V <sub>O</sub> – Upper limit | Comments                    |

|-------------------|----------------------------------|------------------------------|-----------------------------|

| Hysteretic Mode   | 0.82V × (R1 + R2 + R3)/(R2 + R3) | 0.8V × (R1+R2+R3)/(R3)       | Min to max ripple on output |

| Low power Mode    | 0.82V × (R1 + R2 + R3)/(R2 + R3) | VReg + tol <sub>VReg</sub>   | Min to max ripple on output |

| Active (Normal)   | VReg – tol <sub>VReg</sub>       | VReg + tol <sub>VReg</sub>   | Min to max ripple on output |

| Supervisor Thresholds | V <sub>O</sub> - Typical value  | Tolerance                                                                                                               | Comments                      |

|-----------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Overvoltage           | 0.8V × (R1 + R2 + R3)/(R3)      | $\pm$ (tol <sub>Vref</sub> + (R1 + R2/[R1 + R2 + R3]) ×<br>(tol <sub>R1</sub> + tol <sub>R2</sub> + tol <sub>R3</sub> ) | Overvoltage threshold setting |

| Reset                 | 0.8V × (R1 + R2 + R3)/(R2 + R3) | ± (tol <sub>Vref</sub> + (R1/[R1 + R2 + R3]) ×<br>(tol <sub>R1</sub> + tol <sub>R2</sub> + tol <sub>R3</sub> )          | Reset threshold setting       |

#### Load reg/Line reg in Hysteretic Mode

This mode of operation is when a load or line transient step occurs in the application. The converter will go into a hysteretic mode of operation until the error amplifier stabilizes and controls the output regulation to a tighter output tolerance. During the load step the regulator upper threshold is set by the VReg\_OV and the lower threshold is set by the VReg\_UV limit.

The converter enters this mode of operation during load or line transient events if the main control loop cannot respond to regulate within the specified tolerances. The regulator exits this mode once the main control loop responds.

#### Internal Undervoltage Lock Out (UVLO)

The IC is enabled on power up once the internal bandgap and bias currents are stabile, this is typically at  $V_1 = 3.4V$  (min). On power down, the internal circuitry is disabled at  $V_1 = 2.6V$  (max).

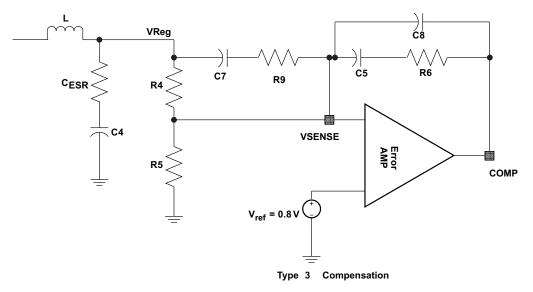

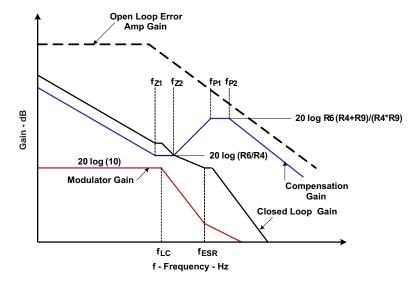

#### **Loop Control Frequency Compensation**

Figure 17. Type 3 Compensation

#### Type III Compensation

fc = fsw  $\times$  0.1 (the cut off frequency, when the gain is 1 is called the unity gain frequency).

The fc is typically 1/5 to 1/10 of the switching frequency, double pole frequency response due to the LC output filter

The modulator break frequencies as a function of the output LC filter is derived from Equation 9 and Equation 10. The LC output filter gives a "Double Pole" which has a –180 degree phase shift

$$f_{LC} = \frac{1}{2\pi \left( LC_{O} \right)^{1/2}}$$

(9)

The ESR of the output capacitor C gives a "ZERO" that has a 90 degree phase shift

$$f_{ESR} = \frac{1}{(2\pi C_0 \times ESR)}$$

(10)

$$Vreg = Vref \times \frac{(R4 + R5)}{R5}$$

(11)

$$\frac{Vreg}{0.8V} = \frac{(R4 + R5)}{R5}$$

(12)

The VIN/Vr modulator gain is about 10 for 8V<VIN<50V. Vr is fixed at 1V for VIN<8V and 5V for VIN>48V Note that the VIN/Vr gain (Amod) is not precise and has a tolerance of about 20%.

$$Vramp = \frac{VIN}{10}$$

$$Gain(dB) = 20 \times log\left(\frac{VIN}{Vramp}\right)$$

(13)

$Gain = 20 \times Log \ 10 = 20 \ dB$

$$fp1 = \frac{(C5 + C8)}{2\pi \times R6 \times (C5 \times C8)}$$

(14)

$$fn2 = \frac{1}{1}$$

$$\frac{1}{2\pi} \times R9 \times C7$$

(15)

$$fz1 = \frac{1}{2\pi \times R6 \times C5}$$

(16)

$$\frac{172}{2\pi \times (R4 + R9) \times C7}$$

(17)

#### **Bode Plot of Converter Gain**

(18)

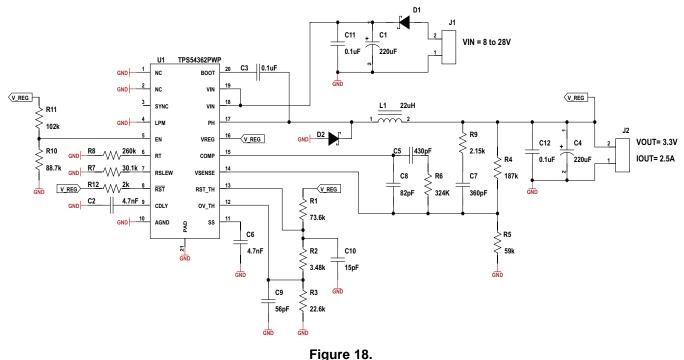

## **APPLICATION INFORMATION**

The following guidelines are recommended for PCB layout of the TPS54362 device.

| Input Voltage, V <sub>I</sub>               | 8V to 28V              |

|---------------------------------------------|------------------------|

| Output Voltage, V <sub>O</sub>              | 3.3V ± 2%              |

| Maximum Output Current, I <sub>O-max</sub>  | 1.0A                   |

| Transient Response 0.25A to 2.25A load step | $\Delta V_{O} = 5\%$   |

| Reset Threshold                             | 92% of Output Voltage  |

| Overvoltage Threshold                       | 106% of Output Voltage |

| Undervoltage Threshold                      | 95% of Output Voltage  |

#### SELECTING THE SWITCHING FREQUENCY

The user selects the switching frequency based on the minimum on-time of the internal power switch, the maximum input voltage and the minimum output voltage and the frequency shift limitations. Equation 18 must be used to find the maximum frequency for the regulator. The value of the resistor to set on the RT terminal to set this frequency can be extrapolated from Figure 18.

$$fsw-\max = \frac{\left(\frac{V_{O-\min}}{V_{I-\max}}\right)}{t_{on-\min}}$$

(Hz)

ton-min = 150ns from the DC Electrical Characteristics

fsw-max = 770kHz

Since the oscillator can vary 10%, decrease the frequency by 10%. Further, to keep the switching frequency outside the AM band, fsw can be selected as 400kHz.

#### Output Inductor Selection $(L_0)$

The minimum inductor value is calculated using Equation 20.

The KIND is the coefficient that represents the amount of inductor ripple current relative to the maximum output current, using equation 19 the ripple is calculated.

The inductor ripple current is filtered by the output capacitor and so the typical range of this ripple current is in the range of  $K_{IND} = 0.2$  to 0.3, depending on the ESR and the ripple current rating of the output capacitor. The minimum inductor value calculated is 14.5µH, choose inductor  $\approx$  22µH.

$$I_{\text{Ripple}} = K_{\text{IND}} \times I_{\text{O}}$$

(19)

$I_{Ripple} = 0.2 \times 2.5 = 0.5A$  (peak-to-peak)

Calculate inductor L:

$$L_{O-min} = \frac{(V_{I-max} - V_O) \times V_O}{f_{SW} \times I_{Ripple} \times V_{I-max}}$$

(Henries) (20)

Where,  $f_{SW}$  is the regulator's switching frequency.

$I_{Ripple}$  = Allowable ripple current in the inductor, typically 20% of max  $I_{O}$

The RMS and peak current flowing in Inductor is:

$$I_{L,RMS} = \sqrt{(I_O)^2 + \frac{(I_{Ripple})^2}{12}}$$

(Amps) (21)

Inductor peak current:

$$I_{L,pk} = I_{O} + \frac{I_{Ripple}}{2} \quad (Amps)$$

(22)

#### Output Capacitor ( $C_0$ )

The selection of the output capacitor will determine several parameters in the operation of the converter, the modulator pole, voltage droop on the out capacitor and the output ripple.

During a load step from no load to full load or changes in the input voltage, the output capacitor must hold up the output voltage above a certain level for a specified time and NOT issue a reset, until the main regulator control loop responds to the change. The minimum output capacitance required to allow sufficient droop on the output voltage with issuing a reset is determined by Equation 24.

The capacitance value determines the modulator pole and the roll off frequency due to the LC output filter double pole - Equation 9.

The output ripple voltage is a product of the output capacitor ESR and ripple current – Equation 26.

Using Equation 23, the minimum capacitance needed to maintain desired output voltage during high to low load transition and prevent over shoot is 157µF.

$$C_{O} = \frac{L \times ((I_{O-max})^{2} - (I_{O-min})^{2})}{(V_{O-max})^{2} - (V_{O-min})^{2}}$$

(Farads)

$I_{O}$  - max, is max output current

$I_{O}$  - min is min output current

The difference between the output current max to min is the worst case load step in the system.

Vo - max is max tolerance of regulated output voltage

$V_{O}$  - min is the min tolerance of regulated output voltage

Minimum Capacitance needed for transient load response, using Equation 24, yields 53µF.

$$C_{O} > \frac{2 \times \Delta I_{O}}{f_{SW} \times \Delta V_{O}}$$

(Farads) (24)

23

**TPS54362-HT** <u>ZHCSA98 – SEPTEMBER 2012</u>

(25)

Minimum Capacitance needed for output voltage ripple specification, using Equation 25, yields 1.18µF.

$$C_{O} > \frac{1}{8 \times fsw} \times \frac{1}{\left(\frac{V_{O-Ripple}}{I_{Ripple}}\right)}$$

(Farads)

The most critical condition based on the calculations above indicates that the output capacitance has to be a minimum of 157µF to keep the output voltage in regulation during load transients.

Additional capacitance de-ratings for temperature, aging and dc bias has to be factored, and so a value of  $220\mu$ F with ESR calculated using Equation 26 of less than  $100m\Omega$  should be used on the output stage.

Maximum ESR of the out capacitor based on output ripple voltage specification.

$$R_{ESR} < \frac{V_{O-Ripple}}{I_{Ripple}}$$

(Ohms) (26)

Output capacitor root mean square (RMS) ripple current. This is to prevent excess heating or failure due to high ripple currents. This parameter is sometimes specified by the manufacturers.

$$I_{O_{RMS}} = \frac{V_O \times (V_{I_{max}} - V_O)}{\sqrt{12} \times V_{I_{max}} \times L_O \times f_{SW}}$$

(Apms) (27)

#### FLYBACK SCHOTTKY DIODE

٠,

The TPS54362 requires an external Schottky diode connected between the PH and power ground termination. The absolute voltage at PH pin should not go beyond the values mentioned in Absolute Maximum Ratings table on page 2 of this document. The schottky diode conducts the output current during the off state of the internal power switch. This schottky diode must have a reverse breakdown higher then the maximum input voltage of the application. A schottky diode is selected for its lower forward voltage. The schottky diode is selected based on the appropriate power rating, which factors in the DC conduction losses and the AC losses due to the high switching frequencies; this is determined by Equation 28.

$$\mathsf{P}_{\mathsf{diode}} = \left(\frac{\left(\mathsf{V}_{\mathsf{I\_max}} - \mathsf{V}_{\mathsf{O}}\right) \times \mathsf{I}_{\mathsf{O}} \times \mathsf{V}_{fd}}{\mathsf{V}_{\mathsf{I\_max}}}\right) + \left(\frac{\left(\mathsf{V}_{\mathsf{I}} - \mathsf{V}_{fd}\right)^2 \times fsw \times \mathsf{C}_{\mathsf{J}}}{2}\right) (\mathsf{Watts})$$

(28)

Where:

V<sub>fd</sub> = forward conducting voltage of Schottky diode

$C_i$  = junction capacitance of the Schottky diode

The recommended part numbers are PDS360 and SBR8U60P5.

#### INPUT CAPACITOR, C<sub>I</sub>

The requires an input ceramic de-coupling capacitor type X5R or X7R and bulk capacitance to minimize input ripple voltage. The dc voltage rating of this input capacitance must be greater than the maximum input voltage. The capacitor must have an input ripple current rating higher than the maximum input ripple current of the converter for the application; this is determined by Equation 29.

The input capacitors for power regulators are chosen to have reasonable capacitance to volume ratio and fairly stable over temperature. The value of the input capacitance also determines the input ripple voltage of the regulator, shown by Equation 30.

$$I_{L_{RMS}} I_{O} \times \sqrt{\frac{V_{O}}{V_{L_{min}}}} \times \frac{(V_{L_{min}} - V_{O})}{V_{L_{min}}}$$

(Amps)

$$\Delta V_{I} = \frac{I_{O-max} \times 0.25}{C_{I} \times fsw}$$

(Volts)

(30)

#### OUTPUT VOLTAGE AND FEEDBACK RESISTOR SELECTION

In the design example,  $187k\Omega$  was selected for R4, using Equation 1, R4 is calculated as  $59k\Omega$ . To minimize the effect of leakage current on the VSENSE terminal, the current flowing through the feedback network should be greater than  $5\mu$ A in order to maintain output accuracy. Higher resistor values help improve the converter efficiency at low output currents, but may introduce noise immunity problems.

#### OVERVOLTAGE RESISTOR SELECTION

Using Equation 8, the value of R3 is determined to set the overvoltage threshold at 1.06 × 3.3V. The total resistor network from VReg output to ground is approximately  $100k\Omega$  (this is R1 + R2 +R3). Then R3 is calculated to be 22.87k $\Omega$ . Use the nearest standard value, which is 22.6k $\Omega$ . A noise decoupling capacitor may be required on this terminal to ensure proper operation; the value chosen for this design is 56pF.

#### **RESET THRESHOLD RESISTOR SELECTION**

Then using Equation 7 the value of R2 + R3 is calculated, and then knowing R3 from the OV\_TH setting, R2 is determined. The value of R2 + R3 yielded  $26.35k\Omega$ , which means R2 is approximately  $3.48k\Omega$ . This will set the reset threshold at  $0.92 \times 3.3V$ . A noise decoupling capacitor may be required on this terminal to ensure proper operation; the value chosen for this design is 15pF. R1 is determined to be  $73.6k\Omega$ .

#### LOW POWER MODE THRESHOLD

To obtain an approximation of the output load current at which the converter is operating in discontinuous mode, use Equation 31. The values used in the equation for minimum and maximum input voltage will affect the duty cycle and the overall discontinuous mode load current. With a maximum input voltage of 28V, the output load current for DCM is 165.8mA, and for minimum input voltage of 8V the DCM mode load current is 111.7mA. These are nominal values and other factors are not taken into consideration like external component variations with temperature and aging.

$$I_{L-DISCONT} = I_{L_{LPM}} = \frac{(1 - D) \times V_{O}}{2 \times f_{SW} \times L}$$

(Amperes) (with ±30% hysteresis) (31)

#### UNDERVOLTAGE THRESHOLD FOR LOW POWER MODE AND LOAD TRANSIENT OPERATION

This threshold is set above the reset threshold to ensure the regulator operates within the specified tolerances during output load transient of low load to high load and during discontinuous conduction mode. Using Equation 6 the typical voltage threshold is determined.

In this design, the value for this threshold is  $0.95 \times 3.3V$ .

#### SOFTSTART CAPACITOR

The soft start capacitor determines the minimum time to reach the desired output voltage during a power up cycle. This is useful when a load requires a controlled voltage slew rate, and helps to limit the current draw from the input voltage supply line. Equation 4 has to be satisfied in addition to the other conditions stated in the soft start section of this document. In this design, a 4.7nF capacitor is required to meet these criteria.

#### **BOOTSTRAP CAPACITOR SELECTION**

A 0.1µF ceramic capacitor must be connected between the PH and BOOT terminals for the converter to operate and regulate the desired output voltage. It is recommended to use a capacitor with X5R or better grade dielectric material, and the voltage rating on this capacitor of at least 25V to allow for derating.

#### COMPENSATION

#### **Guidelines for Compensation Components**

1 2 x π // Co

Make the two zeroes close to the double pole (LC), e.g fz1

$$\approx$$

fz2  $\approx$   $^{2 \times \pi} \sqrt{^{LO}C}$

- 1. Make first zero below the filter double pole (approx 50% to 75% of  $\rm f_{\rm LC})$

- 2. Make second zero at filter double pole (f<sub>LC</sub>)

TEXAS INSTRUMENTS

TPS54362-HT ZHCSA98-SEPTEMBER 2012

www.ti.com.cn

Make the two poles above the cross-over frequency fc,

- 1. Make first pole at the ESR frequency ( $f_{ESR}$ )

- 2. Make the second pole at 0.5 the switching frequency (0.5 × fsw) Select R4 =  $187k\Omega$

$$R5 = \frac{(R4 \times 0.8)}{(V_0 - 0.8)}$$

(32)

$$R5 = \frac{fc \times Vramp \times R4}{Vramp \times R4}$$

$$R6 = \frac{10 \times Vramp \times 104}{(f_{LC} \times VI)}$$

(33)

Calculate C5 based on placing a zero at 50% to 75% of the output filter double pole frequency.

$$C5 = \frac{1}{\pi \times R6 \times f_{LC}}$$

(34)

Calculate C8 by placing the first pole at the ESR zero frequency.

$$C8 = \frac{C5}{(2\pi \times R6 \times C5 \times f_{ESR} - 1)}$$

(35)

Set the second pole at 0.5 the switching frequency and also set the second zero at the output filter double pole frequency.

$$R9 = \frac{R4}{\left(\left(\frac{fsw}{2 \times f_{LC}}\right) - 1\right)}$$

(36)

$$C7 = \frac{1}{\pi \times R9 \times fsw}$$

(37)

#### **Calculate the Loop Compensation**

DC modulator gain (Amod) = 8 /Vr Vr = 0.8 Amod (dB) = 20 log (10) = 20 dB

Output filter due to  $LC_0$  poles and  $C_0$  ESR zeros from Equation 9 and Equation 10.

$f_{LC}$  = 2.3 kHz for  $LC_{O}$  = 22µH,  $C_{O}$  = 220µF  $f_{ESR}$  = 7.23 kHz for  $C_{O}$  = 220µF, ESR = 100m $\Omega$  Choose R4 = 187k $\Omega$

The poles and zeros for a type III network are calculated using equations Equation 32 to Equation 37.

R5 = 59.8k (use standard value 59k) R6 = 326.9k (use standard value 324k) C5 = 425.5pF (use standard value 430pF)

C8 = 79.9pF (use standard value 43pF)

R9 = 2.16k (use standard value 2.15K)

C7 = 367.7pF (use standard value 360pF)

The poles and zeros based on these compensation values can be calculated using Equation 14 to Equation 17.

#### **Power Dissipation**

The power dissipation losses are applicable for continuous conduction mode operation (CCM)

$$\begin{split} P_{CON} &= I_{O}^{2} \times R_{DS(on)} \times \left(\frac{V_{O}}{V_{I}}\right) \mbox{ (Conduction losses)} \end{tabular} \\ P_{SW} &= 1/2 \times V_{I} \times I_{O} \times (t_{r} + t_{f}) \times f_{SW} \mbox{ (Switching losses)} \mbox{ (39)} \\ P_{Gate} &= V_{drive} \times Qg \times \mbox{ fsw (Gate drive losses) where } Qg = 1 \times 10^{-9} \mbox{ (nC)} \mbox{ (40)} \\ P_{IC} &= V_{I} \times Iq \mbox{-normal (Supply losses)} \mbox{ (41)} \\ P_{Total} &= P_{CON} + P_{SW} + P_{Gate} + P_{IC} \mbox{ (Watts)} \mbox{ (42)} \\ re: \end{split}$$

Where:

$V_{O} = \text{Output voltage} \\ V_{I} = \text{Input voltage} \\ I_{O} = \text{Output current} \\ t_{r} = \text{FET switching rise time (tr max = 40ns)} \\ t_{f} = \text{FET switching fall time} \\ V_{drive} = \text{FET gate drive voltage (typically Vdrive = 6V and Vdrive max = 8V)} \\ \text{fsw} = \text{Switching frequency}$

For given operating ambient temperature T<sub>A</sub>

$$T_J = T_{Amb} + Rth \times P_{Total}$$

For a given max junction temperature T<sub>J-Max</sub> = 150°C

$T_{Amb-Max} = T_{J-Max} - Rth \times P_{Total}$

Where:

$\begin{array}{l} \mathsf{P}_{\mathsf{Total}} = \mathsf{Total} \ \mathsf{power} \ \mathsf{dissipation} \ (\mathsf{Watts}) \\ \mathsf{T}_{\mathsf{Amb}} = \mathsf{Ambient} \ \mathsf{Temperature} \ \mathsf{in} \ ^{\mathsf{C}}\mathsf{C} \\ \mathsf{T}_{\mathsf{J}} = \mathsf{Junction} \ \mathsf{Temperature} \ \mathsf{in} \ ^{\mathsf{C}}\mathsf{C} \\ \mathsf{T}_{\mathsf{Amb}\text{-}\mathsf{Max}} = \mathsf{Maximum} \ \mathsf{Ambient} \ \mathsf{Temperature} \ \mathsf{in} \ ^{\mathsf{C}}\mathsf{C} \\ \mathsf{T}_{\mathsf{J}\text{-}\mathsf{Max}} = \mathsf{Maximum} \ \mathsf{junction} \ \mathsf{temperature} \ \mathsf{in} \ ^{\mathsf{C}}\mathsf{C} \\ \mathsf{Rth} = \mathsf{Thermal} \ \mathsf{resistance} \ \mathsf{of} \ \mathsf{package} \ \mathsf{in} \ (^{\mathsf{C}}/\mathsf{W}) \end{array}$

Other factors NOT included in the information above which affect the overall efficiency and power losses are Inductor ac and dc losses.

Trace resistance and losses associated with the copper trace routing connection

Flyback catch diode

The output current rating for the regulator may have to be derated for ambient temperatures above 85°C. The de-rate value will depend on calculated worst case power dissipation and the thermal management implementation in the application.

(43)

(44)

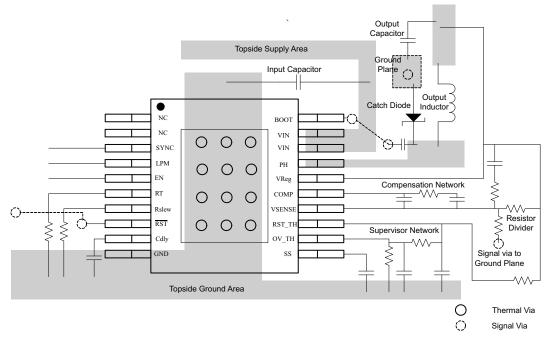

#### LAYOUT

The following guidelines are recommended for PCB layout of the TPS54362 device.

#### INDUCTOR

Use a low EMI inductor with a ferrite type shielded core. Other types of inductors may be used; however, they must be low EMI characteristics and located away from the low power traces and components in the circuit.

#### **INPUT FILTER CAPACITORS**

Input ceramic filter capacitors should be located in the close proximity of the VIN terminal. Surface mount capacitors are recommended to minimize lead length and reduce noise coupling.

#### FEEDBACK

Route the feedback trace such that there is minimum interaction with any noise sources associated with the switching components. Recommended practice is to ensure the inductor is placed away from the feedback trace to prevent EMI noise source.

#### TRACES AND GROUND PLANE

All power (high current) traces should be thick and short as possible. The inductor and output capacitors should be as close to each other as possible. This will reduce EMI radiated by the power traces due to high switching currents.

In a two sided PCB, it is recommended to have ground planes on both sides of the PCB to help reduce noise and ground loop errors. The ground connection for the input and output capacitors and IC ground should be connected to this ground plane.

In a multilayer PCB, the ground plane is used to separate the power plane (high switching currents and components are placed) from the signal plane (where the feedback trace and components are) for improved performance.

Also, arrange the components such that the switching current loops curl in the same direction. Place the high current components such that during conduction the current path is in the same direction. This will prevent magnetic field reversal caused by the traces between the two half cycles, helping to reduce radiated EMI.

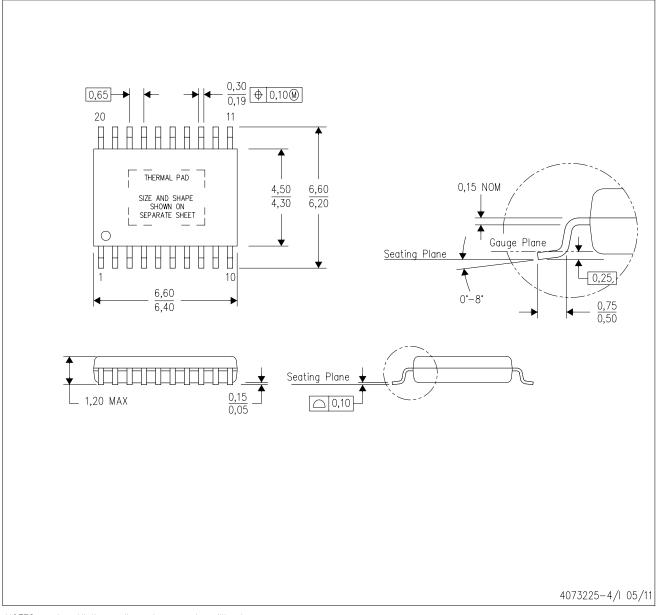

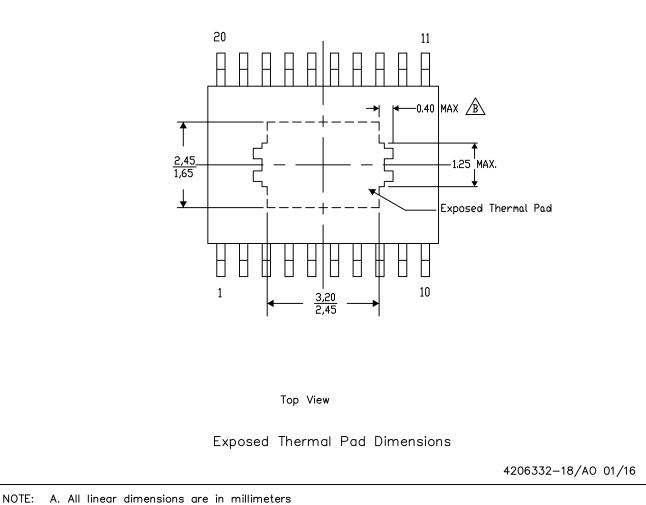

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | e Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|----------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TPS54362HPWP     | ACTIVE        | HTSSOP       | PWP                  | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-4-260C-72 HR   | -55 to 175   | 54362H                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS54362-HT :

www.ti.com

• Automotive : TPS54362-Q1

NOTE: Qualified Version Definitions:

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

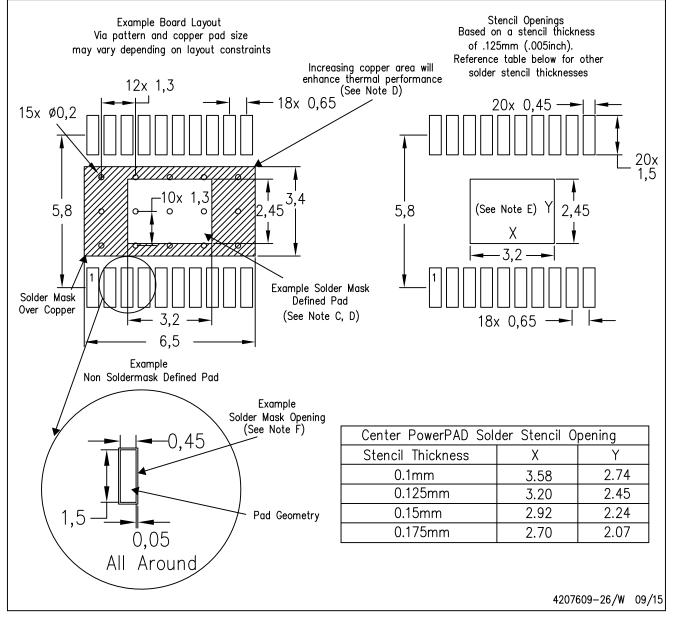

PWP (R-PDSO-G20)

PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

All linear dimensions are in millimeters. NOTES: Α.

- Β. This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side. C.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad D.

- Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions. E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G20) PowerPAD<sup>™</sup> SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION