www.ti.com.cn

# 6.5V 至 28V 输入电压, 5V 固定输出, 2A 输出电流, 带有集成金属氧化物半导体场效应晶体管 (MOSFET) 的非同步降压稳压器

查询样片: TPS5405

## 特性

- 固定 5V 输出

- 6.5V 至 28V 的宽输入电压范围

- 高达 2A 的最大持续输出负载电流

- 脉冲跳跃模式可在轻负载时实现高效率

- 10mA 负载时效率超过 80%

- 由一个外部电阻器设定的可调 50kHz 至 1.1MHz 的开关频率 (将引脚 ROSC 悬空。 将频率设定为 120kHz)

- 峰值电流模式控制

- 逐周期过流保护

- 抗振铃开关节点以减轻电磁干扰 (EMI) 问题

- 外部软启动

- 采用小外形集成电路 (SOIC)8 封装

## 说明

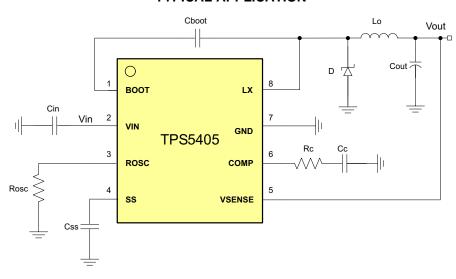

TPS5405 是一款具有宽运行输入电压范围(6.5V 至 28V)的单片非同步降压稳压器。此器件执行内部斜率补偿的电流模式控制来减少组件数量。

TPS5405 还特有一个轻负载脉冲跳跃模式,此特性可在轻负载时减少为系统供电的输入电源的功率损失。

可使用一个外部电阻器将此转换器的开关频率设定在 50kHz 至 1.1MHz 之间。 引入了频率展频操作以减少 EMI。添加了 LX 抗振铃来解决高频 EMI 问题。

具有频率折返功能的逐周期电流限制在过载情况下保护集成电路 (IC)。

## 应用范围

- 9V, 12V 和 24V 分布式电源系统

- 消费类应用,诸如家用电器,机顶盒, CPE 设备, LCD 显示器,外设,和电池充电器

- 工业用和车载娱乐系统电源

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **TYPICAL APPLICATION**

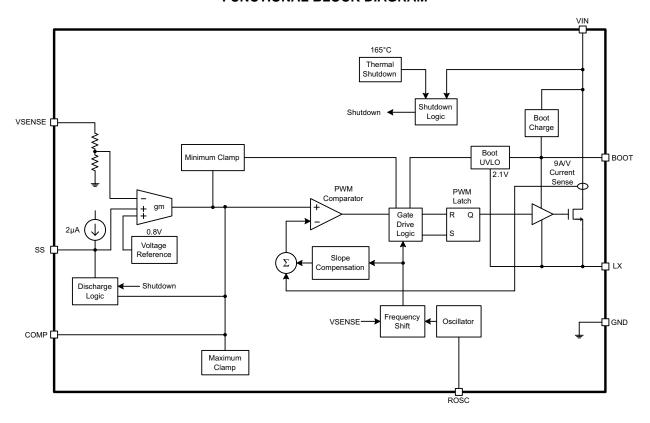

## **FUNCTIONAL BLOCK DIAGRAM**

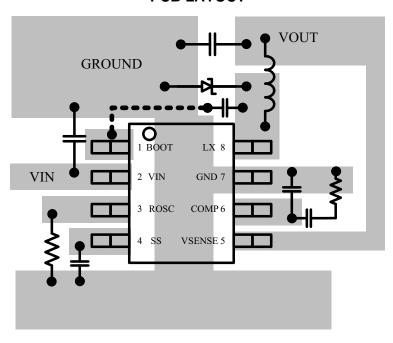

## **PCB LAYOUT**

## ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |  |

|----------------|------------------------|-----------------------|------------------|--|--|

| -40°C to 85°C  | 8-pin SOIC (D)         | TPS5405DR             | T5405            |  |  |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- (2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

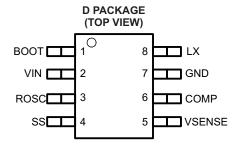

## **PIN OUT**

#### **TERMINAL FUNCTIONS**

| NAME   | NO. | DESCRIPTION                                                                                                                                         |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT   | 1   | A 0.1-µF bootstrap capacitor is required between BOOT and LX.                                                                                       |

| VIN    | 2   | Input supply voltage, 6.5 V to 28 V                                                                                                                 |

| ROSC   | 3   | Switching frequency program pin. Connect a resistor to this pin to set the switching frequency. Leave the pin open for 120-kHz switching frequency. |

| SS     | 4   | Soft start pin. An external capacitor connected to this pin sets the output rise time.                                                              |

| VSENSE | 5   | Output voltage feedback pin                                                                                                                         |

| COMP   | 6   | Error amplifier output and input to the PWM comparator. Connect frequency compensation components to this pin.                                      |

| GND    | 7   | Ground                                                                                                                                              |

| LX     | 8   | Switching node to external inductor                                                                                                                 |

## **ABSOLUTE MAXIMUM RATINGS (1)**

over operating free-air temperature range (unless otherwise noted)

|                  | Voltage range at VIN, LX                                          | -0.3 to 30  | V  |

|------------------|-------------------------------------------------------------------|-------------|----|

|                  | Voltage range at LX (maximum withstand voltage transient < 20 ns) | –5 to 30    | V  |

|                  | Voltage from BOOT to LX                                           | -0.3 to 7   | V  |

|                  | Voltage at VSENSE                                                 | -0.3 to 7   | V  |

|                  | Voltage at SS                                                     | -0.3 to 3   | V  |

|                  | Voltage at ROSC                                                   | -0.3 to 3   | V  |

|                  | Voltage at COMP                                                   | -0.3 to 3   | V  |

|                  | Voltage at GND                                                    | -0.3 to 0.3 | V  |

| TJ               | Operating junction temperature range                              | -40 to 125  | °C |

| T <sub>STG</sub> | Storage temperature range                                         | -55 to 150  | °C |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|       |                         | MIN | NOM MAX | UNIT |

|-------|-------------------------|-----|---------|------|

| VIN   | Input operating voltage | 6.5 | 28      | V    |

| $T_A$ | Ambient temperature     | -40 | 85      | °C   |

#### THERMAL INFORMATION

|                  |                                                             | TPS5405 |       |

|------------------|-------------------------------------------------------------|---------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | D       | UNITS |

|                  |                                                             | 8 PINS  |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (2)                  | 116.7   |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 62.4    |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 57.0    | 9C/M  |

| ΨЈТ              | Junction-to-top characterization parameter <sup>(5)</sup>   | 14.5    | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 56.5    |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | N/A     |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### **ELECTRICAL CHARACTERISTICS**

$T_A = -40$ °C to 125°C,  $V_{IN} = 12$  V (unless otherwise noted)

|                      | PARAMETER                                                  | TEST CONDITIONS                                              | MIN  | TYP   | MAX      | UNIT   |

|----------------------|------------------------------------------------------------|--------------------------------------------------------------|------|-------|----------|--------|

| INPUT SUPP           | PLY                                                        |                                                              |      |       |          |        |

| V <sub>IN</sub>      | Input Voltage range                                        | VIN1 and VIN2                                                | 6.5  |       | 28       | V      |

| IDD <sub>Q_nsw</sub> | Non switching quiescent power supply current               | VFB1 = VFB2 = 900 mV,<br>LOW_P = high                        |      | 100   |          | μΑ     |

| UVLO                 | Vdan.valtana laalvavt                                      | Rising V <sub>IN</sub>                                       |      | 3.5   |          | V      |

| UVLO                 | V <sub>IN</sub> under voltage lockout                      | Hysteresis                                                   |      | 200   |          | mV     |

| FEEDBACK             | AND ERROR AMPLIFIER                                        |                                                              |      |       |          |        |

| V <sub>SENSE</sub>   | Regulated output voltage                                   | V <sub>IN</sub> = 12 V                                       | 4.85 | 5     | 5.15     | V      |

| G <sub>m_EA</sub>    | Error amplifier trans-conductance                          | -2 μA < I <sub>COMP</sub> < 2 μA,<br>V <sub>COMP</sub> = 1 V |      | 92    |          | μs     |

| I <sub>gm</sub>      | Error amplifier source/sink current                        | V <sub>COMP</sub> = 1 V, 100 mV overdrive                    |      | ±7    |          | μΑ     |

| G <sub>m_SRC</sub>   | COMP voltage to inductor current Gm                        | V <sub>IN</sub> = 12 V                                       |      | 9     |          | A/V    |

|                      | AND SOFT-START                                             |                                                              |      |       |          |        |

| I <sub>th</sub>      | Pulse skipping mode switch current threshold               |                                                              |      | 300   |          | mA     |

| I <sub>SS</sub>      | Charge current                                             |                                                              |      | 2     |          | μΑ     |

| OSCILLATO            | R                                                          |                                                              |      |       |          |        |

| f <sub>SW_BK</sub>   | Switching frequency range                                  | Set by external resistor ROSC                                | 50   |       | 1100     | kHz    |

| ı                    | December 1 for successive                                  | ROSC = OPEN                                                  |      | 120   |          | 1.1.1- |

| f <sub>SW</sub>      | Programmable frequency                                     | ROSC = 85.5 kΩ                                               |      | 300   |          | kHz    |

| f <sub>jitter</sub>  | Frequency spread spectrum in percentage of f <sub>SW</sub> | V <sub>IN</sub> = 12 V                                       |      | ±6    |          | %      |

| f <sub>swing</sub>   | Jittering swing frequency in percentage of f <sub>SW</sub> | V <sub>IN</sub> = 12 V                                       |      | 1/512 |          |        |

| t <sub>min_on</sub>  | Minimum on time                                            | V <sub>IN</sub> = 12 V, T <sub>A</sub> = 25°C                |      | 200   |          | ns     |

| D <sub>max</sub>     | Maximum duty ratio                                         | V <sub>IN</sub> = 12 V                                       |      | 93    |          | %      |

| CURRENT L            | IMIT                                                       |                                                              |      |       | ·        |        |

| I <sub>LIMIT</sub>   | Peak inductor current limit                                | V <sub>IN</sub> = 12 V                                       |      | 2.5   |          | Α      |

| MOSFET ON            | I-RESISTANCE                                               |                                                              |      |       |          |        |

| R <sub>dson_HS</sub> | On resistance of high side FET                             | V <sub>IN</sub> = 12 V                                       |      | 120   | 240      | mΩ     |

| THERMAL S            | HUTDOWN                                                    | ·                                                            |      |       | <u>.</u> |        |

| T <sub>TRIP</sub>    | Thermal protection trip point                              | Rising temperature                                           |      | 165   |          | °C     |

## TYPICAL CHARACTERISTICS

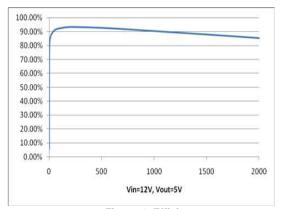

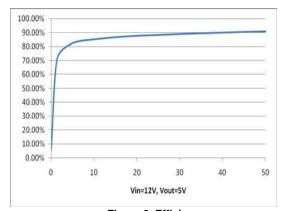

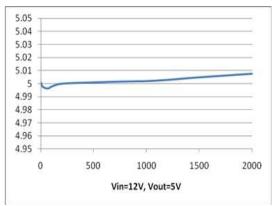

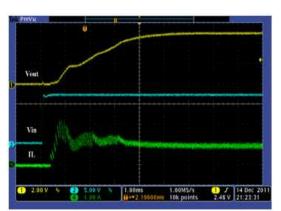

$T_A = 25$ °C,  $V_{IN} = 12$  V,  $f_{SW} = 120$  kHz (unless otherwise noted)

Figure 1. Efficiency V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 5 V

Figure 2. Efficiency V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 5 V

## TYPICAL CHARACTERISTICS (continued)

$T_A = 25$ °C,  $V_{IN} = 12$  V,  $f_{SW} = 120$  kHz (unless otherwise noted)

Figure 3. Load Regulation  $V_{IN} = 12 \text{ V}, V_{OUT} = 5 \text{ V}$

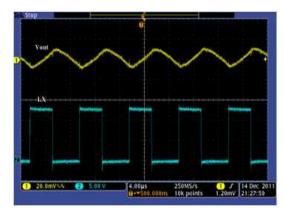

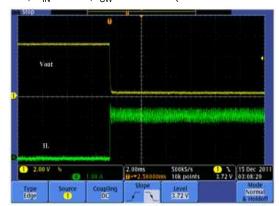

Figure 5. Startup 1-A Preset Loading

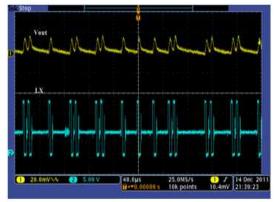

Figure 7. Steady State I<sub>O</sub> = 20 mA

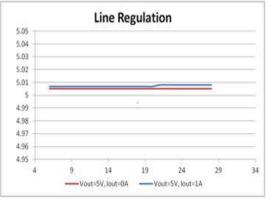

Figure 4. Line Regulation V<sub>OUT</sub> = 5 V

Figure 6. Steady State  $I_0 = 1 A$

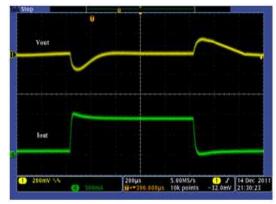

Figure 8. Load Transient  $I_0 = 0.1 A to 1 A$

# **TYPICAL CHARACTERISTICS (continued)**

$T_A = 25$ °C,  $V_{IN} = 12$  V,  $f_{SW} = 120$  kHz (unless otherwise noted)

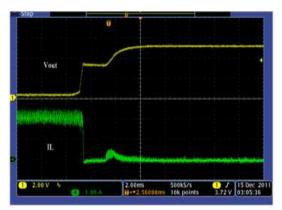

**Figure 9. Short Circuit Protection**

Figure 10. Short Circuit Recovery

#### OVERVIEW

The TPS5405 is a 28-V, 2-A, step-down (buck) converter with an integrated high-side N-channel MOSFET. To improve performance during line and load transients, the device implements a constant frequency, current mode control which reduces output capacitance and simplifies external frequency compensation design.

The TPS5405's switching frequency is adjustable with an external resistor or fixed by connecting the frequency program pin to GND or leaving it unconnected.

The TPS5405 starts switching at  $V_{IN}$  equal to 3.5 V. The operating current is 100  $\mu$ A typically when not switching and under no load. When the device is disabled, the supply current is 1  $\mu$ A typically.

The integrated  $120\text{-m}\Omega$  high-side MOSFET allows for high efficiency power supply designs with continuous output currents up to 2 A.

The TPS5405 reduces the external component count by integrating the boot recharge diode. The bias voltage for the integrated high-side MOSFET is supplied by an external capacitor on the BOOT to PH pins. The boot capacitor voltage is monitored by an UVLO circuit and will turn the high-side MOSFET off when the voltage falls below a preset threshold of 2.1 V typically.

By adding an external capacitor, the slow start time of the TPS5405 can be adjustable which enables flexible output filter selection. To improve the efficiency at light load conditions, the TPS5405 enters a special pulse skipping mode when the peak inductor current drops below 300 mA typically. The frequency foldback reduces the switching frequency during startup and over current conditions to help control the inductor current. The thermal shut down gives the additional protection under fault conditions.

#### **DETAILED DESCRIPTION**

## **Adjustable Frequency PWM Control**

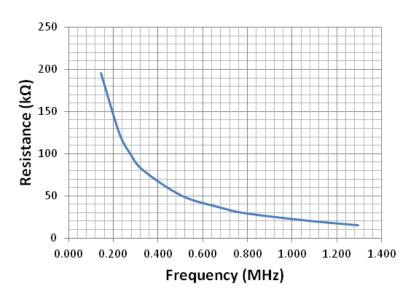

The TPS5405 uses an external resistor to adjust the switching frequency. Connecting the ROSC pin to ground fixes the switching frequency at 70 kHz. Leave this pin open to set 120-kHz switch frequency.

Figure 11. ROSC vs Switching Frequency

$$R_{OSC}(k\Omega) = 21.82 \cdot f_{SW}^{-1.167}$$

(1)

For operation at 300 kHz, an 85.5-k $\Omega$  resistor is required.

## **Pulse Skipping Mode**

The TPS5405 is designed to operate in pulse skipping mode at light load currents to boost light load efficiency. When the peak inductor current is lower than 300 mA typically, the COMP pin voltage falls to 0.5 V typically and the device enters pulse skipping mode. When the device is in pulse skipping mode, the COMP pin voltage is clamped at 0.5 V internally which prevents the high side integrated MOSFET from switching. The peak inductor current must rise above 300 mA for the COMP pin voltage to rise above 0.5 V and exit pulse skipping mode. Since the integrated current comparator catches the peak inductor current only, the average load current entering pulse skipping mode varies with the applications and external output filters.

## Voltage Reference (V<sub>SENSE</sub>)

The voltage reference system produces a ±2% initial accuracy voltage reference (±4% over temperature) by scaling the output of a temperature stable bandgap circuit. The typical voltage reference is designed at 0.8 V.

## **Bootstrap Voltage (BOOT)**

The TPS5405 has an integrated boot regulator and requires a 0.1-µF ceramic capacitor between the BOOT and LX pins to provide the gate drive voltage for the high-side MOSFET. A ceramic capacitor with an X7R or X5R grade dielectric is recommended because of the stable characteristics over temperature and voltage. To improve drop out, the TPS5405 is designed to operate at 100% duty cycle as long as the BOOT to LX pin voltage is greater than 2.1 V typically.

## **Programmable Slow Start Using SS Pin**

It is recommended to program the slow start time externally because no slow start time is implemented internally. The TPS5405 effectively uses the lower voltage of the internal voltage reference or the SS pin voltage as the power supply's reference voltage fed into the error amplifier and will regulate the output accordingly. A capacitor ( $C_{SS}$ ) on the SS pin to ground implements a slow start time. The TPS5405 has an internal pull-up current source of 2  $\mu$ A that charges the external slow start capacitor. The equation for the slow start time (10% to 90%) is shown in Equation 2. The internal  $V_{ref}$  is 0.8 V and the  $I_{SS}$  current is 2  $\mu$ A.

$$t_{ss}(ms) = \frac{C_{ss}(nF) \times V_{ref}(V)}{I_{ss}(\mu A)}$$

(2)

The slow start time should be set between 1 ms to 10 ms to ensure good start-up behavior. The slow start capacitor should be no more than 27 nF.

If during normal operation, the input voltage drops below the VIN UVLO threshold, or a thermal shutdown event occurs, the TPS5405 stops switching.

#### **Error Amplifier**

The TPS5405 has a transconductance amplifier for the error amplifier. The error amplifier compares the VSENSE voltage to the internal effective voltage reference presented at the input of the error amplifier. The transconductance of the error amplifier is 92 µA/V during normal operation. Frequency compensation components are connected between the COMP pin and ground.

#### Slope Compensation

To prevent the sub-harmonic oscillations when operating the device at duty cycles greater than 50%, the TPS5405 adds a built-in slope compensation which is a compensating ramp to the switch current signal.

## **Overcurrent Protection and Frequency Shift**

The TPS5405 implements current mode control that uses the COMP pin voltage to turn off the high-side MOSFET on a cycle by cycle basis. Every cycle the switch current and the COMP pin voltage are compared; when the peak inductor current intersects the COMP pin voltage, the high-side switch is turned off. During overcurrent conditions that pull the output voltage low, the error amplifier responds by driving the COMP pin high, causing the switch current to increase. The COMP pin has a maximum clamp internally, which limits the output current.

www.ti.com.cn

The TPS5405 provides robust protection during short circuits. There is potential for overcurrent runaway in the output inductor during a short circuit at the output. The TPS5405 solves this issue by increasing the off time during short circuit conditions by lowering the switching frequency. The switching frequency is divided by 8, 4, 2, and 1 as the voltage ramps from 0 V to 5V on the VSENSE pin. The relationship between the switching frequency and the VSENSE pin voltage is shown in Table 1.

**Table 1. Switching Frequency Conditions**

| SWITCHING FREQUENCY | VSENSE PIN VOLTAGE                  |

|---------------------|-------------------------------------|

| f <sub>SW</sub>     | V <sub>SENSE</sub> ≥ 3.75 V         |

| f <sub>SW</sub> /2  | 3.75 V > V <sub>SENSE</sub> ≥ 2.5 V |

| f <sub>SW</sub> /4  | 2.5 V > V <sub>SENSE</sub> ≥ 1.25 V |

| f <sub>SW</sub> /8  | 1.25 V > V <sub>SENSE</sub>         |

## **Spread Spectrum**

In order to reduce EMI, TPS5405 introduces frequency spread spectrum. The jittering span is  $\pm 6\%$  of the switching frequency with 1/512 swing frequency.

## **Switching Node Anti-Ringing**

When the non-synchronous buck converter operates in DCM mode, the filter inductor and the parasitic capacitance in the switching node (LX) form an LC resonant circuit; due to its high Q factor, lengthy high frequency oscillation can be observed in the switching node. This ringing could cause radiated EMI issues in some systems. TPS5405 adds an anti-ringing circuit to prevent the ringing from happening, when the inductor current crosses zero and LX starts to climb up, an internal MOSFET between LX and VSENSE is turned on, providing a damping path for the resonant circuit so as to eliminate the ringing.

## **Overvoltage Transient Protection**

The TPS5405 incorporates an overvoltage transient protection (OVTP) circuit to minimize output voltage overshoot when recovering from output fault conditions or strong unload transients. The OVTP circuit includes an overvoltage comparator to compare the VSENSE pin voltage and internal thresholds. When the VSENSE pin voltage goes above  $109\% \times V_{ref}$ , the high-side MOSFET will be forced off. When the VSENSE pin voltage falls below  $107\% \times V_{ref}$ , the high-side MOSFET will be enabled again.

#### **Inductor Selection**

The higher operating frequency allows the use of smaller inductor and capacitor values. A higher frequency generally results in lower efficiency because of switching loss and MOSFET gate charge losses. In addition to this basic trade-off, the effect of the inductor value on ripple current and low current operation must also be considered. The ripple current depends on the inductor value. The inductor ripple current ( $i_L$ ) decreases with higher inductance or higher frequency and increases with higher input voltage ( $V_{IN}$ ). Accepting larger values of  $i_L$  allows the use of low inductances, but results in higher output voltage ripple and greater core losses.

To calculate the value of the output inductor, use Equation 3. LIR is a coefficient that represents inductor peak-to-peak ripple to DC load current. It is recommended to set LIR to  $0.1 \sim 0.3$  for most applications.

Actual core loss of the inductor is independent of core size for a fixed inductor value, but it is very dependent on the inductance value selected. As inductance increases, core losses go down. Unfortunately, increased inductance requires more turns of wire and therefore copper losses will increase. Ferrite designs have very low core loss and are preferred for high switching frequencies, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates hard, which means that inductance collapses abruptly when the peak design current is exceeded. It results in an abrupt increase in inductor ripple current and consequent output voltage ripple. Do not allow the core to saturate. It is important that the RMS current and saturation current ratings are not exceeding the inductor specification. The RMS and peak inductor current can be calculated from Equation 5 and Equation 6.

$$L = \frac{V_{IN} - V_{OUT}}{I_{O} \cdot LIR} \cdot \frac{V_{OUT}}{V_{IN} \cdot fsw}$$

(3)

$$\Delta i_{L} = \frac{V_{IN} - V_{OUT}}{I_{O}} \cdot \frac{V_{OUT}}{V_{IN} \cdot fsw}$$

(4)

$$i_{LRMS} = \sqrt{I_O^2 + \frac{\left(\frac{V_{OUT} \cdot (V_{INmax} - V_{OUT})}{V_{INmax} \cdot L \cdot fsw}\right)^2}{12}}$$

(5)

$$I_{Lpeak} = I_{O} + \frac{\Delta i_{L}}{2} \tag{6}$$

For this design example, use LIR = 0.3 and the inductor is calculated to be 5.40  $\mu$ H with  $V_{IN}$  = 12 V. Choose 4.7  $\mu$ H value for the standard inductor and the peak to peak inductor ripple is about 34% of 1-A DC load current.

## **Output Capacitor Selection**

There are two primary considerations for selecting the value of the output capacitor. The output capacitors are selected to meet load transient and output ripple's requirements.

Equation 7 gives the minimum output capacitance to meet the transient specification. For this example,  $L = 4.7 \ \mu H$ ,  $\Delta I_{OUT} = 1 \ A - 0.0 \ A = 1 \ A$  and  $\Delta V_{OUT} = 500 \ mV$  (10% of regulated 5 V). Using these numbers gives a minimum capacitance of 1  $\mu F$ . A standard 22- $\mu F$  ceramic is chosen in the design.

$$Co > \frac{\Delta I_{OUT}^2 \cdot L}{2 \cdot V_{OUT} \cdot \Delta V_{OUT}}$$

(7)

The selection of  $C_O$  is driven by the effective series resistance (ESR). Equation 8 calculates the minimum output capacitance needed to meet the output voltage ripple specification. Where  $f_{SW}$  is the switching frequency,  $\Delta V_{OUT}$  is the maximum allowable output voltage ripple, and  $\Delta i_L$  is the inductor ripple current. In this case, the maximum output voltage ripple is 50 mV (1% of regulated 5 V). From Equation 4, the output current ripple is 1 A. From Equation 8, the minimum output capacitance meeting the output voltage ripple requirement is 2.5  $\mu$ F with 3-m $\Omega$  ESR resistance.

$$Co > \frac{1}{8 \cdot fsw} \cdot \frac{1}{\frac{\Delta V_{OUT}}{\Delta i_L} - ESR}$$

(8)

After considering both requirements, for this example, one 22- $\mu$ F, 6.3-V X7R ceramic capacitor with 3-m $\Omega$  ESR should be used.

#### **Input Capacitor Selection**

A minimum 10- $\mu$ F X7R/X5R ceramic input capacitor is recommended to be added between VIN and GND. These capacitors should be connected as close as physically possible to the input pins of the converters as they handle the RMS ripple current shown in Equation 9. For this example,  $I_{OUT} = 1$  A,  $V_{OUT} = 5$  V, minimum  $V_{INmin} = 9.6$  V, from Equation 9, the input capacitors must support a ripple current of 1-A RMS.

$$I_{INRMS} = I_{OUT} \cdot \sqrt{\frac{V_{OUT}}{V_{INmin}} \cdot \frac{\left(V_{INmin} - V_{OUT}\right)}{V_{INmin}}}$$

(9)

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using Equation 10. Using the design example values,  $I_{OUTmax} = 1$  A,  $C_{IN} = 10$   $\mu$ F,  $f_{SW} = 300$  kHz, yields an input voltage ripple of 83 mV.

$$\Delta V_{IN} = \frac{I_{OUT\,max} \cdot 0.25}{C_{IN} \cdot f_{SW}} \tag{10}$$

To prevent large voltage transients, a low ESR capacitor sized for the maximum RMS current must be used.

## **Bootstrap Capacitor Selection**

An external bootstrap capacitor connected to the BST pins supplies the gate drive voltages for the topside MOSFETs. The capacitor between BST pin and LX pin is charged though internal diode from V7V when the LX pin is low. When a high side MOSFET is to be turned on, the driver places the bootstrap voltage across the gate-source of the desired MOSFET. This enhances the top MOSFET switch and turns it on. The switch node voltage, LX, rises to VIN and the BST pin follows. With the internal high side MOSFET on, the bootstrap voltage is above the input supply:  $V_{BST} = V_{IN} + V7V$ . The selection on bootstrap capacitance is related with internal high side power MOSFET gate capacitance. A 0.047- $\mu$ F ceramic capacitor is recommended between the BST pin and LX pin for proper operation. It is recommended to use a ceramic capacitor with X5R or better grade dielectric. The capacitor should have 10-V or higher voltage rating.

#### **Thermal Shutdown**

The device implements an internal thermal shutdown to protect itself if the junction temperature exceeds 165°C. The thermal shutdown forces the device to stop switching when the junction temperature exceeds the thermal trip threshold. Once the die temperature decreases below 165°C, the device reinitiates the power up sequence.

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                         |         |

| TPS5405DR        | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | T5405                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Oct-2023

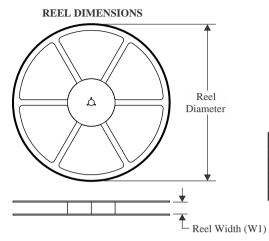

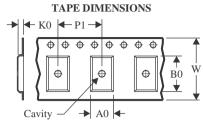

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

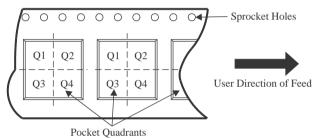

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device    | U    | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------|------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS5405DR | SOIC | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Oct-2023

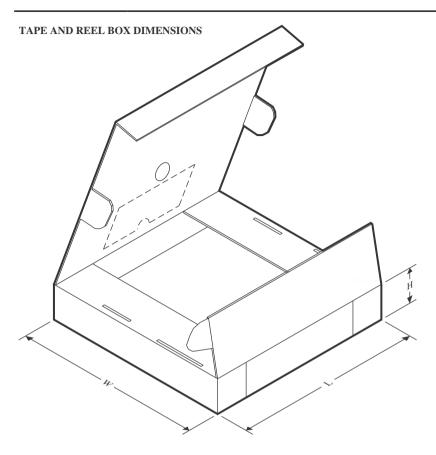

## \*All dimensions are nominal

|   | Device    | Device Package Type |   | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|-----------|---------------------|---|------|------|-------------|------------|-------------|--|

| I | TPS5405DR | SOIC                | D | 8    | 2500 | 340.5       | 338.1      | 20.6        |  |

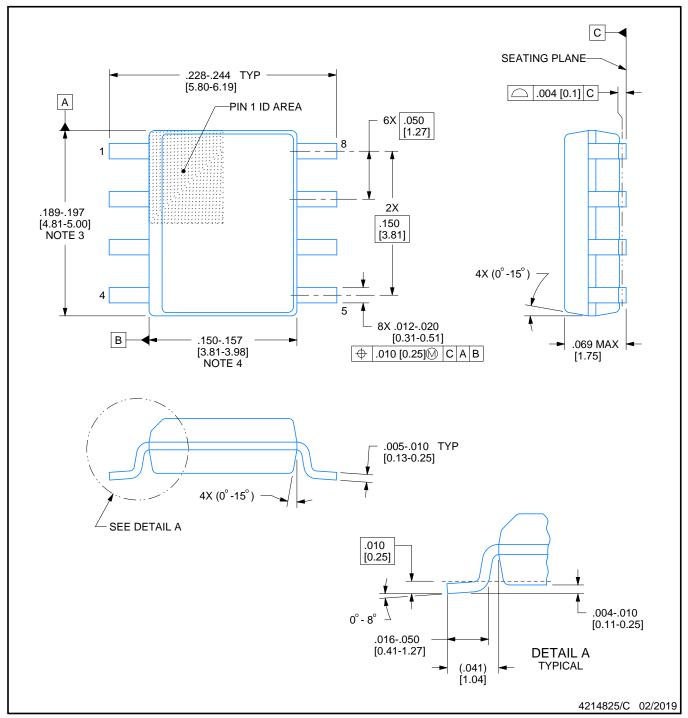

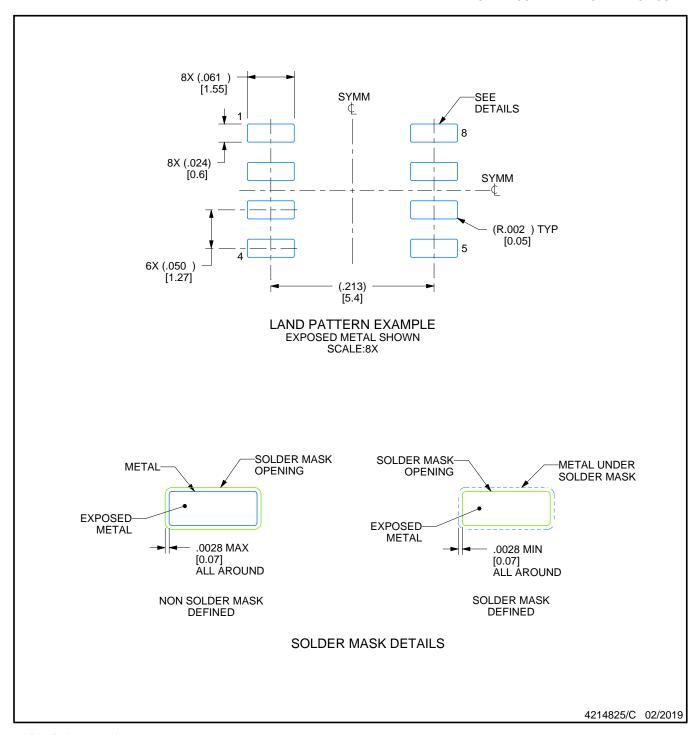

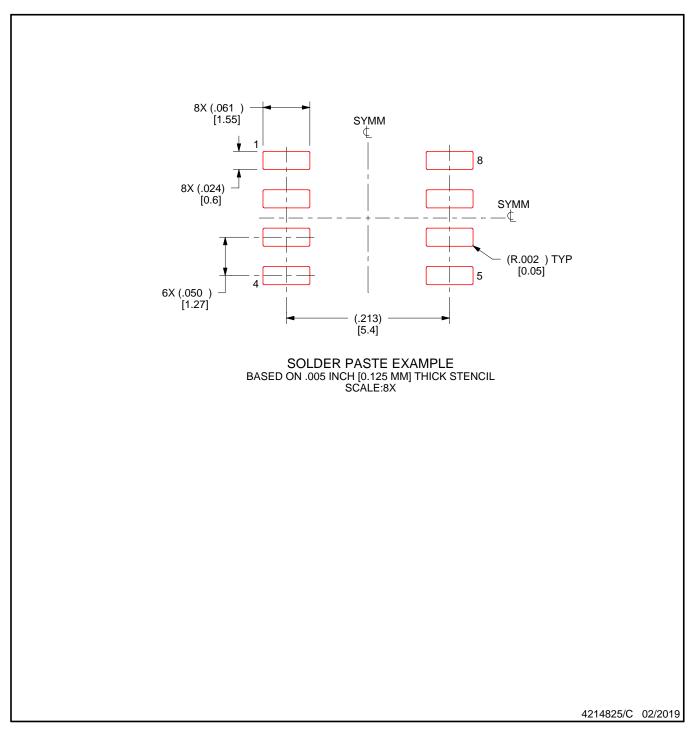

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司