**TPS536C9T**

ZHCST07 - SEPTEMBER 2023

# TPS536C9T 具有 TLVR 支持、PMBus 和 VR14 SVID 接口的双 channel (N + M ≤ 12 相)D-CAP+™降压多相控制器

# 1 特性

输入电压范围: 4.5V 至 17V 输出电压范围: 0.25V 至 5.5V

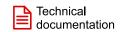

- 支持 N+M 相位配置(N+M ≤ 12,M ≤ 6)的双路输

- 自带跨电感稳压器 (TLVR) 拓扑支持,具有 L<sub>C</sub> 开路 和短路保护

- 与 TI 智能功率级完全兼容

- 支持电压源和电流源 IMON 功率级,具有内部 1kΩ

- 支持传统模式和跛行模式功率级故障识别

- 支持布线长度大于 12 英寸的双侧电力输送

- 符合 Intel® VR14 SVID 标准且支持 PSYS

- 向后兼容 VR13.HC/VR13.0 SVID

- 自动 NVM 故障状态记录

- 增强型 D-CAP+ 控制可提供卓越的瞬态性能和出色 的动态电流共享

- 可通过可编程阈值实现动态切相,从而提高轻负载 和重负载下的效率

- 可通过非易失性存储器 (NVM) 进行配置,从而减少 外部组件数量

- 单独的每相位 IMON 校准,具有多斜率增益校准以 提高系统精度

- 具有可编程超时的二极管制动,可减少瞬态过冲

- 可编程的每相位谷值电流限制 (OCL)

- PMBus™ v1.3.1 系统接口,用于遥测电压、电流、 功率、温度和故障条件

- 可通过 PMBus 对环路补偿进行编程

- 6.00 mm × 6.00 mm, 48 引脚, QFN 封装

#### 2 应用

- 数据中心和企业计算 机架式服务器

- 硬件加速器

- 网络接口卡 (NIC)

- ASIC 和 高性能客户端

# 3 说明

TPS536C9T 是一款符合 VR14 SVID 标准的降压控 制器,具有跨电感稳压器 (TLVR) 拓扑支持、双通道、 内置非易失性存储器 (NVM) 和 PMBus™ 接口,而且 与 TI 智能功率级完全兼容。D-CAP+ 架构等高级控制 特性可提供快速瞬态响应、低输出电容和良好的动态电 流共享。还本地支持输出电压转换率和自适应电压定位 的可调控制。此外,该器件还支持 PMBus 通信接口 可向主机系统报告遥测的电压、电流、功率、温度和故 障状况。所有可编程参数均可通过 PMBus 接口进行配 置,而且可作为新的默认值存储在 NVM 中,以尽可能 减少外部组件数量。

#### 封装信息

| 器件型号      | 封装 <sup>(1)</sup> | 封装尺寸 <sup>(2)</sup> |

|-----------|-------------------|---------------------|

| TPS536C9T | RSL (QFN, 48)     | 6.00 mm × 6.00 mm   |

- 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

- (2) 封装尺寸(长x宽)为标称值,并包括引脚(如适用)。

#### 器件信息

| AR III                       | IH    |

|------------------------------|-------|

| 器 <u>件</u> 型号 <sup>(1)</sup> | 相位数   |

| TPS536C9T                    | 12 相位 |

#### (1) 请参阅器件比较表

简化版应用(交错式 TLVR)

# **Table of Contents**

| 1 特性                                | 5.5 静电放电警告3                                           |

|-------------------------------------|-------------------------------------------------------|

| 3 说明                                |                                                       |

| 5 Device and Documentation Support3 |                                                       |

| 5.1 Documentation Support3          | 6.2 Packaging Information4                            |

| 5.2 接收文档更新通知3                       | 6.3 Tape and Reel Information6                        |

| 5.3 支持资源3                           | 7 Mechanical, Packaging, and Orderable Information 12 |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2023 | *        | Initial Release |

Product Folder Links: TPS536C9T

# **5 Device and Documentation Support**

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

#### **5.1 Documentation Support**

#### 5.2 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*订阅更新* 进行注册,即可每周接收产品信息更 改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 5.3 支持资源

TI E2E™ 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 5.4 Trademarks

TI E2E™ is a trademark of Texas Instruments.

Intel® is a registered trademark of Intel Corporation.

所有商标均为其各自所有者的财产。

## 5.5 静电放电警告

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 5.6 术语表

#### TI 术语表

本术语表列出并解释了术语、首字母缩略词和定义。

# 6 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

## 6.1 Package Option Addendum

## **6.2 Packaging Information**

| O | rderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish (4) | MSL Peak Temp <sup>(3)</sup> | Op Temp (°C) | Device Marking (5) (6) |

|---|-----------------|------------|--------------|--------------------|------|-------------|-------------------------|----------------------|------------------------------|--------------|------------------------|

| Т | PS536C9TRSLR    | ACTIVE     | VQFN         | RSL                | 48   | 3000        | Green (RoHS & no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR          | -40 to 125   | TPS 536C9T             |

1. The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PRE\_PROD Unannounced device, not in production, not available for mass market, nor on the web, samples not available.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

2. Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** Ti's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br)**: TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- 3. MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- 4. Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

- 5. There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device

- 6. Multiple Device markings will be inside parentheses. Only on Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

4 Submit Document Feedback Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: TPS536C9T

Copyright © 2023 Texas Instruments Incorporated

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Product Folder Links: TPS536C9T

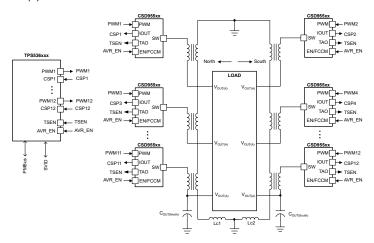

# 6.3 Tape and Reel Information

#

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    |                                                           |

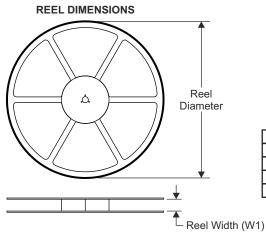

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device        | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS536C9TRSLR | VQFN            | RSL                | 48   | 3000 | 330.0                    | 16.4                     | 6.3        | 6.3        | 1.1        | 12.0       | 16.0      | Q2               |

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS536C9TRSLR | VQFN         | RSL             | 48   | 3000 | 367.0       | 367.0      | 38.0        |

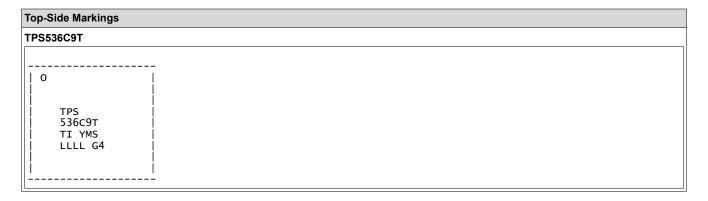

## **Top Side Markings**

TI = The letters "TI" for Texas Instruments

Y = Year (Last digit of the year assembled, 0=2020, 1=2021, ...)

M = Month (1=Jan, 2=Feb, ... A=Oct, B=Nov, C=Dec)

S = Assembly Site Code

LLLL = Assembly Lot Trace Code

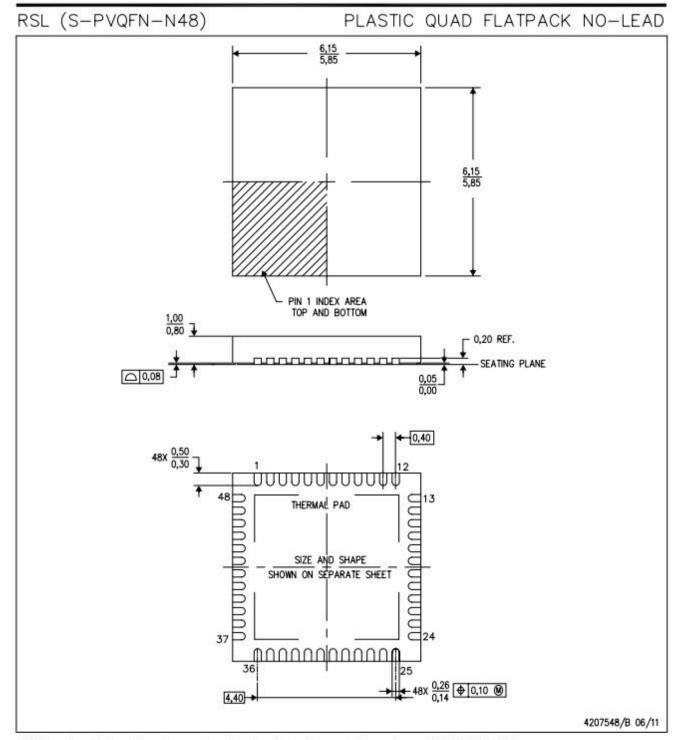

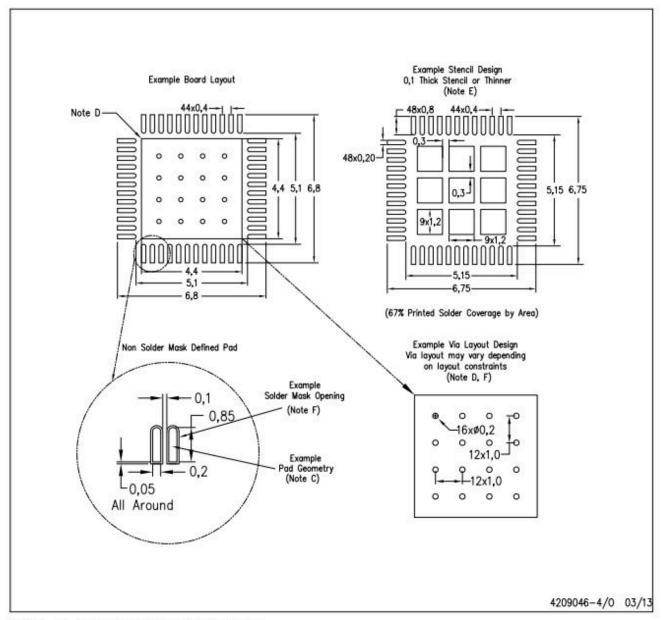

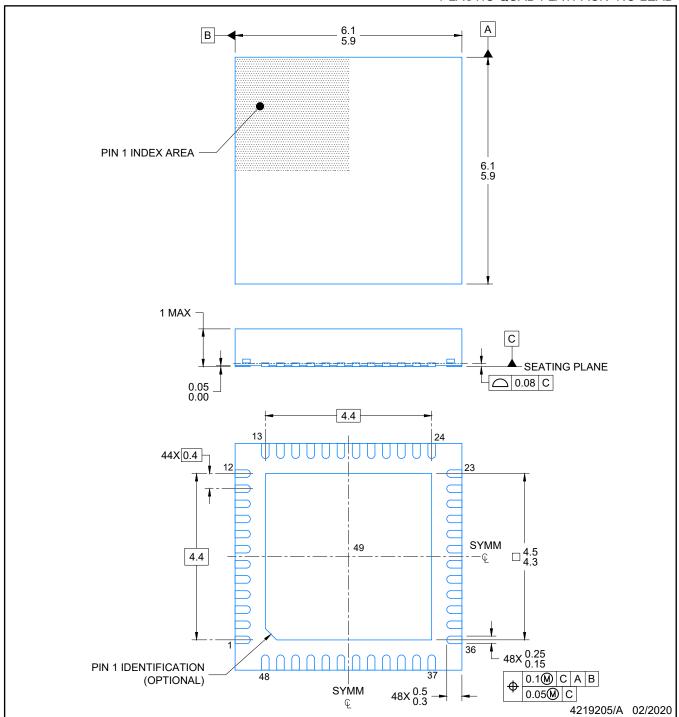

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

# RSL (S-PVQFN-N48)

# PLASTIC QUAD FLATPACK NO-LEAD

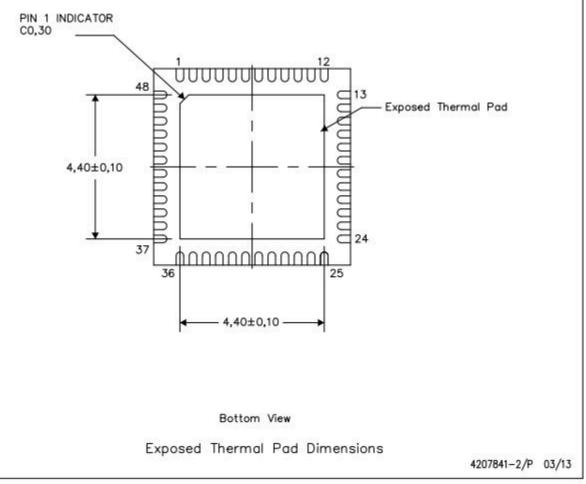

#### THERMAL INFORMATION

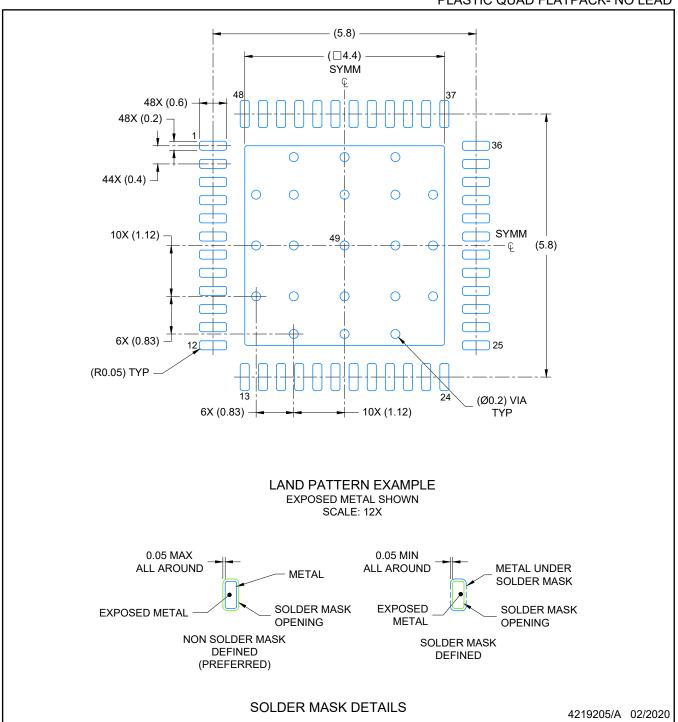

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

# RSL (S-PVQFN-N48)

# PLASTIC QUAD FLATPACK NO-LEAD

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

# 7 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 19-Sep-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                         |         |

| TPS536C9TRSLR    | ACTIVE | VQFN         | RSL                | 48   | 3000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | TPS<br>536C9T           | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

4207548/B 06/11

# RSL (S-PVQFN-N48) PLASTIC QUAD FLATPACK NO-LEAD 6,15 5,85 6,15 5,85 PIN 1 INDEX AREA TOP AND BOTTOM 1,00 0,80 0,20 REF. SEATING PLANE 0,08 0,05 0,00 0,40 48 THERMAL PAD SIZE AND SHAPE SHOWN ON SEPARATE SHEET 37 36 $48 \times \frac{0.26}{0.14}$ 4,40

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

PLASTIC QUAD FLATPACK- NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

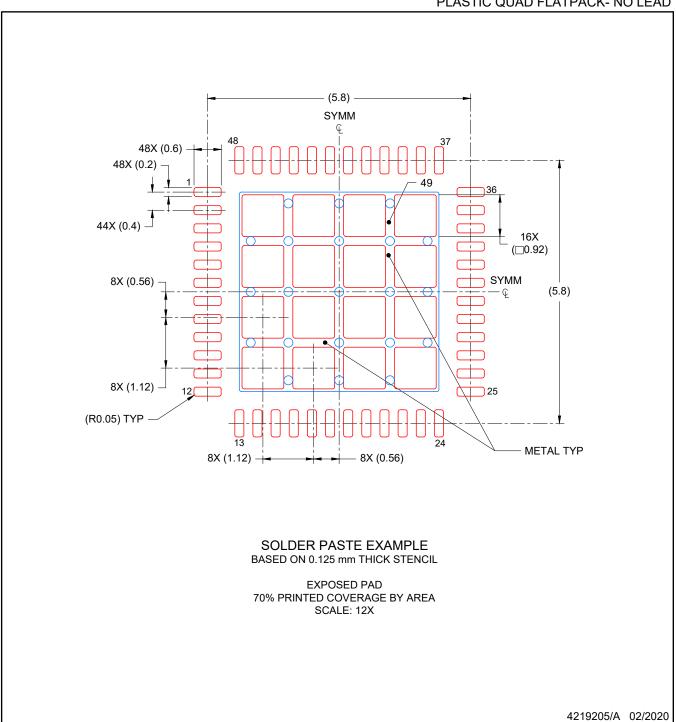

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司