www.ti.com.cn

# 完整 DDR, DDR2, DDR1 和 LPDDR3 存储器电源解决方案 同步降压控制器, 1A 低压降稳压器 (LDO), 经缓冲基准

查询样品: TPS51116-EP

### 特性

- 同步降压控制器 (VDDQ)

- 宽输入电压范围: 3.0V 至 28V

- 负载阶跃响应为 100ns 的 D-CAP™ 模式

- 电流模式选项支持陶瓷输出电容器

- 支持 S4/S5 状态内的软关闭

- R<sub>DS (接通)</sub> 或电阻器的电流感测

- 2.5V (DDR), 1.8V (DDR2), 可调节至

1.5V (DDR3) 或 1.2V (LPDDR3) 或

0.75V 至 3.0V 的输出电压范围

- 配备有电源正常、过压保护和欠压保护

- 1A LDO (VTT), 经缓冲基准 (VREF)

- 灌电流和拉电流的能力达到 1A

- 提供 LDO 输入以优化功率损耗

- 只需 20uF 陶瓷输出电容器

- 经缓冲的低噪声 10mA VREF 输出

- 针对 VREF 和 VTT 的 ±20mV 精度

- 在 **S3** 中支持高阻抗 (high-Z), 在 **S4/S5** 中支持软关闭

- 过热保护

### 应用范围

- DDR/DDR2/DDR3/LPDDR3 内存电源

- SSTL-2, SSTL-18, SSTL-15 和 HSTL 终止

支持国防、航空航天、和医疗应用

- 受控基线

- 一个组装和测试场所

- 一个制造场所

- 支持军用(-55°C至 125°C)温度范围

- 延长的产品生命周期

- 延长的产品变更通知

- 产品可追溯性

### 说明

TPS51116 为 DDR/SSTL-2,DDR2/SSTL-18,DDR3/SSTL-15 和 LPDDR3 内存系统提供一个完整的电源。 它集成了一个具有 1A 灌电流/拉电流跟踪线性稳压器和经缓冲低噪声基准的同步降压控制器。 TPS51116 在空间非常宝贵的系统中提供最低的总体解决方案成本。 TPS51116 同步控制器运行具有自适应接通时间控制的定频400kHz,伪恒定频率脉宽调制 (PWM),此控制可在 D-CAP™ 模式中进行配置,此模式可简化使用并实现最快瞬态响应或者在电流模式中支持陶瓷输出电容器。 1A 灌电流/拉电流 LDO 只需 20μF (2 × 10μF) 陶瓷输出电容器即可保持快速瞬态响应。 此外,LDO 电源输入是外部可用的,这样可大大减少总体功耗。 TPS51116 支持所有睡眠状态控制,此类控制在 S3(挂起到 RAM)中将 VTT 置于 high-Z 状态并且在 S4/S5(挂起到硬盘)中将VDDQ,VTT 和 VTTREF(软关闭)放电。 TPS51116 具有所有保护特性,其中包括热关断并采用 20 引脚散热薄型小外形尺寸 (HTSSOP) PowerPAD™ 封装。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE                               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING | VID NUMBER       |

|----------------|---------------------------------------|--------------------------|---------------------|------------------|

| FF9C +- 40F9C  | Disatis LITCOOD Dawns DAD (DIA/D) (2) | TPS51116MPWPREP          | E444CM              | V62/12602-01XE   |

| –55°C to 125°C | Plastic HTSSOP PowerPAD (PWP) (2)     | TPS51116MPWPEP           | 51116M              | V62/12602-01XE-T |

- For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- With Cu NIPDAU lead/ball finish

### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range unless otherwise noted

|                  |                               |                                                          | MIN  | MAX | UNIT |

|------------------|-------------------------------|----------------------------------------------------------|------|-----|------|

|                  |                               | VBST                                                     | -0.3 | 36  |      |

| .,               | land to the second            | VBST wrt LL                                              | -0.3 | 6   | .,   |

| V <sub>IN</sub>  | Input voltage range           | CS, MODE, S3, S5, VTTSNS, VDDQSNS, V5IN, VLDOIN, VDDQSET | -0.3 | 6   | V    |

|                  |                               | PGND, VTTGND                                             | -0.3 | 0.3 |      |

|                  |                               | DRVH                                                     | -1.0 | 36  | V    |

| .,               | Output voltage range          | LL                                                       | -1.0 | 30  |      |

| V <sub>OUT</sub> |                               | LL, pulse width < 20 ns                                  | -5   | 30  |      |

|                  |                               | COMP, DRVL, PGOOD, VTT, VTTREF                           | -0.3 | 6   |      |

| TJ               | Operating ambient temperature | erature range                                            | -55  | 150 | °C   |

| T <sub>stg</sub> | Storage temperature           |                                                          | -65  | 150 | C    |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

### THERMAL INFORMATION

|                         |                                                             | TPS51116-EP |       |

|-------------------------|-------------------------------------------------------------|-------------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                               | PWP         | UNITS |

|                         |                                                             | 20 PINS     |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 41.2        |       |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance (3)               | 27.4        |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance (4)                    | 23.9        | 0000  |

| Ψлт                     | Junction-to-top characterization parameter <sup>(5)</sup>   | 1.1         | °C/W  |

| ΨЈВ                     | Junction-to-board characterization parameter <sup>(6)</sup> | 23.7        |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 3.6         |       |

- 有关传统和新的热 度量的更多信息,请参阅IC 封装热度量应用报告, SPRA953。

- 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然 对流条件下的结至环 境热阻。

- 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但 可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

- 按照 JESD51-8 中的说明,通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结板热阻。

- 结至顶部特征参数, ψ<sub>JT</sub>,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该参 数以便获得 θ<sub>JA</sub>。

- 结至电路板特征参数,  $\psi_{JB}$ ,估算真实系统中器件的结温,并使用 JESD51-2a(第 6 章和第 7 章)中 描述的程序从仿真数据中 提取出该

- 参数以便获得 θ<sub>JA</sub> 。 通过在外露(电源)焊盘上进行冷板测试仿真来获得 结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准 测试,但可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

### **RECOMMENDED OPERATING CONDITIONS**

|                                                |                                              | MIN         | MAX  | UNIT |

|------------------------------------------------|----------------------------------------------|-------------|------|------|

| Supply voltage, V5IN                           |                                              | 4.75        | 5.25 | V    |

|                                                | VBST, DRVH                                   | -0.1        | 34   |      |

|                                                | LL                                           | -0.6        | 28   |      |

|                                                | VLDOIN, VTT, VTTSNS, VDDQSNS                 | -0.1        | 3.6  |      |

| Voltage range                                  | VTTREF                                       | -0.1        | 1.8  | V    |

|                                                | PGND, VTTGND                                 | -0.1        | 0.1  |      |

|                                                | S3, S5, MODE, VDDQSET, CS, COMP, PGOOD, DRVL | -0.1        | 5.25 |      |

| Operating free-air temperature, T <sub>A</sub> |                                              | <b>-</b> 55 | 125  | °C   |

### **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range,  $V_{V5IN} = 5 \text{ V}$ , VLDOIN is connected to VDDQ output (unless otherwise noted)

|                        | PARAMETER                | TEST CONDITIONS                                                                     | MIN | TYP | MAX  | UNIT |  |  |  |

|------------------------|--------------------------|-------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|

| SUPPLY CURRENT         |                          |                                                                                     |     |     |      |      |  |  |  |

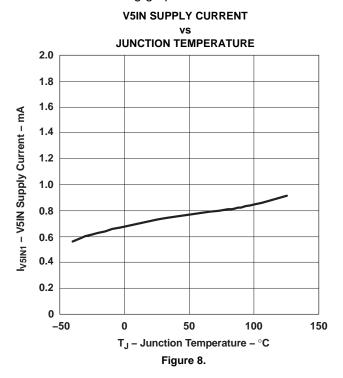

| I <sub>V5IN1</sub>     | Supply current 1, V5IN   | No load, $V_{S3} = V_{S5} = 5 \text{ V}$ , COMP connected to capacitor              |     | 0.8 | 2    | mA   |  |  |  |

| I <sub>V5IN2</sub>     | Supply current 2, V5IN   | No load, $V_{S3} = 0 V$ , $V_{S5} = 5 V$ , COMP connected to capacitor              |     | 300 | 610  |      |  |  |  |

| I <sub>V5IN3</sub>     | Supply current 3, V5IN   | No load, $V_{S3} = 0 \text{ V}$ , $V_{S5} = 5 \text{ V}$ , $V_{COMP} = 5 \text{ V}$ |     | 240 | 508  |      |  |  |  |

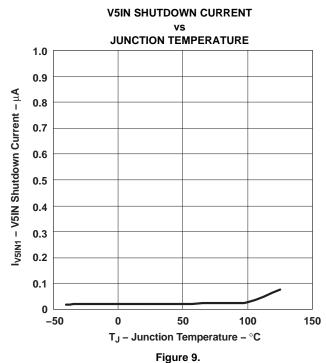

| I <sub>V5INSDN</sub>   | Shutdown current, V5IN   | No load, V <sub>S3</sub> = V <sub>S5</sub> = 0 V                                    |     | 0.1 | 1.81 | μΑ   |  |  |  |

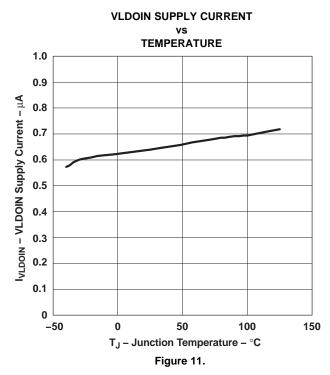

| I <sub>VLDOIN1</sub>   | Supply current 1, VLDOIN | No load, V <sub>S3</sub> = V <sub>S5</sub> = 5 V                                    |     | 1   | 10   |      |  |  |  |

| I <sub>VLDOIN2</sub>   | Supply current 2, VLDOIN | No load, $V_{S3} = 5 \text{ V}$ , $V_{S5} = 0 \text{ V}$ ,                          |     | 0.1 | 10.5 |      |  |  |  |

| I <sub>VLDOINSDN</sub> | Standby current, VLDOIN  | No load, V <sub>S3</sub> = V <sub>S5</sub> = 0 V                                    |     | 0.1 | 1.5  |      |  |  |  |

over operating free-air temperature range,  $V_{V5IN} = 5 V$ , VLDOIN is connected to VDDQ output (unless otherwise noted)

|                          | PARAMETER                              | TEST CONDITIONS                                                                                                                        | MIN   | TYP       | MAX   | UNIT |

|--------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------|------|

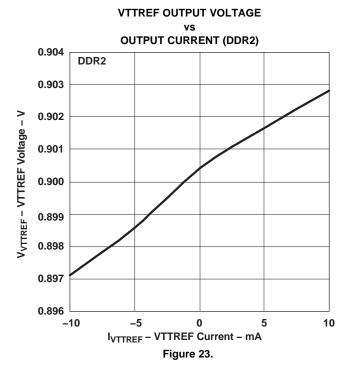

| VTTREF OUT               |                                        | I                                                                                                                                      |       |           |       |      |

| V <sub>VTTREF</sub>      | Output voltage, VTTREF                 | 40 40 40 40                                                                                                                            | V     | VDDQSNS/2 |       | V    |

|                          |                                        | -10 mA < $I_{VTTREF}$ < 10 mA, $V_{VDDQSNS}$ = 2.5 V, Tolerance to $V_{VDDQSNS}/2$                                                     | -20   |           | 20    |      |

| V                        | Output voltage tolerance               | -10 mA < $I_{VTTREF}$ < 10 mA, $V_{VDDQSNS}$ = 1.8 V, Tolerance to $V_{VDDQSNS}/2$                                                     | -19   |           | 19    | mV   |

| V <sub>VTTREFTOL</sub>   | Output voltage tolerance               | -10 mA < $I_{VTTREF}$ < 10 mA, $V_{VDDQSNS}$ = 1.5 V, Tolerance to $V_{VDDQSNS}/2$                                                     | -16   |           | 16    | IIIV |

|                          |                                        | -10 mA < $I_{VTTREF}$ < 10 mA, $V_{VDDQSNS}$ = 1.2 V, Tolerance to $V_{VDDQSNS}/2$                                                     | -13   |           | 13    |      |

| V <sub>VTTREFSRC</sub>   | Source current                         | V <sub>VDDQSNS</sub> = 2.5 V, V <sub>VTTREF</sub> = 0 V                                                                                | -19   | -40       | -83.5 | mΛ   |

| V <sub>VTTREFSNK</sub>   | Sink current                           | V <sub>VDDQSNS</sub> = 2.5 V, V <sub>VTTREF</sub> = 2.5 V                                                                              | 19    | 40        | 83.5  | mA   |

| VDDQ OUTP                | UT                                     |                                                                                                                                        |       |           | ·     |      |

|                          |                                        | T <sub>A</sub> = 25°C, V <sub>VDDQSET</sub> = 0 V, No load                                                                             | 2.465 | 2.500     | 2.535 |      |

|                          |                                        | -55°C ≤ T <sub>A</sub> ≤ 125°C, V <sub>VDDQSET</sub> = 0 V, No load                                                                    | 2.43  | 2.50      | 2.56  |      |

| $V_{VDDQ}$               | Output voltage, VDDQ                   | T <sub>A</sub> = 25°C, V <sub>VDDQSET</sub> = 5 V, No load                                                                             | 1.776 | 1.800     | 1.830 | V    |

|                          |                                        | -55°C ≤ T <sub>A</sub> ≤ 125°C, V <sub>VDDQSET</sub> = 5 V, No load                                                                    | 1.762 | 1.800     | 1.838 |      |

|                          |                                        | -55°C ≤ T <sub>A</sub> ≤ 125°C, Adjustable mode, No load                                                                               | 0.75  |           | 3.0   |      |

| .,                       | VDDOCET regulation valtage             | T <sub>A</sub> = 25°C, Adjustable mode                                                                                                 | 742.5 | 750       | 760.5 | \/   |

| V <sub>VDDQSET</sub>     | VDDQSET regulation voltage             | -55°C ≤ T <sub>A</sub> ≤ 125°C, Adjustable mode                                                                                        | 737   | 750       | 763   | mV   |

|                          | Input impedance, VDDQSNS               | V <sub>VDDQSET</sub> = 0 V                                                                                                             |       | 215       |       | kΩ   |

| R <sub>VDDQSNS</sub>     |                                        | V <sub>VDDQSET</sub> = 5 V                                                                                                             |       | 180       |       |      |

|                          |                                        | Adjustable mode                                                                                                                        |       | 460       |       |      |

| 1                        | land comment VDDOCET                   | V <sub>VDDQSET</sub> = 0.78 V, COMP = Open                                                                                             |       | -0.04     |       |      |

| IVDDQSET                 | Input current, VDDQSET                 | V <sub>VDDQSET</sub> = 0.78 V, COMP = 5 V                                                                                              |       | -0.06     |       | μA   |

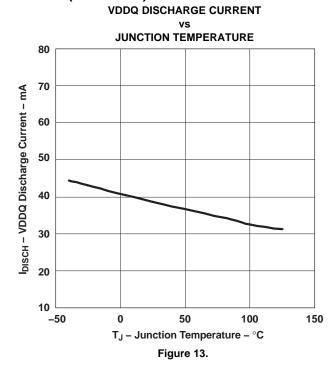

| I <sub>VDDQDisch</sub>   | Discharge current, VDDQ                | $V_{S3} = V_{S5} = 0 \text{ V}, V_{VDDQSNS} = 0.5 \text{ V}, V_{MODE} = 0 \text{ V}$                                                   | 10    | 40        |       | mA   |

| I <sub>VLDOINDisch</sub> | Discharge current, VLDOIN              | $V_{S3} = V_{S5} = 0 \text{ V}, V_{VDDQSNS} = 0.5 \text{ V}, V_{MODE} = 0.5 \text{ V}$                                                 |       | 700       |       | mA   |

| VTT OUTPUT               | T                                      |                                                                                                                                        |       |           |       |      |

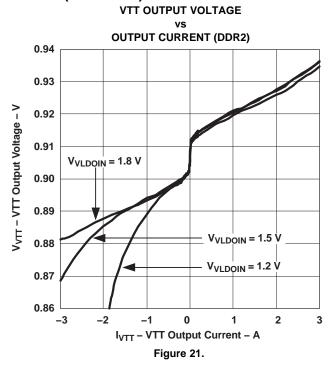

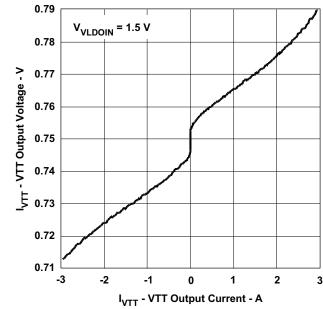

|                          |                                        | $V_{S3} = V_{S5} = 5 \text{ V}, V_{VLDOIN} = V_{VDDQSNS} = 2.5 \text{ V}$                                                              |       | 1.25      |       |      |

| $V_{VTTSNS}$             | Output voltage, VTT                    | V <sub>S3</sub> = V <sub>S5</sub> = 5 V, V <sub>VLDOIN</sub> = V <sub>VDDQSNS</sub> = 1.8 V                                            |       | 0.9       |       | V    |

|                          |                                        | V <sub>S3</sub> = V <sub>S5</sub> = 5 V, V <sub>VLDOIN</sub> = V <sub>VDDQSNS</sub> = 1.5 V                                            |       | 0.75      |       |      |

|                          |                                        | $V_{VDDQSNS} = V_{VLDOIN} = 2.5 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V}, I_{VTT} = 0 \text{ A}$                                       | -21   |           | 21    |      |

| V <sub>VTTTOL25</sub>    | VTT output voltage tolerance to VTTREF | $V_{VDDQSNS} = V_{VLDOIN} = 2.5 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V},$<br>$ I_{VTT}  < 1.5 \text{ A}$                              | -31   |           | 31    | mV   |

|                          |                                        | $V_{VDDQSNS} = V_{VLDOIN} = 2.5 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V},$<br>$ I_{VTT}  < 3 \text{ A}$                                | -41   |           | 41    |      |

|                          |                                        | $\begin{aligned} &V_{VDDQSNS} = V_{VLDOIN} = 1.8 \text{ V},  V_{S3} = V_{S5} = 5 \text{ V}, \\ &I_{VTT} = 0 \text{ A} \end{aligned}$   | -21   |           | 21    |      |

| V <sub>VTTTOL18</sub>    | VTT output voltage tolerance to VTTREF | $V_{VDDQSNS} = V_{VLDOIN} = 1.8 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V},$<br>$ I_{VTT}  < 1 \text{ A}$                                | -31   |           | 31    | m۷   |

|                          |                                        | $\begin{aligned} &V_{VDDQSNS} = V_{VLDOIN} = 1.8 \text{ V},  V_{S3} = V_{S5} = 5 \text{ V}, \\ & I_{VTT}  < 2 \text{ A} \end{aligned}$ | -41   |           | 41    |      |

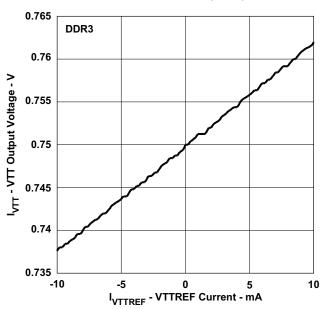

|                          |                                        | $V_{VDDQSNS} = V_{VLDOIN} = 1.5 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V}, I_{VTT} = 0 \text{ A}$                                       | -21   |           | 21    |      |

| V <sub>VTTTOL15</sub>    | VTT output voltage tolerance to VTTREF | $V_{VDDQSNS} = V_{VLDOIN} = 1.5 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V},$<br>$ I_{VTT}  < 1 \text{ A}$                                | -31   |           | 31    | mV   |

|                          |                                        | $V_{VDDQSNS} = V_{VLDOIN} = 1.5 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V},$<br>$ I_{VTT}  < 2 \text{ A}$                                | -41   |           | 41    |      |

over operating free-air temperature range,  $V_{V5IN} = 5 V$ , VLDOIN is connected to VDDQ output (unless otherwise noted)

|                         | PARAMETER                              | TEST CONDITIONS                                                                                                                          | MIN  | TYP  | MAX  | UNIT |  |

|-------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

|                         |                                        | $V_{VDDQSNS} = V_{VLDOIN} = 1.2 \text{ V}, V_{S3} = V_{S5} = 5 \text{ V}, I_{VTT} = 0 \text{ A}$                                         | -21  |      | 21   |      |  |

| V <sub>VTTTOL12</sub>   | VTT output voltage tolerance to VTTREF | $\begin{aligned} &V_{VDDQSNS} = V_{VLDOIN} = 1.2 \text{ V},  V_{S3} = V_{S5} = 5 \text{ V}, \\ & I_{VTT}  < 1 \text{ A} \end{aligned}$   | -31  |      | 31   | mV   |  |

|                         |                                        | $\begin{aligned} &V_{VDDQSNS} = V_{VLDOIN} = 1.2 \text{ V},  V_{S3} = V_{S5} = 5 \text{ V}, \\ & I_{VTT}  < 1.5 \text{ A} \end{aligned}$ | -41  |      | 41   |      |  |

| I <sub>VTTTOCLSRC</sub> | Source current limit, VTT              | $V_{VLDOIN} = V_{VDDQSNS} = 2.5 \text{ V},$<br>$V_{VTT} = V_{VTTSNS} = 1.19 \text{ V}, \text{ PGOOD} = \text{HI}$                        | 2.7  | 3.8  | 6.2  |      |  |

|                         |                                        | $V_{VLDOIN} = V_{VDDQSNS} = 2.5 \text{ V}, V_{VTT} = 0 \text{ V}$                                                                        | 1.4  | 2.2  | 3.2  | Α    |  |

| I <sub>VTTTOCLSNK</sub> | Sink current limit, VTT                | $V_{VLDOIN} = V_{VDDQSNS} = 2.5 \text{ V},$<br>$V_{VTT} = V_{VTTSNS} = 1.31 \text{ V}, PGOOD = HI$                                       | 2.65 | 3.6  | 6    | Α    |  |

|                         |                                        | $V_{VLDOIN} = V_{VDDQSNS} = 2.5 \text{ V}, V_{VTT} = V_{VDDQ}$                                                                           | 1.4  | 2.2  | 3    | 3    |  |

| $I_{VTTLK}$             | Leakage current, VTT                   | $V_{S3} = 0 \text{ V}, V_{S5} = 5 \text{ V}, V_{VTT} = V_{VDDQSNS} /2$                                                                   | -11  |      | 11   |      |  |

| I <sub>VTTBIAS</sub>    | Input bias current, VTTSNS             | $V_{S3} = 5 \text{ V}, V_{VTTSNS} = V_{VDDQSNS}/2$                                                                                       | -1.1 |      | 1.1  | μΑ   |  |

| I <sub>VTTSNSLK</sub>   | Leakage current, VTTSNS                | $V_{S3} = 0 \text{ V}, V_{S5} = 5 \text{ V}, V_{VTT} = V_{VDDQSNS} / 2$                                                                  | -1   |      | 1    |      |  |

| I <sub>VTTDisch</sub>   | Discharge current, VTT                 | $V_{S3} = V_{S5} = V_{VDDQSNS} = 0 \text{ V}, V_{VTT} = 0.5 \text{ V}$                                                                   | 9.5  | 17   |      | mA   |  |

| TRANSCONE               | DUCTANCE AMPLIFIER                     |                                                                                                                                          |      |      | ·    |      |  |

| gm                      | Gain                                   |                                                                                                                                          | 232  | 300  | 364  | μS   |  |

| I <sub>COMPSNK</sub>    | COMP maximum sink current              | V <sub>S3</sub> = 0 V, V <sub>S5</sub> = 5 V, V <sub>VDDQSET</sub> = 0 V,<br>V <sub>VDDQSNS</sub> = 2.7 V, V <sub>COMP</sub> = 1.28 V    | 13   |      |      |      |  |

| I <sub>COMPSRC</sub>    | COMP maximum source current            | $V_{S3} = 0 \text{ V}, V_{S5} = 5 \text{ V}, V_{VDDQSET} = 0 \text{ V}, V_{VDDQSNS} = 2.3 \text{ V}, V_{COMP} = 1.28 \text{ V}$          |      | -13  | μА   |      |  |

| V <sub>COMPHI</sub>     | COMP high clamp voltage                | $V_{S3} = 0 \text{ V}, V_{S5} = 5 \text{ V}, V_{VDDQSET} = 0 \text{ V}, V_{VDDQSNS} = 2.3 \text{ V}, V_{CS} = 0 \text{ V}$               | 1.3  | 1.34 | 1.38 | V    |  |

| $V_{COMPLO}$            | COMP low clamp voltage                 | $V_{S3} = 0 \text{ V}, V_{S5} = 5 \text{ V}, V_{VDDQSET} = 0 \text{ V}, V_{VDDQSNS} = 2.7 \text{ V}, V_{CS} = 0 \text{ V}$               | 1.17 | 1.21 | 1.25 | V    |  |

| DUTY CONTI              | ROL                                    |                                                                                                                                          |      |      |      |      |  |

| t <sub>ON</sub>         | Operating on-time                      | V <sub>IN</sub> = 12 V, V <sub>VDDQSET</sub> = 0 V                                                                                       |      | 520  |      |      |  |

| t <sub>ON0</sub>        | Startup on-time                        | $V_{IN} = 12 \text{ V}, V_{VDDQSNS} = 0 \text{ V}$                                                                                       |      | 125  |      |      |  |

| t <sub>ON(min)</sub>    | Minimum on-time                        | T <sub>A</sub> = 25°C                                                                                                                    |      | 100  |      | ns   |  |

| t <sub>OFF(min)</sub>   | Minimum off-time                       | T <sub>A</sub> = 25°C                                                                                                                    |      | 350  |      |      |  |

| ZERO CURR               | ENT COMPARATOR                         |                                                                                                                                          |      |      |      |      |  |

| V <sub>ZC</sub>         | Zero current comparator offset         |                                                                                                                                          | -6   | 0    | 6    | mV   |  |

| OUTPUT DRI              | VERS                                   |                                                                                                                                          |      |      |      |      |  |

|                         | DD\/LL registeres                      | Source, I <sub>DRVH</sub> = -100 mA                                                                                                      |      | 3    | 6    |      |  |

| $R_{DRVH}$              | DRVH resistance                        | Sink, I <sub>DRVH</sub> = 100 mA                                                                                                         |      | 0.9  | 3    | 3    |  |

| D                       | DDV// manintage = -                    | Source, I <sub>DRVL</sub> = -100 mA                                                                                                      |      | 3    | 6    | Ω    |  |

| $R_{DRVL}$              | DRVL resistance                        | Sink, I <sub>DRVL</sub> = 100 mA                                                                                                         |      | 0.9  | 3    | 3    |  |

|                         | Decid Co.                              | LL-low to DRVL-on                                                                                                                        |      | 10   |      |      |  |

| $t_D$                   | Dead time                              | DRVL-off to DRVH-on                                                                                                                      |      | 20   |      | ns   |  |

over operating free-air temperature range,  $V_{V5IN} = 5 V$ , VLDOIN is connected to VDDQ output (unless otherwise noted)

|                        | PARAMETER                             | TEST CONDITIONS                                                                         | MIN   | TYP   | MAX   | UNIT   |

|------------------------|---------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| INTERNAL B             | ST DIODE                              |                                                                                         |       |       |       |        |

| V <sub>FBST</sub>      | Forward voltage                       | $V_{V5IN-VBST}$ , $I_F = 10 \text{ mA}$                                                 | 0.58  | 0.8   | 1.1   | V      |

| I <sub>VBSTLK</sub>    | VBST leakage current                  | V <sub>VBST</sub> = 34 V, V <sub>LL</sub> = 28 V, V <sub>VDDQ</sub> = 2.6 V             |       | 0.1   | 1.11  | μA     |

| PROTECTIO              | NS                                    |                                                                                         | - "   |       |       |        |

| .,                     |                                       | V <sub>PGND-CS</sub> , PGOOD = HI, V <sub>CS</sub> < 0.5 V                              | 47    | 60    | 70    | >/     |

| V <sub>OCL</sub>       | Current limit threshold               | V <sub>PGND-CS</sub> , PGOOD = LO, V <sub>CS</sub> < 0.5 V                              | 18    | 30    | 40    | mV     |

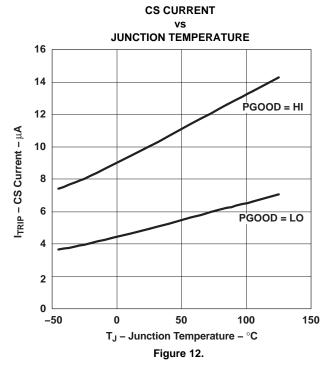

|                        |                                       | V <sub>CS</sub> > 4.5 V, PGOOD = HI                                                     | 4     | 10    | 20    |        |

| I <sub>TRIP</sub>      | Current sense sink current            | V <sub>CS</sub> > 4.5 V, PGOOD = LO                                                     | 2     | 5     | 10    | μΑ     |

| TC <sub>ITRIP</sub>    | TRIP current temperature coefficient  | $R_{DS(on)}$ sense scheme, On the basis of $T_A = 25^{\circ}C^{(1)}$                    |       | 4500  |       | ppm/°C |

| V <sub>OCL(off)</sub>  | Overcurrent protection COMP offset    | $(V_{V5IN-CS} - V_{PGND-LL}), V_{V5IN-CS} = 60 \text{ mV},$<br>$V_{CS} > 4.5 \text{ V}$ | -7    | 0     | 7     | .,     |

| V <sub>R(trip)</sub>   | Current limit threshold setting range | V <sub>V5IN-CS</sub>                                                                    | 30    |       | 150   | mV     |

| POWERGOO               | D COMPARATOR                          |                                                                                         | *     |       | '     |        |

|                        |                                       | PG in from lower                                                                        | 92%   | 95%   | 98%   |        |

| $V_{TVDDQPG}$          | VDDQ powergood threshold              | PG in from higher                                                                       | 102%  | 105%  | 108%  |        |

|                        |                                       | PG hysteresis                                                                           |       | 5%    |       |        |

| I <sub>PG(max)</sub>   | PGOOD sink current                    | V <sub>VTT</sub> = 0 V, V <sub>PGOOD</sub> = 0.5 V                                      | 2.3   | 7.5   |       | mA     |

| t <sub>PG(del)</sub>   | PGOOD delay time                      | Delay for PG in                                                                         | 78    | 130   | 205   | μs     |

| ` '                    | AGE LOCKOUT AND LOGIC T               | HRESHOLD                                                                                |       |       | I     |        |

|                        | V5IN UVLO threshold                   | Wake up                                                                                 | 3.6   | 4     | 4.4   |        |

| $V_{UVV5IN}$           | voltage                               | Hysteresis                                                                              | 0.19  | 0.3   | 0.41  |        |

|                        | MODE threshold                        | No discharge                                                                            | 4.7   |       |       |        |

| $V_{THMODE}$           |                                       | Non-tracking discharge                                                                  |       |       | 0.08  |        |

|                        |                                       | 2.5 V output                                                                            | 0.075 | 0.150 | 0.255 | V      |

| V <sub>THVDDQSET</sub> | VDDQSET threshold voltage             | 1.8 V output                                                                            | 3.45  | 4     | 4.55  |        |

| V <sub>IH</sub>        | High-level input voltage              | S3, S5                                                                                  | 2.2   |       |       |        |

| V <sub>IL</sub>        | Low-level input voltage               | S3, S5                                                                                  |       |       | 0.3   |        |

| V <sub>IHYST</sub>     | Hysteresis voltage                    | S3, S5                                                                                  |       | 0.2   |       |        |

| V <sub>INLEAK</sub>    | Logic input leakage current           | S3, S5, MODE                                                                            | -1    |       | 1     |        |

| V <sub>INVDDQSET</sub> | Input leakage/ bias current           | VDDQSET                                                                                 | -1    |       | 1     | μΑ     |

|                        | TAGE AND OVERVOLTAGE PR               | OTECTION                                                                                |       |       |       |        |

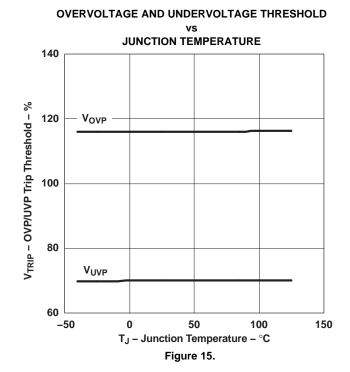

|                        | VDDQ OVP trip threshold               | OVP detect                                                                              | 109%  | 115%  | 121%  |        |

| $V_{OVP}$              | voltage                               | Hysteresis                                                                              |       | 5%    |       |        |

| t <sub>OVPDEL</sub>    | VDDQ OVP propagation delay            | •                                                                                       |       | 1.5   |       | μs     |

|                        |                                       | UVP detect                                                                              |       | 70%   |       |        |

| $V_{UVP}$              | Output UVP trip threshold             | Hysteresis                                                                              |       | 10%   |       |        |

| t <sub>UVPDEL</sub>    | Output UVP propagation delay          |                                                                                         |       | 32    |       | cycle  |

| t <sub>UVPEN</sub>     | Output UVP enable delay               |                                                                                         |       | 1007  |       | Syons  |

| THERMAL SI             |                                       | 1                                                                                       | 1     |       |       |        |

|                        |                                       | Shutdown temperature                                                                    |       | 160   |       |        |

| $T_{SDN}$              | Thermal SDN threshold <sup>(1)</sup>  | Hysteresis                                                                              |       | 10    |       | °C     |

<sup>(1)</sup> Specified by design. Not production tested.

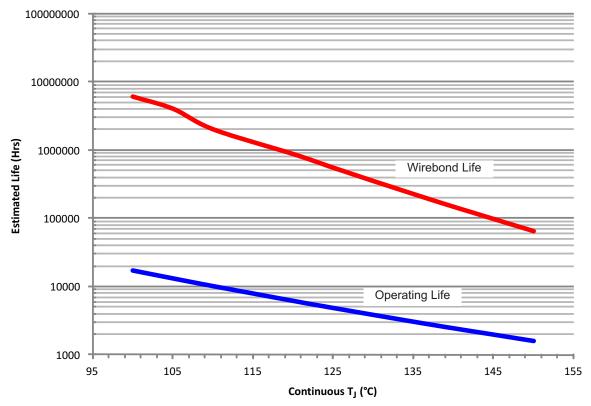

- (1) See datasheet for absolute maximum and minimum recommended operating conditions.

- (2) Sillicon operating life design goal is 10 years at 110°C junction temperature.

Figure 1. Operating and Wirebond Life Derating Chart

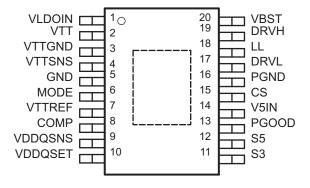

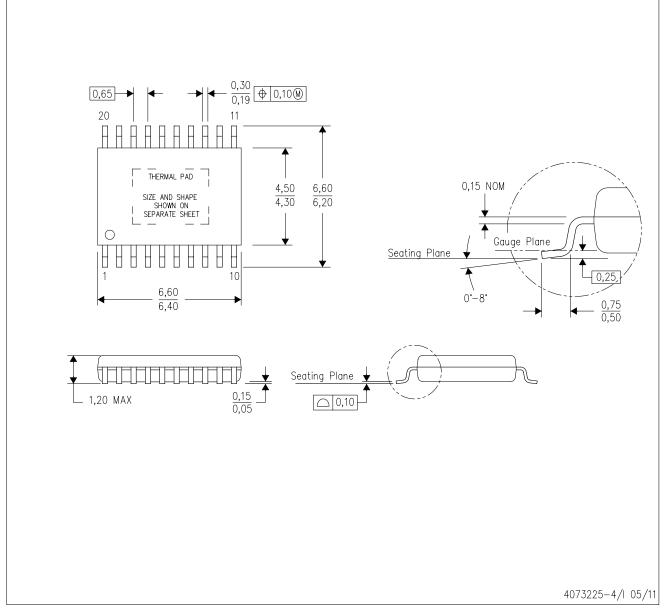

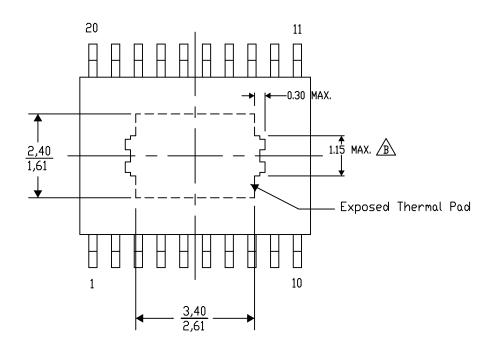

### **DEVICE INFORMATION**

### **TERMINAL FUNCTIONS**

| TERMINAL |     |     |                                                                                                                                                                                                                                     |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                         |

| NAME     | PWP |     |                                                                                                                                                                                                                                     |

| COMP     | 8   | I/O | Output of the transconductance amplifier for phase compensation. Connect to V5IN to disable gm amplifier and use D-CAP™ mode.                                                                                                       |

| CS       | 15  | I/O | Current sense comparator input (-) for resistor current sense scheme. Or overcurrent trip voltage setting input for R <sub>DS(on)</sub> current sense scheme if connected to V5IN through the voltage setting resistor.             |

| DRVH     | 19  | 0   | Switching (top) MOSFET gate drive output.                                                                                                                                                                                           |

| DRVL     | 17  | 0   | Rectifying (bottom) MOSFET gate drive output.                                                                                                                                                                                       |

| GND      | 5   | -   | Signal ground. Connect to minus terminal of the VTT LDO output capacitor.                                                                                                                                                           |

| LL       | 18  | I/O | Switching (top) MOSFET gate driver return. Current sense comparator input (-) for R <sub>DS(on)</sub> current sense.                                                                                                                |

| MODE     | 6   | I   | Discharge mode setting pin. See VDDQ and VTT Discharge Control section.                                                                                                                                                             |

| PGND     | 16  | _   | Ground for rectifying (bottom) MOSFET gate driver. Also current sense comparator input(+) and ground for powergood circuit.                                                                                                         |

| PGOOD    | 13  | 0   | Powergood signal open drain output, In HIGH state when VDDQ output voltage is within the target range.                                                                                                                              |

| S3       | 11  | 1   | S3 signal input.                                                                                                                                                                                                                    |

| S5       | 12  | I   | S5 signal input.                                                                                                                                                                                                                    |

| V5IN     | 14  | I   | 5-V power supply input for internal circuits and MOSFET gate drivers.                                                                                                                                                               |

| VBST     | 20  | I/O | Switching (top) MOSFET driver bootstrap voltage input.                                                                                                                                                                              |

| VDDQSET  | 10  | I   | VDDQ output voltage setting pin. See VDDQ Output Voltage Selection section.                                                                                                                                                         |

| VDDQSNS  | 9   | I/O | VDDQ reference input for VTT and VTTREF. Power supply for the VTTREF. Discharge current sinking terminal for VDDQ Non-tracking discharge. Output voltage feedback input for VDDQ output if VDDQSET pin is connected to V5IN or GND. |

| VLDOIN   | 1   | I   | Power supply for the VTT LDO.                                                                                                                                                                                                       |

| VTT      | 2   | 0   | Power output for the VTT LDO.                                                                                                                                                                                                       |

| VTTGND   | 3   | -   | Power ground output for the VTT LDO.                                                                                                                                                                                                |

| VTTREF   | 7   | 0   | VTTREF buffered reference output.                                                                                                                                                                                                   |

| VTTSNS   | 4   | I   | Voltage sense input for the VTT LDO. Connect to plus terminal of the VTT LDO output capacitor.                                                                                                                                      |

### PWP PACKAGE (TOP VIEW)

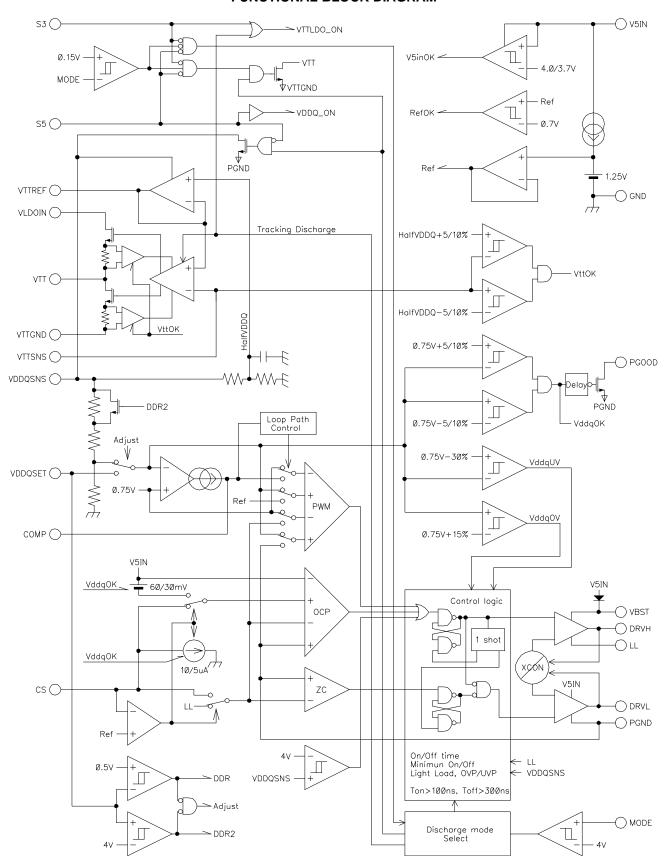

### **FUNCTIONAL BLOCK DIAGRAM**

### DETAILED DESCRIPTION

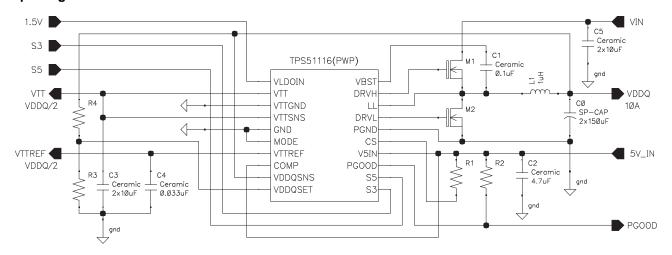

The TPS51116 is an integrated power management solution which combines a synchronous buck controller, a 10-mA buffered reference and a high-current sink/source low-dropout linear regulator (LDO) in a small 20-pin HTSSOP package or a 24-pin QFN package. Each of these rails generates VDDQ, VTTREF and VTT that required with DDR/DDR2/DDR3/LPDDR3 memory systems. The switch mode power supply (SMPS) portion employs external N-channel MOSFETs to support high current for DDR/DDR3/LPDDR3 memory VDD/VDDQ. The preset output voltage is selectable from 2.5 V or 1.8 V. User-defined output voltage is also possible and can be adjustable from 0.75 V to 3 V. Input voltage range of the SMPS is 3 V to 28 V. The SMPS runs an adaptive on-time PWM operation at high-load condition and automatically reduces frequency to keep excellent efficiency down to several mA. Current sensing scheme uses either R<sub>DS(on)</sub> of the external rectifying MOSFET for a low-cost, loss-less solution, or an optional sense resistor placed in series to the rectifying MOSFET for more accurate current limit. The output of the switcher is sensed by VDDQSNS pin to generate one-half VDDQ for the 10-mA buffered reference (VTTREF) and the VTT active termination supply. The VTT LDO can source and sink up to 3-A peak current with only 20-µF (two 10-µF in parallel) ceramic output capacitors. VTTREF tracks VDDQ/2 within ±1% of VDDQ. VTT output tracks VTTREF within ±20 mV at no load condition while ±40 mV at full load. The LDO input can be separated from VDDQ and optionally connected to a lower voltage by using VLDOIN pin. This helps reducing power dissipation in sourcing phase. TheTPS51116 is fully compatible to JEDEC DDR/DDR2 specifications at S3/S5 sleep state (see Table 2). The part has two options of output discharge function when both VTT and VDDQ are disabled. The tracking discharge mode discharges VDDQ and VTT outputs through the internal LDO transistors and then VTT output tracks half of VDDQ voltage during discharge. The non-tracking discharge mode discharges outputs using internal discharge MOSFETs which are connected to VDDQSNS and VTT. The current capability of these discharge FETs are limited and discharge occurs more slowly than the tracking discharge. These discharge functions can be disabled by selecting non-discharge mode.

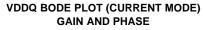

### **VDDQ SMPS, Dual PWM Operation Modes**

The main control loop of the SMPS is designed as an adaptive on-time pulse width modulation (PWM) controller. It supports two control schemes which are a current mode and a proprietary D-CAP™ mode. D-CAP™ mode uses internal compensation circuit and is suitable for low external component count configuration with an appropriate amount of ESR at the output capacitor(s). Current mode control has more flexibility, using external compensation network, and can be used to achieve stable operation with very low ESR capacitor(s) such as ceramic or specialty polymer capacitors.

These control modes are selected by the COMP terminal connection. If the COMP pin is connected to V5IN, TPS51116 works in the D-CAP™ mode, otherwise it works in the current mode. VDDQ output voltage is monitored at a feedback point voltage. If VDDQSET is connected to V5IN or GND, this feedback point is the output of the internal resistor divider inside VDDQSNS pin. If an external resistor divider is connected to VDDQSET pin, VDDQSET pin itself becomes the feedback point (see *VDDQ Output Voltage Selection* section).

At the beginning of each cycle, the synchronous high-side MOSFET is turned on, or becomes ON state. This MOSFET is turned off, or becomes OFF state, after internal one shot timer expires. This one shot is determined by  $V_{IN}$  and  $V_{OUT}$  to keep frequency fairly constant over input voltage range, hence it is called adaptive on-time control (see PWM Frequency and Adaptive On-Time Control section). The MOSFET is turned on again when feedback information indicates insufficient output voltage and inductor current information indicates below the overcurrent limit. Repeating operation in this manner, the controller regulates the output voltage. The synchronous bottom or the rectifying MOSFET is turned on each OFF state to keep the conduction loss minimum. The rectifying MOSFET is turned off when inductor current information detects zero level. This enables seamless transition to the reduced frequency operation at light load condition so that high efficiency is kept over broad range of load current.

In the current mode control scheme, the transconductance amplifier generates a target current level corresponding to the voltage difference between the feedback point and the internal 750 mV reference. During the *OFF* state, the PWM comparator monitors the inductor current signal as well as this target current level, and when the inductor current signal comes lower than the target current level, the comparator provides *SET* signal to initiate the next *ON* state. The voltage feedback gain is adjustable outside the controller device to support various types of output MOSFETs and capacitors. In the D-CAP<sup>TM</sup> mode, the transconductance amplifier is disabled and the PWM comparator compares the feedback point voltage and the internal 750 mV reference during the *OFF* state. When the feedback point comes lower than the reference voltage, the comparator provides *SET* signal to initiate the next *ON* state.

### **VDDQ SMPS, Light Load Condition**

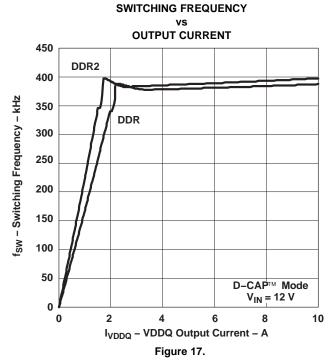

TPS51116 automatically reduces switching frequency at light load condition to maintain high efficiency. This reduction of frequency is achieved smoothly and without increase of V<sub>OUT</sub>ripple or load regulation. Detail operation is described as follows. As the output current decreases from heavy load condition, the inductor current is also reduced and eventually comes to the point that its *valley* touches zero current, which is the boundary between continuous conduction and discontinuous conduction modes. The rectifying MOSFET is turned off when this zero inductor current is detected. As the load current further decreased, the converter runs in discontinuous conduction mode and it takes longer and longer to discharge the output capacitor to the level that requires next *ON* cycle. The ON-time is kept the same as that in the heavy load condition. In reverse, when the output current increase from light load to heavy load, switching frequency increases to the constant 400 kHz as the inductor current reaches to the continuous conduction. The transition load point to the light load operation I<sub>OUT(LL)</sub> (i.e. the threshold between continuous and discontinuous conduction mode) can be calculated in Equation 1:

$$I_{\text{OUT(LL)}} = \frac{1}{2 \times L \times f} \times \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times V_{\text{OUT}}}{V_{\text{IN}}}$$

where

f is the PWM switching frequency (400 kHz)

(1)

Switching frequency versus output current in the light load condition is a function of L, f,  $V_{IN}$  and  $V_{OUT}$ , but it decreases almost proportional to the output current from the  $I_{OUT(LL)}$  given above. For example, it is 40 kHz at  $I_{OUT(LL)}/10$  and 4 kHz at  $I_{OUT(LL)}/100$ .

### **Low-Side Driver**

The low-side driver is designed to drive high-current, low- $R_{DS(on)}$ , N-channel MOSFET(s). The drive capability is represented by the internal resistance, which is 3  $\Omega$  for V5IN to DRVL and 0.9  $\Omega$  for DRVL to PGND. A dead-time to prevent shoot through is internally generated between high-side MOSFET off to low-side MOSFET on, and low-side MOSFET off to high-side MOSFET on. 5-V bias voltage is delivered from V5IN supply. The instantaneous drive current is supplied by an input capacitor connected between V5IN and GND. The average drive current is equal to the gate charge at  $V_{GS}$  = 5 V times switching frequency. This gate drive current as well as the high-side gate drive current times 5 V makes the driving power which needs to be dissipated from TPS51116 package.

### **High-Side Driver**

The high-side driver is designed to drive high-current, low on-resistance, N-channel MOSFET(s). When configured as a floating driver, 5-V bias voltage is delivered from V5IN supply. The average drive current is also calculated by the gate charge at  $V_{GS}$  = 5V times switching frequency. The instantaneous drive current is supplied by the flying capacitor between VBST and LL pins. The drive capability is represented by the internal resistance, which is 3  $\Omega$  for VBST to DRVH and 0.9  $\Omega$  for DRVH to LL.

### **Current Sensing Scheme**

In order to provide both good accuracy and cost effective solution, TPS51116 supports both of external resistor sensing and MOSFET  $R_{DS(on)}$  sensing. For resistor sensing scheme, an appropriate current sensing resistor should be connected between the source terminal of the low-side MOSFET and PGND. CS pin is connected to the MOSFET source terminal node. The inductor current is monitored by the voltage between PGND pin and CS pin. For  $R_{DS(on)}$  sensing scheme, CS pin should be connected to V5IN through the trip voltage setting resistor,  $R_{TRIP}$ . In this scheme, CS terminal sinks 10- $\mu$ A  $I_{TRIP}$  current and the trip level is set to the voltage across the  $R_{TRIP}$ . The inductor current is monitored by the voltage between PGND pin and LL pin so that LL pin should be connected to the drain terminal of the low-side MOSFET.  $I_{TRIP}$  has 4500ppm/°C temperature slope to compensate the temperature dependency of the  $R_{DS(on)}$ . In either scheme, PGND is used as the positive current sensing node so that PGND should be connected to the proper current sensing device, i.e. the sense resistor or the source terminal of the low-side MOSFET.

### **PWM Frequency and Adaptive On-Time Control**

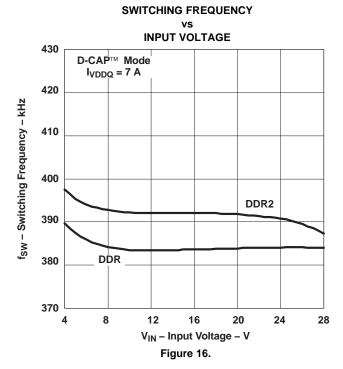

TPS51116 includes an adaptive on-time control scheme and does not have a dedicated oscillator on board. However, the device runs with fixed 400-kHz pseudo-constant frequency by feed-forwarding the input and output voltage into the on-time one-shot timer. The on-time is controlled inverse proportional to the input voltage and proportional to the output voltage so that the duty ratio is kept as  $V_{OUT}/V_{IN}$  technically with the same cycle time. Although the TPS51116 does not have a pin connected to VIN, the input voltage is monitored at LL pin during the *ON* state. This helps pin count reduction to make the part compact without sacrificing its performance. In order to secure minimum ON-time during startup, feed-forward from the output voltage is enabled after the output becomes 750 mV or larger.

### **VDDQ Output Voltage Selection**

TPS51116 can be used for both of DDR ( $V_{VDDQ} = 2.5 \text{ V}$ ) and DDR2 ( $V_{VDDQ} = 1.8 \text{ V}$ ) power supply and adjustable output voltage (0.75 V <  $V_{VDDQ} < 3 \text{ V}$ ) by connecting VDDQSET pin as shown in Table 1. Use the adjustable output voltage scheme for a DDR3 ( $V_{VDDQ} = 1.5 \text{ V}$ ) or LPDDR3 ( $V_{VDDQ} = 1.2 \text{ V}$ ) application.

**Table 1. VDDQSET and Output Voltages**

| VDDQSET      | VDDQ (V)   | VTTREF and VTT          | NOTE                                                |

|--------------|------------|-------------------------|-----------------------------------------------------|

| GND          | 2.5        | V <sub>VDDQSNS</sub> /2 | DDR                                                 |

| V5IN         | 1.8        | V <sub>VDDQSNS</sub> /2 | DDR2                                                |

| FB Resistors | Adjustable | V <sub>VDDQSNS</sub> /2 | 0.75 V < V <sub>VDDQ</sub> < 3 V <sup>(1)</sup> (2) |

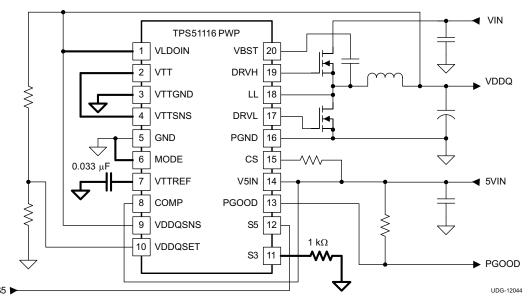

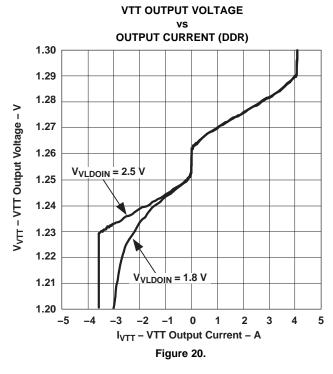

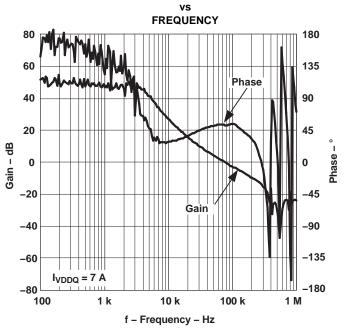

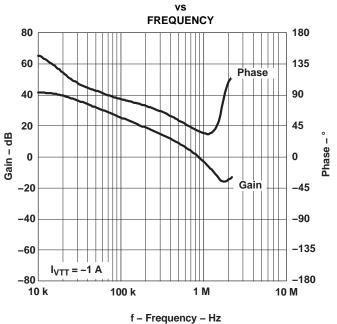

### **VTT Linear Regulator and VTTREF**

TPS51116 integrates high performance low-dropout linear regulator that is capable of sourcing and sinking current up to 3 A. This VTT linear regulator employs ultimate fast response feedback loop so that small ceramic capacitors are enough to keep tracking the VTTREF within  $\pm 40$  mV at all conditions including fast load transient. To achieve tight regulation with minimum effect of wiring resistance, a remote sensing terminal, VTTSNS, should be connected to the positive node of VTT output capacitor(s) as a separate trace from VTT pin. For stable operation, total capacitance of the VTT output terminal can be equal to or greater than 20  $\mu$ F. It is recommended to attach two 10- $\mu$ F ceramic capacitors in parallel to minimize the effect of ESR and ESL. If ESR of the output capacitor is greater than 2 m $\Omega$ , insert an RC filter between the output and the VTTSNS input to achieve loop stability. The RC filter time constant should be almost the same or slightly lower than the time constant made by the output capacitor and its ESR. VTTREF block consists of on-chip 1/2 divider, LPF and buffer. This regulator also has sink and source capability up to 10 mA. Bypass VTTREF to GND by a 0.033- $\mu$ F ceramic capacitor for stable operation.

When VTT is not required in the design, following treatment is strongly recommended.

- Connect VLDOIN to VDDQSNS.

- Tie VTTSNS to VTT, and remove capacitors from VTT to float.

- Connect VTTGND and MODE to GND (Non-tracking discharge mode as shown in Table 3)

- Maintain a 0.033-µF capacitor connected at VTTREF.

- Pull down S3 to GND with 1  $k\Omega$  of resistance.

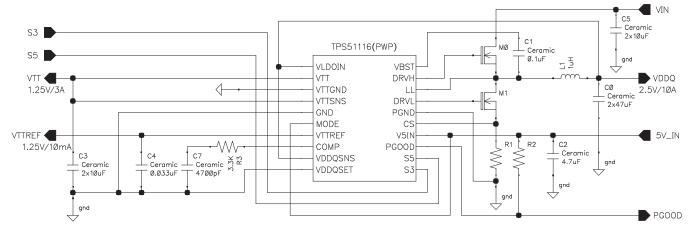

A typical circuit for this application is shown in Figure 2

V<sub>VDDQ</sub>≥ 1.2 V when used as VLDOIN.

<sup>(2)</sup> Including DDR3 and LPDDR3

Figure 2. Application Circuit When VTT Is Not Required

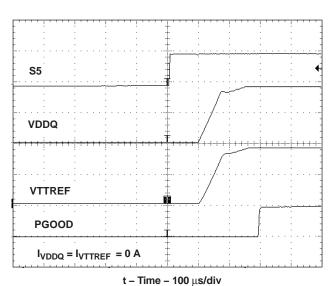

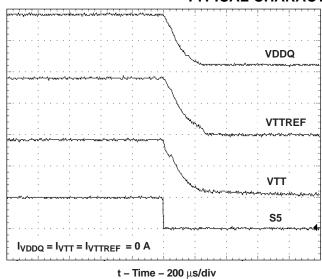

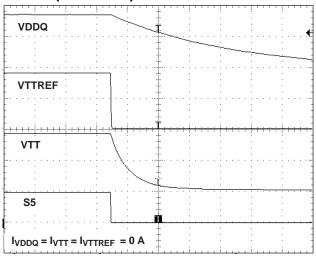

### Controling Outputs Using the S3 and S5 Pins

In the DDR/DDR3/LPDDR3 memory applications, it is important to keep VDDQ always higher than VTT/VTTREF including both start-up and shutdown. TPS51116 provides this management by simply connecting both the S3 and S5 pins to the sleep-mode signals such as SLP\_S3 and SLP\_S5 in the notebook PC system. All of VDDQ, VTTREF and VTT are turned on at S0 state (S3 = S5 = high). In S3 state (S3 = low, S5 = high), VDDQ and VTTREF voltages are kept on while VTT is turned off and left at high impedance (high-Z) state. The VTT output is floated and does not sink or source current in this state. In S4/S5 states (S3 = S5 = low), all of the three outputs are disabled. Outputs are discharged to ground according to the discharge mode selected by MODE pin (see *VDDQ and VTT Discharge Control* section). Each state code represents as follow; S0 = full ON, S3 = suspend to RAM (STR), S4 = suspend to disk (STD), S5 = soft OFF. (See Table 2)

STATE **S5 VDDQ VTTREF** VTT **S3** S0 ΗΙ ΗΙ ON ON ON ON S3 LO ΗΙ ON OFF (High-Z) S4/S5 LO LO OFF (Discharge) Off (Discharge) OFF (Discharge)

Table 2. Sleep Mode Control Using the S3 and S5 Pins

### **Soft-Start and Powergood**

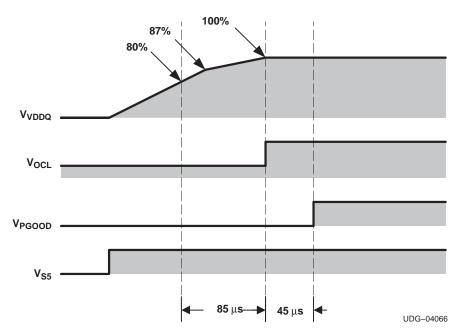

The soft start function of the SMPS is achieved by ramping up reference voltage and two-stage current clamp. At the starting point, the reference voltage is set to 650 mV (87% of its target value) and the overcurrent threshold is set half of the nominal value. When UVP comparator detects VDDQ become greater than 80% of the target, the reference voltage is raised toward 750 mV using internal 4-bit DAC. This takes approximately 85  $\mu$ s. The overcurrent threshold is released to nominal value at the end of this period. The powergood signal waits another 45  $\mu$ s after the reference voltage reaches 750 mV and the VDDQ voltage becomes good (above 95% of the target voltage), then turns off powergood open-drain MOSFET.

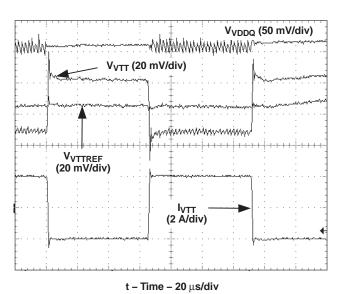

The soft-start function of the VTT LDO is achieved by current clamp. The current limit threshold is also changed in two stages using an internal powergood signal dedicated for LDO. During VTT is below the powergood threshold, the current limit level is cut into 60% (2.2 A). This allows the output capacitors to be charged with low and constant current that gives linear ramp up of the output. When the output comes up to the good state, the overcurrent limit level is released to normal value (3.8 A). TPS51116 has an independent counter for each output, but the PGOOD signal indicates only the status of VDDQ and does not indicate VTT powergood externally. See Figure 3.

Figure 3. VDDQ Soft-Start and Powergood Timing

Soft-start duration,  $t_{VDDQSS}$ ,  $t_{VTTSS}$  are functions of output capacitances.

$$t_{VDDQSS} = \frac{2 \times C_{VDDQ} \times V_{VDDQ} \times 0.8}{I_{VDDQOCP}} + 85 \,\mu\text{s}$$

where

•

$$I_{VDDQOCP}$$

is the current limit value for VDDQ switcher calculated by Equation 5

$$\frac{C_{VTT} \times V_{VTT}}{I_{VTTOCL}}$$

(2)

where

•

$$I_{VTTOCL} = 2.2 \text{ A (typ)}$$

In both Equation 2 and Equation 3 , no load current during start-up are assumed. Note that both switchers and the LDO do not start up with full load condition.

### **VDDQ and VTT Discharge Control**

TPS51116 discharges VDDQ, VTTREF and VTT outputs when S3 and S5 are both low. There are two different discharge modes. The discharge mode can be set by connecting MODE pin as shown in Table 3.

**Table 3. Discharge Selection**

| MODE | DISCHARGE MODE         |  |

|------|------------------------|--|

| V5IN | No discharge           |  |

| VDDQ | Tracking discharge     |  |

| GND  | Non-tracking discharge |  |

When in tracking-discharge mode, TPS51116 discharges outputs through the internal VTT regulator transistors and VTT output tracks half of VDDQ voltage during this discharge. Note that VDDQ discharge current flows via VLDOIN to LDOGND thus VLDOIN must be connected to VDDQ output in this mode. The internal LDO can handle up to 3 A and discharge quickly. After VDDQ is discharged down to 0.2 V, the internal LDO is turned off and the operation mode is changed to the non-tracking-discharge mode.

When in non-tracking-discharge mode, TPS51116 discharges outputs using internal MOSFETs which are connected to VDDQSNS and VTT. The current capability of these MOSFETs are limited to discharge slowly. Note that VDDQ discharge current flows from VDDQSNS to PGND in this mode. In no discharge mode, TPS51116 does not discharge any output charge.

### Current Protection for VDDQ

The SMPS has cycle-by-cycle overcurrent limiting control. The inductor current is monitored during the *OFF* state and the controller keeps the OFF state during the inductor current is larger than the overcurrent trip level. The trip level and current sense scheme are determined by CS pin connection (see *Current Sensing Scheme* section). For resistor sensing scheme, the trip level, V<sub>TRIP</sub>, is fixed value of 60 mV.

For  $R_{DS(on)}$  sensing scheme, CS terminal sinks 10  $\mu A$  and the trip level is set to the voltage across this  $R_{TRIP}$  resistor.

$$V_{TRIP} (mV) = R_{TRIP} (k\Omega) \times 10 (\mu A)$$

(4)

As the comparison is done during the *OFF* state,  $V_{TRIP}$  sets valley level of the inductor current. Thus, the load current at overcurrent threshold,  $I_{OCP}$ , can be calculated as shown in Equation 5.

$$I_{OCP} = \frac{V_{TRIP}}{R_{DS(on)}} + \frac{I_{RIPPLE}}{2} = \frac{V_{TRIP}}{R_{DS(on)}} + \frac{1}{2 \times L \times f} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

(5)

In an overcurrent condition, the current to the load exceeds the current to the output capacitor thus the output voltage tends to fall down. If the output voltage becomes less than Powergood level, the  $V_{TRIP}$  is cut into half and the output voltage tends to be even lower. Eventually, it crosses the undervoltage protection threshold and shutdown.

### **Current Protection for VTT**

The LDO has an internally fixed constant overcurrent limiting of 3.8 A while operating at normal condition. This trip point is reduced to 2.2 A before the output voltage comes within ±5% of the target voltage or goes outside of ±10% of the target voltage.

### Overvoltage and Undervoltage Protection for VDDQ

TPS51116 monitors a resistor divided feedback voltage to detect overvoltage and undervoltage. If VDDQSET is connected to V5IN or GND, the feedback voltage is made by an internal resistor divider inside VDDQSNS pin. If an external resistor divider is connected to VDDQSET pin, the feedback voltage is VDDQSET voltage itself. When the feedback voltage becomes higher than 115% of the target voltage, the OVP comparator output goes high and the circuit latches as the high-side MOSFET driver OFF and the low-side MOSFET driver ON.

Also, TPS51116 monitors VDDQSNS voltage directly and if it becomes greater than 4 V TPS51116 turns off the high-side MOSFET driver. When the feedback voltage becomes lower than 70% of the target voltage, the UVP comparator output goes high and an internal UVP delay counter begins counting. After 32 cycles, TPS51116 latches OFF both top and low-side MOSFETs. This function is enabled after 1007 cycles of SMPS operation to ensure startup.

### V5IN Undervoltage Lockout (UVLO) Protection

TPS51116 has 5-V supply undervoltage lockout protection (UVLO). When the V5IN voltage is lower than UVLO threshold voltage, SMPS, VTTLDO and VTTREF are shut off. This is a non-latch protection.

### **V5IN Input Capacitor**

Add a ceramic capacitor with a value between 1.0  $\mu$ F and 4.7  $\mu$ F placed close to the V5IN pin to stabilize 5 V from any parasitic impedance from the supply.

### Thermal Shutdown

TPS51116 monitors the temperature of itself. If the temperature exceeds the threshold value, 160°C (typ), SMPS, VTTLDO and VTTREF are shut off. This is a non-latch protection and the operation is resumed when the device is cooled down by about 10°C.

### **APPLICATION INFORMATION**

### **Loop Compensation and External Parts Selection**

### **Current Mode Operation**

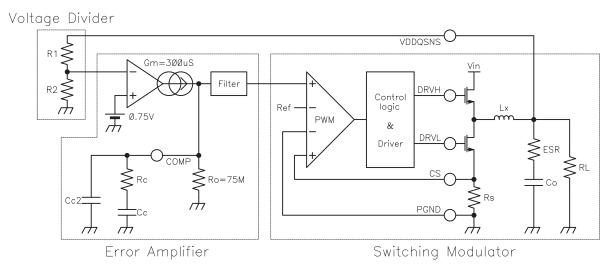

A buck converter using TPS51116 current mode operation can be partitioned into three portions, a voltage divider, an error amplifier and a switching modulator. By linearizing the switching modulator, we can derive the transfer function of the whole system. Because current mode scheme directly controls the inductor current, the modulator can be linearized as shown in Figure 4.

Figure 4. Linearizing the Modulator

Here, the inductor is located inside the local feedback loop and its inductance does not appear in the small signal model. As a result, a modulated current source including the power inductor can be modeled as a current source with its transconductance of  $1/R_S$  and the output capacitor represent the modulator portion. This simplified model is applicable in the frequency space up to approximately a half of the switching frequency. One note is, although the inductance has no influence to small signal model, it has influence to the large signal model as it limits slew rate of the current source. This means the buck converter's load transient response, one of the large signal behaviors, can be improved by using smaller inductance without affecting the loop stability.

Total open loop transfer function of the whole system is given by Equation 6.

$$H(s) = H1(s) \times H2(s) \times H3(s)$$

(6)

Assuming RL>>ESR,  $R_O>>R_C$  and  $C_C>>C_{C2}$ , each transfer function of the three blocks is shown starting with Equation 7.

$$H_1(s) = \frac{R2}{(R2 + R1)}$$

(7)

$$H_{2}(s) = -gm \times \frac{R_{O} (1 + s \times C_{C} \times R_{C})}{(1 + s \times C_{C} \times R_{O}) (1 + s \times C_{C2} \times R_{C})}$$

(8)

$$H_3(s) = \frac{(1 + s \times C_O \times ESR)}{(1 + s \times C_O \times RL)} \times \frac{RL}{R_S}$$

(9)

There are three poles and two zeros in H(s). Each pole and zero is given by the following five equations.

$$\omega_{P1} = \frac{1}{\left(C_C \times R_O\right)} \tag{10}$$

$$\omega_{P2} = \frac{1}{\left(C_{O} \times RL\right)} \tag{11}$$

$$\omega_{P3} = \frac{1}{\left(C_{C2} \times R_{C}\right)} \tag{12}$$

$$\omega_{Z1} = \frac{1}{\left(C_C \times R_C\right)} \tag{13}$$

$$\omega_{Z2} = \frac{1}{\left(C_{O} \times ESR\right)} \tag{14}$$

Usually, each frequency of those poles and zeros is lower than the 0 dB frequency, f<sub>0</sub>. However, the f<sub>0</sub> should be kept under 1/3 of the switching frequency to avoid effect of switching circuit delay. The f<sub>0</sub> is given by Equation 15.

$$f_0 = \frac{1}{2\pi} \times \frac{R1}{R1 + R2} \times \frac{gm}{C_O} \times \frac{R_C}{R_S} = \frac{1}{2\pi} \times \frac{0.75}{V_{OUT}} \times \frac{gm}{C_O} \times \frac{R_C}{R_S}$$

$$(15)$$

Based on small signal analysis above, the external components can be selected by following manner.

1. **Choose the inductor.** The inductance value should be determined to give the ripple current of approximately 1/4 to 1/2 of maximum output current.

$$L = \frac{1}{I_{\text{IND(ripple)}} \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}} = \frac{2}{I_{\text{OUT(max)}} \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(16)

The inductor also needs to have low DCR to achieve good efficiency, as well as enough room above peak inductor current before saturation. The peak inductor current can be estimated as shown in Equation 17.

$$I_{\text{IND(peak)}} = \frac{V_{\text{TRIP}}}{R_{\text{DS(on)}}} + \frac{1}{L \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(17)

- 2. Choose rectifying (bottom) MOSFET. When R<sub>DS(on)</sub> sensing scheme is selected, the rectifying MOSFET's on-resistance is used as this R<sub>S</sub> so that lower R<sub>DS(on)</sub> does not always promise better performance. In order to clearly detect inductor current, minimum R<sub>S</sub> recommended is to give 15 mV or larger ripple voltage with the inductor ripple current. This promises smooth transition from CCM to DCM or vice versa. Upper side of the R<sub>DS(on)</sub> is of course restricted by the efficiency requirement, and usually this resistance affects efficiency more at high-load conditions. When using external resistor current sensing, there is no restriction for low R<sub>DS(on)</sub>. However, the current sensing resistance R<sub>S</sub> itself affects the efficiency

- 3. Choose output capacitor(s). When organic semiconductor capacitors (OS-CON) or specialty polymer capacitors (SP-CAP) are used, ESR to achieve required ripple value at stable state or transient load conditions determines the amount of capacitor(s) need, and capacitance is then enough to satisfy stable operation. The peak-to-peak ripple value can be estimated by ESR times the inductor ripple current for stable state, or ESR times the load current step for a fast transient load response. When ceramic capacitor(s) are used, the ESR is usually small enough to meet ripple requirement. In contrast, transient undershoot and overshoot driven by output capacitance becomes the key factor in determining the capacitor(s) required.

- 4. **Determine**  $f_0$  and calculate  $R_C$  using Equation 18. Note that higher  $R_C$  shows faster transient response in cost of unstableness. If the transient response is not enough even with high  $R_C$  value, try increasing the out put capacitance. Recommended  $f_0$  is  $f_{OSC}/4$ . Then  $R_C$  can be derived by Equation 19.

$$R_{C} \le 2\pi \times f_{0} \times \frac{V_{OUT}}{0.75} \times \frac{C_{O}}{gm} \times R_{S}$$

(18)

$$R_{C} = 2.8 \times V_{OUT} \times C_{O} [\mu F] \times R_{S} [m\Omega]$$

(19)

Calculate C<sub>C2</sub>. Purpose of this capacitance is to cancel zero caused by ESR of the output capacitor. When ceramic capacitor(s) are used, no need for C<sub>C2</sub>.

$$\omega_{z2} = \frac{1}{\left(C_{O} \times ESR\right)} = \omega_{p3} = \frac{1}{\left(C_{C2} \times R_{C}\right)}$$

(20)

$$C_{C2} = \frac{C_{O} \times ESR}{R_{C}}$$

(21)

6. Calculate  $C_C$ . The purpose of  $C_C$  is to cut DC component to obtain high DC feedback gain. However, as it causes phase delay, another zero to cancel this effect at  $f_0$  frequency is need. This zero,  $\omega z 1$ , is determined by Cc and Rc. Recommended  $\omega z 1$  is 10 times lower to the  $f_0$  frequency.

$$f_{z1} = \frac{1}{2\pi \times C_C \times R_C} = \frac{f_0}{10}$$

(22)

7. When using adjustable mode, determine the value of R1 and R2. .

$$R1 = \frac{V_{OUT} - 0.75}{0.75} \times R2 \tag{23}$$

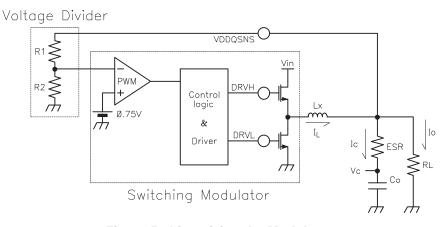

### **D-CAP™** Mode Operation

A buck converter system using D-CAP™ Mode can be simplified as below.

Figure 5. Linearizing the Modulator

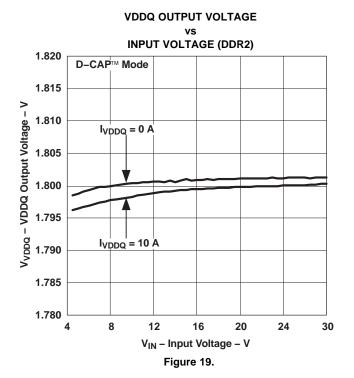

The PWM comparator compares the VDDQSNS voltage divided by R1 and R2 with internal reference voltage, and determines the timing to turn on the high-side MOSFET. The gain and speed of the comparator is high enough to keep the voltage at the beginning of each on cycle (or the end of off cycle) substantially constant. The DC output voltage may have line regulation due to ripple amplitude that slightly increases as the input voltage increase.

For the loop stability, the 0-dB frequency,  $f_0$ , defined below need to be lower than 1/3 of the switching frequency.

$$f_0 = \frac{1}{2\pi \times \mathsf{ESR} \times \mathsf{C}_\mathsf{O}} \le \frac{f_\mathsf{SW}}{3} \tag{24}$$

As  $f_0$  is determined solely by the output capacitor's characteristics, loop stability of D-CAP<sup>TM</sup> mode is determined by the capacitor's chemistry. For example, specialty polymer capacitors (SP-CAP) have  $C_0$  in the order of several 100  $\mu$ F and ESR in range of 10 m $\Omega$ . These makes  $f_0$  in the order of 100 kHz or less and the loop is then stable. However, ceramic capacitors have  $f_0$  at more than 700 kHz, which is not suitable for this operational mode.

Although D-CAP™ mode provides many advantages such as ease-of-use, minimum external components configuration and extremely short response time, due to not employing an error amplifier in the loop, sufficient amount of feedback signal needs to be provided by external circuit to reduce jitter level.

The required signal level is approximately 15 mV at comparing point. This gives  $V_{RIPPLE} = (V_{OUT}/0.75) \times 15 \text{ (mV)}$  at the output node. The output capacitor's ESR should meet this requirement.

The external components selection is much simple in D-CAP™ mode.

- 1. **Choose inductor.** This section is the same as the current mode. Please refer to the instructions in the *Current Mode Operation* section.

- 2. Choose output capacitor(s). Organic semiconductor capacitor(s) or specialty polymer capacitor(s) are recommended. Determine ESR to meet required ripple voltage above. A quick approximation is shown in

Equation 25.

$$\mathsf{ESR} = \frac{\mathsf{V}_{\mathsf{OUT}} \times 0.015}{\mathsf{I}_{\mathsf{RIPPLE}} \times 0.75} \approx \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{I}_{\mathsf{OUT}(\mathsf{max})}} \times 60 \ [\mathsf{m}\Omega] \tag{25}$$

### **Thermal Design**

Primary power dissipation of TPS51116 is generated from VTT regulator. VTT current flow in both source and sink directions generate power dissipation from the part. In the source phase, potential difference between VLDOIN and VTT times VTT current becomes the power dissipation, W<sub>DSRC</sub>.

$$W_{DSRC} = (V_{VLDOIN} - V_{VTT}) \times I_{VTT}$$

(26)

In this case, if VLDOIN is connected to an alternative power supply lower than VDDQ voltage, power loss can be decreased.

For the sink phase, VTT voltage is applied across the internal LDO regulator, and the power dissipation, W<sub>DSNK</sub>, is calculated by Equation 27:

$$W_{DSNK} = V_{VTT} \times I_{VTT}$$

(27)

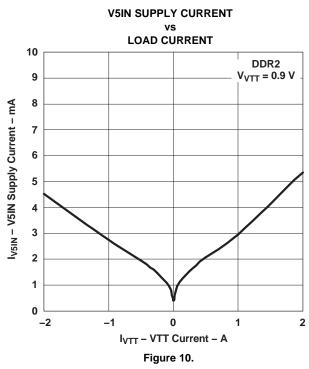

Because this device does not sink AND source the current at the same time and  $I_{VTT}$  varies rapidly with time, actual power dissipation need to be considered for thermal design is an average of above value. Another power consumption is the current used for internal control circuitry from V5IN supply and VLDOIN supply. V5IN supports both the internal circuit and external MOSFETs drive current. The former current is in the VLDOIN supply can be estimated as 1.5 mA or less at normal operational conditions.

These powers need to be effectively dissipated from the package. Maximum power dissipation allowed to the package is calculated by Equation 28,

$$W_{PKG} = \frac{T_{J(max)} - T_{A(max)}}{\theta_{JA}}$$

(28)

### where

- T<sub>I(max)</sub> is 125°C

- T<sub>A(max)</sub> is the maximum ambient temperature in the system

- $\theta_{JA}$  is the thermal resistance from the silicon junction to the ambient

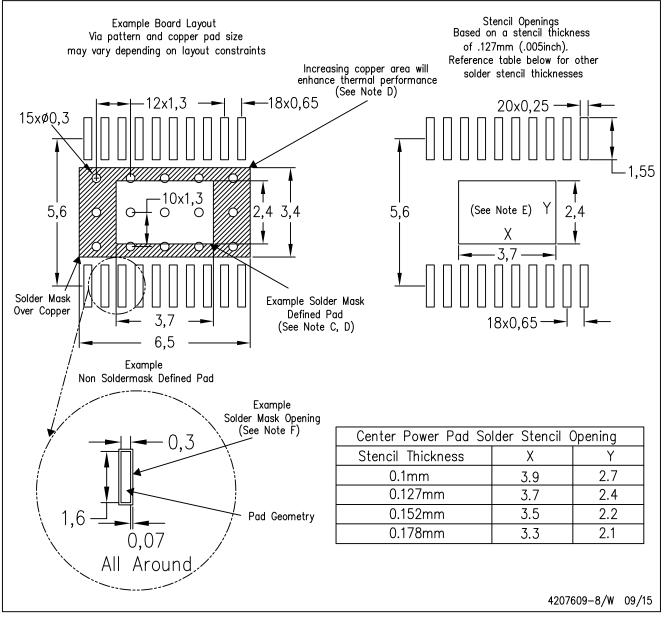

This thermal resistance strongly depends on the board layout. TPS51116 is assembled in a thermally enhanced PowerPAD™ package that has exposed die pad underneath the body. For improved thermal performance, this die pad needs to be attached to ground trace via thermal land on the PCB. This ground trace acts as a heat sink/spread. The typical thermal resistance, 39.6°C/W, is achieved based on a 6.5 mm × 3.4 mm thermal land with eight vias without air flow. It can be improved by using larger thermal land and/or increasing vias number. Further information about PowerPAD™ and its recommended board layout is described in (SLMA002). This document is available at http:\\www.ti.com.

### **Layout Considerations**

Certain points must be considered before designing a layout using the TPS51116.

- PCB trace defined as LL node, which connects to source of switching MOSFET, drain of rectifying MOSFET and high-voltage side of the inductor, should be as short and wide as possible.

- Consider adding a small snubber circuit, consisting of a 3-Ω resitor and a 1-nF capacitor, between LL and PGND in case a high-frequency surge is observed on the LL voltage waveform.

- All sensitive analog traces such as VDDQSNS, VTTSNS and CS should placed away from high-voltage switching nodes such as LL, DRVL or DRVH nodes to avoid coupling.

- VLDOIN should be connected to VDDQ output with short and wide trace. If different power source is used for VLDOIN, an input bypass capacitor should be placed to the pin as close as possible with short and wide connection.

- The output capacitor for VTT should be placed close to the pin with short and wide connection in order to avoid additional ESR and/or ESL of the trace.

- VTTSNS should be connected to the positive node of VTT output capacitor(s) as a separate trace from the

high current power line and is strongly recommended to avoid additional ESR and/or ESL. If it is needed to

sense the voltage of the point of the load, it is recommended to attach the output capacitor(s) at that point.

Also, it is recommended to minimize any additional ESR and/or ESL of ground trace between GND pin and

the output capacitor(s).

- Consider adding LPF at VTTSNS when the ESR of the VTT output capacitor(s) is larger than 2 m $\Omega$ .

- VDDQSNS can be connected separately from VLDOIN. Remember that this sensing potential is the reference voltage of VTTREF. Avoid any noise generative lines.

- Negative node of VTT output capacitor(s) and VTTREF capacitor should be tied together by avoiding common impedance to the high current path of the VTT source/sink current.

- GND (Signal GND) pin node represents the reference potential for VTTREF and VTT outputs. Connect GND

to negative nodes of VTT capacitor(s), VTTREF capacitor and VDDQ capacitor(s) with care to avoid

additional ESR and/or ESL. GND and PGND (power ground) should be connected together at a single point.

- PGND is the return path for rectifying MOSFET gate drive. Use 0.65 mm (25mil) or wider trace. Connect to source of rectifying MOSFET with shortest possible path.

- The trace from the CS pin should avoid high-voltage switching nodes such as those for LL, VBST, DRVH, DRVL or PGOOD.