**PGA305**

ZHCSIP5 - AUGUST 2018

# 适用于压力传感器的 PGA305 信号调节器和发送器

## 1 特性

#### • 模拟 特性

- 适用于阻性桥式传感器的模拟前端

- 传感器灵敏度可调节范围: 1mV/V 至 135mV/V

- 片上温度传感器

- 可编程增益

- 适用于信号通道的 24 位 Σ-Δ 模数转换器

- 适用干温度通道的 24 位 Σ-Δ 模数转换器

- 14 位输出数模转换器 (DAC)

## • 数字 特性

- 整个温度范围内的 FSO 精度 < 0.1%

- 系统响应时间 < 220µs</li>

- 三阶偏移、增益和非线性温度补偿

- 诊断功能

- 集成 EEPROM 用于存储器件操作、校准数据和 用户数据

#### • 外设特性

- 可通过 I<sup>2</sup>C 接口实现数据读取和器件配置

- 单线接口,可通过电源引脚进行通信,无需额外 使用线路

- 4mA 至 20mA 电流回路接口

- 比例电压输出和绝对电压输出

- 电源管理控制

- 模拟低压检测

#### • 通用特性

- 工业温度范围: -40°C 至 150°C

#### - 电源:

- 片上电源管理,支持 3.3V 至 30V 的宽电源 电压范围

- 集成反向保护电路

## 2 应用

- 压力传感发送器和变送器

- 液位计、流量计

- 电阻场发射器

## 3 说明

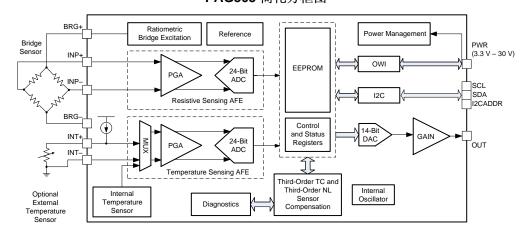

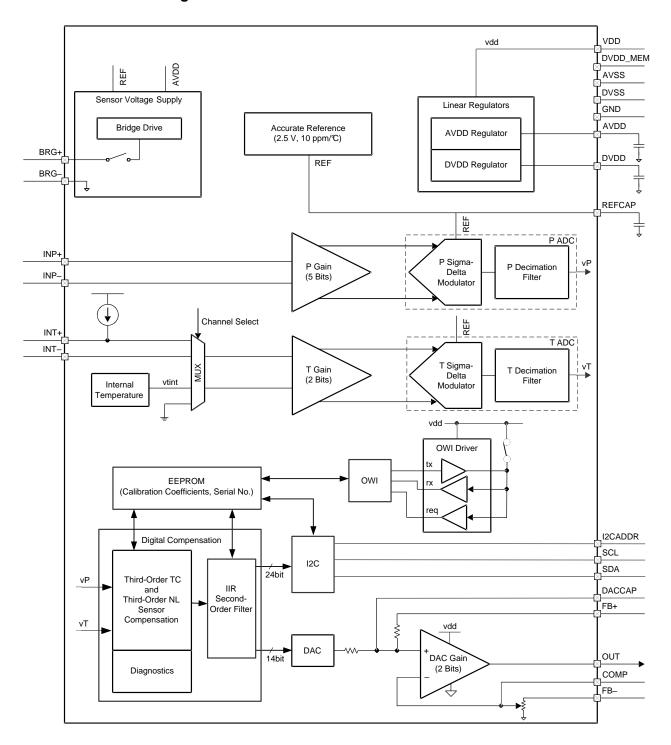

PGA305 器件提供了一个适用于压阻式和应力计式压感元件的接口。该器件是一套完整的片上系统 (SoC)解决方案,具有可编程模拟前端 (AFE)、ADC 和数字信号处理功能,可直接连接传感元件。此外,PGA305器件还集成了稳压器和振荡器,最大程度地减少了外部组件数。PGA305器件可以采用三阶温度和非线性补偿来实现高精度。该器件还可以使用集成 I<sup>2</sup>C 接口或单线制串行接口 (OWI) 来实现外部通信并简化系统校准流程。集成 DAC 支持绝对电压、比例电压以及 4mA至 20mA 的电流回路输出。

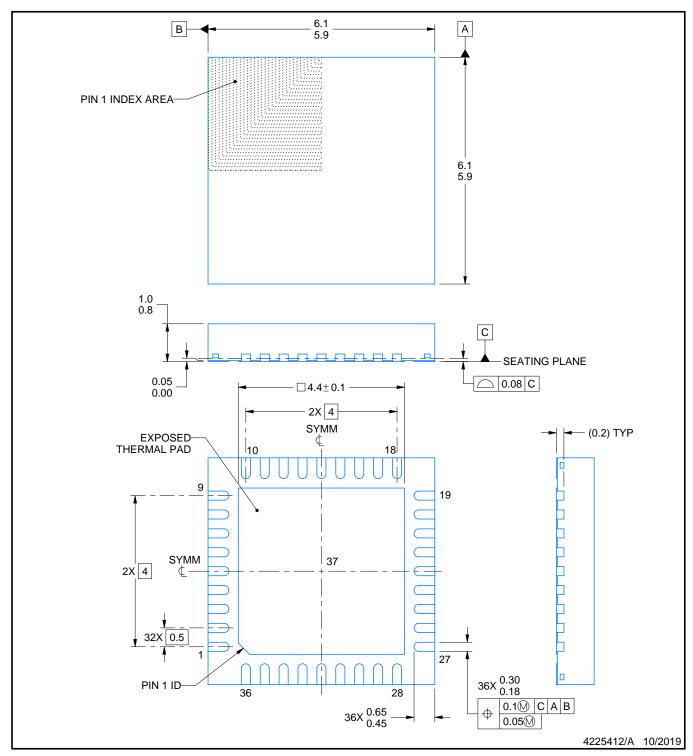

### 器件信息<sup>(1)</sup>

| 器件型号   | 封装        | 封装尺寸 (标称值)      |

|--------|-----------|-----------------|

| PAG305 | VQFN (36) | 6.00mm x 6.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

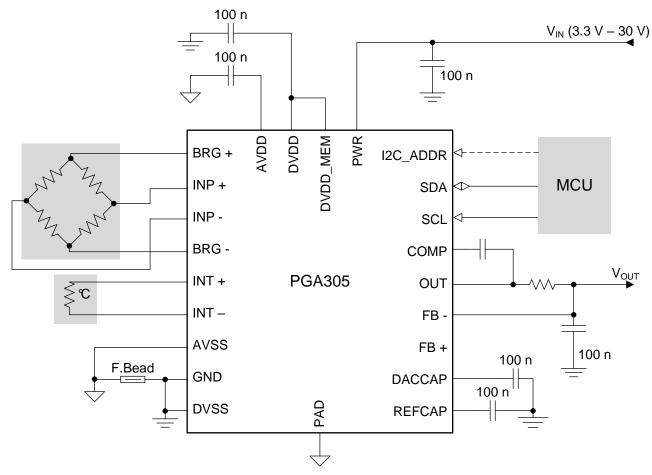

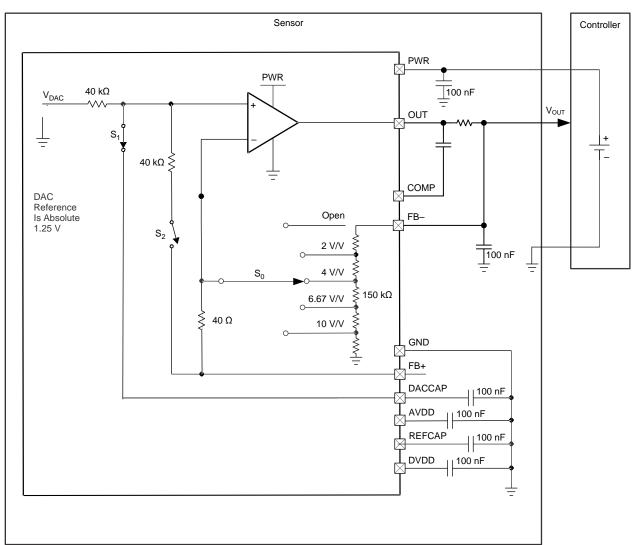

## PAG305 简化方框图

$\triangle$

| 1 | 特性 1                                                            |    | 6.17 Electrical Characteristics – DAC Output        |         |

|---|-----------------------------------------------------------------|----|-----------------------------------------------------|---------|

| 2 | 应用 1                                                            |    | 6.18 Electrical Characteristics – DAC Gain          | 9       |

| 3 | 说明1                                                             |    | 6.19 Electrical Characteristics - Non-Volatile Memo | ry . 10 |

| 4 | 修订历史记录 2                                                        |    | 6.20 Electrical Characteristics – Diagnostics       | 10      |

| 5 | Pin Configuration and Functions                                 |    | 6.21 Operating Characteristics                      | 1       |

| 6 | Specifications 5                                                |    | 6.22 I <sup>2</sup> C Interface Timing Requirements | 13      |

| • | 6.1 Absolute Maximum Ratings                                    |    | 6.23 Timing Diagram                                 | 13      |

|   | 6.2 ESD Ratings                                                 |    | 6.24 Typical Characteristics                        | 14      |

|   | 6.3 Recommended Operating Conditions                            | 7  | Detailed Description                                | 18      |

|   | 6.4 Thermal Information                                         |    | 7.1 Overview                                        | 1!      |

|   | 6.5 Electrical Characteristics – Reverse Voltage                |    | 7.2 Functional Block Diagram                        | 16      |

|   | Protection                                                      |    | 7.3 Feature Description                             | 17      |

|   | 6.6 Electrical Characteristics – Regulators                     |    | 7.4 Device Functional Modes                         | 46      |

|   | 6.7 Electrical Characteristics – Internal Reference 6           |    | 7.5 Register Maps                                   | 46      |

|   | 6.8 Electrical Characteristics – Bridge Sensor Supply 6         | 8  | Application and Implementation                      | 64      |

|   | 6.9 Electrical Characteristics – Temperature Sensor             |    | 8.1 Application Information                         | 64      |

|   | Supply                                                          |    | 8.2 Typical Applications                            | 64      |

|   | 6.10 Electrical Characteristics – Internal Temperature          | 9  | Power Supply Recommendations                        | 70      |

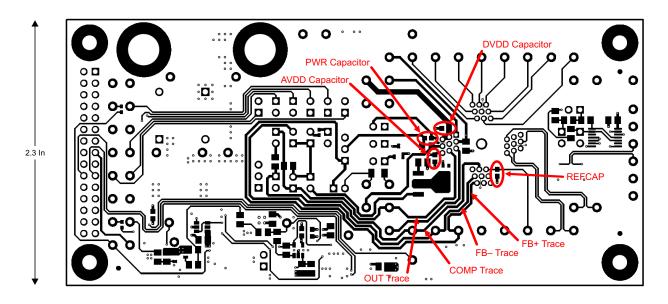

|   | Sensor 7                                                        | 10 | Layout                                              |         |

|   | 6.11 Electrical Characteristics – P Gain (Chopper               |    | 10.1 Layout Guidelines                              | 70      |

|   | Stabilized)                                                     |    | 10.2 Layout Example                                 |         |

|   | 6.12 Electrical Characteristics – P Analog-to-Digital Converter | 11 | 器件和文档支持                                             | 73      |

|   | 6.13 Electrical Characteristics – T Gain (Chopper               |    | <b>11.1</b> 接收文档更新通知                                |         |

|   | Stabilized) 8                                                   |    | 11.2 社区资源                                           | 7       |

|   | 6.14 Electrical Characteristics – T Analog-to-Digital           |    | 11.3 商标                                             | 7       |

|   | Converter 9                                                     |    | 11.4 静电放电警告                                         |         |

|   | 6.15 Electrical Characteristics – One-Wire Interface 9          |    | 11.5 术语表                                            |         |

|   | 6.16 I <sup>2</sup> C Interface                                 | 12 | 机械、封装和可订购信息                                         |         |

|   |                                                                 |    |                                                     |         |

# 4 修订历史记录

| 日期      | 修订版本 | 说明      |

|---------|------|---------|

| 2018年8月 | *    | 最初发布版本。 |

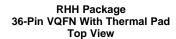

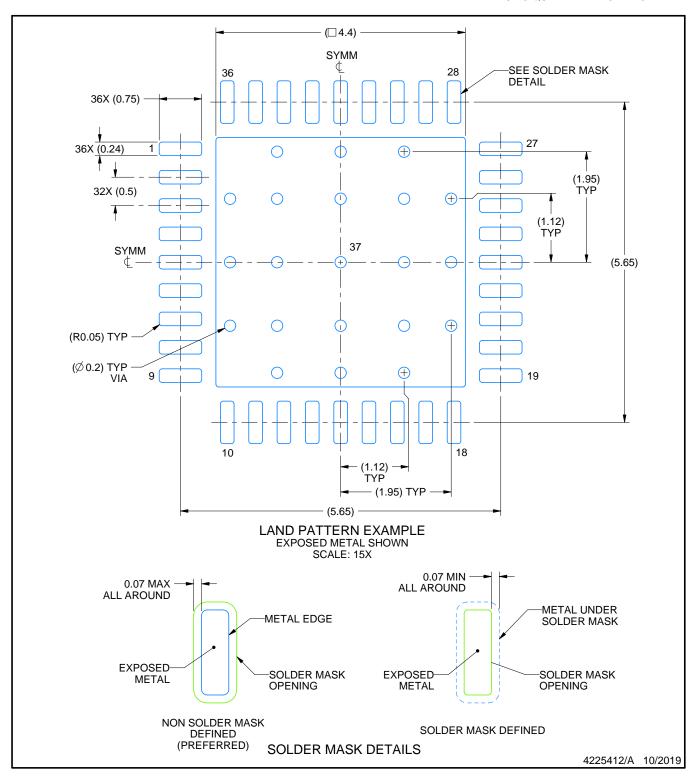

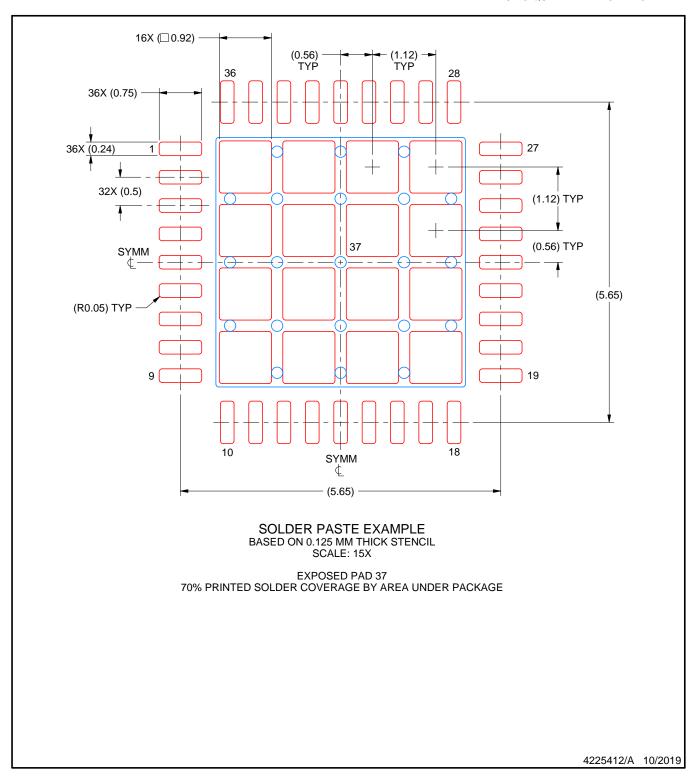

# 5 Pin Configuration and Functions

NU = Make no external connection.

## **Pin Functions**

|             | PIN                                             | 1/0 | DESCRIPTION                                 |  |  |

|-------------|-------------------------------------------------|-----|---------------------------------------------|--|--|

| NAME        | NO.                                             | I/O | DESCRIPTION                                 |  |  |

| AVDD        | 9                                               | 0   | AVDD regulator output.                      |  |  |

| AVSS        | 23                                              | _   | Analog ground.                              |  |  |

| BRG+        | 15                                              | 0   | Bridge drive, positive.                     |  |  |

| BRG-        | 14                                              | 0   | Bridge drive, negative.                     |  |  |

| COMP        | 13                                              | I   | Output amplifier compensation.              |  |  |

| DACCAP      | 6                                               | 0   | DAC capacitor.                              |  |  |

| DVDD        | 3                                               | 0   | VDD regulator output.                       |  |  |

| DVDD_MEM    | 2                                               | 0   | Power supply for EEPROM and OTP.            |  |  |

| DVSS        | 32                                              | _   | Digital ground.                             |  |  |

| FB+         | 12                                              | I   | Feedback, positive.                         |  |  |

| FB-         | 11                                              | I   | Feedback, negative.                         |  |  |

| GND         | 10                                              | _   | Ground.                                     |  |  |

| I2CADDR     | 29                                              | I   | I <sup>2</sup> C chip address select.       |  |  |

| INP+        | 18                                              | I   | Resistive sensor positive input.            |  |  |

| INP-        | 17                                              | I   | Resistive sensor negative input.            |  |  |

| INT+        | 21                                              | I   | External temperature sensor positive input. |  |  |

| INT-        | 22                                              | I   | External temperature sensor negative input. |  |  |

| NU          | 1, 4, 7, 19, 20,<br>24 to 28, 30, 31,<br>34, 35 | _   | Do not connect.                             |  |  |

| OUT         | 8                                               | 0   | DAC gained output.                          |  |  |

| PWR         | 5                                               | I   | Input power supply.                         |  |  |

| REFCAP      | 16                                              | 0   | ADC reference capacitor.                    |  |  |

| SCL         | 36                                              | I/O | I <sup>2</sup> C clock.                     |  |  |

| SDA         | 33                                              | I/O | I <sup>2</sup> C data.                      |  |  |

| Thermal pad | _                                               |     | Connect to analog ground.                   |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

see (1)

|                                     |                                                                                                             | MIN  | MAX             | UNIT |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-----------------|------|

| PWR                                 | Supply voltage                                                                                              | -28  | 33              | V    |

|                                     | Voltage at sensor input pins: INP+, INP-, INT+, INT-                                                        | -0.3 | 2               | V    |

|                                     | Voltage at AVDD, AVSS, BRG+, BRG-, COMP, DACCAP, DVDD, DVDD_MEM, DVSS, FB-, GATE, REFCAP, SCL, SDA, I2CADDR | -0.3 | 3.6             | ٧    |

|                                     | Voltage at FB+ pin                                                                                          | -2   | $V_{PWR} + 0.3$ | V    |

|                                     | Voltage at OUT pin                                                                                          | -0.3 | 33              | V    |

| I <sub>PWR</sub> , short on OUT pin | Supply current                                                                                              |      | 25              | mA   |

| T <sub>Jmax</sub>                   | Maximum junction temperature                                                                                |      | 155             | °C   |

| T <sub>stg</sub>                    | Storage temperature                                                                                         | -40  | 150             | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT     |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|----------|

| V                  | Flootroototic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | V        |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | <b>v</b> |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                  |                                              |                                                                  | MIN | NOM | MAX              | UNIT |

|------------------|----------------------------------------------|------------------------------------------------------------------|-----|-----|------------------|------|

| V <sub>PWR</sub> | Power supply voltage                         |                                                                  | 3.3 |     | 30               | V    |

|                  | Slew rate                                    | V <sub>DD</sub> = 0 to 30 V                                      |     |     | 0.5              | V/µs |

|                  | Power supply current - normal operation      | No load on BRG, no load on DAC                                   |     | 2.5 |                  |      |

| I <sub>PWR</sub> | Power supply current - EEPROM programming    | While EEPROM is being programmed, no load on BRG, no load on DAC |     |     | 9 <sup>(1)</sup> | mA   |

| T <sub>A</sub>   | Operating ambient temperature                |                                                                  | -40 |     | 150              | °C   |

|                  | Programming temperature                      | EEPROM                                                           | -40 |     | 140              | °C   |

|                  | Start-up time (including analog and digital) | V <sub>PWR</sub> ramp rate 0.5 V/μs                              |     |     | 1                | ms   |

|                  | Capacitor on PWR pin                         |                                                                  | 10  |     |                  | nF   |

<sup>(1)</sup> Programming of the EEPROM results in an additional 6 mA of current on the PWR pin.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Thermal Information

|                      |                                              | PGA305     |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHH (VQFN) | UNIT |

|                      |                                              | 36 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 30.6       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 16.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 5.4        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 5.4        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics – Reverse Voltage Protection

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                                              | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|--------------------------------------------------------|-----------------|-----|---------|------|

| Reverse voltage                                        |                 | -28 |         | V    |

| Voltage drop across reverse voltage protection element |                 |     | 20      | mV   |

## 6.6 Electrical Characteristics - Regulators

|            | PARAMETER                | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|------------|--------------------------|----------------------------|-----|-----|-----|------|

| $V_{AVDD}$ | AVDD voltage             | C <sub>AVDD</sub> = 100 nF |     | 3   |     | V    |

| $V_{DVDD}$ | DVDD voltage – operating | C <sub>DVDD</sub> = 100 nF |     | 1.8 |     | V    |

### 6.7 Electrical Characteristics - Internal Reference

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------------|-----------------|-----|-----|-----|------|

| High-voltage reference voltage (1) |                 |     | 1.2 |     | V    |

| Accurate reference voltage         |                 |     | 2.5 |     | V    |

| Capacitor value on REFCAP pin      |                 |     | 100 |     | nF   |

<sup>(1)</sup> TEMP\_DRIFT = [(Value at TEMP – Value at 25°C) / (Value at 25°C ×  $\Delta$ TEMP)] × 10<sup>6</sup>.

## 6.8 Electrical Characteristics - Bridge Sensor Supply

|                                          | PARAMETER                    | TEST CONDITIONS                           | MIN | TYP  | MAX | UNIT |  |  |

|------------------------------------------|------------------------------|-------------------------------------------|-----|------|-----|------|--|--|

| BRG SUPPLY FOR RESISTIVE BRIDGE SENSORS  |                              |                                           |     |      |     |      |  |  |

| V <sub>BRG+</sub> –<br>V <sub>BRG-</sub> | Bridge supply voltage        | Bridge supply control bit = 0b00, no load |     | 2.5  |     |      |  |  |

|                                          |                              | Bridge supply control bit = 0b01, no load |     | 2    |     | V    |  |  |

|                                          |                              | Bridge supply control bit = 0b10, no load |     | 1.25 |     |      |  |  |

| I <sub>BRG</sub>                         | Current supply to the bridge |                                           |     |      | 1.5 | mA   |  |  |

| C <sub>BRG</sub>                         | Capacitive load              | $R_{BRG} = 20 \text{ k}\Omega$            |     |      | 2   | nF   |  |  |

# 6.9 Electrical Characteristics - Temperature Sensor Supply

|                       | PARAMETER                            | TEST CONDITIONS     | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------------|---------------------|-----|-----|-----|------|

| I <sub>TEMP</sub> SUF | PPLY FOR TEMPERATURE SENSOR          |                     |     |     |     |      |

|                       |                                      | Control bit = 0b000 |     | 25  |     | μA   |

|                       |                                      | Control bit = 0b001 |     | 50  |     | μΑ   |

| I <sub>TEMP</sub>     | Current supply to temperature sensor | Control bit = 0b010 |     | 100 |     | μΑ   |

|                       |                                      | Control bit = 0b011 |     | 500 |     | μΑ   |

|                       |                                      | Control bit = 0b1xx |     | OFF |     |      |

| C <sub>TEMP</sub>     | Capacitive load                      |                     |     |     | 100 | nF   |

|                       | Output impedance                     |                     |     | 15  |     | ΜΩ   |

# 6.10 Electrical Characteristics – Internal Temperature Sensor

| PARAMETER         | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|-----------------|-----|-----|-----|------|

| Temperature range |                 | -40 |     | 150 | °C   |

# 6.11 Electrical Characteristics - P Gain (Chopper Stabilized)

| PARAMETER           | TEST CONDITIONS | MIN TYP MAX | UNIT |

|---------------------|-----------------|-------------|------|

|                     | 00000, at dc    | 5           |      |

|                     | 00001           | 5.48        |      |

|                     | 00010           | 5.97        |      |

|                     | 00011           | 6.56        |      |

|                     | 00100           | 7.02        |      |

|                     | 00101           | 8           |      |

|                     | 00110           | 9.09        |      |

|                     | 00111           | 10          |      |

|                     | 01000           | 10.53       |      |

|                     | 01001           | 11.11       |      |

|                     | 01010           | 12.5        |      |

|                     | 01011           | 13.33       |      |

|                     | 01100           | 14.29       |      |

|                     | 01101           | 16          |      |

|                     | 01110           | 17.39       |      |

| Cain stans (5 hits) | 01111           | 18.18       | 1/// |

| Gain steps (5 bits) | 10000           | 19.05       | V/V  |

|                     | 10001           | 20          |      |

|                     | 10010           | 22.22       |      |

|                     | 10011           | 25          |      |

|                     | 10100           | 30.77       |      |

|                     | 10101           | 36.36       |      |

|                     | 10110           | 40          |      |

|                     | 10111           | 44.44       |      |

|                     | 11000           | 50          |      |

|                     | 11001           | 57.14       |      |

|                     | 11010           | 66.67       |      |

|                     | 11011           | 80          |      |

|                     | 11100           | 100         |      |

|                     | 11101           | 133.33      |      |

|                     | 11110           | 200         |      |

|                     | 11111           | 400         |      |

# TRUMENTS

## Electrical Characteristics - P Gain (Chopper Stabilized) (continued)

| PARAMETER                                   | TEST CONDITIONS                                                                       | MIN TYP MAX                                                            | UNIT   |

|---------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------|

| Gain bandwidth product                      |                                                                                       | 10                                                                     | MHz    |

| Input-referred noise density <sup>(1)</sup> | f = 0.1 Hz to 2 kHz, gain = 400 V/V,<br>sampling rate = 128 μs, across<br>temperature | 15                                                                     | nV/√Hz |

| Input offset voltage                        |                                                                                       | 10                                                                     | μV     |

| Input bias current                          |                                                                                       | 5                                                                      | nA     |

| Frequency response                          | Gain = 400 V/V, <1 kHz                                                                | ±0.1                                                                   | %V/V   |

| Common-mode voltage range                   |                                                                                       | Depends on selected gain, bridge supply and sensor span <sup>(2)</sup> | V      |

| Common-mode rejection ratio                 | f <sub>CM</sub> = 50 Hz at gain = 5 V/V                                               | 110                                                                    | dB     |

| Input impedance                             |                                                                                       | 10                                                                     | ΜΩ     |

- (1) Total input-referred noise including gain noise, ADC reference noise, ADC thermal noise, and ADC quantization noise.

- Common Mode at P Gain Input and Output: There are two constraints:

- (a) The single-ended voltage of the positive and negative pins at the P gain input must be between 0.3 V and 1.8 V. (b) The single-ended voltage of the positive and negative pins at the P gain output must be between 0.1 V and 2 V.

## 6.12 Electrical Characteristics – P Analog-to-Digital Converter

| PARAMETER                                                | TEST CONDITIONS | MIN                   | TYP                  | MAX  | UNIT |

|----------------------------------------------------------|-----------------|-----------------------|----------------------|------|------|

| Sigma-delta modulator frequency                          |                 |                       | 1                    |      | MHz  |

| ADC voltage input range                                  |                 | -2.5                  |                      | 2.5  | V    |

| Number of bits                                           |                 |                       | 24                   |      | bits |

| ADC 2s complement code for -2.5-<br>V differential input |                 | 800000 <sub>hex</sub> |                      |      |      |

| ADC 2s complement code for 0-V differential input        |                 | 000000 <sub>hex</sub> |                      |      |      |

| ADC 2s complement code for 2.5-V differential input      |                 | 71                    | FFFFF <sub>hex</sub> |      |      |

| INL Integral nonlinearity                                |                 |                       |                      | ±0.5 | LSB  |

## 6.13 Electrical Characteristics – T Gain (Chopper Stabilized)

| PARAMETER                    | TEST CONDITIONS                                             | MIN TYP MAX                                     | UNIT               |

|------------------------------|-------------------------------------------------------------|-------------------------------------------------|--------------------|

|                              | Gain control bits = 0b00 at dc                              | 1.33                                            |                    |

| Gain steps (2 bits)          | Gain control bits = 0b01                                    | 2                                               | V/V                |

| Cairi steps (2 bits)         | Gain control bits = 0b10                                    | 5                                               | V/ V               |

|                              | Gain control bits = 0b11                                    | 20                                              |                    |

| Gain bandwidth product       |                                                             | 350                                             | kHz                |

| Noise density <sup>(1)</sup> | f = 0.1 Hz to 100 Hz<br>at gain = 5 V/V, across temperature | 110                                             | nV/√ <del>Hz</del> |

| Input offset voltage         |                                                             | 95                                              | μV                 |

| Input bias current           |                                                             | 5                                               | nA                 |

| Frequency response           | Gain = 20 V/V, <100 Hz                                      | 0.335                                           | %V/V               |

| Common mode voltage range    |                                                             | Depends on selected gain and current supply (2) |                    |

| Common-mode rejection ratio  | f <sub>CM</sub> = 50 Hz                                     | 110                                             | dB                 |

| Input impedance              |                                                             | 1                                               | ΜΩ                 |

- (1) Total input-referred noise including gain noise, ADC reference noise, ADC thermal noise, and ADC quantization noise.

- Common Mode at T Gain Input and Output: There are two constraints:

- (a) The single-ended voltage of positive/negative pin at the T gain input should be between 5 mV and 1.8 V.

- (b) The single-ended voltage of positive/negative pin at the T gain output should be between 0.1 V and 2 V.

## 6.14 Electrical Characteristics - T Analog-to-Digital Converter

| PARAMETER                                            | TEST CONDITIONS | MIN                   | TYP | MAX  | UNIT |

|------------------------------------------------------|-----------------|-----------------------|-----|------|------|

| Sigma-delta modulator frequency                      |                 |                       | 1   |      | MHz  |

| ADC voltage input range                              |                 | -2.5                  |     | 2.5  | V    |

| Number of bits                                       |                 |                       | 24  |      | bits |

| ADC 2s complement code for –2.5-V differential input | 2s complement   | 800000 <sub>hex</sub> |     |      | LSB  |

| ADC 2s complement code for 0-V differential input    |                 | 000000 <sub>hex</sub> |     | LSB  |      |

| ADC 2s complement code for 2.5-V differential input  |                 | 7FFFF <sub>hex</sub>  |     | LSB  |      |

| INL Integral nonlinearity                            |                 |                       |     | ±0.5 | LSB  |

#### 6.15 Electrical Characteristics – One-Wire Interface

|         | PARAMETER                              | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|---------|----------------------------------------|-----------------|------|-----|------|------|

|         | Communication baud rate <sup>(1)</sup> |                 | 600  |     | 9600 | bps  |

| OWI_ENH | OWI activation high                    |                 | 5.95 |     |      | V    |

| OWI_ENL | OWI activation low                     |                 |      |     | 5.75 | V    |

| OWI_VIH | OWI transceiver Rx threshold for high  |                 | 4.8  |     | 5.1  | V    |

| OWI_VIL | OWI transceiver Rx threshold for low   |                 | 3.9  |     | 4.2  | V    |

| OWI_IOH | OWI transceiver Tx threshold for high  |                 | 500  |     | 1379 | μΑ   |

| OWI_IOL | OWI transceiver Tx threshold for low   |                 | 2    |     | 5    | μΑ   |

<sup>(1)</sup> OWI over power line does not work if there is an LDO between the supply to the sensor and the PWR pin, or if the OWI high and low voltages are greater than the regulated voltage.

## 6.16 I<sup>2</sup>C Interface

over operating free-air temperature range at  $V_{DD} = 5 \text{ V}$  (unless otherwise noted)

|                 | PARAMETER                | TEST CONDITIONS                                                      | MIN           | TYP | MAX           | UNIT     |

|-----------------|--------------------------|----------------------------------------------------------------------|---------------|-----|---------------|----------|

| V <sub>IH</sub> | High-level input voltage |                                                                      | 0.7 ×<br>AVDD |     |               | V        |

| V <sub>IL</sub> | Low-level input voltage  |                                                                      |               |     | 0.3 ×<br>AVDD | <b>V</b> |

| V <sub>OL</sub> | Low-level output voltage | I <sub>OL</sub> = 3 mA, I <sup>2</sup> C RATE configuration bit = 0  |               |     | 0.4           | <b>V</b> |

| V <sub>OL</sub> | Low-level output voltage | I <sub>OL</sub> = 20 mA, I <sup>2</sup> C RATE configuration bit = 1 |               |     | 0.4           | V        |

| $f_{SCL}$       | SCL clock frequency      |                                                                      |               | 400 | 800           | KBPS     |

# 6.17 Electrical Characteristics - DAC Output

| PARAMETER             | TEST CONDITIONS                 | MIN | TYP                   | MAX | UNIT |

|-----------------------|---------------------------------|-----|-----------------------|-----|------|

| DAC reference voltage | Reference bit = 1               |     | 1.25                  |     | \/   |

| DAC reference voltage | Reference bit = 0 (ratiometric) | 0.2 | 25 × V <sub>PWR</sub> |     | V    |

| DAC resolution        |                                 |     | 14                    |     | bits |

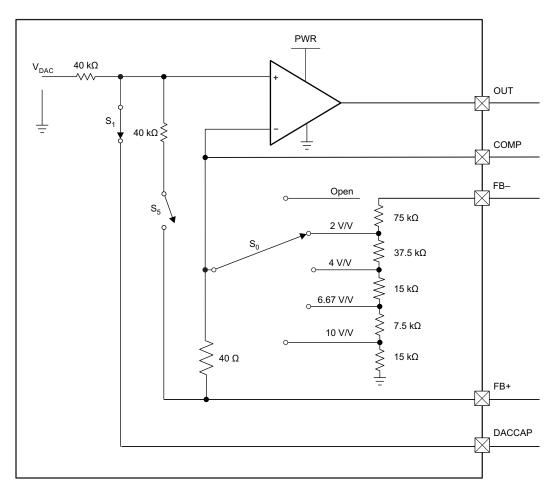

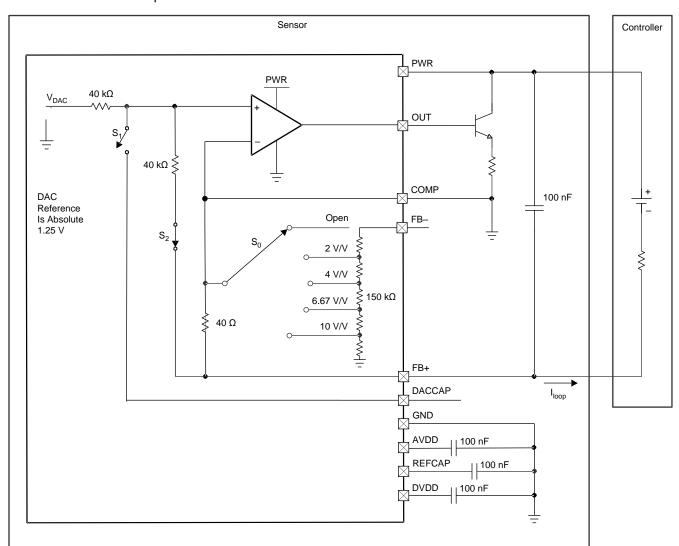

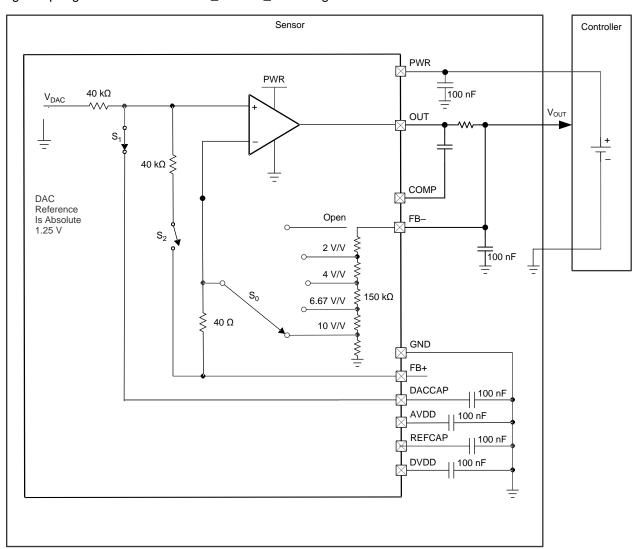

## 6.18 Electrical Characteristics - DAC Gain

| PARAMETER                   | TEST CONDITIONS | MIN | TYP  | MAX | UNIT  |

|-----------------------------|-----------------|-----|------|-----|-------|

| Buffer gain (see Figure 20) | 2×              |     | 2    |     |       |

|                             | 4×              |     | 4    |     | 1/0/  |

|                             | 6.67×           |     | 6.67 |     | V/V   |

|                             | 10×             |     | 10   |     |       |

| Current loop gain           |                 |     | 1001 |     | mA/mA |

# **Electrical Characteristics – DAC Gain (continued)**

| PARAMETER                     | TEST CONDITIONS                                | MIN | TYP | MAX  | UNIT |

|-------------------------------|------------------------------------------------|-----|-----|------|------|

| Gain-bandwidth product        |                                                |     | 1   |      | MHz  |

| Zero-code voltage (gain = 4x) | DAC code = 0000h, I <sub>DAC</sub> = 2.5 mA    |     |     | 20   | mV   |

| Full-code voltage (gain = 4x) | DAC code is 1FFFh, $I_{DAC} = -2.5 \text{ mA}$ | 4.8 |     |      | V    |

| Output current                | DAC code = 1FFFh , DAC code = 0000h            |     |     | ±2.5 | mA   |

| Short-circuit source current  | DAC code = 1FFFh                               |     | 27  |      | mA   |

| Short-circuit sink current    | DAC code = 0000h                               |     | 27  |      | mA   |

| Maximum conscitones           | Without compensation                           |     |     | 100  | pF   |

| Maximum capacitance           | With compensation                              |     |     | 100  | nF   |

# 6.19 Electrical Characteristics - Non-Volatile Memory

| PARAMETER |                    | TEST CONDITIONS | MIN | TYP | MAX  | UNIT   |

|-----------|--------------------|-----------------|-----|-----|------|--------|

| FEDDOM    | Size               |                 |     | 128 |      | bytes  |

|           | Erase-write cycles |                 |     |     | 1000 | cycles |

| EEPROM    | Programming time   | 1 8-byte page   |     |     | 8    | ms     |

|           | Data retention     |                 | 10  |     |      | years  |

## 6.20 Electrical Characteristics – Diagnostics

over operating ambient temperature range (unless otherwise noted)

|            | PARAMETER                                                   | TEST CONDIT | IONS |     | MIN TYP | MAX | UNIT                       |

|------------|-------------------------------------------------------------|-------------|------|-----|---------|-----|----------------------------|

| OSC_PWR_OV | Oscillator circuit supply overvoltage threshold             |             |      |     | 3.3     |     | V                          |

| OSC_PWR_UV | Oscillator circuit supply undervoltage threshold            |             |      |     | 2.7     |     | V                          |

| BRG_OV     | Resistive bridge sensor supply overvoltage threshold        |             |      |     | 10      |     | %V <sub>BRG</sub>          |

| BRG_UV     | Resistive bridge sensor<br>supply undervoltage<br>threshold |             |      |     | -10     |     | %Prog.<br>V <sub>BRG</sub> |

| AVDD_OV    | AVDD overvoltage threshold                                  |             |      |     | 3.3     |     | V                          |

| AVDD_UV    | AVDD undervoltage threshold                                 |             |      |     | 2.7     |     | V                          |

| DVDD_OV    | DVDD overvoltage threshold                                  |             |      |     | 2       |     | V                          |

| DVDD_UV    | DVDD undervoltage threshold                                 |             |      |     | 1.53    |     | V                          |

| REF_OV     | Reference overvoltage threshold                             |             |      |     | 2.75    |     | V                          |

| REF_UV     | Reference undervoltage threshold                            |             |      |     | 2.25    |     | V                          |

|            |                                                             |             | PD2  | PD1 |         |     |                            |

|            |                                                             |             | 0    | 0   | 1       |     |                            |

| P_DIAG_PU  | P gain input diagnostics pulldown resistor value            |             | 0    | 1   | 2       |     | $M\Omega$                  |

|            | panaown rodiotor valuo                                      |             | 1    | 0   | 3       |     |                            |

|            |                                                             |             | 1    | 1   | 4       |     |                            |

## **Electrical Characteristics – Diagnostics (continued)**

over operating ambient temperature range (unless otherwise noted)

| P.A            | ARAMETER                                                         | TEST CONDITIONS                                      |                 |            |         | MIN TYP N | IAX  | UNIT           |  |  |

|----------------|------------------------------------------------------------------|------------------------------------------------------|-----------------|------------|---------|-----------|------|----------------|--|--|

|                |                                                                  | INP+ and INP-<br>each has<br>threshold<br>comparator | THRS[2]         | THRS[1]    | THRS[0] |           |      |                |  |  |

|                |                                                                  |                                                      |                 |            | 0       | 0         | 0    | 72.5           |  |  |

|                |                                                                  | $V_{BRG} = 2.5 V$                                    | 0               | 0          | 1       | 70        |      |                |  |  |

| INP_OV         | P gain input overvoltage threshold value                         |                                                      | 0               | 1          | 0       | 65        |      | $%V_{BRG}$     |  |  |

|                |                                                                  |                                                      | 0               | 1          | 1       | 90        |      |                |  |  |

|                |                                                                  | $V_{BRG} = 2 V$                                      | 1               | 0          | 0       | 87.5      |      |                |  |  |

|                |                                                                  |                                                      | 1               | 0          | 1       | 82.5      |      |                |  |  |

|                |                                                                  | V <sub>BRG</sub> = 1.25 V                            | 1               | 1          | 0       | 100       |      |                |  |  |

|                |                                                                  | V <sub>BRG</sub> = 1.25 V                            | 1               | 1          | 1       | 95        |      |                |  |  |

|                |                                                                  | INP+ and INP-<br>each has<br>threshold<br>comparator | THRS[2]         | THRS[1]    | THRS[0] |           |      |                |  |  |

|                | P gain input undervoltage threshold value                        | V <sub>BRG</sub> = 2.5 V                             | 0               | 0          | 0       | 7.5       |      |                |  |  |

|                |                                                                  |                                                      | 0               | 0          | 1       | 10.0      |      |                |  |  |

| INP_UV         |                                                                  |                                                      | 0               | 1          | 0       | 15.0      |      | $\rm %V_{BRG}$ |  |  |

|                |                                                                  |                                                      | ilestioid value |            | 0       | 1         | 1    | 10.0           |  |  |

|                |                                                                  |                                                      | $V_{BRG} = 2.V$ | 1          | 0       | 0         | 12.5 |                |  |  |

|                |                                                                  |                                                      | 1               | 0          | 1       | 17.5      |      |                |  |  |

|                |                                                                  | 1.05.1/                                              | 1               | 1          | 0       | 17.5      |      |                |  |  |

|                |                                                                  | $V_{BRG} = 1.25 \text{ V}$                           | 1               | 1          | 1       | 22.5      |      |                |  |  |

| INT_OV         | T gain input overvoltage                                         | INT+ and INT- ea                                     | ch has thres    | shold comp | arator  | 2.1       |      | V              |  |  |

| PGAIN_OV       | Output overvoltage (single-<br>ended) threshold for P gain       |                                                      |                 |            |         | 2.25      |      | V              |  |  |

| PGAIN_UV       | Output undervoltage (single-<br>ended) threshold for P gain      |                                                      |                 |            |         | 0.15      |      | V              |  |  |

| TGAIN_OV       | Output overvoltage (single-<br>ended) threshold for T gain       |                                                      |                 |            |         | 2.25      |      | V              |  |  |

| TGAIN_UV       | Output undervoltage (single-<br>ended) threshold for T gain      |                                                      |                 |            |         | 0.15      |      | V              |  |  |

| HARNESS_FAULT1 | Open-wire leakage current 1.<br>Open PWR with pullup on<br>OUT   |                                                      |                 |            |         | 2         |      | μΑ             |  |  |

| HARNESS_FAULT2 | Open-wire leakage current 2.<br>Open GND with pulldown on<br>OUT |                                                      |                 |            |         | 20        |      | μA             |  |  |

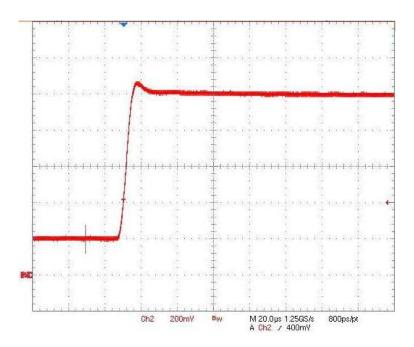

## 6.21 Operating Characteristics

over operating ambient temperature range (unless otherwise noted). Start-up time and response time testing performed in 0-5V absolute voltage mode.

| PARAMETER                    | TEST CONDITIONS                          | MIN | TYP  | MAX | UNIT |

|------------------------------|------------------------------------------|-----|------|-----|------|

| Start-up time <sup>(1)</sup> | No IIR filter, Vout step 0 to 2.5 V      |     | 9.6  |     | ms   |

| Start-up time (2)            | IIR filter = 320Hz, Vout step 0 to 2.5 V |     | 10.8 |     | ms   |

| Output rate                  |                                          |     | 512  |     | μs   |

| Response time <sup>(3)</sup> | No IIR filter, Vout step 0 to 2.5 V      |     | 1700 |     | μs   |

- Time from power up to reach 90% of valid output.

Time from power up to reach valid output, including settling time.

- Time to reach 90% of valid output.

## **Operating Characteristics (continued)**

over operating ambient temperature range (unless otherwise noted). Start-up time and response time testing performed in 0-5V absolute voltage mode.

| PARAMETER                                                                              | TEST CONDITIONS                                                                                                                                                                 | MIN | TYP  | MAX | UNIT |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Response time <sup>(4)</sup>                                                           | IIR filter = 320Hz, Vout step 0 to 2.5 V                                                                                                                                        |     | 2680 |     | μs   |

|                                                                                        | 3 pressure - 1 temperature calibration, overall accuracy calculated using points different from points used for calibration                                                     |     | 0.13 |     |      |

| Absolute-voltage mode, overall accuracy (PGA305 only, no sense element) <sup>(5)</sup> | 3 pressure - 3 temperature calibration, input voltage not subject to temperature variation, overall accuracy calculated using points different from points used for calibration |     | 0.08 |     | %FSO |

|                                                                                        | 4 pressure - 4 temperature calibration, input voltage not subject to temperature variation, overall accuracy calculated using points different from points used for calibration |     | 0.08 |     |      |

|                                                                                        | 3 pressure - 1 temperature calibration,<br>overall accuracy calculated using points<br>different from points used for calibration                                               |     | 0.15 |     |      |

| Ratiometric-voltage mode, overall accuracy (PGA305, no sense element) (5)              | 3 pressure - 3 temperature calibration, input voltage not subject to temperature variation, overall accuracy calculated using points different from points used for calibration |     | 0.13 |     | %FSO |

| element) (-7                                                                           | 4 pressure - 4 temperature calibration, input voltage not subject to temperature variation, overall accuracy calculated using points different from points used for calibration |     | 0.10 |     |      |

|                                                                                        | 3 pressure - 1 temperature calibration, overall accuracy calculated using points different from points used for calibration                                                     |     | 0.18 |     |      |

| Current mode, overall accuracy (PGA305, no sense element) (5)                          | 3 pressure - 3 temperature calibration, input voltage not subject to temperature variation, overall accuracy calculated using points different from points used for calibration |     | 0.08 |     | %FSO |

|                                                                                        | 4 pressure - 4 temperature calibration, input voltage not subject to temperature variation, overall accuracy calculated using points different from points used for calibration |     | 0.06 |     |      |

<sup>(4)</sup> Time to reach valid output, including settling time.

<sup>(5)</sup> Sense element held at constant temperature while the PGA305 device was calibrated at –25°C, 25°C, 85°C and 125°C. Accuracy was then measured at –40°C, 50°C and 150 °C.

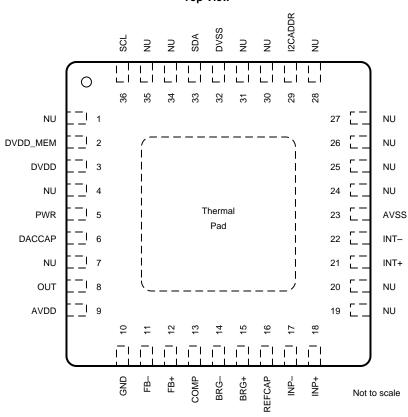

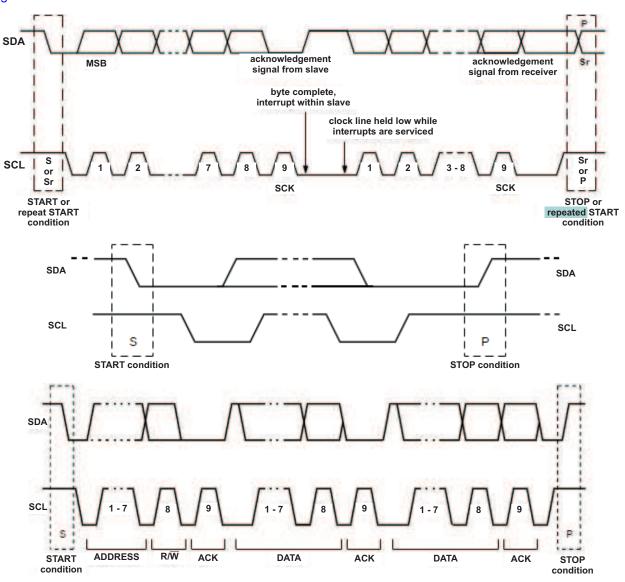

6.22 I<sup>2</sup>C Interface Timing Requirements

|                    |                             | MIN  | TYP | MAX | UNIT |

|--------------------|-----------------------------|------|-----|-----|------|

| t <sub>STASU</sub> | START condition set-up time | 500  |     |     | ns   |

| t <sub>STAHD</sub> | START condition hold time   | 500  |     |     | ns   |

| t <sub>LOW</sub>   | SCL low time                | 1.25 |     |     | μs   |

| t <sub>HIGH</sub>  | SCL high time               | 1.25 |     |     | μs   |

| t <sub>RISE</sub>  | SCL and SDA rise time       |      |     | 7   | ns   |

| FALL               | SCL and SDA fall time       |      |     | 7   | ns   |

| t <sub>DATSU</sub> | Data setup time             | 500  |     |     | ns   |

| t <sub>DATHD</sub> | Data hold time              | 500  |     |     | ns   |

| t <sub>STOSU</sub> | STOP condition set-up time  | 500  |     |     | ns   |

# 6.23 Timing Diagram

Figure 1. I<sup>2</sup>C Timing

# TEXAS INSTRUMENTS

# 6.24 Typical Characteristics

## 7 Detailed Description

#### 7.1 Overview

www.ti.com.cn

The PGA305 device can be used in a variety of applications. The most common ones are for pressure and temperature measurement. Depending on the application, the device itself can be configured in different modes. These sections give information regarding these configurations.

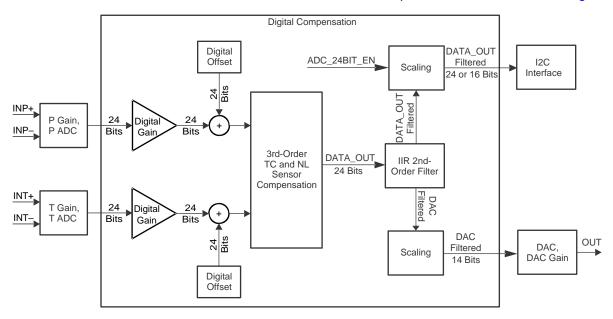

The PGA305 device is a high-accuracy, low-drift, low-noise, low-power, and easily programmable signal-conditioner device for resistive-bridge pressure and temperature-sensing applications. The PGA305 device implements a third-order temperature coefficient (TC) and nonlinearity (NL) algorithm to linearize the analog output. The PGA305 device accommodates various sensing element types, such as piezoresistive, ceramic film, and steel membrane. It supports the sensing element spans from 1 mV/V to 135 mV/V. The typical applications supported are pressure sensor transmitters, transducers, liquid-level meters, flow meters, strain gauges, weight scales, thermocouples, thermistors, two-wire resistance thermometers (RTD), and resistive field transmitters. The device can also be used in accelerometer and humidity sensor signal-conditioning applications.

The PGA305 device provides bridge excitation voltages of 2.5 V, 2 V, and 1.25 V, all ratiometric to the ADC reference level. The PGA305 device has the unique one-wire interface (OWI) that supports communication and configuration through the power-supply line during the calibration process. This feature minimizes the number of wires necessary for an application.

The PGA305 device contains two separated analog front-end (AFE) chains for resistive-bridge inputs and temperature-sensing inputs. Each AFE chain has its own gain amplifier and a 16-bit ADC at a 7.8-kHz output rate. The resistive-bridge input AFE chain consists of a programmable gain with 32 steps from 5 V/V to 400 V/V. For the temperature-sensing AFE input chain, the PGA305 device provides a current source that can supply up to 500  $\mu$ A for optional external temperature sensing. This current source can also be used as constant-current bridge excitation. The programmable gain in the temperature-sensing chain has four steps from 1.33 V/V to 20 V/V. In addition, the PGA305 device integrates an internal temperature sensor that can be configured as the input of the temperature-sensing AFE chain.

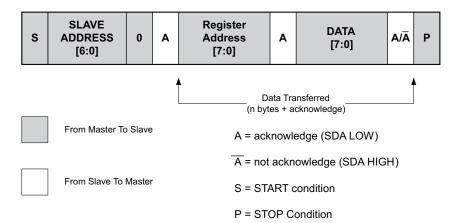

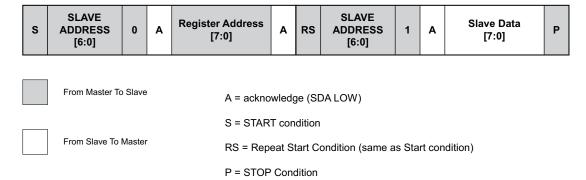

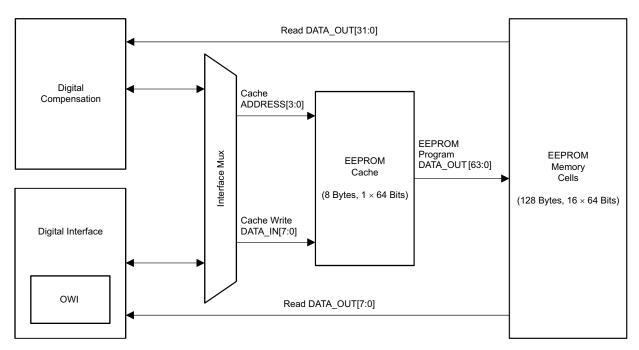

A 128-byte EEPROM is integrated in the PGA305 device to store the calibration coefficients and the PGA305 configuration settings as needed. The PGA305 device has an integrated I<sup>2</sup>C interface used for data capture and also for device configuration. In addition, 14-bit DAC followed by a buffer gain stage of 2 V/V to 10 V/V. The device supports industrial-standard ratiometric-voltage output, absolute-voltage output, and 4-mA to 20-mA current loop.

The diagnostic function monitors the operating condition of the PGA305 device. The device can operate with a 3.3-V to 30-V power supply directly without using an external LDO. The PGA305 device has a wide ambient-temperature operating range from -40°C to 150°C. The package form is 6-mm × 6-mm, 36-pin VQFN. In this small package size, the PGA305 device has integrated all the functions necessary for resistive-bridge sensing applications to minimize the PCB area and simplify the overall application design.

# TEXAS INSTRUMENTS

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

This section describes individual functional blocks of the PGA305 device.

#### 7.3.1 Reverse-Voltage Protection Block

The PGA305 device includes a reverse-voltage protection block. This block protects the device from reverse-battery conditions on the external power supply.

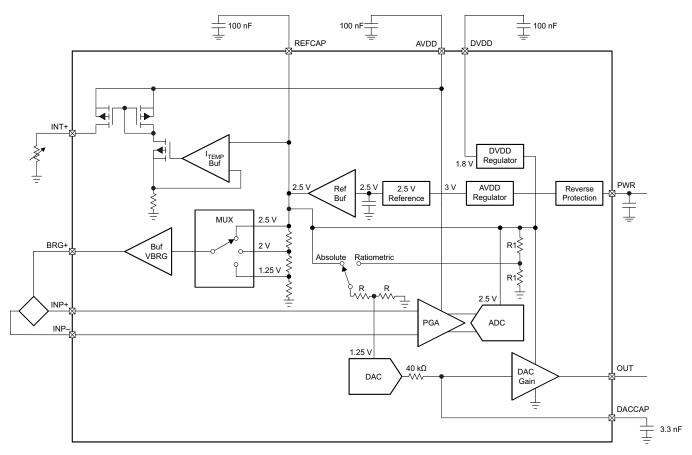

#### 7.3.2 Linear Regulators

The PGA305 device has two main linear regulators: an AVDD regulator and a DVDD regulator. The AVDD regulator supplies the 3-V voltage source for internal analog circuitry, while the DVDD regulator supplies the 1.8-V regulated voltage for the digital circuitry. The user must connect bypass capacitors of 100 nF each to the AVDD and DVDD pins of the device.

#### 7.3.3 Internal Reference

The PGA305 device has two internal references. These references are given in these subsections.

#### 7.3.3.1 High-Voltage Reference

The high-voltage reference is an inaccurate reference used in the diagnostic thresholds.

#### 7.3.3.2 Accurate Reference

The accurate reference is used to generate reference voltage for the P ADC, T ADC and DAC. TI recommends to place a 100-nF capacitor on the REFCAP pin to limit the bandwidth of reference noise.

The user can set the ADC\_EN\_VREF bit in the ALPWR register to 0 to disable the accurate reference buffer. This allows the user to connect an external single-ended reference voltage to the REFCAP pin and then supply the reference voltage to the ADCs and the DAC. Note that the default power-up state of ADC\_EN\_VREF is such that the reference buffer is disabled.

#### NOTE

The accurate reference is valid 50 µs after the digital core starts running at power up.

## 7.3.4 BRG+ to BRG- Supply for the Resistive Bridge

The sensor voltage-supply block of the PGA305 device supplies power to the resistive-bridge sensor. Use the BRG\_CTRL bits in the BRG\_CTRL register to configure the sensor supply in the PGA305 device to a 2.5-V, 2-V, or 1.25-V nominal output supply. These three output supply options can accommodate bridge sense elements with different resistor values. This nominal supply is ratiometric to the accurate reference as shown in Figure 3.

# TEXAS INSTRUMENTS

#### **Feature Description (continued)**

Figure 3. Bridge Supply and P ADC Reference are Ratiometric

The sensor drive includes a switch. This switch can be used to turn off power to the sense element.

## 7.3.5 ITEMP Supply for the Temperature Sensor

The ITEMP block in PGA305 device supplies programmable current to an external temperature sensor, such as an RTD temperature probe or NTC or PTC thermistor. The temperature-sensor current source is ratiometric to the accurate reference.

Use the ITEMP\_CTRL bits in the TEMP\_CTRL register to program the value of the current.

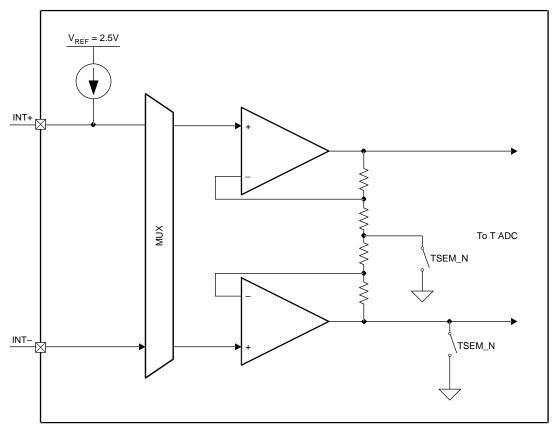

### 7.3.6 Internal Temperature Sensor

PGA305 device includes an internal temperature sensor whose voltage output is digitized by the T ADC and made available to the microprocessor. This digitized value is used to implement temperature compensation algorithms in software. Note that the voltage generated by the internal temperature sensor is proportional to the junction temperature.

## **Feature Description (continued)**

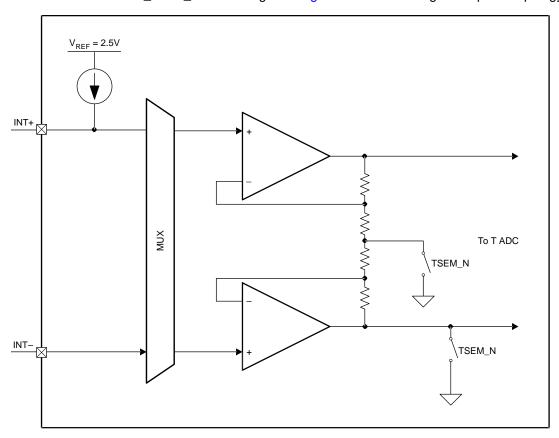

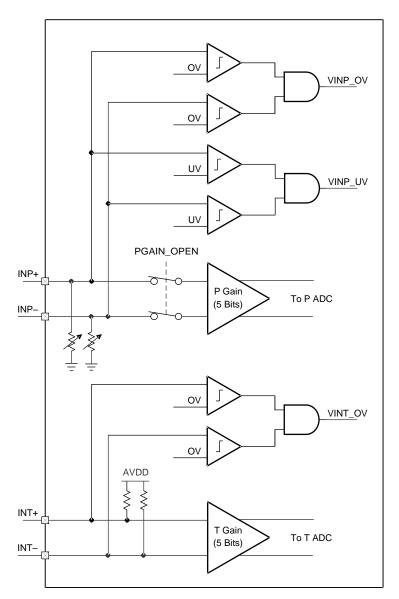

Figure 4 shows the internal temperature sensor AFE.

Figure 4. Temperature Sensor AFE

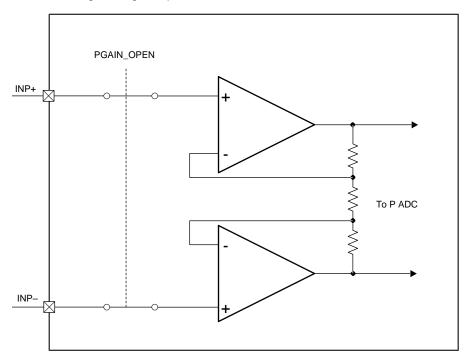

## 7.3.7 P Gain

P gain is designed with precision, low-drift, low-flicker-noise, chopper-stabilized amplifiers. P gain is implemented as an instrument amplifier as shown in Figure 5.

#### **Feature Description (continued)**

The user can use five bits in the P\_GAIN\_SELECT register to adjust the gain of this stage to accommodate sense elements with a wide range of signal spans.

Figure 5. P Gain

#### 7.3.8 P Analog-to-Digital Converter

The P analog-to-digital converter digitizes the voltage output of the P-gain amplifier.

#### 7.3.8.1 P Sigma-Delta Modulator for P ADC

The sigma-delta modulator for P ADC is a 1-MHz, second-order, 3-bit quantizing sigma-delta modulator.

#### 7.3.8.2 P Decimation Filter for P ADC

The pressure signal path internal conversion time is 128 µs.

The output of the decimation filter in the pressure signal path is a 24-bit signed value. Some example decimation output codes for given differential voltages at the input of the sigma-delta modulator are shown in Table 1.

Table 1. Input Voltage to Output Counts for the P ADC

| SIGMA-DELTA MODULATOR<br>DIFFERENTIAL INPUT VOLTAGE<br>(V) | 24-BIT NOISE-FREE<br>DECIMATOR OUTPUT |

|------------------------------------------------------------|---------------------------------------|

| -2.5                                                       | -8 388 608 (0x800000)                 |

| -1.25                                                      | -4 194 304 (0xC00000)                 |

| 0                                                          | 0 (0x000000)                          |

| 1.25                                                       | 4 194 303 (0x3FFFFF)                  |

| 2.5                                                        | 8 388 607 (0x7FFFFF)                  |

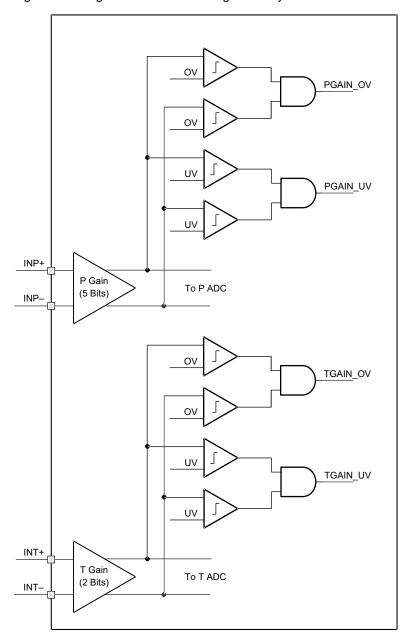

#### 7.3.9 T Gain

www.ti.com.cn

The device has the ability to perform temperature compensation through an internal or external temperature sensor. The user can select the source of the temperature measurement with the TEMP\_MUX\_CTRL bits in TEMP\_CTRL register. Note that the device connects to an external temperature sensor through the INT+ and INT- pins.

The T gain block is constructed with a low-flicker-noise, low-offset, chopper-stabilized amplifier. The gain is configurable with two bits in the T GAIN SELECT register. Figure 6 shows the T-gain amplifier topology.

Figure 6. Temperature Sensor AFE

The T-gain amplifier can be configured for single-ended or differential operation using the TSEM\_N bit in the AMUX\_CTRL register. Note that when the T-gain amplifier is set up for single-ended operation, the differential voltage converted by the T ADC is with respect to ground. Table 2 shows the configuration that the user must select for the different temperature sources.

**Table 2. T-Gain Configuration**

| TEMPERATURE SOURCE                                                                  | T GAIN CONFIGURATION |

|-------------------------------------------------------------------------------------|----------------------|

| Internal temperature sensor                                                         | Single-ended         |

| External temperature sensor with one terminal of the sensor connected to ground     | Single-ended         |

| External temperature sensor with neither terminal of the sensor connected to ground | Differential         |

ZHCSIP5-AUGUST 2018 www.ti.com.cn

**ISTRUMENTS**

The T-gain amplifier must be set up for either the single-ended or differential configuration, depending on the source of signal to the T gain.

#### **NOTE**

When T GAIN is configured to measure the internal temperature-sensor output, T GAIN must be configured to operate in single-ended mode and with a gain of 5 V/V.

### 7.3.10 T Analog-to-Digital Converter

The T analog-to-digital converter is for digitizing the T-gain amplifier output. The digitized value is available in the TADC\_DATA2 and TADC\_DATA3 registers.

## 7.3.10.1 T Sigma-Delta Modulator for T ADC

The sigma-delta modulator for T ADC is a 1-MHz, second-order, 3-bit quantizing sigma-delta modulator.

#### 7.3.10.2 T Decimation Filters for T ADC

The temperature signal path contains a decimation filter with an internal output rate of 128 µs.

The output of the decimation filter in the temperature signal path is 24-bit signed value. Some example decimation output codes for given differential voltages at the input of the sigma-delta modulator are shown in Table 3.

Table 3. Input Voltage to Output Counts for T ADC

| SIGMA-DELTA MODULATOR<br>DIFFERENTIAL INPUT VOLTAGE | 24-BIT NOISE-FREE<br>DECIMATOR OUTPUT |

|-----------------------------------------------------|---------------------------------------|

| –2.5 V                                              | -8 388 608 (0x800000)                 |

| −1.25 V                                             | -4 194 304 (0xC00000)                 |

| 0 V                                                 | 0 (0x000000)                          |

| 1.25 V                                              | 4 194 303 (0x3FFFFF)                  |

| 2.5 V                                               | 8 388 607 (0x7FFFFF)                  |

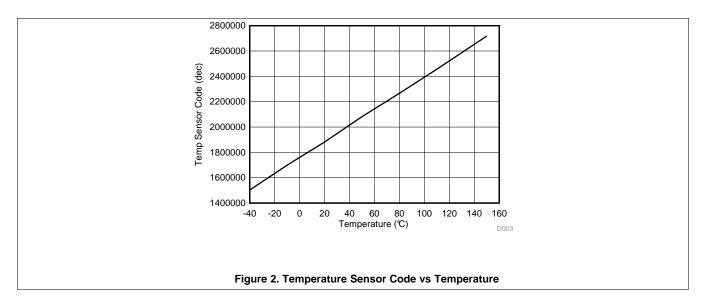

The nominal relationship between the device junction temperature and 24-bit T ADC Code for T GAIN = 5 V/V is shown in Equation 1.

T ADC Code =  $6632.1 \times TEMP + 1710281.3$ ,

TEMP is temperature in °C

## (1)

#### 7.3.11 P GAIN and T GAIN Calibration

The P\_GAIN value should be set based on the maximum bridge output voltage. The maximum bridge voltage is the maximum sum of bridge offset and bridge span across the entire operating temperature range.

The T GAIN value should be set based on the temperature sense element. The specific values to be used are:

- For the internal temperature sensor, set T\_GAIN to 5 V/V gain.

- For an external temperature sensor such as a PTC thermistor, set T GAIN to 20 V/V gain.

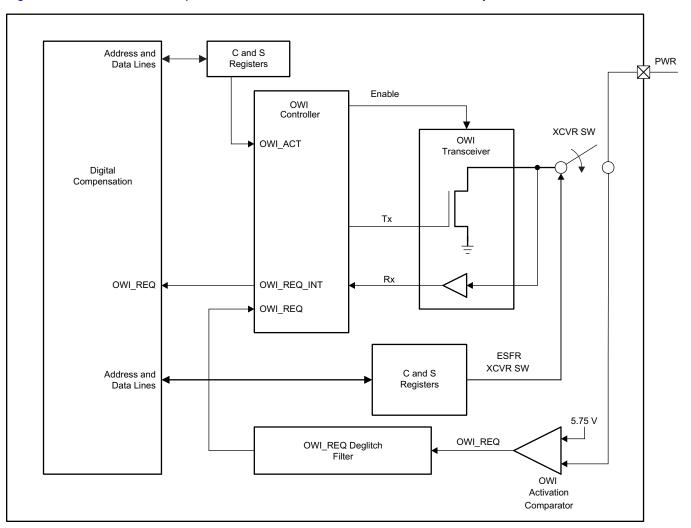

## 7.3.12 One-Wire Interface (OWI)

The device includes an OWI digital communication interface. The function of OWI is to enable writes to and reads from all memory locations inside the PGA305 device that are available for OWI access.

#### 7.3.12.1 Overview of OWI

The OWI digital communication is a master-slave communication link in which the PGA305 device operates as a slave device only. The master device controls when data transmission begins and ends. The slave device does not transmit data back to the master until it is commanded to do so by the master.

The PWR pin of PGA305 device is used as OWI interface, so that when the PGA305 device is embedded inside of a system module, only two pins are needed (PWR and GND) for communication. The OWI master communicates with the PGA305 device by modulating the voltage on the PWR pin, whereas the PGA305 device communicates with the master by modulating the current on the PWR pin. The OWI master activates OWI communication by generating an activation pulse on the PWR pin.

Figure 7 shows a functional equivalent circuit for the structure of the OWI circuitry.

Figure 7. OWI System Components

# TEXAS INSTRUMENTS

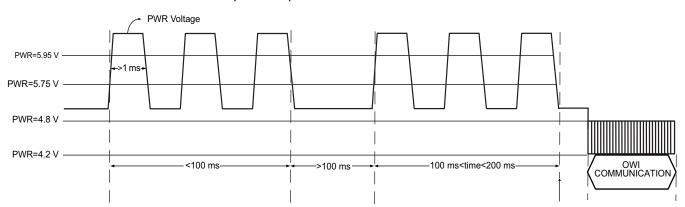

#### 7.3.12.2 Activating and Deactivating the OWI Interface

#### 7.3.12.2.1 Activating OWI Communication

The OWI master initiates OWI communication when the OWI master generates an **OWI activation-pulse sequence** on the PWR pin. When the PGA305 device receives a valid OWI activation-pulse sequence, it prepares itself for OWI communication. Notice that after the valid OWI activation-pulse sequence is received, the logic checks on the EEPROM lock status. If the EEPROM is locked, the sequence 0x5555 must be sent within 100 ms after the end of the activation-pulse sequence.

Figure 8. OWI Activation Using Overvoltage Drive

#### 7.3.12.2.2 Deactivating OWI Communication

To deactivate OWI communication and restart the compensation engine inside the PGA305 device (if it was in reset), these two steps must be performed by the OWI master:

- Set the OWI\_XCR\_EN bit in the DIG\_IF\_CTRL register to 0 to turn off the OWI transceiver.

- Set the COMPENSATION\_RESET bit in the COMPENSATION\_CONTROL register to 0 to de-assert the compensation engine reset.

#### 7.3.12.3 OWI Protocol

#### 7.3.12.3.1 OWI Frame Structure

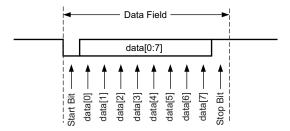

#### 7.3.12.3.1.1 Standard Field Structure

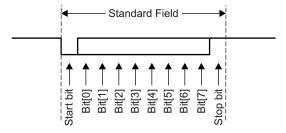

Data is transmitted on the one-wire interface in byte-sized packets. The first bit of the OWI field is the start bit. The next eight bits of the field are data bits to be processed by the OWI control logic. The final bit in the OWI field is the stop bit. A group of fields make up a transmission frame. A transmission frame is composed of the fields necessary to complete one transmission operation on the one-wire interface. The standard field structure for a one-wire field is shown in Figure 9.

Figure 9. Standard OWI Field

#### 7.3.12.3.1.2 Frame Structure

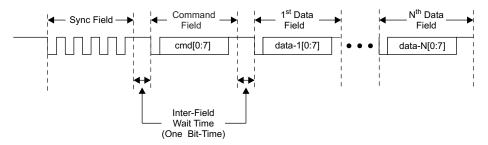

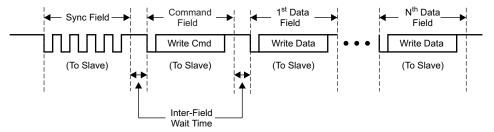

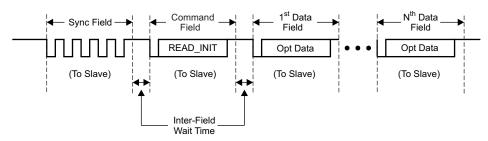

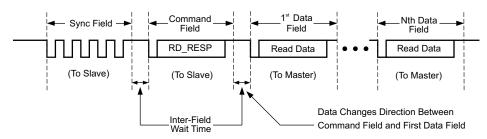

A complete one-wire data transmission operation is done in a frame with the structure is shown in Figure 10.

Figure 10. OWI Transmission Frame, N = 1 to 8

Each transmission frame must have a synchronization field and a command field followed by zero to a maximum of eight data fields. The sync field and command fields are always transmitted by the master device. The data fields may be transmitted either by the master or the slave, depending on the command given in the command field. It is the command field which determines direction of travel of the data fields (master-to-slave or slave-to-master). The number of data fields transmitted is also determined by the command in the command field. The inter-field wait time is optional and may be necessary for the slave or the master to process data that has been received.

#### NOTE

If the OWI remains idle in either the logic-0 or logic-1 state for more than 15 ms, then the PGA305 communication resets and requires a sync field as the next data transmission from the master.

#### 7.3.12.3.1.3 Sync Field

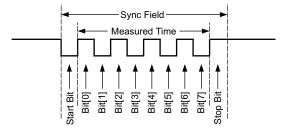

The sync field is the first field in every frame that is transmitted by the master. The sync field is used by the slave device to compute the bit width transmitted by the master. This bit width is used to receive accurately all subsequent fields transmitted by the master. The format of the sync field is shown in Figure 11.

Figure 11. OWI Sync Field

#### NOTE

Consecutive sync-field bits are measured and compared to determine if a sync field was transmitted to the PGA305 device is valid. If the difference in bit widths of any two consecutive SYNC field bits is greater than ±25%, then the PGA305 device ignores the rest of the OWI frame and does not respond to the OWI message.

ZHCSIP5 – AUGUST 2018 www.ti.com.cn

# TEXAS INSTRUMENTS

#### 7.3.12.3.1.4 Command Field

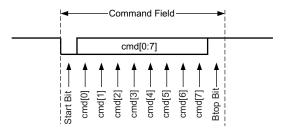

The command field is the second field in every frame sent by the master. The command field contains instructions about what to do with and where to send the data that is transmitted to the slave. The command field can also instruct the slave to send data back to the master during a read operation. The number of data fields to be transmitted is also determined by the command in the command field. The format of the command field is shown in Figure 12.

Figure 12. OWI Command Field

#### 7.3.12.3.1.5 Data Fields

After the master has transmitted the command field in the transmission frame, zero or more data fields are transmitted to the slave (write operation) or to the master (read operation). The data fields can be raw EEPROM data or address locations in which to store data. The format of the data is determined by the command in the command field. The typical format of a data field is shown in Figure 13.

Figure 13. OWI Data Field

## 7.3.12.3.2 OWI Commands

The following is the list of five OWI commands supported by PGA305:

- 1. OWI write

- 2. OWI read initialization

- 3. OWI read response

- 4. OWI burst write of EEPROM cache

- 5. OWI burst read from EEPROM cache

#### 7.3.12.3.2.1 OWI Write Command

| FIELD<br>LOCATION | DESCRIPTION             | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command field     | Basic write command     | 0     | P2    | P1    | P0    | 0     | 0     | 0     | 1     |

| Data field 1      | Destination address     | A7    | A6    | A5    | A4    | А3    | A2    | A1    | A0    |

| Data field 2      | Data byte to be written | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

ZHCSIP5 - AUGUST 2018 www.ti.com.cn

The P2, P1, and P0 bits in the command field determine the memory page that is being accessed by the OWI. The memory page decode is shown in Table 4.

| Tab | le | 4. | owi | Memory | Page | Decod | е |

|-----|----|----|-----|--------|------|-------|---|

|-----|----|----|-----|--------|------|-------|---|

| P2 | P1 | P0 | MEMORY PAGE                                          |

|----|----|----|------------------------------------------------------|

| 0  | 0  | 0  | Reserved                                             |

| 0  | 0  | 1  | Reserved                                             |

| 0  | 1  | 0  | Control and status registers, DI_PAGE_ADDRESS = 0x02 |

| 0  | 1  | 1  | Reserved                                             |

| 1  | 0  | 0  | Reserved                                             |

| 1  | 0  | 1  | EEPROM cache                                         |

| 1  | 1  | 0  | Reserved                                             |

| 1  | 1  | 1  | Control and status registers, DI_PAGE_ADDRESS = 0x07 |

#### 7.3.12.3.2.2 OWI Read Initialization Command

| FIELD<br>LOCATION | DESCRIPTION                 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|-----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command field     | Read initialization command | 0     | P2    | P1    | P0    | 0     | 0     | 1     | 0     |

| Data field 1      | Fetch address               | A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    |

The P2, P1, and P0 bits in the command field determine the memory page that is being accessed by the OWI. The memory page decode is shown in Table 4.

#### 7.3.12.3.2.3 OWI Read-Response Command

| FIELD<br>LOCATION | DESCRIPTION                          | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|--------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command field     | Read-response command                | 0     | 1     | 1     | 1     | 0     | 0     | 1     | 1     |

| Data field 1      | Data retrieved (OWI drives data out) | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

The P2, P1, and P0 bits in the command field determine the memory page that is being accessed by the OWI. The memory page decode is shown in Table 4.

### 7.3.12.3.2.4 OWI Burst-Write Command (EEPROM Cache Access)

| FIELD<br>LOCATION | DESCRIPTION                              | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command field     | EE_CACHE write-command cache bytes (0–7) | 1     | 1     | 0     | 1     | 0     | 0     | 0     | 0     |

| Data field 1      | First data byte to be written            | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 2      | Second data byte to be written           | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 3      | Third data byte to be written            | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 4      | Fourth data byte to be written           | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 5      | Fifth data byte to be written            | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 6      | Sixth data byte to be written            | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 7      | Seventh data byte to be written          | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 8      | Eighth data byte to be written           | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

# TEXAS INSTRUMENTS

#### 7.3.12.3.2.5 OWI Burst Read Command (EEPROM Cache Access)

| FIELD<br>LOCATION | DESCRIPTION                                     | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command field     | Burst-read response (8 bytes)                   | 1     | 1     | 0     | 1     | 0     | 0     | 1     | 1     |

| Data field 1      | First data byte retrieved EEPROM cache byte 0   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 2      | Second data byte retrieved EEPROM cache byte 1  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 3      | Third data byte retrieved EEPROM cache byte 2   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 4      | Fourth data byte retrieved EEPROM cache byte 3  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 5      | Fifth data byte retrieved EEPROM cache byte 4   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 6      | Sixth data byte retrieved EEPROM cache byte 5   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 7      | Seventh data byte retrieved EEPROM cache byte 6 | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Data field 8      | Eighth data byte retrieved EEPROM cache byte 7  | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

#### 7.3.12.3.3 OWI Operations

#### 7.3.12.3.3.1 Write Operation

The write operation on the one-wire interface is fairly straightforward. The command field specifies the write operation, where the subsequent data bytes are to be stored in the slave, and how many data fields are going to be sent. Additional command instructions can be sent in the first few data fields if necessary. The write operation is shown in Figure 14.

Figure 14. Write Operation, N = 1 to 8

### 7.3.12.3.3.2 Read Operation

The read operation requires two consecutive transmission frames to move data from the slave to the master. The first frame is the read-initialization frame. It tells the slave to retrieve data from a particular location within the slave device and prepare to send it over the OWI. The data location may be specified in the command field or may require additional data fields for complete data-location specification. The data is not sent until the master commands it to be sent in the subsequent frame called the read-response frame. During the read-response frame, the data direction changes from master  $\rightarrow$  slave to slave  $\rightarrow$  master immediately after the read response command field is sent. Enough time elapses between the command field and data field to allow the signal drivers to change direction. This wait time is 20  $\mu$ s, and the timer for this wait time is located on the slave device. After this wait time is complete, the slave transmits the requested data. The master device is expected to have switched its signal drivers and is ready to receive data. The read frames are shown in Figure 15.

Figure 15. Read-Initialization Frame, N = 1 to 8

Figure 16. Read-Response Frame, N = 1 to 8

#### 7.3.12.3.3.3 EEPROM Burst Write

The user can use the EEPROM burst write to write eight bytes of data to the EEPROM cache with one OWI frame to allow fast programming of EEPROM. Note that the EEPROM page must be selected before the EEPROM can transfer the contents of the EEPROM memory cells to the EEPROM cache.

#### 7.3.12.3.3.4 EEPROM Burst Read