Order

Now

LM5008A

ZHCSIX0H-MARCH 2009-REVISED OCTOBER 2018

# LM5008A 95V 350mA 恒定导通时间直流/直流降压开关稳压器

Technical

Documents

# 1 特性

- 工作输入电压范围: 6V 至 95V

- 集成型 100V N 沟道降压开关

- 内部启动稳压器

- 无需环路补偿

- 超快瞬态响应

- 导通时间与输入电压成反比变化

- 线路电压和负载电流变化时运行频率保持不变

- 可调节输出电压(以 2.5V 为基准电压)

- 高运行效率

- 精密的内部基准电压

- 低偏置电流

- 智能电流限制

- 热关断

- 8 引脚 VSSOP 和 8 引脚 WSON 封装

- 使用 LM5008A 及其 WEBENCH<sup>®</sup> 电源设计器创建 定制设计

# 2 应用

- 非隔离式电信降压稳压器

- 次级侧高电压后稳压器

- 48V 汽车系统

# 3 说明

🥭 Tools &

Software

LM5008A 直流/直流转换器是 LM5008 COT 降压开关 稳压器的功能变型。LM5008A 的功能差异表现在:最 低输入运行电压为 6V,导通时间公式稍有不同且去除 了最小负载电流要求。

Support &

Community

22

LM5008A 350mA 降压开关稳压器 具有 实现低成本高效率的降压稳压器所需的全部功能。此高电压转换器具有集成型 100V N 沟道降压开关,且可在 6V 至 95V 的输入电压范围内运行。该器件易于实施,且可采用 8 引脚 VSSOP 封装和热增强型 8 引脚 WSON 封装。该转换器使用了 PWM 控制方案,导通时间与 V<sub>IN</sub> 成反比。此特性使得运行频率能够保持相对恒定。该控制方案不需要任何环路补偿。该器件实现了智能电流限制, 其强制关闭时间与 V<sub>OUT</sub> 成反比。该方案可在提供最低折返的同时确保实现短路控制。其他 特性 包括:热关断、V<sub>CC</sub> 欠压锁定、栅极驱动欠压锁定、最大占空比限幅器和预充电开关。

#### 器件信息<sup>(1)</sup>

| 器件型号      | 封装        | 封装尺寸(标称值)       |

|-----------|-----------|-----------------|

| LM5008A   | VSSOP (8) | 3.00mm × 3.00mm |

| LIVIDUUOA | WSON (8)  | 4.00mm × 4.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

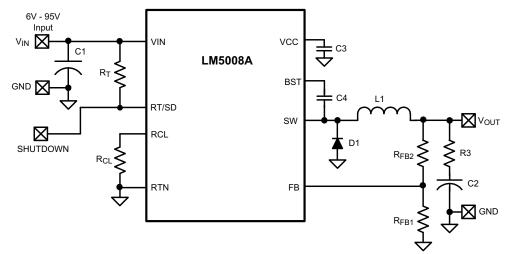

典型应用,基本降压稳压器

Copyright © 2016, Texas Instruments Incorporated

# 目录

| 1 | 特性   |                                  | 1   |  |  |  |  |

|---|------|----------------------------------|-----|--|--|--|--|

| 2 | 应用1  |                                  |     |  |  |  |  |

| 3 | 说明   |                                  | 1   |  |  |  |  |

| 4 |      | 历史记录                             |     |  |  |  |  |

| 5 |      | Configuration and Functions      |     |  |  |  |  |

| 6 | Spe  | cifications                      | 4   |  |  |  |  |

|   | 6.1  | Absolute Maximum Ratings         | . 4 |  |  |  |  |

|   | 6.2  | ESD Ratings                      | 4   |  |  |  |  |

|   | 6.3  | Recommended Operating Conditions | . 4 |  |  |  |  |

|   | 6.4  | Thermal Information              | . 4 |  |  |  |  |

|   | 6.5  | Electrical Characteristics       | . 5 |  |  |  |  |

|   | 6.6  | Switching Characteristics        | . 6 |  |  |  |  |

|   | 6.7  | Typical Characteristics          | . 7 |  |  |  |  |

| 7 | Deta | ailed Description                | 8   |  |  |  |  |

|   | 7.1  | Overview                         | 8   |  |  |  |  |

|   | 7.2  | Functional Block Diagram         | . 8 |  |  |  |  |

|   | 7.3  | Feature Description              | . 8 |  |  |  |  |

|   |      |                                  |     |  |  |  |  |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Ch | nanges from Revision G (December 2016) to Revision H | Page |

|----|------------------------------------------------------|------|

| •  | 已添加 WEBENCH 链接                                       | 1    |

| •  | 己更改 在器件信息 中将 VSSOP-8 封装大小更改成了 3mm × 3mm              | 1    |

## Changes from Revision F (March 2013) to Revision G

| • | Changed R <sub>0JA</sub> value From: 200°C/W To: 139.7°C/W (VSSOP) and From: 40°C/W To: 42°C/W (WSON) | 4 |

|---|-------------------------------------------------------------------------------------------------------|---|

| • | Deleted Lead temperature (260°C maximum)                                                              | 4 |

| • | 已添加 添加了 ESD 额定值 表、特性 说明 部分、器件功能模式、应用和实施 部分、电源建议 部分、布局 部分、器<br>件和文档支持 部分以及机械、封装和可订购信息 部分               | 1 |

| • |                                                                                                       |   |

| _ | Changed layout of National Data Sheet to TI format | . «g |   |

|---|----------------------------------------------------|------|---|

| • | Changed layout of National Data Sheet to TI format | 1    | 7 |

#### 7.4 Device Functional Modes..... 12 Application and Implementation ...... 13 8 8.1 Application Information..... 13 8.2 Typical Application ..... 13 Power Supply Recommendations ...... 18 9 10.1 Layout Guidelines ..... 19 10.2 Layout Example ..... 19 11 器件和文档支持 ...... 20 11.1 器件支持 ...... 20 11.2 文档支持...... 20 11.3 接收文档更新通知 ..... 21 11.4 社区资源...... 21 11.5 11.6 静电放电警告...... 21 11.7 术语表 ...... 21 12 机械、封装和可订购信息...... 21

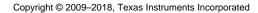

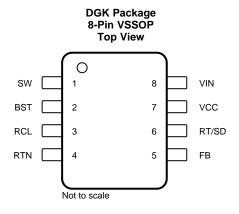

# 5 Pin Configuration and Functions

#### **Pin Functions**

|        | PIN                                                                                                                                                                                                                                                                                                              | ТҮРЕ                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO.    | NAME                                                                                                                                                                                                                                                                                                             | TIFE                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 1      | SW                                                                                                                                                                                                                                                                                                               | Ρ                                                                                                                                                                                                                                 | Switching node: power switching node. Connect to the output inductor, re-circulating diode, and bootstrap capacitor.                                                                                                                                                                                                |  |  |  |  |

| 2      | BST                                                                                                                                                                                                                                                                                                              | I                                                                                                                                                                                                                                 | Boost pin (bootstrap capacitor input): an external capacitor is required between the BST and the SW pins. A 0.01- $\mu$ F ceramic capacitor is recommended. An internal diode charges the capacitor from V <sub>CC</sub> during each off-time.                                                                      |  |  |  |  |

| 3      | RCL                                                                                                                                                                                                                                                                                                              | CL I Current limit off-time set pin: a resistor between this pin and RTN sets the off-time when current limit is detected. The off-time is preset to 35 µs if FB = 0 V.                                                           |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 4      | RTN                                                                                                                                                                                                                                                                                                              | G                                                                                                                                                                                                                                 | G Ground pin: ground for the entire circuit.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 5      | FB                                                                                                                                                                                                                                                                                                               | I                                                                                                                                                                                                                                 | Feedback input from regulated output: this pin is connected to the inverting input of the internal regulation comparator. The regulation threshold is 2.5 V.                                                                                                                                                        |  |  |  |  |

| 6      | RT/SD                                                                                                                                                                                                                                                                                                            | On-time set pin: a resistor between this pin and VIN sets the switch on time as a function of V <sub>IN</sub> . The minimum recommended on time is 400 ns at the maximum input voltage. This pin can be used for remote shutdown. |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 7      | VCC P Output from the internal high voltage series pass regulator: this regulated voltage provides gate driv<br>for the internal buck switch. An internal diode is provided between this pin and the BST pin. A local<br>decoupling capacitor is required. The series pass regulator is current limited to 9 mA. |                                                                                                                                                                                                                                   | Output from the internal high voltage series pass regulator: this regulated voltage provides gate drive power for the internal buck switch. An internal diode is provided between this pin and the BST pin. A local 0.47-µF decoupling capacitor is required. The series pass regulator is current limited to 9 mA. |  |  |  |  |

| 8      | VIN                                                                                                                                                                                                                                                                                                              | Р                                                                                                                                                                                                                                 | Input voltage: input operating range from 6 V to 95 V.                                                                                                                                                                                                                                                              |  |  |  |  |

| — EP G |                                                                                                                                                                                                                                                                                                                  | G                                                                                                                                                                                                                                 | Exposed pad: the exposed pad has no electrical contact. Connect to system ground plane for reduced thermal resistance. (WSON package only)                                                                                                                                                                          |  |  |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       | MIN  | MAX | UNIT |

|---------------------------------------|------|-----|------|

| V <sub>IN</sub> to GND                | -0.3 | 100 | V    |

| BST to GND                            | -0.3 | 114 | V    |

| SW to GND (steady-state)              |      | -1  | V    |

| BST to V <sub>CC</sub>                |      | 100 | V    |

| BST to SW                             |      | 14  | V    |

| V <sub>CC</sub> to GND                |      | 14  | V    |

| All other inputs to GND               | -0.3 | 7   | V    |

| Storage temperature, T <sub>stg</sub> | -55  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|        |                          |                                                                                | VALUE | UNIT |

|--------|--------------------------|--------------------------------------------------------------------------------|-------|------|

| V      | Flastraatatia diasharraa | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V(ESD) | Electrostatic discharge  | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | v    |

|        |                          |                                                                                |       |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                | MIN | MAX | UNIT |

|--------------------------------|-----|-----|------|

| V <sub>IN</sub>                | 6   | 95  | V    |

| Operating junction temperature | -40 | 125 | °C   |

## 6.4 Thermal Information

|                       |                                              | LM5         |            |      |

|-----------------------|----------------------------------------------|-------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGK (VSSOP) | NGU (WSON) | UNIT |

|                       |                                              | 8 PINS      | 8 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 139.7       | 42         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 51.2        | 27.6       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 70.5        | 18.5       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 3.4         | 0.3        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 69.5        | 18.5       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | -           | 4.3        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$T_1 = 25^{\circ}C$  and  $V_{IN} = 48 \text{ V}$  (unless otherwise noted)<sup>(1)</sup>

|                     | PARAMETER                         | TEST COND                                  | ITIONS                                                          | MIN      | TYP   | MAX  | UNI |

|---------------------|-----------------------------------|--------------------------------------------|-----------------------------------------------------------------|----------|-------|------|-----|

| VCC SUR             | PPLY                              |                                            |                                                                 |          |       |      |     |

|                     |                                   | \/                                         | $T_J = 25^{\circ}C$                                             |          | 7     |      | V   |

| V <sub>CC</sub> Reg | V <sub>CC</sub> regulator output  | V <sub>IN</sub> = 48 V                     | $T_J = -40^{\circ}C$ to $125^{\circ}C$                          | 6.6      |       | 7.4  | V   |

|                     | $V_{IN} - V_{CC}$                 | 6 V < V <sub>IN</sub> < 8.5 V              |                                                                 |          | 100   |      | m∖  |

|                     | V <sub>CC</sub> bypass threshold  | V <sub>IN</sub> increasing                 |                                                                 |          | 8.5   |      | V   |

|                     | V <sub>CC</sub> bypass hysteresis |                                            |                                                                 |          | 300   |      | m∖  |

|                     |                                   | V <sub>IN</sub> = 6 V                      |                                                                 |          | 100   |      | Ω   |

|                     | V <sub>CC</sub> output impedance  | V <sub>IN</sub> = 10 V                     |                                                                 |          | 8.8   |      | Ω   |

|                     |                                   | V <sub>IN</sub> = 48 V                     |                                                                 |          | 0.8   |      | Ω   |

|                     | V <sub>CC</sub> current limit     | V <sub>IN</sub> = 48 V                     |                                                                 |          | 9.2   |      | mA  |

|                     | V <sub>CC</sub> UVLO              | V <sub>CC</sub> increasing                 |                                                                 |          | 5.3   |      | V   |

|                     | V <sub>CC</sub> UVLO hysteresis   |                                            |                                                                 |          | 190   |      | m∖  |

|                     | V <sub>CC</sub> UVLO filter delay |                                            |                                                                 |          | 3     |      | μs  |

|                     |                                   |                                            | $T_J = 25^{\circ}C$                                             | -        | 550   |      |     |

|                     | I <sub>IN</sub> operating current | FB = 3 V, V <sub>IN</sub> = 48 V           | $T_{\rm J} = -40^{\circ}$ C to 125°C                            |          |       | 750  | μA  |

|                     |                                   |                                            | $T_J = 25^{\circ}C$                                             | -        | 110   |      |     |

|                     | I <sub>IN</sub> shutdown current  | RT/SD = 0 V                                | $T_{\rm J} = -40^{\circ}{\rm C} \text{ to } 125^{\circ}{\rm C}$ |          |       | 176  | μA  |

| CURREN              | IT LIMIT                          |                                            | -                                                               |          |       | I    |     |

|                     |                                   | T <sub>J</sub> = 25°C 0.51                 |                                                                 |          |       |      |     |

|                     | Current limit threshold           | $T_{J} = -40^{\circ}C$ to 125°C            |                                                                 | 0.41     |       | 0.61 | A   |

|                     | Current limit response time       | $I_{switch}$ overdrive = 0.1 A, time to s  | switch off                                                      |          | 350   |      | ns  |

| T <sub>OFF-1</sub>  | Off-time generator                | $FB = 0 V, R_{CL} = 100 k\Omega$           |                                                                 |          | 35    |      | μs  |

| T <sub>OFF-2</sub>  | Off-time generator                | FB = 2.3 V, R <sub>CL</sub> = 100 kΩ       |                                                                 |          | 2.56  |      | μs  |

|                     | GENERATOR                         |                                            |                                                                 |          |       |      |     |

|                     | <b>—</b> /                        |                                            | T <sub>J</sub> = 25°C                                           |          | 2.77  |      |     |

|                     | T <sub>ON</sub> – 1               | $V_{IN}$ = 10 V, $R_{ON}$ = 200 k $\Omega$ | $T_J = -40^{\circ}C$ to $125^{\circ}C$                          | 2.15     |       | 3.5  | μs  |

|                     | <b>T</b> 0                        | N 05 N D 000 L 0                           | $T_J = 25^{\circ}C$                                             |          | 300   |      |     |

|                     | T <sub>ON</sub> – 2               | $V_{IN}$ = 95 V, $R_{ON}$ = 200 k $\Omega$ | $T_J = -40^{\circ}C$ to $125^{\circ}C$                          | 200      |       | 420  | ns  |

|                     | Remote shutdown                   |                                            | T <sub>J</sub> = 25°C                                           |          | 0.7   |      |     |

|                     | threshold                         | Rising                                     | $T_J = -40^{\circ}C$ to $125^{\circ}C$                          | 0.4      |       | 1.05 | V   |

|                     | Remote shutdown                   |                                            |                                                                 |          | 35    |      | m∖  |

|                     | hysteresis                        |                                            |                                                                 |          |       |      |     |

| MINIMUN             | A OFF-TIME                        |                                            |                                                                 |          |       |      |     |

|                     | Minimum off-timer                 | V <sub>FB</sub> = 0 V                      |                                                                 |          | 300   |      | ns  |

| REGULA              | TION AND OV COMPARATO             |                                            | T 0500                                                          |          | c -   |      |     |

|                     | FB reference threshold            | Internal reference, trip point for         | $T_J = 25^{\circ}C$                                             |          | 2.5   |      | V   |

|                     |                                   | switch ON                                  | $T_J = -40^{\circ}C$ to $125^{\circ}C$                          | 2.445    |       | 2.55 |     |

|                     | FB overvoltage threshold          | Trip point for switch OFF                  |                                                                 | <u> </u> | 2.875 |      | V   |

|                     | FB bias current                   |                                            |                                                                 |          | 100   |      | nA  |

| THERMA              | L SHUTDOWN                        |                                            |                                                                 |          |       |      |     |

| Tsd                 | Thermal shutdown temperature      |                                            |                                                                 |          | 165   |      | °C  |

|                     | Thermal shutdown<br>hysteresis    |                                            |                                                                 |          | 25    |      | °C  |

|                     |                                   |                                            |                                                                 | -        |       |      |     |

(1) All electrical characteristics having room temperature limits are tested during production with  $T_A = T_J = 25^{\circ}$ C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

ZHCSIX0H-MARCH 2009-REVISED OCTOBER 2018

www.ti.com.cn

# 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                       | TEST                                                                                         | TEST CONDITIONS                        |     | TYP  | MAX  | UNIT |

|---------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------|-----|------|------|------|

| Puck owitch P                   | L _ 200 mA                                                                                   | $T_J = 25^{\circ}C$                    |     | 1.25 |      | Ω    |

| Buck switch R <sub>DS(on)</sub> | $R_{DS(on)}$ $I_{TEST} = 200 \text{ mA}$ $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ | $T_J = -40^{\circ}C$ to $125^{\circ}C$ |     |      | 2.57 | 52   |

|                                 |                                                                                              | $T_J = 25^{\circ}C$                    |     | 3.8  |      | V    |

| Gate drive UVLO                 | V <sub>BST</sub> – V <sub>SW</sub> rising                                                    | $T_J = -40^{\circ}C$ to $125^{\circ}C$ | 2.8 |      | 4.8  |      |

| Gate drive UVLO hysteresis      |                                                                                              | At 1 mA                                |     | 490  |      | mV   |

| Pre-charge switch voltage       | At 1 mA                                                                                      |                                        |     | 0.8  |      | V    |

| Pre-charge switch on-time       |                                                                                              |                                        |     | 150  |      | ns   |

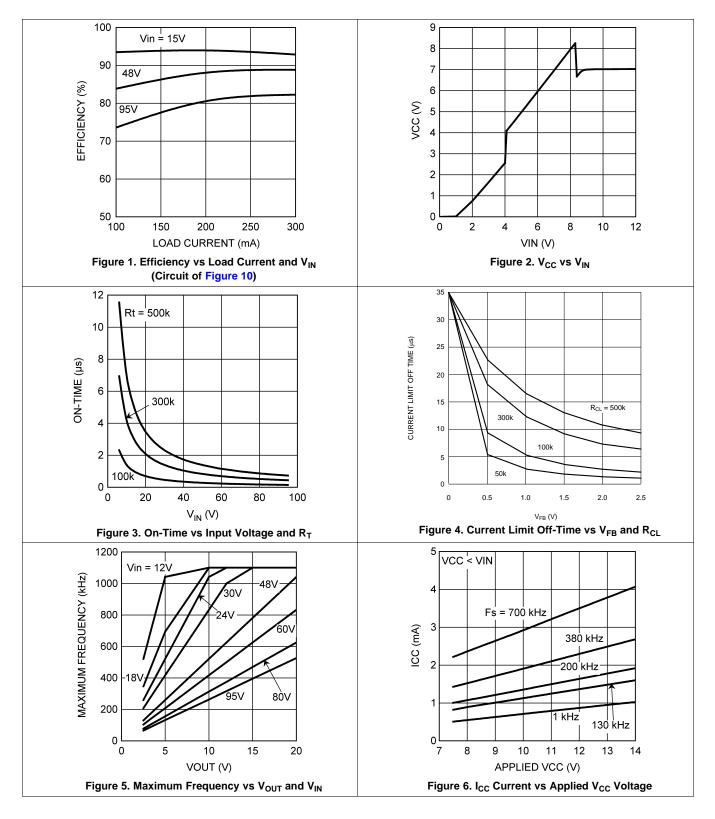

# 6.7 Typical Characteristics

TEXAS INSTRUMENTS

www.ti.com.cn

# 7 Detailed Description

## 7.1 Overview

The LM5008A regulator is an easy-to-use buck DC-DC converter that operates from 6-V to 95-V supply voltage. The device is intended for step-down conversions from 12-V, 24-V, and 48-V unregulated, semi-regulated and fully-regulated supply rails. With integrated buck power MOSFET, the LM5008A delivers up to 350-mA DC load current with exceptional efficiency and low input quiescent current in a very small solution size.

Designed for simple implementation, a nearly fixed-frequency, constant on-time (COT) operation with discontinuous conduction mode (DCM) at light loads is ideal for low-noise, high current, fast transient load requirements. Control loop compensation is not required reducing design time and external component count.

The LM5008A incorporates other features for comprehensive system requirements, including VCC undervoltage lockout (UVLO), gate drive undervoltage lockout, maximum duty cycle limiter, intelligent current limit off-timer, a pre-charge switch, and thermal shutdown with automatic recovery. These features enable a flexible and easy-to-use platform for a wide range of applications. The pin arrangement is designed for simple and optimized PCB layout, requiring only a few external components.

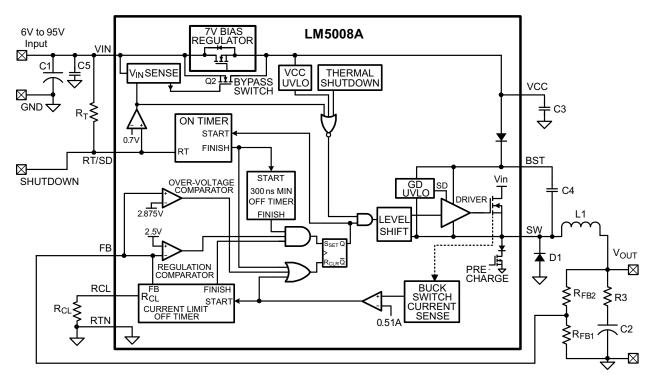

# 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 7.3 Feature Description

## 7.3.1 Control Circuit Overview

The LM5008A is a buck DC-DC regulator that uses a control scheme in which the on-time varies inversely with line voltage ( $V_{IN}$ ). Control is based on a comparator and the on-time one-shot, with the output voltage feedback (FB) compared to an internal reference (2.5 V). If the FB level is below the reference the buck switch is turned on for a fixed time determined by the line voltage and a programming resistor ( $R_T$ ). Following the ON period, the switch remains off for at least the minimum off-timer period of 300 ns. If FB is still below the reference at that time, the switch turns on again for another on-time period. This continues until regulation is achieved.

#### Feature Description (continued)

The LM5008A operates in discontinuous conduction mode at light load currents, and continuous conduction mode at heavy load current. In discontinuous conduction mode, current through the output inductor starts at zero and ramps up to a peak during the on-time, then ramps back to zero before the end of the off-time. The next on-time period starts when the voltage at FB falls below the internal reference; until then, the inductor current remains zero. In this mode, the operating frequency is lower than in continuous conduction mode and varies with load current. Therefore, at light loads, the conversion efficiency is maintained because the switching losses reduce with the reduction in load and frequency. The discontinuous operating frequency can be calculated with Equation 1.

$$F = \frac{V_{OUT}^2 \times L \times 1.04 \times 10^{20}}{R_L \times (R_T)^2}$$

where

(1)

(3)

In continuous conduction mode, current flows continuously through the inductor and never ramps down to zero. In this mode the operating frequency is greater than the discontinuous mode frequency and remains relatively constant with load and line variations. The approximate continuous mode operating frequency can be calculated with Equation 2.

$$F = \frac{V_{OUT}}{1.385 \times 10^{-10} \times R_{T}}$$

(2)

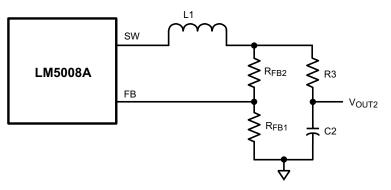

The output voltage ( $V_{OUT}$ ) is programmed by two external resistors as shown in the *Functional Block Diagram*. The regulation point can be calculated with Equation 3.

$$V_{OUT} = 2.5 \times (R_{FB1} + R_{FB2}) / R_{FB1}$$

The LM5008A regulates the output voltage based on ripple voltage at the feedback input, requiring a minimum amount of ESR for the output capacitor C2. A minimum of 25 mV to 50 mV of ripple voltage at the feedback pin (FB) is required for the LM5008A. In cases where the capacitor ESR is too small, additional series resistance may be required (R3 in the *Functional Block Diagram*).

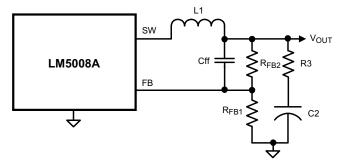

For applications where lower output voltage ripple is required, the output can be taken directly from a low-ESR output capacitor as shown in Figure 7. However, R3 slightly degrades the load regulation.

Copyright © 2016, Texas Instruments Incorporated

Figure 7. Low-Ripple Output Configuration

## 7.3.2 Start-Up Regulator (V<sub>CC</sub>)

The high voltage bias regulator is integrated within the LM5008A. The input pin (VIN) can be connected directly to line voltages between 6 V and 95 V, with transient capability to 100 V. Referring to the *Functional Block Diagram* and Figure 2, when V<sub>IN</sub> is between 6 V and the bypass threshold (nominally 8.5 V), the bypass switch (Q2) is on, and V<sub>CC</sub> tracks V<sub>IN</sub> within 100 mV to 150 mV. The bypass switch on-resistance is approximately 100  $\Omega$ , with inherent current limiting at approximately 100 mA. When V<sub>IN</sub> is above the bypass threshold Q2 is turned off, and V<sub>CC</sub> is regulated at 7 V. The V<sub>CC</sub> regulator output current is limited at approximately 9.2 mA. When the LM5008A is shut down using the RT/SD pin, the V<sub>CC</sub> bypass switch is shut off regardless of the voltage at V<sub>IN</sub>.

## Feature Description (continued)

When VIN exceeds the bypass threshold, the time required for Q2 to shut off is approximately 2  $\mu$ s to 3  $\mu$ s. The capacitor at VCC (C3) must be a minimum of 0.47  $\mu$ F to prevent the voltage at V<sub>CC</sub> from rising above its absolute maximum rating in response to a step input applied at V<sub>IN</sub>. C3 must be placed as close as possible to the VCC and RTN pins. In applications with a relatively high input voltage, power dissipation in the bias regulator is a concern. An auxiliary voltage of between 7.5 V and 14 V can be diode connected to the VCC pin to shut off the V<sub>CC</sub> regulator, thereby reducing internal power dissipation. The current required into the VCC pin is shown in Figure 6. Internally a diode connects VCC to VIN requiring that the auxiliary voltage be less than V<sub>IN</sub>.

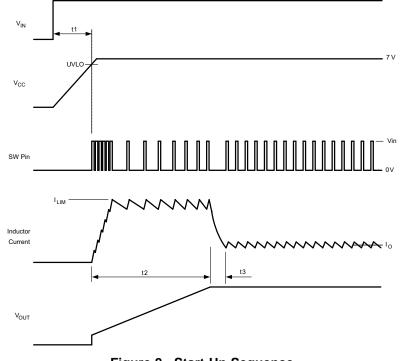

The turnon sequence is shown in Figure 8. During the initial delay (t1), VCC ramps up at a rate determined by its current limit and C3 while internal circuitry stabilizes. When  $V_{CC}$  reaches the upper threshold of its undervoltage lockout (UVLO, typically 5.3 V), the buck switch is enabled. The inductor current increases to the current limit threshold (I<sub>LIM</sub>), and during t2 the V<sub>OUT</sub> increases as the output capacitor charges up. When V<sub>OUT</sub> reaches the intended voltage the average inductor current decreases (t3) to the nominal load current (I<sub>O</sub>).

Figure 8. Start-Up Sequence

## 7.3.3 Regulation Comparator

The feedback voltage at FB is compared to an internal 2.5-V reference. In normal operation (the output voltage is regulated), an on-time period is initiated when the voltage at FB falls below 2.5 V. The buck switch stays on for the on-time, causing the FB voltage to rise above 2.5 V. After the on-time period, the buck switch stays off until the FB voltage again falls below 2.5 V. During start-up, the FB voltage is below 2.5 V at the end of each on-time, resulting in the minimum off-time of 300 ns. Bias current at the FB pin is nominally 100 nA.

## 7.3.4 Overvoltage Comparator

The feedback voltage at FB is compared to an internal 2.875-V reference. If the voltage at FB rises above 2.875 V, the on-time pulse is immediately terminated. This condition can occur if the input voltage or the output load change suddenly. The buck switch does not turn on again until the voltage at FB falls below 2.5 V.

## 7.3.5 On-Time Generator and Shutdown

The on-time for the LM5008A is determined by the  $R_T$  resistor and is inversely proportional to the input voltage (V<sub>IN</sub>), resulting in a nearly constant frequency as Vin is varied over its range. The on-time equation for the LM5008A is Equation 4.

### Feature Description (continued)

$T_{ON} = 1.385 \times 10^{-10} \times R_T / V_{IN}$

ZHCSIX0H-MARCH 2009-REVISED OCTOBER 2018

LM5008A

(4)

$R_T$  must be selected for a minimum on-time (at maximum  $V_{IN}$ ) greater than 400 ns, for proper current limit operation. This requirement limits the maximum frequency for each application, depending on  $V_{IN}$  and  $V_{OUT}$ .

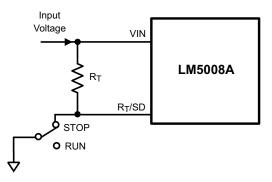

The LM5008A can be remotely disabled by taking the  $R_T/SD$  pin to ground. See Figure 9. The voltage at the  $R_T/SD$  pin is between 1.5 V and 3 V, depending on  $V_{IN}$  and the value of the  $R_T$  resistor.

Copyright © 2016, Texas Instruments Incorporated

#### Figure 9. Shutdown Implementation

### 7.3.6 Current Limit

The LM5008A contains an intelligent current limit OFF timer. If the current in the Buck switch exceeds 0.51 A the present cycle is immediately terminated and a non-resetable OFF timer is initiated. The length of off-time is controlled by an external resistor ( $R_{CL}$ ) and the FB voltage (see Figure 4). When FB = 0 V, a maximum off-time is required, and the time is preset to 35 µs. This condition occurs when the output is shorted and during the initial part of start-up. This amount of time ensures safe short-circuit operation up to the maximum input voltage of 95 V. In cases of overload where the FB voltage is above zero volts (not a short circuit), the current limit off-time is less than 35 µs. Reducing the off-time during less severe overloads reduces the amount of foldback, recovery time, and the start-up time. The off-time is calculated from Equation 5.

$$T_{OFF} = \frac{10^{-5}}{0.285 + \frac{V_{FB}}{(6.35 \times 10^{-6} \times R_{CL})}}$$

(5)

The current limit-sensing circuit is blanked for the first 50 ns to 70 ns of each on-time, so it is not falsely tripped by the current surge which occurs at turnon. The current surge is required by the re-circulating diode (D1) for its turnoff recovery.

#### 7.3.7 N-Channel Buck Switch and Driver

The LM5008A integrates an N-Channel Buck switch and associated floating high voltage gate driver. The gate driver circuit works in conjunction with an external bootstrap capacitor and an internal high voltage diode. A 0.01- $\mu$ F ceramic capacitor (C4) connected between the BST pin and SW pin provides the voltage to the driver during the on-time.

During each off-time, the SW pin is at approximately 0 V and the bootstrap capacitor charges from  $V_{CC}$  through the internal diode. The minimum off-timer, set to 300 ns, ensures a minimum time each cycle to recharge the bootstrap capacitor.

The internal pre-charge switch at the SW pin is turned on for  $\approx$  150 ns during the minimum off-time period, ensuring sufficient voltage exists across the bootstrap capacitor for the on-time. This feature helps prevent operating problems which can occur during very light-load conditions, involving a long off-time, during which the voltage across the bootstrap capacitor could otherwise reduce below the Gate Drive UVLO threshold. The pre-charge switch also helps prevent start-up problems which can occur if the output voltage is pre-charged prior to turnon. After current limit detection, the pre-charge switch is turned on for the entire duration of the forced off-time.

Copyright © 2009-2018, Texas Instruments Incorporated

(6)

## Feature Description (continued)

### 7.3.8 Thermal Protection

The LM5008A must be operated so the junction temperature does not exceed  $125^{\circ}$ C during normal operation. An internal Thermal Shutdown circuit is provided to shutdown the LM5008A in the event of a higher than normal junction temperature. When activated, typically at  $165^{\circ}$ C, the controller is forced into a low-power reset state by disabling the buck switch. This feature prevents catastrophic failures from accidental device overheating. When the junction temperature reduces below  $140^{\circ}$ C (typical hysteresis =  $25^{\circ}$ C), normal operation is resumed.

# 7.4 Device Functional Modes

### 7.4.1 Shutdown Mode

The RT/SD pin provides ON and OFF control for the LM5008A. When V<sub>SD</sub> is below approximately 0.7 V, the device is in shutdown mode. Both the internal LDO and the switching regulator are off. The quiescent current in shutdown mode drops to 110  $\mu$ A (typical) at V<sub>IN</sub> = 48 V. The LM5008A also employs V<sub>CC</sub> bias rail undervoltage protection. If the V<sub>CC</sub> bias supply voltage is below its UV threshold, the regulator remains off.

# 7.4.2 Active Mode

LM5008A is in active mode when the internal bias rail, VCC, is above its UV threshold. Depending on the load current, the device operates in either DCM or CCM mode.

Whenever the load current is reduced to a level less than half the peak-to-peak inductor ripple current, the device enters discontinuous conduction mode (DCM). Calculate the critical conduction boundary using Equation 6.

$$I_{\text{BOUNDARY}} = \frac{\Delta I_{\text{L}}}{2} = \frac{V_{\text{OUT}} \cdot (1 - D)}{2 \cdot L_{\text{F}} \cdot F_{\text{SW}}}$$

When the inductor current reaches zero, the SW node becomes high impedance. Resonant ringing occurs at SW as a result of the LC tank circuit formed by the buck inductor and the parasitic capacitance at the SW node. At light loads, several pulses may be skipped in between switching cycles, effectively reducing the switching frequency and further improving light-load efficiency.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

LM5008A requires only a few external components to convert from a wide range of supply voltages to a fixed output voltage. To expedite and streamline the process of designing a LM5008A-based converter, a comprehensive LM5008A Quick-Start tool is available for download to assist the designer with component selection for a given application. WEBENCH<sup>®</sup> online software is also available to generate complete designs, leveraging iterative design procedures and access to comprehensive component databases. The following sections discuss a design procedure using a typical application example. Figure 10 shows the LM5008A in a configuration suitable for several application use cases. See the LM5008A EVM for more details.

## 8.2 Typical Application

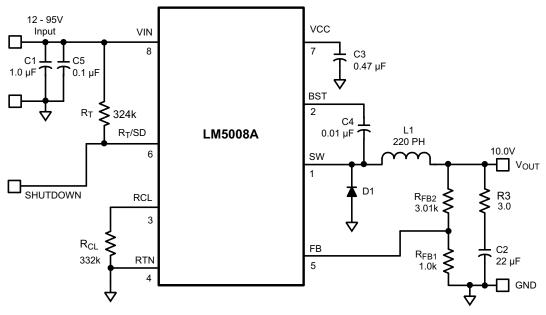

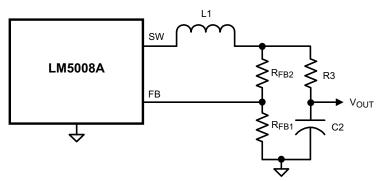

The final circuit is shown in Figure 10. The circuit was tested, and the resulting performance is shown in Figure 14 and Figure 15.

Copyright © 2016, Texas Instruments Incorporated

Figure 10. LM5008A Example Circuit

#### 8.2.1 Design Requirements

A guide for determining the component values is shown in Figure 10. Table 1 lists the bill of materials for this application example. The following steps configure the LM5008A:

- Input voltage range (V<sub>IN</sub>): 12 V to 95 V

- Output voltage (V<sub>OUT1</sub>): 10 V

- Load current (for continuous conduction mode): 100 mA to 300 mA

TEXAS INSTRUMENTS

www.ti.com.cn

# **Typical Application (continued)**

| ITEM             | DESCRIPTION          | PART NUMBER                                         | VALUE         |  |  |

|------------------|----------------------|-----------------------------------------------------|---------------|--|--|

| C1               | Ceramic Capacitor    | TDK C4532X7R2A105M                                  | 1 µF, 100 V   |  |  |

| C2               | Ceramic Capacitor    | TDK C4532X7R1E226M                                  | 22 µF, 25 V   |  |  |

| C3               | Ceramic Capacitor    | Kemet C1206C474K5RAC                                | 0.47 µF, 50 V |  |  |

| C4               | Ceramic Capacitor    | Kemet C1206C103K5RAC                                | 0.01 µF, 50 V |  |  |

| C5               | Ceramic Capacitor    | TDK C3216X7R2A104M                                  | 0.1 µF, 100 V |  |  |

| D1               | Schottky Power Diode | Diodes Inc. DFLS1100                                | 100 V, 1 A    |  |  |

| L1               | Power Inductor       | COILTRONICS DR125-221-R or<br>TDK SLF10145T-221MR65 | 220 µH        |  |  |

| R <sub>FB2</sub> | Resistor             | Vishay CRCW12063011F                                | 3.01 kΩ       |  |  |

| R <sub>FB1</sub> | Resistor             | Vishay CRCW12061001F                                | 1.0 kΩ        |  |  |

| R3               | Resistor             | Vishay CRCW12063R00F                                | 3.0 Ω         |  |  |

| R <sub>T</sub>   | Resistor             | Vishay CRCW12063243F                                | 324 kΩ        |  |  |

| R <sub>CL</sub>  | Resistor             | Vishay CRCW12063323F                                | 332 kΩ        |  |  |

| U1               | Switching Regulator  | LM5008A                                             |               |  |  |

#### Table 1. Bill of Materials

#### 8.2.2 Detailed Design Procedure

## 8.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LM5008A device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and output current ( $I_{OUT}$ ) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 8.2.2.2 Selection Of External Components

**R<sub>FB1</sub>**, **R<sub>FB2</sub>**: V<sub>OUT</sub> = V<sub>FB</sub> × (R<sub>FB1</sub> + R<sub>FB2</sub>) / R<sub>FB1</sub>, and because V<sub>FB</sub> = 2.5 V, the ratio of R<sub>FB2</sub> to R<sub>FB1</sub> calculates as 3:1. Standard values of 3.01 k $\Omega$  and 1 k $\Omega$  are chosen. Other values could be used as long as the 3:1 ratio is maintained.

$F_s$  and  $R_T$ : The recommended operating frequency range for the LM5008A is 50 kHz to 1.1 MHz. Unless the application requires a specific frequency, the choice of frequency is generally a compromise because it affects the size of L1 and C2 and the switching losses. The maximum allowed frequency, based on a minimum on-time of 400 ns, is calculated with Equation 7.

$F_{MAX} = V_{OUT} / (V_{INMAX} \times 400 \text{ ns})$

(7)

For this exercise,  $F_{MAX} = 263$  kHz. From Equation 2,  $R_T$  calculates to 274 k $\Omega$ . A standard value 324-k $\Omega$  resistor is used to allow for tolerances in Equation 2, resulting in a frequency of 223 kHz.

**L1:** The main parameter affected by the inductor is the output current ripple amplitude. The choice of inductor value therefore depends on both the minimum and maximum load currents, keeping in mind that the maximum ripple current occurs at maximum  $V_{IN}$ .

a. Minimum load current: To maintain continuous conduction at minimum lo (100 mA), the ripple amplitude

$(I_{OR})$  must be less than 200 mAp-p so the lower peak of the waveform does not reach zero. L1 is calculated using Equation 8.

$$L1 = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{I_{OR} \times F_s \times V_{IN}}$$

(8)

At V<sub>IN</sub> = 95 V, L1 (minimum) calculates to 200  $\mu$ H. The next larger standard value (220  $\mu$ H) is chosen and with this value I<sub>OR</sub> calculates to 182 mAp-p at V<sub>IN</sub> = 95 V, and 34 mAp-p at V<sub>IN</sub> = 12 V.

b. Maximum load current: At a load current of 300 mA, the peak of the ripple waveform must not reach the minimum value of the LM5008A's current limit threshold (410 mA). Therefore the ripple amplitude must be less than 220 mAp-p, which is already satisfied in Equation 8. With L1 = 220 μH, at maximum V<sub>IN</sub> and I<sub>O</sub>, the peak of the ripple is 391 mA. While L1 must carry this peak current without saturating or exceeding its temperature rating, it also must be capable of carrying the maximum value of the LM5008A's current limit threshold (610 mA) without saturating because the current limit is reached during start-up.

The DC resistance of the inductor must be as low as possible. For example, if the inductor's DCR is 1  $\Omega$ , the power dissipated at maximum load current is 0.09 W. While small, it is not insignificant compared to the load power of 3 W.

C3: The capacitor on the  $V_{CC}$  output provides not only noise filtering and stability, but its primary purpose is to prevent false triggering of the  $V_{CC}$  UVLO at the buck switch on and off transitions. C3 must be no smaller than 0.47  $\mu$ F.

**C2, and R3:** When selecting the output filter capacitor C2, the items to consider are ripple voltage due to its ESR, ripple voltage due to its capacitance, and the nature of the load.

**ESR and R3:** A low ESR for C2 is generally desirable to minimize power losses and heating within the capacitor. However, the regulator requires a minimum amount of ripple voltage at the feedback input for proper loop operation. For the LM5008A the minimum ripple required at pin 5 is 25 mVp-p, requiring a minimum ripple at V<sub>OUT</sub> of 100 mV. Because the minimum ripple current (at minimum V<sub>IN</sub>) is 34 mA p-p, the minimum ESR required at V<sub>OUT</sub> is 100 mV / 34 mA = 2.94  $\Omega$ . Because quality capacitors for SMPS applications have an ESR considerably less than this, R3 is inserted as shown in the *Functional Block Diagram*. R3's value, along with C2's ESR, must result in at least 25 mVp-p ripple at pin 5. Generally, R3 is 0.5 to 3  $\Omega$ .

**R**<sub>cL</sub>: When current limit is detected, the minimum off-time set by this resistor must be greater than the maximum normal off-time, which occurs at maximum input voltage. Using Equation 4, the minimum on-time is 472 ns, yielding an off-time of 4 μs (at 223 kHz). Due to the 25% tolerance on the on-time, the off-time tolerance is also 25%, yielding a maximum off-time of 5 μs. Allowing for the response time of the current limit detection circuit (350 ns) increases the maximum off-time to 5.35 μs. This is increased an additional 25% to 6.7 μs to allow for the tolerances of Equation 5. Using Equation 5, R<sub>CL</sub> calculates to 325 kΩ at V<sub>FB</sub> = 2.5 V. A standard value 332-kΩ resistor is used.

**D1:** The important parameters are reverse recovery time and forward voltage. The reverse recovery time determines how long the reverse current surge lasts each time the buck switch is turned on. The forward voltage drop is significant in the event the output is short-circuited as it is only this diode's voltage which forces the inductor current to reduce during the forced off-time. For this reason, a higher voltage is better, although that affects efficiency. A good choice is a Schottky power diode, such as the DFLS1100. D1's reverse voltage rating must be at least as great as the maximum  $V_{IN}$ , and its current rating be greater than the maximum current limit threshold (610 mA).

**C1:** This capacitor's purpose is to supply most of the switch current during the on-time, and limit the voltage ripple at  $V_{IN}$ , on the assumption that the voltage source feeding  $V_{IN}$  has an output impedance greater than zero. At maximum load current, when the buck switch turns on, the current into pin 8 suddenly increases to the lower peak of the output current waveform, ramp up to the peak value, then drop to zero at turnoff. The average input current during this on-time is the load current (300 mA). For a worst-case calculation, C1 must supply this average load current during the maximum on-time. To keep the input voltage ripple to less than 2 V (for this exercise), C1 is calculated with Equation 9.

$$C1 = \frac{I \times t_{ON}}{\Delta V} = \frac{0.3A \times 3.74 \ \mu S}{2.0 \ V} = 0.56 \ \mu F$$

(9)

Quality ceramic capacitors in this value have a low ESR which adds only a few millivolts to the ripple. It is the capacitance which is dominant in this case. To allow for the capacitor's tolerance, temperature effects, and voltage effects, a 1-µF, 100-V, X7R capacitor is used.

#### LM5008A ZHCSIX0H-MARCH 2009-REVISED OCTOBER 2018

www.ti.com.cn

C4: The recommended value is 0.01 µF for C4, as this is appropriate in the majority of applications. A highquality ceramic capacitor with low ESR is recommended as C4 supplies the surge current to charge the buck switch gate at turnon. A low ESR also ensures a quick recharge during each off-time. At minimum V<sub>IN</sub>, when the on-time is at maximum, it is possible during start-up that C4 does not fully recharge during each 300-ns off-time. The circuit is not able to complete the start-up, and achieve output regulation. This can occur when the frequency is intended to be low (for example,  $R_T$  = 500 K). In this case C4 must be increased so it can maintain sufficient voltage across the buck switch driver during each on-time.

C5: This capacitor helps avoid supply voltage transients and ringing due to long lead inductance at V<sub>IN</sub>. A low-ESR, 0.1-µF ceramic chip capacitor is recommended placed close to the LM5008A.

## 8.2.2.3 Low-Output Ripple Configurations

For applications where low-output ripple is required, the following options can be used to reduce or nearly eliminate the ripple:

a. Reduced ripple configuration: In Figure 11, Cff is added across R<sub>FB2</sub> to AC-couple the ripple at V<sub>OUT</sub> directly to the FB pin. This allows the ripple at V<sub>OUT</sub> to be reduced to a minimum of 25 mVp-p by reducing R3, because the ripple at V<sub>OUT</sub> is not attenuated by the feedback resistors. The minimum value for Cff is determined by Equation 10:

$$Cff = \frac{3 \times t_{ON(max)}}{(R_{FB1} / / R_{FB2})}$$

where

$t_{ON(max)}$  is the maximum on-time, which occurs at  $V_{IN(min)}$ . The next larger standard value capacitor must be used for Cff. (10)

Copyright © 2016, Texas Instruments Incorporated

Figure 11. Reduced Ripple Configuration

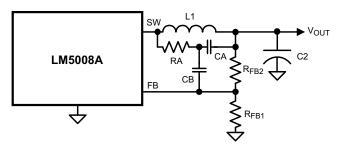

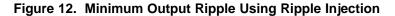

b. Minimum ripple configuration: If the application requires a lower value of ripple (<10 mVp-p), the circuit of Figure 12 can be used. R3 is removed, and the resulting output ripple voltage is determined by the inductor's ripple current and C2's characteristics. RA and CA are chosen to generate a sawtooth waveform at their junction, and that voltage is AC-coupled to the FB pin through CB. To determine the values for RA, CA, and CB, use the following procedure in Equation 11:

Calculate  $V_A = V_{OUT} - (V_{SW} \times (1 - (V_{OUT}/V_{IN(min)})))$

where

V<sub>SW</sub> is the absolute value of the voltage at the SW pin during the off-time (typically 1 V). VA is the DC voltage at the RA/CA junction, and is used in Equation 12. (11)

Calculate RA × CA =  $(V_{IN(min)} - V_A) \times t_{ON}/\Delta V$

where

$t_{ON}$  is the maximum on-time (at minimum input voltage), and  $\Delta V$  is the desired ripple amplitude at the RA/CA junction (typically 40-50 mV). RA and CA are then chosen from standard value components to satisfy the above product. Typically CA is 1000 pF to 5000 pF, and RA is 10 k $\Omega$  to 300 k $\Omega$ . CB is then chosen large compared to CA, typically 0.1 µF.

(12)

Copyright © 2016, Texas Instruments Incorporated

c. Alternate minimum ripple configuration: The circuit in Figure 13 is the same as that in the *Functional Block Diagram*, except the output voltage is taken from the junction of R3 and C2. The ripple at V<sub>OUT</sub> is determined by the inductor's ripple current and C2's characteristics. However, R3 slightly degrades the load regulation. This circuit may be suitable if the load current is fairly constant.

Copyright © 2016, Texas Instruments Incorporated

Figure 13. Alternate Minimum Output Ripple Configuration

#### 8.2.3 Application Curves

# 9 Power Supply Recommendations

The LM5008A converter is designed to operate from a wide input voltage range from 6 V to 95 V. The characteristics of the input supply must be compatible with the *Absolute Maximum Ratings* and *Recommended Operating Conditions*. In addition, the input supply must be capable of delivering the required input current to the fully-loaded regulator. Estimate the average input current with Equation 13.

$$I_{IN} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta}$$

where

• η is the efficiency

(13)

If the converter is connected to an input supply through long wires or PCB traces with large impedance, special care is required to achieve stable performance. The parasitic inductance and resistance of the input cables may have an adverse affect on converter operation. The parasitic inductance in combination with the low-ESR ceramic input capacitors form an underdamped resonant circuit. This circuit can cause overvoltage transients at VIN each time the input supply is cycled ON and OFF. The parasitic resistance causes the input voltage to dip during a load transient. If the regulator is operating close to the minimum input voltage, this dip can cause false UVLO fault triggering and a system reset. The best way to solve such issues is to reduce the distance from the input supply to the regulator and use an aluminum or tantalum input capacitor in parallel with the ceramics. The moderate ESR of the electrolytic capacitors helps to damp the input resonant circuit and reduce any voltage overshoots. A capacitance in the range of 10  $\mu$ F to 47  $\mu$ F is usually sufficient to provide input damping and helps to hold the input voltage steady during large load transients.

An EMI input filter is often used in front of the regulator that, unless carefully designed, can lead to instability as well as some of the effects mentioned above. The user's guide *Simple Success Wth Conducted EMI for DC-DC Converters* (SNVA489) provides helpful suggestions when designing an input filter for any switching regulator.

# 10 Layout

## **10.1 Layout Guidelines**

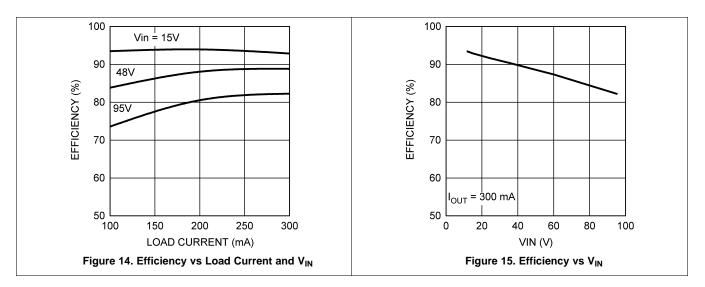

The LM5008A regulation and overvoltage comparators are very fast, and as such responds to short-duration noise pulses. Layout considerations are therefore critical for optimum performance:

- 1. Minimize the area of the high di/dt switching current loop consisting of the VIN pin, input ceramic capacitor, SW node and freewheeling power diode. Keep the input capacitor as close as possible to the VIN pin and route a short, direct connection to the RTN pin using polygon copper pours.

- 2. Minimize SW copper area to reduce radiated noise related to high dv/dt.

- 3. Locate all components as physically close as possible to their respective pins, thereby minimizing noise pickup in the printed-circuit tracks.

- 4. The FB trace should be away from noise sources and inductors. The lower feedback resistor should connect to ground close to the IC RTN.

If the internal dissipation of the LM5008A converter produces excessive junction temperatures during normal operation, optimal use of the PCB ground plane can help considerably to dissipate heat. The exposed pad on the bottom of the WSON-8 package can be soldered to a ground plane on the PCB, and that plane should extend out from beneath the IC to help dissipate the heat. Additionally, the use of wide PCB traces for power connection can also help conduct heat away from the IC. Judicious positioning of the LM5008A converter within the end product, along with use of any available air flow (forced or natural convection), can help reduce the operating junction temperature.

## 10.2 Layout Example

Figure 16. LM5008A PCB Layout Example

TEXAS INSTRUMENTS

www.ti.com.cn

# 11 器件和文档支持

# 11.1 器件支持

#### 11.1.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

## 11.1.2 使用 WEBENCH® 工具创建定制设计

单击此处,使用 LM5008A 器件及其 WEBENCH® 电源设计器创建定制设计。

- 1. 首先输入输入电压 (V<sub>IN</sub>)、输出电压 (V<sub>OUT</sub>) 和输出电流 (I<sub>OUT</sub>) 要求。

- 2. 使用优化器拨盘优化该设计的关键参数,如效率、尺寸和成本。

- 3. 将生成的设计与德州仪器 (TI) 的其他可行的解决方案进行比较。

WEBENCH 电源设计器可提供定制原理图以及罗列实时价格和组件供货情况的物料清单。

在多数情况下,可执行以下操作:

- 运行电气仿真,观察重要波形以及电路性能

- 运行热性能仿真,了解电路板热性能

- 将定制原理图和布局方案以常用 CAD 格式导出

- 打印设计方案的 PDF 报告并与同事共享

有关 WEBENCH 工具的详细信息,请访问 www.ti.com.cn/WEBENCH。

# 11.1.3 开发支持

相关开发支持请参阅以下资源:

- 有关 TI 的参考设计库,请访问 TI Designs

- 有关 TI WEBENCH 设计环境,请访问 WEBENCH<sup>®</sup> 设计中心

- 如需在 LM5008A 应用中选择 组件,请参阅 LM5008A 快速入门件计算器

## 11.2 文档支持

## 11.2.1 相关文档

请参阅如下相关文档:

- LM5008 快速入门计算器

- 《AN-1925 LM5008A 评估板》(SNVA380)

- 《AN-1330 LM5008 评估板》(SNVA090)

- 《支持宽输入/输出电压差异的降压稳压器拓朴》(SNVA594)

- 白皮书:

- 《评估适用于成本驱动型严苛应用的宽 V<sub>IN</sub>、低 EMI 同步降压 电路》

- 《电源的传导 EMI 规格概述》

- 《电源的辐射 EMI 规格概述》

## 11.2.1.1 PCB 布局资源

- 《AN-1149 开关电源布局指南》(SNVA021)

- 《AN-1229 Simple Switcher PCB 布局指南》(SNVA054)

- 构建电源 布局注意事项 (SLUP230)

- 《使用 LM4360x 与 LM4600x 简化低辐射 EMI 布局》(SNVA721)

- 《AN-2162: 轻松解决直流/直流转换器的传导 EMI 问题》(SNVA489)

- 《通过将电感寄生效应降至最低来降低降压转换器 EMI 和电压应力》(SLYT682)

- Power House 博客:

- 直流/直流转换器的高密度 PCB 布局

TEXAS INSTRUMENTS

#### www.ti.com.cn

#### 文档支持 (接下页)

#### 11.2.1.2 热设计资源

- 《AN-2020 热设计: 学会洞察先机,不做事后诸葛》(SNVA419)

- 《确保外露焊盘封装的最佳热阻性的 AN-1520 电路板布局指南》(SNVA183)

- 《半导体和 IC 封装热指标》(文献编号: SPRA953)

- 《使用 LM43603 和 LM43602 简化热设计》(SNVA719)

- 《PowerPAD™热增强型封装》(SLMA002)

- 《PowerPAD 速成》(文献编号: SLMA004)

- 《使用新的热指标》(SBVA025)

### 11.3 接收文档更新通知

要接收文档更新通知,请导航至 TI.com.cn 上的器件产品文件夹。单击右上角的通知我 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

## 11.4 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范, 并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 **71 参考设计支持** 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 11.5 商标

《PowerPAD, E2E are trademarks of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.6 静电放电警告

▶ 这些装置包含有限的内置 ESD 保护。存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损 伤。

### 11.7 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、缩写和定义。

#### 12 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更, 恕不另行通知, 且 不会对此文档进行修订。如需获取此数据表的浏览器版本,请查阅左侧的导航栏。

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|-----------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  | (.,    |              |                    |      | -              | (_)             | (6)                           | (-/                |              | ()                      |         |

| LM5008AMM/NOPB   | ACTIVE | VSSOP        | DGK                | 8    | 1000           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | SAYA                    | Samples |

| LM5008AMMX/NOPB  | ACTIVE | VSSOP        | DGK                | 8    | 3500           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | SAYA                    | Samples |

| LM5008ASD/NOPB   | ACTIVE | WSON         | NGU                | 8    | 1000           | RoHS & Green    | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | L00070A                 | Samples |

| LM5008ASDX/NOPB  | ACTIVE | WSON         | NGU                | 8    | 4500           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | L00070A                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

www.ti.com

9-Mar-2021

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

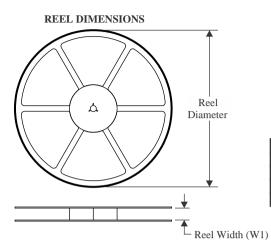

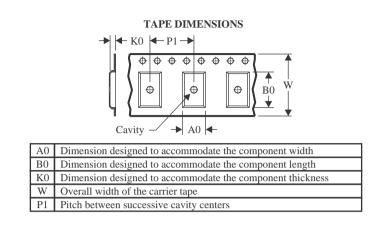

# TAPE AND REEL INFORMATION

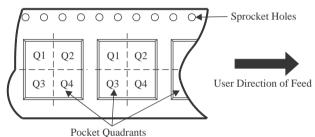

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM5008AMM/NOPB             | VSSOP           | DGK                | 8 | 1000 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LM5008AMM/NOPB             | VSSOP           | DGK                | 8 | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LM5008AMMX/NOPB            | VSSOP           | DGK                | 8 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LM5008ASD/NOPB             | WSON            | NGU                | 8 | 1000 | 180.0                    | 12.4                     | 4.3        | 4.3        | 1.1        | 8.0        | 12.0      | Q1               |

| LM5008ASDX/NOPB            | WSON            | NGU                | 8 | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

www.ti.com

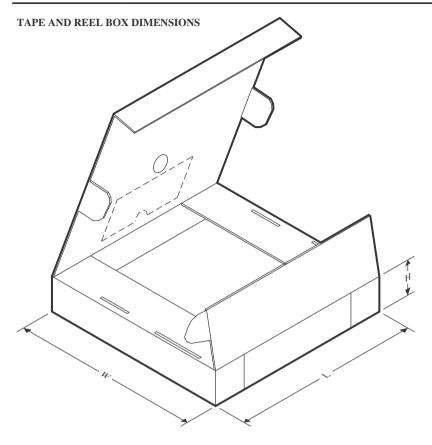

# PACKAGE MATERIALS INFORMATION

4-Jan-2024

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5008AMM/NOPB  | VSSOP        | DGK             | 8    | 1000 | 366.0       | 364.0      | 50.0        |

| LM5008AMM/NOPB  | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LM5008AMMX/NOPB | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

| LM5008ASD/NOPB  | WSON         | NGU             | 8    | 1000 | 200.0       | 183.0      | 25.0        |

| LM5008ASDX/NOPB | WSON         | NGU             | 8    | 4500 | 367.0       | 367.0      | 35.0        |

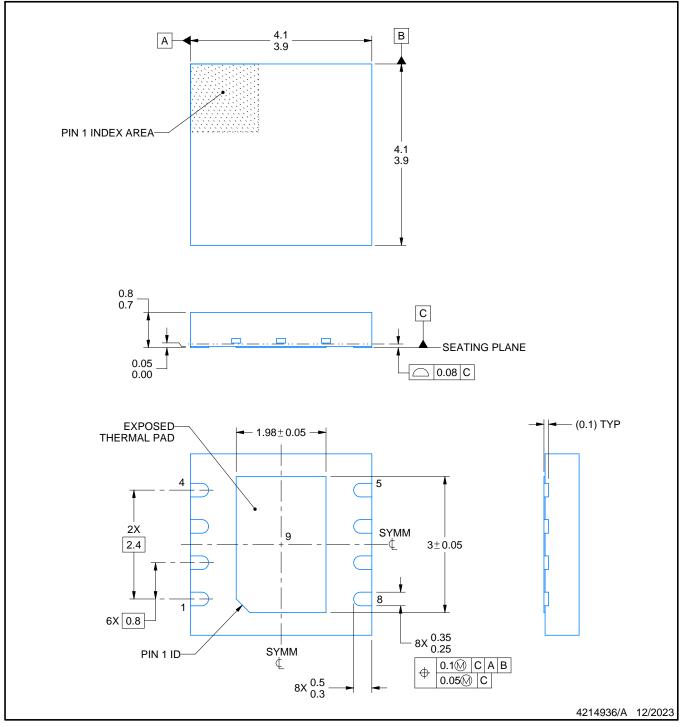

# NGU0008B

# **PACKAGE OUTLINE**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

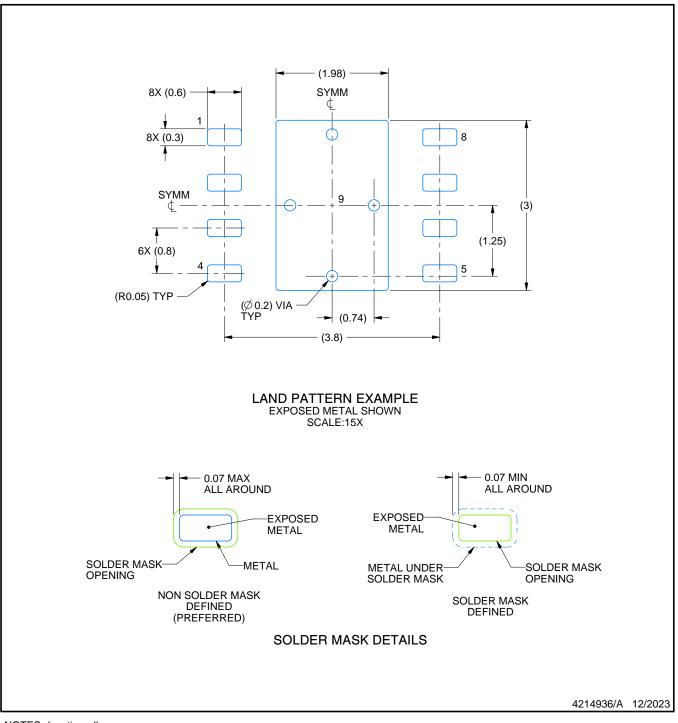

# **NGU0008B**

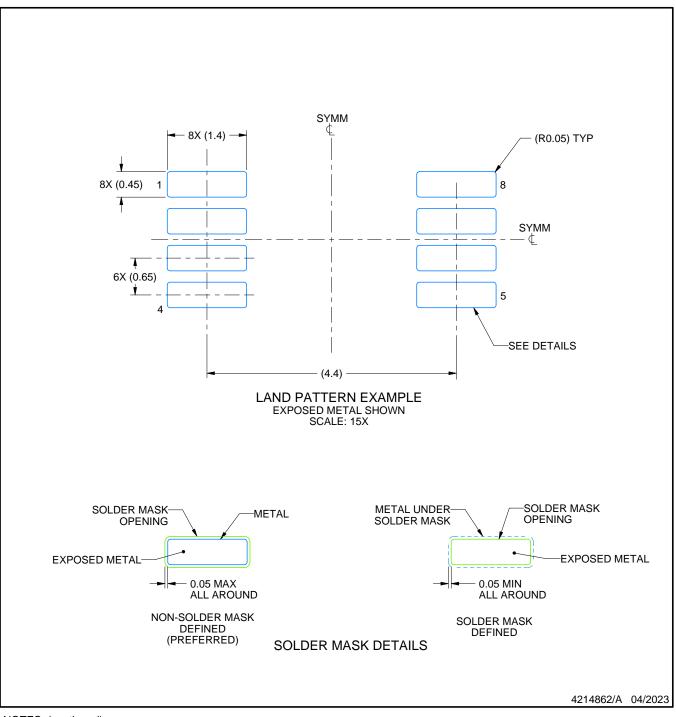

# **EXAMPLE BOARD LAYOUT**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

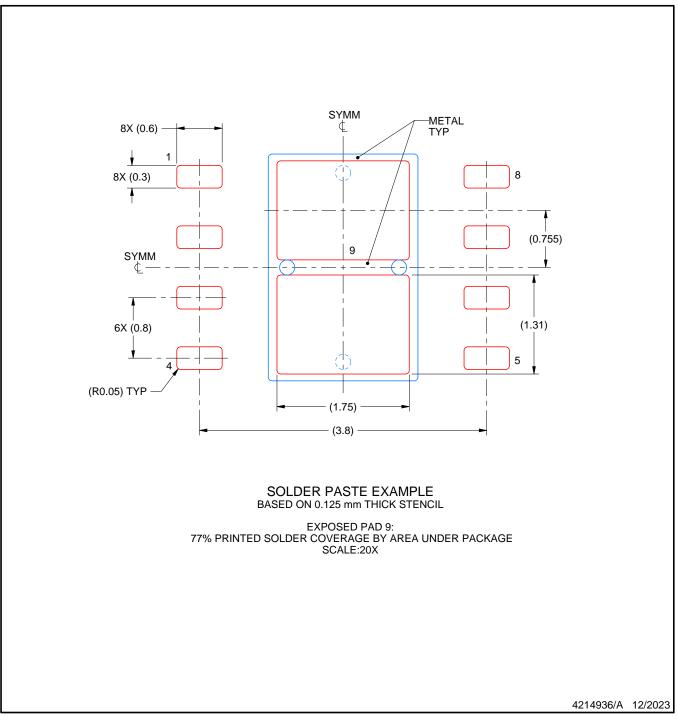

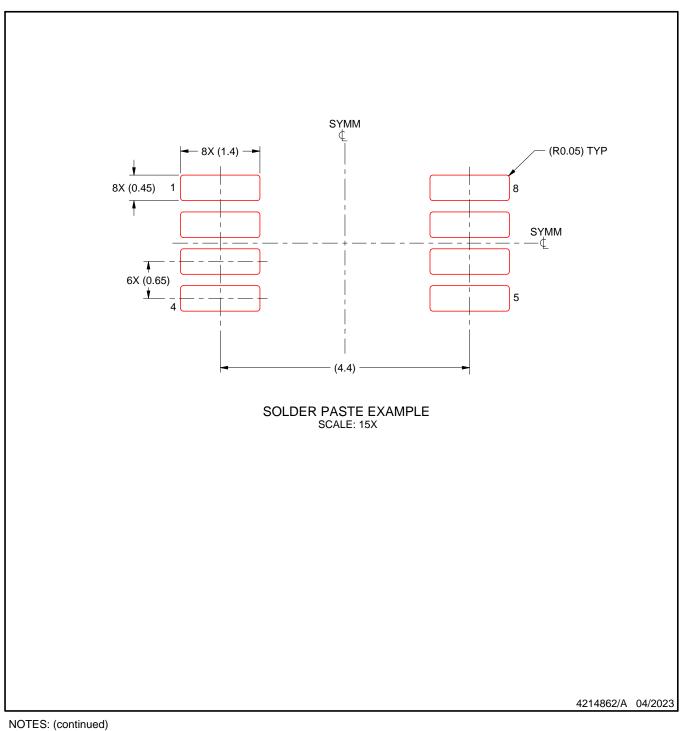

# **NGU0008B**

# **EXAMPLE STENCIL DESIGN**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

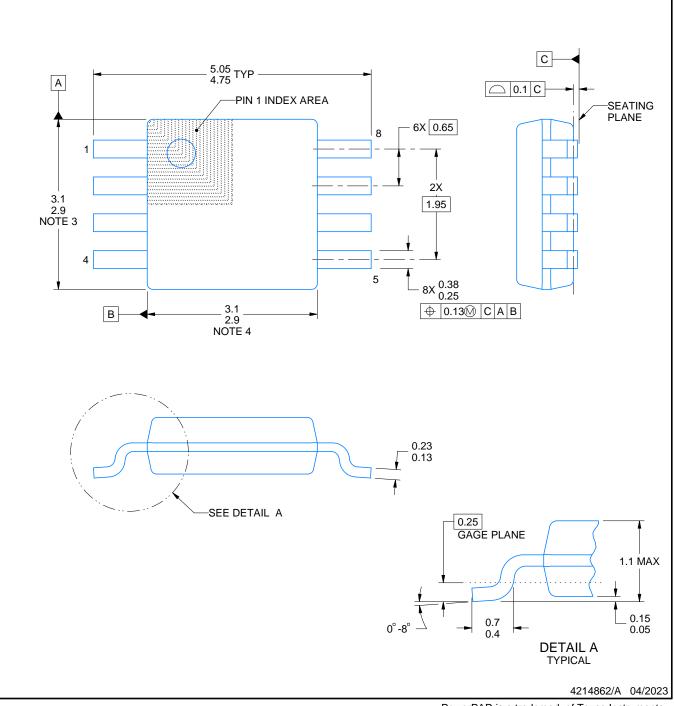

# **DGK0008A**

# **PACKAGE OUTLINE**

# VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

# DGK0008A

# **EXAMPLE BOARD LAYOUT**

# <sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown

on this view. It is recommended that vias under paste be filled, plugged or tented.

9. Size of metal pad may vary due to creepage requirement.

# DGK0008A

# **EXAMPLE STENCIL DESIGN**

# <sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源, 不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担 保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验 证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。 您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成 本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司