LM10507

ZHCSCG8-MAY 2014

# LM10507 三路降压 + 低压降稳压器 (LDO) 电源管理单元

## 特性

- 三个高效可编程降压稳压器

- 具有低 R<sub>DS-ON</sub> 的集成场效应晶体管 (FET)

- 降压稳压器运行时发生相移,以减少输入电流纹 波和电容器尺寸

- 可经由 SPI 接口进行编程的输出电压

- 过压和欠压闭锁

- 具有加电复位功能的自动内部软启动

- 电流过载和热关断保护

- 在轻负载条件下实现高效率的脉冲频率调制 (PFM) 模式

- 低压降稳压器 2.5V, 250mA

- 硬件 ENABLE 和 PWR\_OK 端子

- 在大约 3.5ms 时间内, 所有电压轨快速驱动至 PWR OK

- 稳压器输出上的快速关闭/有源放电

- 可编程降压稳压器:

- 降压 1: 0.9 3.4V; 1.6A

- 降压 2: 0.9 3.4V; 1A

- 降压 3: 0.865 1.5V; 1A

- ±3% 反馈电压精度

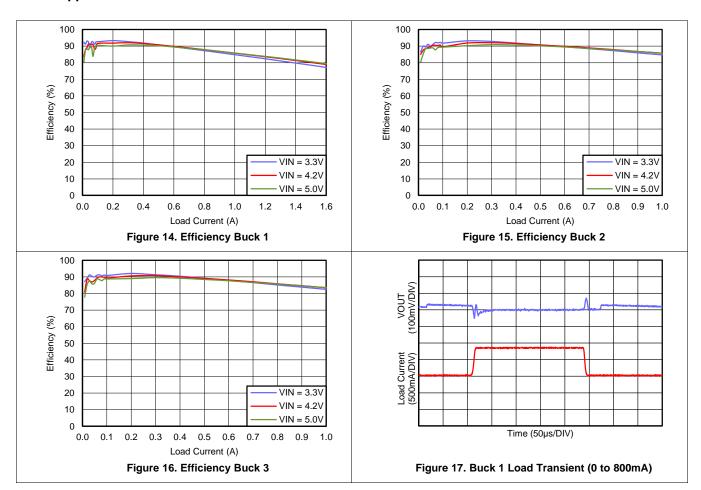

- 效率高达 95% 的降压稳压器

- 用于实现更小电感器尺寸的 2MHz 开关频率

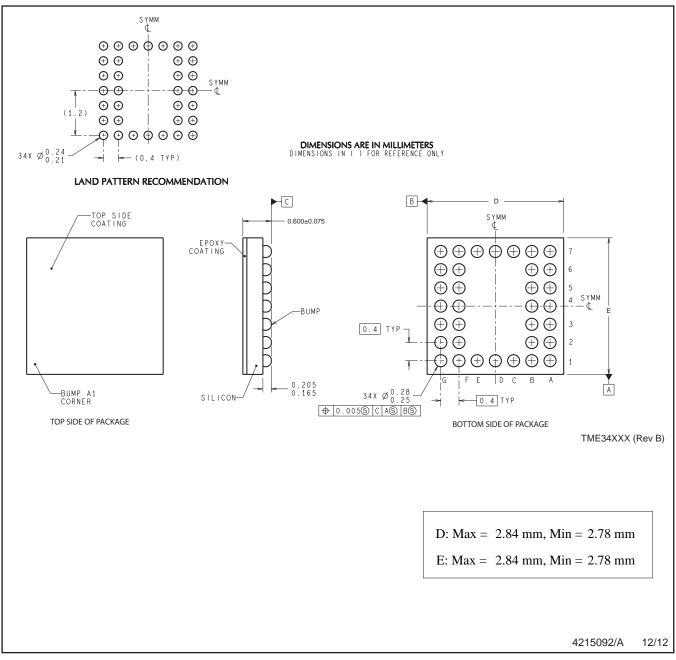

- 2.8mm x 2.8mm, 0.4mm 焊球间距, 34 焊锡凸 块 µSMD 封装

# 2 应用范围

固态硬盘

# 3 说明

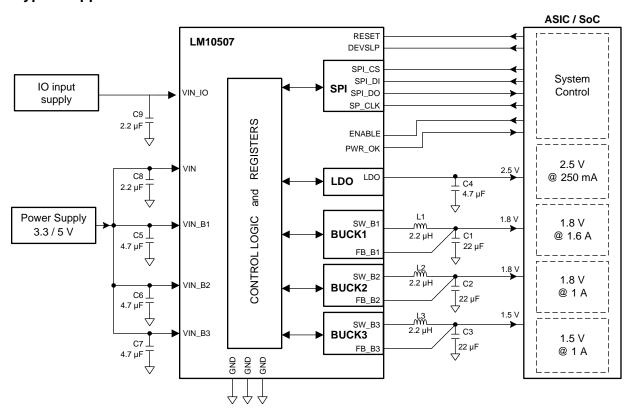

LM10507 是一款高级电源管理单元 (PMU), 它包含 3 个用来提供可变电压的可配置、高效降压稳压器。 此 器件非常适合为针对固态和闪存盘的特定用途集成电路 (ASIC) 和片上系统 (SOC) 设计提供支持。

LM10507 与 ASIC 一同运行,以通过 SPI 接口优化低 功率条件和节电模式下的电源电压。它还支持一个 2.5A 250mA LDO.

### 器件信息(1)

| 产品型号    | 封装                               | 封装尺寸 (标称值)      |

|---------|----------------------------------|-----------------|

| LM10507 | 芯片尺寸球状<br>引脚栅格阵列<br>(DSBGA) (34) | 2.82mm x 2.82mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

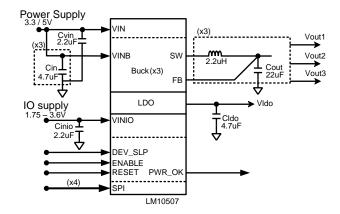

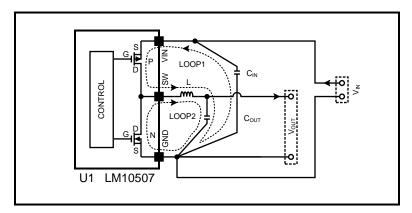

## 简化电路原理图

# 目录

| 1 | 特性1                                     |       | 8.1 Overview                         | 12 |

|---|-----------------------------------------|-------|--------------------------------------|----|

| 2 | 应用范围 1                                  |       | 8.2 Functional Block Diagram         | 12 |

| 3 |                                         |       | 8.3 Feature Description              | 12 |

| 4 | 简化电路原理图1                                |       | 8.4 Device Functional Modes          | 13 |

| 5 | 修订历史记录                                  |       | 8.5 Programming                      | 18 |

| 6 | Pin Configuration and Functions         |       | 8.6 Register Maps                    | 19 |

| - | _                                       | 9     | Applications and Implementation      | 23 |

| 7 | Specifications5                         |       | 9.1 Application Information          | 23 |

|   | 7.1 Absolute Maximum Ratings 5          |       | 9.2 Typical Application              |    |

|   | 7.2 Handling Ratings5                   | 10    | Power Supply Recommendations         |    |

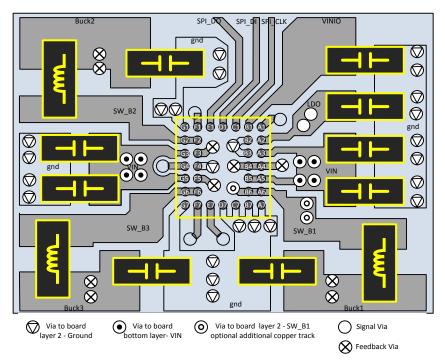

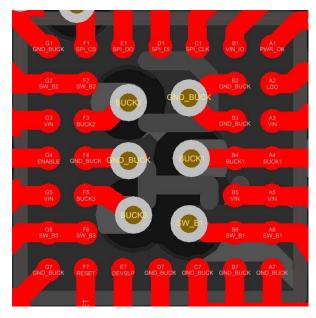

|   | 7.3 Recommended Operating Conditions    | 11    | Layout                               |    |

|   | 7.4 Thermal Information                 | • • • | 11.1 Layout Guidelines               |    |

|   | 7.5 General Electrical Characteristics6 |       | 11.2 Layout Example                  |    |

|   | 7.6 Buck 1 Electrical Characteristics 7 | 40    |                                      |    |

|   | 7.7 Buck 2 Electrical Characteristics 8 | 12    | 器件和文档支持                              |    |

|   | 7.8 Buck 3 Electrical Characteristics9  |       | 12.1 Trademarks                      | 33 |

|   | 7.9 LDO Electrical Characteristics      |       | 12.2 Electrostatic Discharge Caution | 33 |

|   | 7.10 Typical Characteristics            |       | 12.3 Glossary                        | 33 |

| 8 | Detailed Description                    | 13    | 机械封装和可订购信息                           | 34 |

| • | Totalisa Possipilari                    |       |                                      |    |

# 5 修订历史记录

| 日期         | 修订版本 | 注释    |

|------------|------|-------|

| 2014 年 5 月 | *    | 最初发布。 |

# 6 Pin Configuration and Functions

# 34 bump DSBGA with 0.4mm pitch TOP VIEW

### **Pin Functions**

| Р      | in   | 1/0 | Provident                                                                                                                            |

|--------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| Name   | No.  | 1/0 | Description                                                                                                                          |

| VIN_B1 | A/B5 | I   | Buck Switcher Regulator 1 - Power supply voltage input for power stage PFET, if buck 1 is not used, tie to ground to reduce leakage. |

| SW_B1  | A/B6 | 0   | Buck Switcher Regulator 1 - Power Switching node, connect to inductor                                                                |

| FB_B1  | A/B4 | I   | Buck Switcher Regulator 1 - Voltage output feedback for Buck Regulator 1                                                             |

| GND_B1 | A/B7 | G   | Buck Switcher Regulator 1 - Power ground for Buck Regulator                                                                          |

| VIN_B2 | G3   | ı   | Buck Switcher Regulator 2 - Power supply voltage input for power stage PFET, if buck 2 is not used, tie to ground to reduce leakage. |

| SW_B2  | F/G2 | 0   | Buck Switcher Regulator 2 - Power Switching node, connect to inductor                                                                |

| FB_B2  | F3   | I   | Buck Switcher Regulator 2 - Voltage output feedback for Buck Regulator 2                                                             |

| GND_B2 | G1   | G   | Buck Switcher Regulator 2 - Power ground for Buck Regulator                                                                          |

| VIN_B3 | G5   | I   | Buck Switcher Regulator 3 - Power supply voltage input for power stage PFET                                                          |

| SW_B3  | F/G6 | 0   | Buck Switcher Regulator 3 - Power Switching node, connect to inductor                                                                |

| FB_B3  | F5   | I   | Buck Switcher Regulator 3 - Voltage output feedback for Buck Regulator 3                                                             |

| GND_B3 | G7   | G   | Buck Switcher Regulator 3 - Power ground for Buck Regulator                                                                          |

| VIN    | А3   | I   | Power supply Input Voltage, must be present for device to work                                                                       |

| LDO    | A2   | 0   | LDO Regulator - LDO regulator output voltage                                                                                         |

| SPI_CS | F1   | I   | SPI Interface – chip select                                                                                                          |

| SPI_DI | D1   | I   | SPI Interface – serial data input                                                                                                    |

| SPI_DO | E1   | 0   | SPI Interface – serial data output                                                                                                   |

# Pin Functions (continued)

| P             | in                | 1/0            | Description                                                                                                                                                  |

|---------------|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name          | No.               | I/O            | Description                                                                                                                                                  |

| SPI_CLK       | C1                |                | SPI Interface – serial clock input                                                                                                                           |

| ENABLE        | G4                | 1              | Digital Input Control Signal to Enable/Disable PMIC. Signal Level is related to VIN_IO. This is an active High pin with an internal pull-down resistor.      |

| GND           | F4                | I              | Digital Input Control Signal – Not Used – Connect to GND.                                                                                                    |

| DEVSLP        | E7                | I              | Digital Input Control Signal for entering Device Sleep Mode – see table 1. This is an active High pin with an internal pull-down resistor.                   |

| RESET         | F7                | I              | Digital Input Control Signal to abort SPI transactions and resets the PMIC to default Voltages. This is an active Low pin with an internal pull-up resistor. |

| GND           | C7                |                | Not Used – Connect to GND.                                                                                                                                   |

| PWR_OK        | A1                | 0              | Digital Output of Power Good signal – all output rails are started.                                                                                          |

| VIN_IO        | B1                | Р              | Supply Voltage for Digital Interface Signals to ASIC like SPI, RESET, DEVSLP, ENABLE, PWR_OK.                                                                |

| GND           | B2                | G              | Ground. Connect to system Ground.                                                                                                                            |

| GND           | В3                | G              | Ground. Connect to system Ground.                                                                                                                            |

| GND           | D7                | G              | Ground. Connect to system Ground.                                                                                                                            |

| A: Analog Pin | D : Digital Pin G | : Ground Pin F | P: Power Pin I: Input Pin O: Output Pin                                                                                                                      |

ZHCSCG8-MAY 2014 www.ti.com.cn

## **Specifications**

# 7.1 Absolute Maximum Ratings<sup>(1)(2)(3)</sup>

|                                                                                                | MIN  | MAX | UNIT |

|------------------------------------------------------------------------------------------------|------|-----|------|

| VIN,                                                                                           | -0.3 | 6.0 | V    |

| VIN_IO, VIN_B1, VIN_B2, VIN_B3, SPI_CS, SPI_DI, SPI_CLK, SPI_DO, ENABLE, RESET, PWR_OK, DEVSLP | -0.3 | VIN | V    |

| Junction Temperature (T <sub>J-MAX</sub> )                                                     |      | 150 | °C   |

- (1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

- Internal thermal shutdown protects device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = +140°C and disengages at T<sub>J</sub> = +120°C (typ.). Thermal shutdown is ensured by design.

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

# 7.2 Handling Ratings

|                    |                          |                                                                  | MIN | MAX | UNIT |

|--------------------|--------------------------|------------------------------------------------------------------|-----|-----|------|

| T <sub>stg</sub>   | Storage temperature rang | e                                                                | -65 | 150 | ô    |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1) |     | 1.0 | kV   |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions (1)(2)

over operating free-air temperature range (unless otherwise noted)

|                                                                | /    |                         |      |

|----------------------------------------------------------------|------|-------------------------|------|

|                                                                | MIN  | MAX                     | UNIT |

| VIN_B1, VIN_B2_VIN_B3, VIN                                     | 3.0  | 5.5                     | V    |

| VIN_IO                                                         | 1.75 | 3.63, but less than VIN | V    |

| Junction Temperature (T <sub>J</sub> )                         | -30  | 125                     | °C   |

| Ambient Temperature (T <sub>A</sub> )                          | -30  | 85                      | °C   |

| Maximum Continuous Power Dissipation (P <sub>D-MAX</sub> ) (1) |      | 0.9                     | W    |

- (1) In applications where high power dissipation and/or poor thermal resistance is present the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = +125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

- The amount of Absolute Maximum power dissipation allowed for the device depends on the ambient temperature and can be calculated using the formula:  $P = (T_J - T_A)/\theta_{JA}$ , where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-toambient thermal resistance.  $\theta_{JA}$  is highly application and board-layout dependent. Internal thermal shutdown circuitry protects the device from permanent damage (see General Electrical Characteristics)

#### 7.4 Thermal Information

|                 | THERMAL METRIC                                        | TYP  | UNIT |

|-----------------|-------------------------------------------------------|------|------|

| $R_{\theta JA}$ | Junction-to-Ambient Thermal Resistance <sup>(1)</sup> | 44.5 | °C/W |

In applications where high power dissipation and/or poor thermal resistance is present the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = +125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

# NSTRUMENTS

# 7.5 General Electrical Characteristics (1)(2)(3)

| SYMBOL                    | PARAMETER                            | TEST CONDITIONS                                      | MIN                     | TYP | MAX                     | UNIT  |  |

|---------------------------|--------------------------------------|------------------------------------------------------|-------------------------|-----|-------------------------|-------|--|

| I <sub>Q(STANDBY)</sub>   | Quiescent Supply<br>Current          | DEVSLP=High Only Buck3 is ON ,PFM mode, no load. (4) |                         | 50  | 150                     | μA    |  |

| UNDER/OVERVOL             | TAGE LOCK OUT                        |                                                      |                         |     |                         |       |  |

| V <sub>UVLO_RISING</sub>  |                                      | LM10507-A <sup>(4)</sup>                             | 2.5                     | 2.8 | 2.95                    |       |  |

| V <sub>UVLO_FALLING</sub> |                                      | (4)                                                  | 2.35                    | 2.5 | 2.65                    | , , , |  |

| V <sub>OVLO_RISING</sub>  |                                      | LM10507-A <sup>(4)</sup> 5.7 5.9                     |                         | V   |                         |       |  |

| V <sub>OVLO_FALLING</sub> |                                      | LM10507-A <sup>(4)</sup>                             |                         |     |                         |       |  |

| DIGITAL INTERFA           | CE                                   |                                                      |                         |     |                         | *     |  |

| V <sub>IL</sub>           | Logic input low                      | SPI_CS, SPI_DI, SPI_CLK, ENABLE,                     |                         |     | $0.3*V_{VIN\_IO}$       |       |  |

| V <sub>IH</sub>           | Logic input high                     | RESET, DEVSLP (5)(4)                                 | 0.7*V <sub>VIN_I0</sub> |     |                         | Ī ,,  |  |

| V <sub>OL</sub>           | Logic output low                     |                                                      |                         |     | 0.2*V <sub>VIN_IO</sub> | V     |  |

| V <sub>OH</sub>           | Logic output high                    | PWR_OK (at 2mA load), SPI_DO (4)                     | 0.8*V <sub>VIN_IO</sub> |     |                         | 1     |  |

| I <sub>IL</sub>           | Input current, pindriven             | SPI_CS, SPI_DI, SPI_CLK, ENABLE, DEVSLP              | -2                      |     |                         | μA    |  |

| 12                        | low                                  | RESET                                                | -5                      |     |                         |       |  |

|                           | Input current, pindriven             | SPI_CS, SPI_DI, SPI_CLK, RESET                       |                         |     | 2                       |       |  |

| I <sub>IH</sub>           | high                                 | ENABLE, DEVSLP                                       |                         |     | 5                       | μA    |  |

| f <sub>SPI_MAX</sub>      | SPI max frequency                    | (4)                                                  |                         |     | 10                      | MHz   |  |

| t <sub>DEVSLP</sub>       | Minimum pulse width                  |                                                      |                         | 2   |                         | μs    |  |

| t <sub>RESET</sub>        | Minimum pulse width                  |                                                      |                         | 2   |                         |       |  |

| t <sub>ENABLE</sub>       | Minimum pulse width                  |                                                      |                         | 5   |                         | μs    |  |

| t <sub>COMP</sub>         | Transition time of PWR_OK output (5) |                                                      |                         | 0   | 1                       |       |  |

<sup>(1)</sup> All limits are ensured by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with  $T_J = 25$ °C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics. Unless otherwise noted,  $V_{IN} = 5.0V$  where:  $V_{IN} = V_{VIN\_B1} = V_{VIN\_B2} = V_{VIN\_B3}$ . Limits apply for  $T_J = 25^{\circ}C$  unless otherwise noted. Limits apply over the entire operating junction temperature range of  $-30^{\circ}C \le TA = TJ \le +85^{\circ}C$ . Specification ensured by design. Not tested during production.

# 7.6 Buck 1 Electrical Characteristics (1)(2)(3)(4)

| SYMBOL                      | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                | MIN  | TYP | MAX | UNIT |

|-----------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| IQ                          | DC Bias Current in V <sub>IN</sub>                    | No Load, PFM Mode <sup>(5)</sup>                                                                                                                               |      | 15  | 50  | μΑ   |

| I <sub>OUT-MAX</sub>        | Continuous maximum load current <sup>(6)</sup> (7)(8) | Buck 1 enabled, switching in PWM <sup>(5)</sup>                                                                                                                | 1.6  |     |     | А    |

| I <sub>PEAK</sub>           | Peak switching current limit                          | Buck 1 enabled, switching in PWM <sup>(5)</sup>                                                                                                                | 1.9  | 2.2 | 2.8 | Α    |

| η                           | Efficiency peak, Buck 1                               | I <sub>OUT</sub> = 0.3A, V <sub>VIN</sub> = 5.0 V                                                                                                              |      | 90% |     |      |

| F <sub>SW</sub>             | Switching Frequency <sup>(6)</sup>                    | (5)                                                                                                                                                            | 1.75 | 2   | 2.3 | MHz  |

| C <sub>IN</sub>             | Input Capacitor (6)                                   |                                                                                                                                                                |      | 4.7 |     |      |

| 0                           | Output Filter Capacitor (6)                           | 0 4 4                                                                                                                                                          | 10   | 10  | 100 | μF   |

| C <sub>OUT</sub>            | Output Capacitor ESR (6)                              | 0mA ≤ I <sub>OUT</sub> ≤ I <sub>OUT-MAX</sub>                                                                                                                  |      |     | 20  | mΩ   |

| L                           | Output Filter Inductance (6)                          |                                                                                                                                                                |      | 2.2 |     | μH   |

|                             | DC Line regulation <sup>(6)</sup>                     | $3.3V \le V_{IN} \le 5.0V$ , $I_{OUT} = I_{OUT-MAX}$                                                                                                           |      | 0.5 |     | %/V  |

| ΔVOUT                       | DC Load regulation, PWM <sup>(6)</sup>                | V <sub>VIN</sub> =5 V, 0.1 *I <sub>OUT-MAX</sub> ≤ I <sub>OUT</sub> ≤ I <sub>OUT-</sub>                                                                        |      | 0.3 |     | %/A  |

| I <sub>FB</sub>             | Feedback pininput bias current                        | V <sub>FB</sub> = 1 V <sup>(5)</sup>                                                                                                                           |      | 1.2 | 5   | μΑ   |

| V <sub>FB</sub>             | Feedback accuracy                                     | V <sub>FB</sub> =1 V <sup>(5)</sup>                                                                                                                            | -3%  |     | 3%  |      |

| Б                           | High Cids Codes On Designation                        | V <sub>IN</sub> =5.0 V                                                                                                                                         |      | 135 |     | 0    |

| R <sub>DS-ON-HS</sub>       | High Side Switch On Resistance                        | V <sub>IN</sub> = 2.6 V                                                                                                                                        |      | 215 |     | mΩ   |

| R <sub>DS-ON-LS</sub>       | Low Side Switch On Resistance                         | V <sub>VIN</sub> =5.0 V <sup>(5)</sup>                                                                                                                         |      | 85  | 190 | mΩ   |

| STARTUP                     |                                                       |                                                                                                                                                                |      |     |     |      |

| T <sub>START_NoLoad</sub>   | Internal soft-start (turn on time) (6)                | Startup from shutdown, V <sub>OUT</sub> = 0V, no load, LC = recommended circuit, using software enable, to V <sub>OUT</sub> = 95% of final value               |      | 0.1 |     | ms   |

| T <sub>START_FullLoad</sub> | Internal soft-start (turn on time) (6)                | Startup from shutdown, V <sub>OUT</sub> = 0V,<br>Maximum Load, LC = recommended<br>circuit, using software enable, to V <sub>OUT</sub><br>= 95% of final value |      | 0.5 |     | ms   |

- All limits are ensured by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with  $T_J = 25^{\circ}$ C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

- Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

- BUCK normal operation is ensured if  $V_{IN} \ge V_{OUT} + 1.0V$ .

- Unless otherwise noted,  $V_{IN} = 5.0V$  where:  $V_{IN} = V_{VIN\_B1} = V_{VIN\_B2} = V_{VIN\_B3}$ . Limits apply for  $T_J = 25^{\circ}C$  unless otherwise noted. Limits apply over the entire operating junction temperature range of  $-30^{\circ}C \le TA = TJ \le +85^{\circ}C$ .

- Specification ensured by design. Not tested during production.

- In applications where high power dissipation and/or poor thermal resistance is present the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = +125°C), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ), and the junction-to-ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

- The amount of Absolute Maximum power dissipation allowed for the device depends on the ambient temperature and can be calculated using the formula:  $P = (T_J - T_A)/\theta_{JA}$ , where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.  $\theta_{JA}$  is highly application and board-layout dependent. Internal thermal shutdown circuitry protects the device from permanent damage (see General Electrical Characteristics)

# 7.7 Buck 2 Electrical Characteristics (1)(2)(3)(4)

| SYMBOL                       | PARAMETER                                 | TEST CONDITIONS                                                                                                                                                | MIN  | TYP | MAX  | UNIT      |

|------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-----------|

| IQ                           | DC Bias Current in V <sub>IN</sub>        | No Load, PFM Mode <sup>(5)</sup>                                                                                                                               |      | 15  | 50   | μA        |

| I <sub>OUT -MAX</sub>        | Continuous maximum load current (6)(7)(8) | Buck 1 enabled, switching in PWM <sup>(5)</sup>                                                                                                                | 1    |     |      | А         |

| I <sub>PEAK</sub>            | Peak switching current limit              | Buck 1 enabled, switching in PWM <sup>(5)</sup>                                                                                                                | 1.35 | 1.6 | 1.85 | Α         |

| η                            | Efficiency peak, Buck 2                   | I <sub>OUT</sub> = 0.3A, V <sub>VIN</sub> = 5.0 V                                                                                                              |      | 90% |      |           |

| F <sub>SW</sub>              | Switching Frequency <sup>(6)</sup>        | (5)                                                                                                                                                            | 1.75 | 2   | 2.3  | MHz       |

| C <sub>IN</sub>              | Input Capacitor (6)                       |                                                                                                                                                                |      | 4.7 |      |           |

| C <sub>OUT</sub>             | Output Filter Capacitor                   | 0mA ≤ I <sub>OUT</sub> ≤I <sub>OUT-MAX</sub>                                                                                                                   | 10   | 10  | 100  | μF        |

| 001                          | Output Capacitor ESR (6)                  |                                                                                                                                                                |      |     | 20   | mΩ        |

| L                            | Output Filter Inductance (6)              |                                                                                                                                                                |      | 2.2 |      | μH        |

| ΔV <sub>OUT</sub>            | DC Line regulation (6)                    | $3.3 \text{ V} \leq \text{V}_{\text{IN}} \leq 5.0 \text{ V}, \text{I}_{\text{OUT}} = \text{I}_{\text{OUT-MAX}}$                                                |      | 0.5 |      | %/V       |

|                              | DC Load regulation <sup>(6)</sup> , PWM   | $VIN = 5 \text{ V}, 0.1*I_{OUT-MAX} \le I_{OUT} \le I_{OUTMAX}$                                                                                                |      | 0.3 |      | %/A       |

| I <sub>FB</sub>              | Feedback pininput bias current            | V <sub>FB</sub> = 1.8 V <sup>(5)</sup>                                                                                                                         |      | 2.2 | 5    | μΑ        |

| $V_{FB}$                     | Feedback accuracy                         | V <sub>FB</sub> = 2 V <sup>(5)</sup>                                                                                                                           | -3%  |     | -3%  |           |

| D                            | High Side Switch On                       | V <sub>VIN</sub> = 5.0 V                                                                                                                                       |      | 135 |      |           |

| R <sub>DS-ON-HS</sub>        | Resistance                                | V <sub>IN</sub> = 2.6 V                                                                                                                                        |      | 215 |      | $m\Omega$ |

| R <sub>DS-ON-LS</sub>        | Low Side Switch On Resistance             | $V_{VIN} = 5.0 V^{(5)}$                                                                                                                                        |      | 85  | 190  |           |

| STARTUP                      | •                                         |                                                                                                                                                                |      |     |      |           |

| T <sub>START_NoLoad</sub>    | Internal soft-start (turn on time)        | Startup from shutdown, $V_{OUT} = 0V$ , no load, LC = recommended circuit, using software enable, to $V_{OUT} = 95\%$ of final value                           |      | 0.1 |      | ms        |

| T <sub>START_</sub> FullLoad | Internal soft-start (turn on time)        | Start up from shutdown, V <sub>OUT</sub> =0V,<br>Maximum Load, LC = recommended<br>circuit, using software enable, to V <sub>OUT</sub> =<br>95% of final value |      | 0.5 |      | ms        |

- (1) All limits are ensured by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with  $T_J = 25^{\circ}$ C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

- Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

- BUCK normal operation is ensured if  $V_{IN} \ge V_{OUT} + 1.0V$ .

- Unless otherwise noted,  $V_{IN} = 5.0V$  where:  $V_{IN} = V_{VIN\_B1} = V_{VIN\_B2} = V_{VIN\_B3}$ . Limits apply for  $T_J = 25^{\circ}C$  unless otherwise noted. Limits apply over the entire operating junction temperature range of  $-30^{\circ}C \le TA = TJ \le +85^{\circ}C$ .

- Specification ensured by design. Not tested during production.

- In applications where high power dissipation and/or poor thermal resistance is present the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = +125°C), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ), and the junction-to-ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

- The amount of Absolute Maximum power dissipation allowed for the device depends on the ambient temperature and can be calculated using the formula:  $P = (T_J - T_A)/\theta_{JA}$ , where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.  $\theta_{JA}$  is highly application and board-layout dependent. Internal thermal shutdown circuitry protects the device from permanent damage (see General Electrical Characteristics)

TRUMENTS

# 7.8 Buck 3 Electrical Characteristics (1)(2)(3)(4)

| SYMBOL                      | PARAMETER                                            | TEST CONDITIONS                                                                                                                                                 | MIN  | TYP | MAX  | UNIT  |

|-----------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| IQ                          | DC Bias Current in V <sub>IN</sub>                   | No Load, PFM Mode (5)                                                                                                                                           |      | 15  | 50   | μA    |

| I <sub>OUT-MAX</sub>        | Continuous maximum load current <sup>(6)(7)(8)</sup> | Buck 1 enabled, switching in PWM <sup>(5)</sup>                                                                                                                 | 1    |     |      | А     |

| I <sub>PEAK</sub>           | Peak switching current limit                         | Buck 1 enabled, switching in PWM <sup>(5)</sup>                                                                                                                 | 1.35 | 1.6 | 1.85 | Α     |

| η                           | Efficiency peak, Buck 3 (6)                          | I <sub>OUT</sub> = 0.3A, V <sub>VIN</sub> =5.0 V                                                                                                                |      | 90% |      |       |

| F <sub>SW</sub>             | Switching Frequency <sup>(6)</sup>                   | (5)                                                                                                                                                             | 1.75 | 2   | 2.3  | MHz   |

| C <sub>IN</sub>             | Input Capacitor (6)                                  |                                                                                                                                                                 |      | 4.7 |      |       |

|                             | Output Filter Capacitor (6)                          | 04                                                                                                                                                              | 10   | 10  | 100  | μF    |

| C <sub>OUT</sub>            | Output Capacitor ESR (6)                             | 0mA ≤ I <sub>OUT</sub> ≤ I <sub>OUT-MAX</sub>                                                                                                                   |      |     | 20   | mΩ    |

| L                           | Output Filter Inductance (6)                         |                                                                                                                                                                 |      | 2.2 |      | μH    |

| A) (OLIT                    | DC Line regulation (6)                               | $3.3 \text{ V} \leq \text{V}_{\text{IN}} \leq 5.0 \text{ V}, \text{I}_{\text{OUT}} = \text{I}_{\text{OUT-MAX}}$                                                 |      | 0.5 |      | %/V   |

| ΔVOUT                       | DC Load regulation, PWM (6)                          | VIN=5 V, 0.1* I <sub>OUT-MAX</sub> ≤ I <sub>OUT</sub> ≥I <sub>OUT-MAX</sub>                                                                                     |      | 0.3 |      | %/A   |

| I <sub>FB</sub>             | Feedback pininput bias current                       | V <sub>FB</sub> = 1.5 V <sup>(5)</sup>                                                                                                                          |      | 1.0 | 5    | μΑ    |

| $V_{FB}$                    | Feedback accuracy                                    | V <sub>FB</sub> = 3 V <sup>(5)</sup>                                                                                                                            | -3%  |     | -3%  |       |

| D                           | High Side Switch On                                  | V <sub>VIN</sub> =5.0 V                                                                                                                                         |      | 135 |      |       |

| R <sub>DS-ON-HS</sub>       | Resistance                                           | V <sub>IN</sub> = 2.6 V                                                                                                                                         |      | 215 |      | mΩ    |

| R <sub>DS-ON-LS</sub>       | Low Side Switch On Resistance                        | V <sub>VIN</sub> =5.0 V <sup>(5)</sup>                                                                                                                          |      | 85  | 190  | 11152 |

| STARTUP                     |                                                      |                                                                                                                                                                 |      |     |      |       |

| T <sub>START_NoLoad</sub>   | Internal soft-start (turn on time) <sup>(6)</sup>    | Startup from shutdown, $V_{OUT} = 0$ V, no load, LC = recommended circuit, using software enable, to $V_{OUT} = 95\%$ of final value                            |      | 0.1 |      | ms    |

| T <sub>START_FullLoad</sub> | Internal soft-start (turn on time) <sup>(6)</sup>    | Start up from shutdown, V <sub>OUT</sub> =0 V,<br>Maximum Load, LC = recommended<br>circuit, using software enable, to V <sub>OUT</sub> =<br>95% of final value |      | 0.5 |      | ms    |

- (1) All limits are ensured by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

- (2) Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

- (3) BUCK normal operation is ensured if  $V_{IN} \ge V_{OUT} + 1.0 \text{ V}$ .

- Unless otherwise noted,  $V_{IN} = 5.0V$  where:  $V_{IN} = V_{VIN\_B1} = V_{VIN\_B2} = V_{VIN\_B3}$ . Limits apply for  $T_J = 25^{\circ}$ C unless otherwise noted.

- (5) Limits apply over the entire operating junction temperature range of -30°C ≤TA = TJ ≤ +85°C.

- (6) Specification ensured by design. Not tested during production.

- (7) In applications where high power dissipation and/or poor thermal resistance is present the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = +125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (P<sub>D-MAX</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>L-MAX-OP</sub> = (P<sub>L-A</sub> × P<sub>D-MAX</sub>).

- part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

(8) The amount of Absolute Maximum power dissipation allowed for the device depends on the ambient temperature and can be calculated using the formula: P = (T<sub>J</sub>-T<sub>A</sub>)/θ<sub>JA</sub>, where T<sub>J</sub> is the junction temperature, T<sub>A</sub> is the ambient temperature, and θ<sub>JA</sub> is the junction-to-ambient thermal resistance. θ<sub>JA</sub> is highly application and board-layout dependent. Internal thermal shutdown circuitry protects the device from permanent damage (see General Electrical Characteristics)

# **STRUMENTS**

# 7.9 LDO Electrical Characteristics (1)(2)(3)

| SYMBOL                 | PARAMETER                         | TEST CONDITION                                                                                 | TEST CONDITIONS                                                                                   |     |     |     | UNIT          |

|------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| V <sub>OUT</sub>       | Output Voltage Accuracy           | $I_{OUT} = 1 \text{mA}, V_{OUT} = 2.5 \text{ V}^{(4)}$                                         | $I_{OUT} = 1 \text{mA}, V_{OUT} = 2.5 \text{ V}^{(4)}$                                            |     |     | +3% |               |

| I <sub>OUT</sub>       | Maximum Output Current            | (4)                                                                                            |                                                                                                   | 250 |     |     | mA            |

| I <sub>SC</sub>        | Short-Circuit Current Limit       |                                                                                                |                                                                                                   |     | 0.5 |     | Α             |

| $V_{DO}$               | Dropout Voltage <sup>(5)</sup>    | I <sub>OUT</sub> = 250 mA <sup>(4)</sup>                                                       | I <sub>OUT</sub> = 250 mA <sup>(4)</sup>                                                          |     |     |     |               |

| A\/                    | Line Regulation                   | $3.3 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{I}_{\text{OUT}} = 1 \text{r}$ | $3.3 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{I}_{\text{OUT}} = 1 \text{mA}$   |     | 5   |     | mV            |

| $\Delta V_{OUT}$       | Load Regulation                   | 1mA ≤ I <sub>OUT</sub> ≤ 250 mA, V <sub>IN</sub> =                                             | $1 \text{mA} \le I_{\text{OUT}} \le 250 \text{ mA}, V_{\text{IN}} = 3.3 \text{ V}, 5.0 \text{ V}$ |     | 5   |     |               |

|                        | Out and Nation (6)                | 40.11- 46.4400.111-                                                                            | V <sub>IN</sub> = 5.0 V                                                                           |     | 10  |     |               |

| e <sub>N</sub>         | Output Noise Voltage (6)          | 10 Hz ≤ f ≤ 100 kHz                                                                            | V <sub>IN</sub> = 3.3 V                                                                           |     | 35  |     | $\mu V_{RMS}$ |

| DODD                   | D                                 | $F = 10 \text{ kHz}, C_{OUT} = 4.7 \mu F,$                                                     | V <sub>IN</sub> = 5.0 V                                                                           |     | 65  |     | j             |

| PSRR                   | Power Supply Rejection Ratio (6)  | I <sub>OUT</sub> = 20 mA                                                                       | V <sub>IN</sub> = 3.3 V                                                                           |     | 40  |     | dB            |

|                        | Startura Timo franco Shutdown (6) | C <sub>OUT</sub> = 4.7 μF I <sub>OUT</sub> =                                                   | V <sub>IN</sub> = 5.0 V                                                                           |     | 45  |     |               |

| t <sub>STARTUP</sub>   | Startup Time from Shutdown (6)    | 250mA                                                                                          | V <sub>IN</sub> = 3.3 V                                                                           |     | 60  |     | μs            |

| T <sub>TRANSIENT</sub> | Startup Transient Overshoot (6)   | $C_{OUT} = 4.7 \mu F I_{OUT} = 250 mA$                                                         | (4)                                                                                               |     |     | 30  | mV            |

<sup>(1)</sup> All limits are ensured by design, test and/or statistical analysis. All electrical characteristics having room-temperature limits are tested during production with  $T_J = 25^{\circ}$ C. All hot and cold limits are ensured by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

- Capacitors: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

- Unless otherwise noted,  $V_{IN} = 5.0V$  where:  $V_{IN} = V_{VIN\_B1} = V_{VIN\_B2} = V_{VIN\_B2}$ . Limits apply for  $T_J = 25^{\circ}$ C unless otherwise noted. Limits apply over the entire operating junction temperature range of  $-30^{\circ}$ C  $\leq$ TA = TJ  $\leq$  +85 $^{\circ}$ C. Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100 mV below its (<del>5</del>) nominal value.

- Specification ensured by design. Not tested during production.

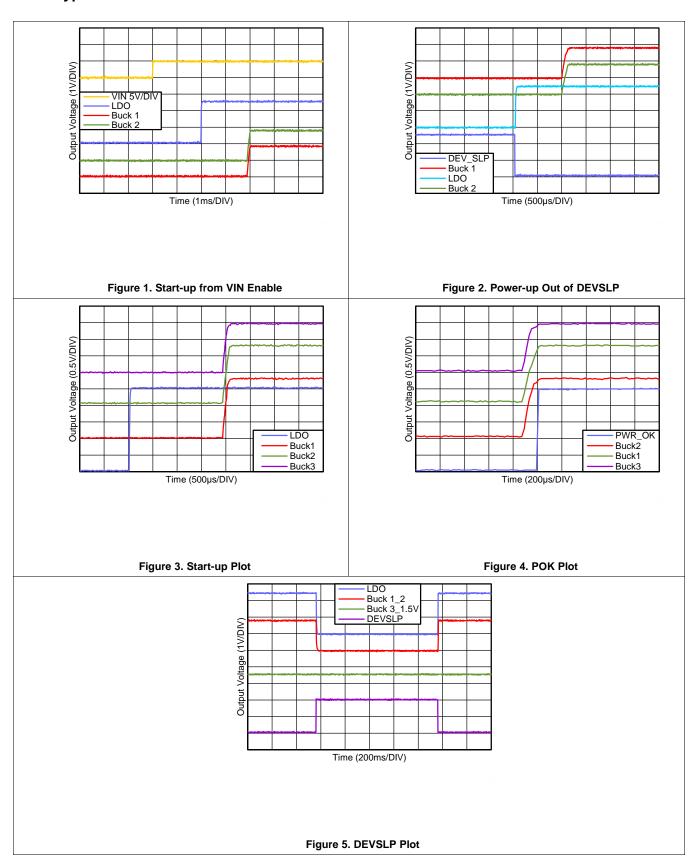

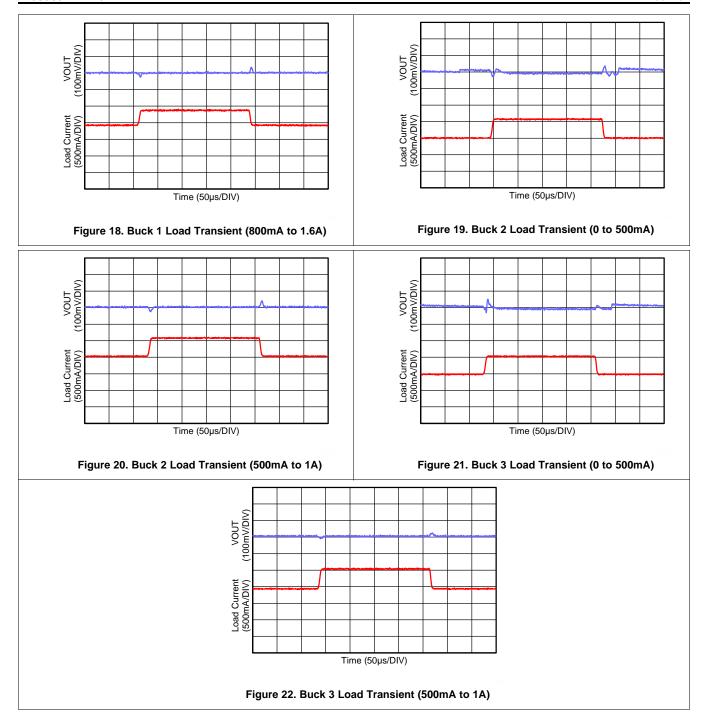

# 7.10 Typical Characteristics

ZHCSCG8 - MAY 2014 www.ti.com.cn

# TEXAS INSTRUMENTS

# 8 Detailed Description

#### 8.1 Overview

LM10507 is a highly efficient and integrated Power Management Unit for Systems-on-a-Chip (SoCs), ASICs, and processors. It operates cooperatively and communicates with processors over an SPI interface with output Voltage programmability and Standby Mode. The device incorporates three high-efficiency synchronous buck regulators and one LDO that deliver four output voltages from a single power source. The device also includes a SPI-programmable Comparator Block that provides an interrupt output signal

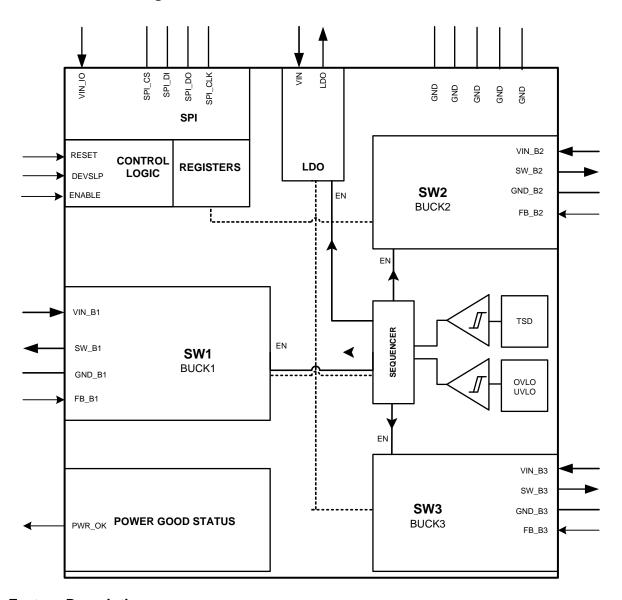

## 8.2 Functional Block Diagram

### 8.3 Feature Description

## 8.3.1 Buck Regulators Operation

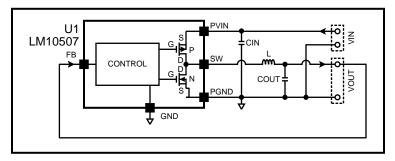

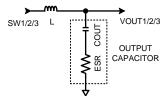

A buck converter contains a control block, a switching PFET connected between input and output, a synchronous rectifying NFET connected between the output and ground and a feedback path. The following figure shows the block diagram of each of the three buck regulators integrated in the device.

## **Feature Description (continued)**

Figure 6. Buck Functional Diagram

During the first portion of each switching cycle, the control block turns on the internal PFET switch. This allows current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of  $(V_{IN} - V_{OUT})/L$  by storing energy in a magnetic field. During the second portion of each cycle, the control block turns the PFET switch off, blocking current flow from the input, and then turns the NFET synchronous rectifier on. The inductor draws current from ground through the NFET to the output filter capacitor and load, which ramps the inductor current down with a slope of  $(-V_{OUT})/L$ .

The output filter stores charge when the inductor current is high, and releases it when low, smoothing the voltage across the load. The output voltage is regulated by modulating the PFET switch on time to control the average current sent to the load. The effect is identical to sending a duty-cycle modulated rectangular wave formed by the switch and synchronous rectifier at the SW pinto a low-pass filter formed by the inductor and output filter capacitor. The output voltage is equal to the average voltage at the SW terminal.

#### 8.3.2 Buck Regulators Description

The LM10507 incorporates three high-efficiency synchronous switching buck regulators that deliver various voltages from a single DC input voltage. They include many advanced features to achieve excellent voltage regulation, high efficiency and fast transient response time. The bucks feature voltage mode architecture with synchronous rectification.

Each of the switching regulators is specially designed for high-efficiency operation throughout the load range. With a 2MHz typical switching frequency, the external L- C filter can be small and still provide very low output voltage ripple. The bucks are internally compensated to be stable with the recommended external inductors and capacitors as detailed in the application diagram. Synchronous rectification yields high efficiency for low voltage and high output currents.

All bucks can operate up to a 100% duty cycle allowing for the lowest possible input voltage that still maintains the regulation of the output. The lowest input to output dropout voltage is achieved by keeping the PMOS switch on.

Additional features include soft-start, undervoltage lockout, bypass, and current and thermal overload protection. To reduce the input current ripple, the device employs a control circuit that operates the 3 bucks at 120° phase. These bucks are nearly identical in performance and mode of operation. They can operate in FPWM (forced PWM) or automatic mode (PWM/PFM).

#### 8.4 Device Functional Modes

#### 8.4.1 PWM Operation

During PWM operation the converter operates as a voltage-mode controller with input voltage feed forward. This allows the converter to achieve excellent load and line regulation. The DC gain of the power stage is proportional to the input voltage. To eliminate this dependence, a feed forward voltage inversely proportional to the input voltage is introduced.

In Forced PWM Mode the bucks always operate in PWM mode regardless of the output current.

# TEXAS INSTRUMENTS

#### **Device Functional Modes (continued)**

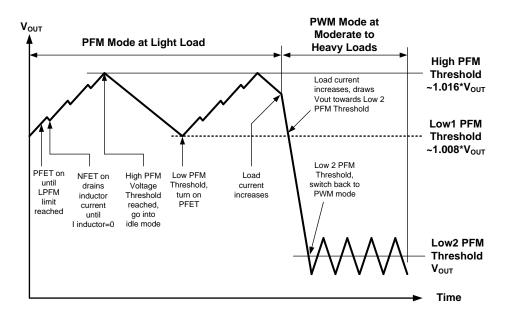

In **Automatic Mode**, if the output current is less than 70 mA (typ.), the bucks automatically transition into PFM (Pulse Frequency Modulation) operation to reduce the current consumption. At higher than 70 mA (typ.) they operate in PWM mode. This increases the efficiency at lower output currents.

Figure 7. PFM vs PWM Operation

### 8.4.2 PFM Operation (Bucks 1, 2 & 3)

At very light loads, Bucks 1, 2, and Buck 3 enter PFM mode and operate with reduced switching frequency and supply current to maintain high efficiency.

Bucks 1, 2 and 3 will automatically transition into PFM mode when either of two conditions occurs for a duration of 32 or more clock cycles:

- 1. The inductor current becomes discontinuous, or

- 2. The peak PMOS switch current drops below the I<sub>MODE</sub> level.

During PFM operation, the converter positions the output voltage slightly higher than the nominal output voltage during PWM operation, allowing additional headroom for voltage drop during a load transient from light to heavy load. The PFM comparators sense the output voltage via the feedback pinand control the switching of the output FETs such that the output voltage ramps between 0.8% and 1.6% (typical) above the nominal PWM output voltage. If the output voltage is below the 'high' PFM comparator threshold, the PMOS power switch is turned on. It remains on until the output voltage exceeds the 'high' PFM threshold or the peak current exceeds the I<sub>PFM</sub> level set for PFM mode.

Once the PMOS power switch is turned off, the NMOS power switch is turned on until the inductor current ramps to zero. When the NMOS zero-current condition is detected, the NMOS power switch is turned off. If the output voltage is below the 'high' PFM comparator threshold (see Figure 7), the PMOS switch is again turned on and the cycle is repeated until the output reaches the desired level. Once the output reaches the 'high' PFM threshold, the NMOS switch is turned on briefly to ramp the inductor current to zero and then both output switches are turned off and the part enters an extremely low power mode. Quiescent supply current during this 'idle' mode is less than 100  $\mu$ A, which allows the part to achieve high efficiencies under extremely light load conditions. When the output drops below the 'low' PFM threshold, the cycle repeats to restore the output voltage to ~1.6% above the nominal PWM output voltage.

If the load current should increase during PFM mode causing the output voltage to fall below the 'low2' PFM threshold, the part will automatically transition into fixed-frequency PWM mode.

# **Device Functional Modes (continued)**

#### 8.4.3 Soft Start

Each of the buck converters has an internal soft-start circuit that limits the in-rush current during startup. This allows the converters to gradually reach the steady-state operating point, thus reducing startup stresses and surges. During startup, the switch current limit is increased in steps.

For **Bucks 1, 2 and 3** the soft start is implemented by increasing the switch current limit in steps that are gradually set higher. The startup time depends on the output capacitor size, load current and output voltage. Typical startup time with the recommended output capacitor of 10  $\mu$ F is 0.1-0.5ms. It is expected that in the final application the load current condition will be more likely in the lower load current range during the startup.

#### 8.4.4 Current Limiting

A current limit feature protects the device and any external components during overload conditions. In PWM mode the current limiting is implemented by using an internal comparator that trips at current levels according to the buck capability. If the output is shorted to ground the device enters a timed current limit mode where the NFET is turned on for a longer duration until the inductor current falls below a low threshold, ensuring inductor current has more time to decay, thereby preventing runaway.

#### 8.4.5 Internal Synchronous Rectification

While in PWM mode, the bucks use an internal NFET as a synchronous rectifier to reduce the rectifier forward voltage drop and the associated power loss. Synchronous rectification provides a significant improvement in efficiency whenever the output voltage is relatively low compared to the voltage drop across an ordinary rectifier diode.

### 8.4.6 Low Dropout Operation

The device can operate at 100% duty cycle (no switching; PMOS switch completely on) for low dropout support. In this way the output voltage will be controlled down to the lowest possible input voltage. When the device operates near 100% duty cycle, output voltage ripple is approximately 25 mV.

The minimum input voltage needed to support the output voltage:

$V_{IN\_MIN} = V_{OUT} + I_{LOAD}^* (R_{DSON\_PFET} + R_{IND})$

where

I<sub>LOAD</sub>: Load Current

R<sub>DSON\_PFET</sub>: Drain to source resistance of PFET (high side)

• R<sub>IND</sub>: Inductor resistance (1)

#### 8.4.7 Device Operating Modes

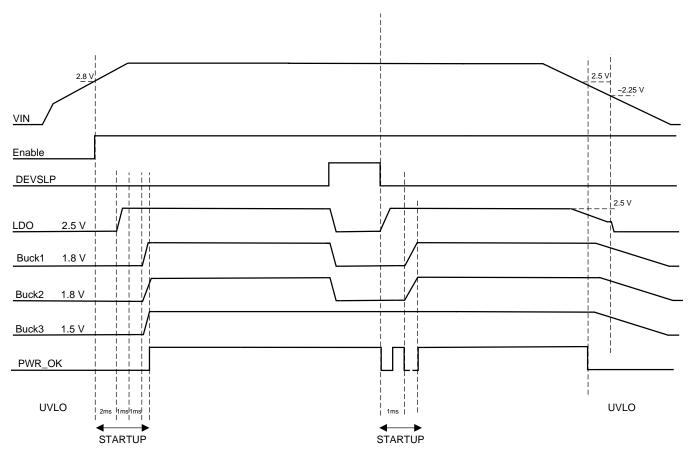

### 8.4.7.1 Startup Sequence

Once VVIN reaches the UVLO threshold and the ENABLE pin= High the LM10507 will start up. There is a fixed delay of approx. 1 ms before the LDO starts up, followed by Buck1 at 1ms. After a delay of 1msec from Buck1, Buck2 and Buck3 regulators start together. There is a maximum of 500us soft-start with full load for the Bucks

#### The Startup Sequence will be:

- 1. 2.5ms delay after ENABLE.

- 2. LDO -> 2.5 V,

- 3. 2ms delay.

- 4. Buck1 -> 1.8 V, Buck2 -> 1.8 V, Buck3 -> 1.5 V

- 5. PWR OK goes high

# TEXAS INSTRUMENTS

## **Device Functional Modes (continued)**

Figure 8. Normal Operating Mode

#### 8.4.7.2 Power-On Default and Device Enable

The device will be enabled over the ENABLE terminal, unless outside of operating voltage range. Once  $V_{VIN}$  reaches a minimum required input Voltage and ENABLE=High the power-up sequence will be started. Once the device is started, the output voltage of the Bucks can be individually disabled by accessing their corresponding BK1EN, BK2EN register bits (BUCK CONTROL).

#### 8.4.7.3 RESET: Pin Function

The RESET pinis internally pulled up. If the RESET pinis set low, the device will perform a complete reset of all the registers to their default states. This means that all of the voltage settings on the regulators will go back to their default state and all Regulators will be turned ON. All Registers will be set back to default instantaneously but no Start-Up Sequence initiated like it would be with ENABLE terminal.

## 8.4.7.4 DEVSLP (Device Sleep) Function

The Device can be programmed into Standby mode. There are 2 ways for doing that:

- 1. DEVSLP terminal

- Programming via SPI

# **Device Functional Modes (continued)**

### 8.4.7.5 DEVSLP Terminal

When the DEVSLP pinis asserted high, the LM10507 will enter Device Sleep Mode. While in Device Sleep Mode, all Regulator outputs are turned OFF except Buck3. Note: Bucks1,2 and LDO will turn off when the DEVSLP signal is given. All disabled output Rails will turn off immediately and at the same time (no sequencing). An internal 22 k $\Omega$  (typ.) pull down resistor is attached to the FB pinof Buck 1 and Buck2. Buck 1 and 2 outputs are pulled to ground level when they are disabled to discharge any residual charge present in the output circuitry. When Device Sleep transitions to a low, Buck 1, Buck2 and LDO are enabled. Buck 3 will go back to its previous state

#### 8.4.7.6 Device Sleep (DEVSLP) Programming via SPI

There is no bit which has the same function as DEVSLP terminal. Disabling or programming the Bucks to new level is the user's decision based on power consumption and other requirements

The following section describes how to program the chip into Device Sleep Mode corresponding to DEVSLP pinfunction: Buck 3 must be PFM. To program the LM10507 to Device Sleep Mode via SPI, Buck 1 and Buck2 must be disabled by host device (Register 0x0A bit 0). The LDO must be disabled (Register 0x0B bit 1 and 0). Then stop the oscillator (Register 0x0E bit 1) To wake LM10507 from Device Sleep Mode, reverse this sequence.

#### 8.4.7.7 ENABLE, Function

The ENABLE pinis a digital function to control the Start-Up of PMIC. ENABLE has an internal pull-down and is active High. A pull-down resistor is connected to GND. Transitions of the ENABLE pinto Low during device operation will disable all regulators and actively force down all the output voltages. Register defaults are restored while ENABLE is low.

### 8.4.7.8 Under Voltage Lock Out (UVLO)

The VIN voltage is monitored for a supply under voltage condition, for which the operation of the device cannot be guaranteed. The part will automatically disable PMIC. To prevent unstable operation, the UVLO has a hysteresis window of about 300mV. An under voltage lockout (UVLO) will disable all buck outputs, all internal registers are reset. Once the supply voltage is above the UVLO hysteresis, the device will initiate a power-up sequence and then enter the active state.

The LDO will remain functional past the UVLO threshold until V<sub>VIN</sub> reaches approximately 2.25V.

#### 8.4.7.9 Over Voltage Lock Out (OVLO)

The VIN voltage is monitored for a supply over voltage condition, for which the operation of the device cannot be guaranteed. The purpose of OVLO is to protect the part and all other components connected to the PMU outputs from any damage and malfunction. Once  $V_{\text{VIN}}$  rises over about 5.8V all the Bucks and LDO will be disabled automatically. To prevent unstable operation, the OVLO has a hysteresis window of about 100mV. An over voltage lockout (OVLO) will force the device into the reset state, all internal registers are reset. Once the supply voltage goes below the OVLO lower threshold, the device will initiate a power-up sequence and then enter the active state. Operating maximum input voltage at which parameters are guaranteed is 5.5 V. Absolute maximum of the device is 6.0 V.

#### 8.4.7.10 PWR OK - Pin Function

The LM10507 has PWR\_OK pinto signal that all output rails are valid. PWR\_OK is Low if Buck3 is disabled in register0x0A. If PWR\_OK condition is detected, then the Hardware PWR\_OK pinwill be set immediately. There are four PWR\_OK generating conditions, all must be fulfilled:

- Buck 3 output is over flag level (90% when rising,85% when falling).

- Buck 2 output is over flag level (90% when rising,85% when falling), but not applicable if disabled in register 0x0A.

- Buck 1 output is over flag level (90% when rising,85% when falling), but not applicable if disabled in register 0x0A

- LDO output is over flag level (90% when rising,85% when falling), but not applicable if disabled in register 0x0B.

## **Device Functional Modes (continued)**

#### NOTE

SPI commanded Disable of any output, followed by a subsequent SPI commanded ENABLE will cause a temporary logic LOW of the PWR\_OK pinuntil that Buck output voltage has risen back to the 90% flag level.

## 8.4.7.11 Thermal Shutdown (TSD)

The temperature of the silicon die is monitored for an over-temperature condition, for which the operation of the device cannot be guaranteed. The part will automatically be disabled if the temperature is too high. The thermal shutdown (TSD) will force the device into the reset state. In reset, all circuitry is disabled. To prevent unstable operation, the TSD has a hysteresis window of about 20°C. Once the temperature has decreased below the TSD hysteresis, the device will initiate a power-up sequence and then enter the active state. In the active state, the part will start up as if for the first time, all registers will be in their default state.

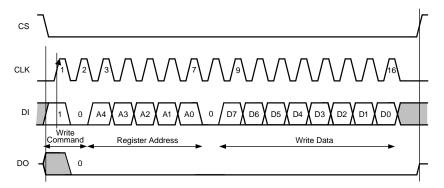

### 8.5 Programming

#### 8.5.1 SPI Data Interface

The device is programmable via 4-wire SPI Interface. The signals associated with this interface are CS, DI, DO and CLK. Through this interface, the user can enable/disable the device, program the output voltages of the individual bucks and of course read the status of Flag registers.

By accessing the registers in the device through this interface, the user can get access and control the operation of the buck controllers and program the reference voltage of the comparator in the device.

Figure 9. SPI Interface Write

- Data In (DI)

- 1 to 0 Write Command

- A<sub>4</sub>to A<sub>0</sub> Register address to be written

- D<sub>7</sub> to D<sub>0</sub> Data to be written

- Data Out (DO)

- All Os

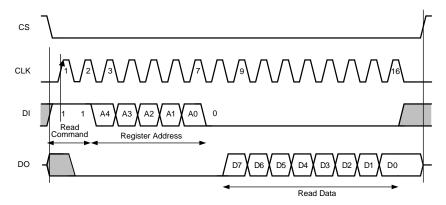

# **Programming (continued)**

Figure 10. SPI Interface Read

- Data In (DI)

- 1 to 1 Read Command

- A<sub>4</sub>to A<sub>0</sub> Register address to be read

- Data Out (DO)

- D<sub>7</sub> to D<sub>0</sub> Data Read

# 8.6 Register Maps

# 8.6.1 Registers Configurable Via The SPI Interface

| Addr | Reg Name           | Bit | R/W | Default | Description            | Notes              |

|------|--------------------|-----|-----|---------|------------------------|--------------------|

|      |                    | 7   | _   | _       |                        | Reset default:     |

|      |                    |     |     |         |                        | 0x7F (1.5 V)       |

|      |                    | 6   | R/W | 1       | Buck 3 Voltage Code[6] |                    |

|      |                    | 5   | R/W | 1       | Buck 3 Voltage Code[5] |                    |

| 0x00 | x00 Buck 3 Voltage | 4   | R/W | 1       | Buck 3 Voltage Code[4] |                    |

|      |                    | 3   | R/W | 1       | Buck 3 Voltage Code[3] | Range: 0.865-1.5 V |

|      |                    | 2   | R/W | 1       | Buck 3 Voltage Code[2] |                    |

|      |                    | 1   | R/W | 1       | Buck 3 Voltage Code[1] |                    |

|      |                    | 0   | R/W | 1       | Buck 3 Voltage Code[0] |                    |

|      |                    | 7   | _   | _       | _                      | Reset default:     |

|      | 0.07               | 6   | _   | _       |                        | 0x12 (1.8 V)       |

|      |                    | 5   | R/W | 0       | Buck 1 Voltage Code[5] |                    |

| 0x07 |                    | 4   | R/W | 1       | Buck 1 Voltage Code[4] | Range: 0.9-3.4     |

| UXU7 | Buck 1 Voltage     | 3   | R/W | 0       | Buck 1 Voltage Code[3] |                    |

|      |                    | 2   | R/W | 0       | Buck 1 Voltage Code[2] |                    |

|      |                    | 1   | R/W | 1       | Buck 1 Voltage Code[1] |                    |

|      |                    | 0   | R/W | 0       | Buck 1 Voltage Code[0] |                    |

|      |                    | 7   | _   | _       | _                      | Reset default:     |

|      |                    | 6   | _   | _       | _                      | 0x12 (1.8 V)       |

|      |                    | 5   | R/W | 0       | Buck 2 Voltage Code[5] |                    |

| 0x08 | Duralis O Maltagra | 4   | R/W | 1       | Buck 2 Voltage Code[4] | Range: 0.9-3.4     |

| UXUO | Buck 2 Voltage     | 3   | R/W | 0       | Buck 2 Voltage Code[3] |                    |

|      |                    | 2   | R/W | 0       | Buck 2 Voltage Code[2] |                    |

|      |                    | 1   | R/W | 1       | Buck 2 Voltage Code[1] |                    |

|      |                    | 0   | R/W | 0       | Buck 2 Voltage Code[0] |                    |

# TEXAS INSTRUMENTS

# **Register Maps (continued)**

| Addr | Reg Name                          | Bit | R/W | Default | Description            | Notes                                |

|------|-----------------------------------|-----|-----|---------|------------------------|--------------------------------------|

|      |                                   | 7   | R/W | _       | _                      | Reset default:                       |

|      | DevSLP Mode<br>Voltage for Buck 3 | 6   | R/W | 1       | Buck 3 Voltage Code[6] | 0x7F (1.5 V)                         |

|      |                                   | 5   | R/W | 1       | Buck 3 Voltage Code[5] |                                      |

| 000  |                                   | 4   | R/W | 1       | Buck 3 Voltage Code[4] |                                      |

| 0X09 |                                   | 3   | R/W | 1       | Buck 3 Voltage Code[3] |                                      |

|      |                                   | 2   | R/W | 1       | Buck 3 Voltage Code[2] |                                      |

|      |                                   | 1   | R/W | 1       | Buck 3 Voltage Code[1] |                                      |

|      |                                   | 0   | R/W | 1       | Buck 3 Voltage Code[0] |                                      |

|      |                                   | 7   | R/W | 1       | BK3EN                  | Enable/Disable Buck 3                |

|      |                                   | 6   | _   | _       | _                      |                                      |

|      |                                   | 5   | _   | _       | _                      |                                      |

| 004  | Decel Control                     | 4   | R/W | _       | BK1FPWM                | Buck 1 forced PWM mode when high     |

| 0x0A | Buck Control                      | 3   | R/W | 0       | BK2FPWM                | Buck 2 forced PWM mode when high     |

|      |                                   | 2   | R/W | 0       | BK3FPWM                | Buck 3 forced PWM mode when high     |

|      |                                   | 1   | R/W | 1       | BK1EN                  | Enables Buck 1 0-disabled, 1-enabled |

|      |                                   | 0   | R/W | 1       | BK2EN                  | Enables Buck 2 0-disabled, 1-enabled |

|      |                                   | 7   | _   | _       | _                      |                                      |

|      |                                   | 6   | _   | _       | _                      |                                      |

|      |                                   | 5   | _   | _       | _                      |                                      |

| 000  | LDO Control                       | 4   | _   | _       | _                      |                                      |

| 0x0B | LDO Control                       | 3   | _   | _       | _                      |                                      |

|      |                                   | 2   | _   | _       | _                      |                                      |

|      |                                   | 1   | _   | _       | _                      |                                      |

|      |                                   | 0   | R/W | 1       | LDO Enable             |                                      |

|      |                                   | 7   | _   |         |                        |                                      |

|      |                                   | 6   | _   |         |                        |                                      |

|      |                                   | 5   | _   |         |                        |                                      |

| 0x0D | Status                            | 4   | R   |         | LDO OK                 | LDO is greater than 90% of target    |

| OXOD | Status                            | 3   | R   |         | Buck 3 OK              | Buck 3 is greater than 90% of target |

|      |                                   | 2   | R   |         | Buck 2 OK              | Buck 2 is greater than 90% of target |

|      |                                   | 1   | R   |         | Buck 1 OK              | Buck 1 is greater than 90% of target |

|      |                                   | 0   | R   |         | PWR_OK                 | PWR_OK output is high                |

|      |                                   | 7   |     |         |                        |                                      |

|      |                                   | 6   |     |         |                        |                                      |

|      |                                   | 5   | _   |         |                        |                                      |

| 0x0E | MISC Control                      | 4   | _   |         |                        |                                      |

| OAUL | WINGO CONTROL                     | 3   |     |         |                        |                                      |

|      |                                   | 2   | _   |         |                        |                                      |

|      |                                   | 1   | R/W | 0       | Oscillator Disable     | OSC ENABLE/DISABLE                   |

|      |                                   | 0   |     |         |                        |                                      |

# 8.6.1.1 ADDR 0x07 & 0x08: Buck 1 and Buck 2 Voltage Code and V<sub>OUT</sub> Level Mapping

| Voltage Code | Voltage | Voltage Code | Voltage |

|--------------|---------|--------------|---------|

| 0x00         | 0.9     | 0x20         | 2.5     |

| 0x01         | 0.95    | 0x21         | 2.55    |

| 0x02         | 1       | 0x22         | 2.6     |

| 0x03         | 1.05    | 0x23         | 2.65    |

| 0x04         | 1.1     | 0x24         | 2.7     |

| 0x05         | 1.15    | 0x25         | 2.75    |

| 0x06         | 1.2     | 0x26         | 2.8     |

| 0x07         | 1.25    | 0x27         | 2.85    |

| 0x08         | 1.3     | 0x28         | 2.9     |

| 0x09         | 1.35    | 0x29         | 2.95    |

| 0x0A         | 1.4     | 0x2A         | 3       |

| 0x0B         | 1.45    | 0x2B         | 3.05    |

| 0x0C         | 1.5     | 0x2C         | 3.1     |

| 0x0D         | 1.55    | 0x2D         | 3.15    |

| 0x0E         | 1.6     | 0x2E         | 3.2     |

| 0x0F         | 1.65    | 0x2F         | 3.25    |

| 0x10         | 1.7     | 0x30         | 3.3     |

| 0x11         | 1.75    | 0x31         | 3.35    |

| 0x12         | 1.8     | 0x32         | 3.4     |

| 0x13         | 1.85    | 0x33         | 3.4     |

| 0x14         | 1.9     | 0x34         | 3.4     |

| 0x15         | 1.95    | 0x35         | 3.4     |

| 0x16         | 2       | 0x36         | 3.4     |

| 0x17         | 2.05    | 0x37         | 3.4     |

| 0x18         | 2.1     | 0x38         | 3.4     |

| 0x19         | 2.15    | 0x39         | 3.4     |

| 0x1A         | 2.2     | 0x3A         | 3.4     |

| 0x1B         | 2.25    | 0x3B         | 3.4     |

| 0x1C         | 2.3     | 0x3C         | 3.4     |

| 0x1D         | 2.35    | 0x3D         | 3.4     |

| 0x1E         | 2.4     | 0x3E         | 3.4     |

| 0x1F         | 2.45    | 0x3F         | 3.4     |

# TEXAS INSTRUMENTS

# 8.6.1.2 ADDR 0x00 Buck 3 Voltage Code and V<sub>OUT</sub> Level Mapping

| Voltage Code | Voltage |

|--------------|---------|--------------|---------|--------------|---------|--------------|---------|

| 0x00         | 0.865   | 0x20         | 1.025   | 0x40         | 1.185   | 0x60         | 1.345   |

| 0x01         | 0.87    | 0x21         | 1.03    | 0x41         | 1.19    | 0x61         | 1.35    |

| 0x02         | 0.875   | 0x22         | 1.035   | 0x42         | 1.195   | 0x62         | 1.355   |

| 0x03         | 0.88    | 0x23         | 1.04    | 0x43         | 1.2     | 0x63         | 1.36    |

| 0x04         | 0.885   | 0x24         | 1.045   | 0x44         | 1.205   | 0x64         | 1.365   |

| 0x05         | 0.89    | 0x25         | 1.05    | 0x45         | 1.21    | 0x65         | 1.37    |

| 0x06         | 0.895   | 0x26         | 1.055   | 0x46         | 1.215   | 0x66         | 1.375   |

| 0x07         | 0.9     | 0x27         | 1.06    | 0x47         | 1.22    | 0x67         | 1.38    |

| 0x08         | 0.905   | 0x28         | 1.065   | 0x48         | 1.225   | 0x68         | 1.385   |