SLES101A - DECEMBER 2003 - REVISED NOVEMBER 2006

# 24-BIT, 192-kHz SAMPLING, ADVANCED SEGMENT, AUDIO STEREO DIGITAL-TO-ANALOG CONVERTER

## **FEATURES**

- Supports Both DSD and PCM Formats

- 24-Bit Resolution

- Analog Performance:

- Dynamic Range: 123 dB

- THD+N: 0.0005%

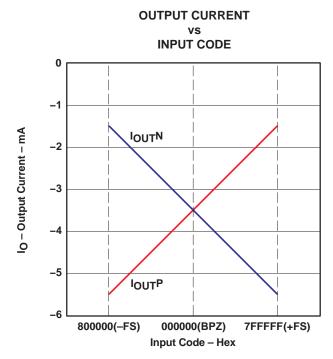

- Differential Current Output: 4 mA p-p

- 8× Oversampling Digital Filter:

- Stop-Band Attenuation: -98 dB

- Pass-Band Ripple: ±0.0002 dB

- Sampling Frequency: 10 kHz to 200 kHz

- System Clock: 128, 192, 256, 384, 512, or 768 fs With Autodetect

- Accepts 16-, 20-, and 24-Bit Audio Data

- PCM Data Formats: Standard, I<sup>2</sup>S, and Left-Justified

- DSD Format Interface Available

- Interface Available for Optional External Digital Filter or DSP

- TDMCA Interface Available

- User-Programmable Mode Controls:

- Digital Attenuation: 0 dB to -120 dB, 0.5 dB/Step

- Digital De-Emphasis

- Digital Filter Rolloff: Sharp or Slow

- Soft Mute

- Compatible With DSD1792 (Pins and Mode Controls)

- Dual Supply Operation:

- 5-V Analog, 3.3-V Digital

- 5-V Tolerant Digital Inputs

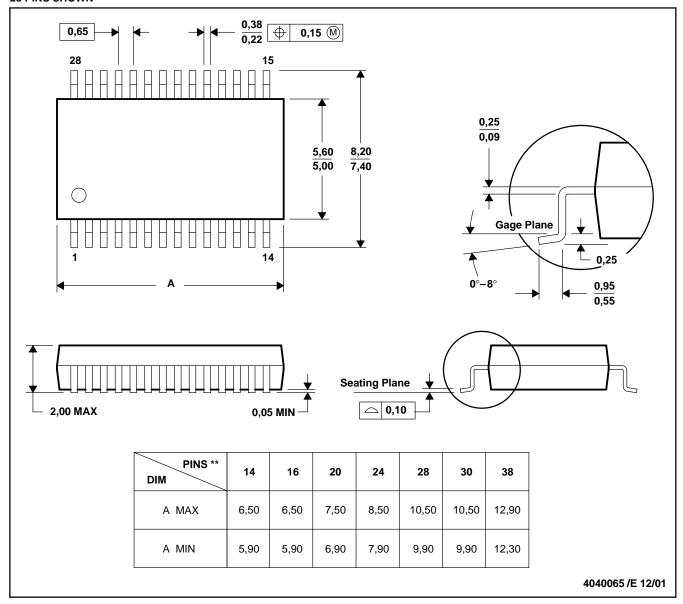

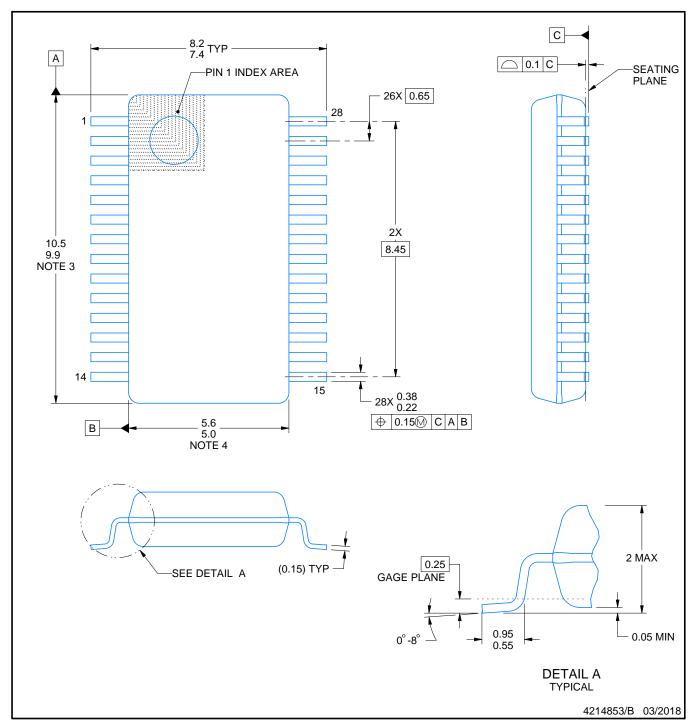

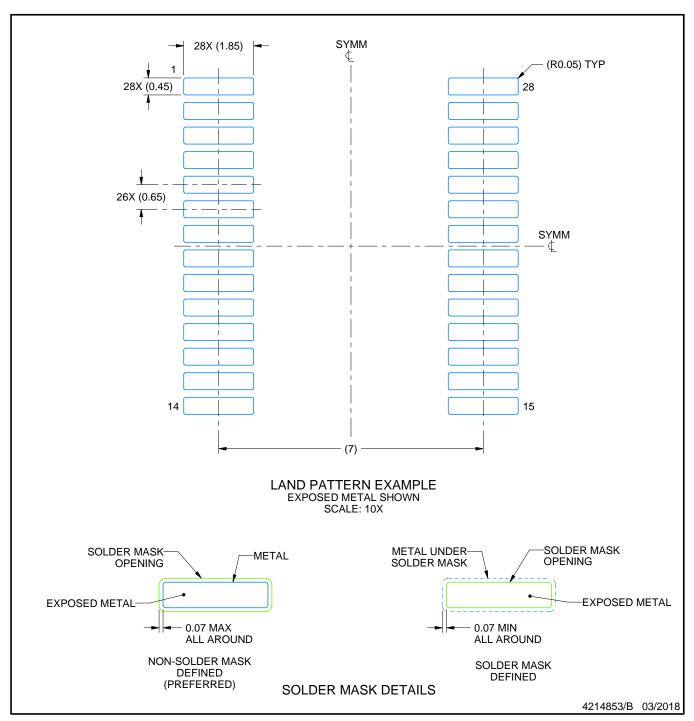

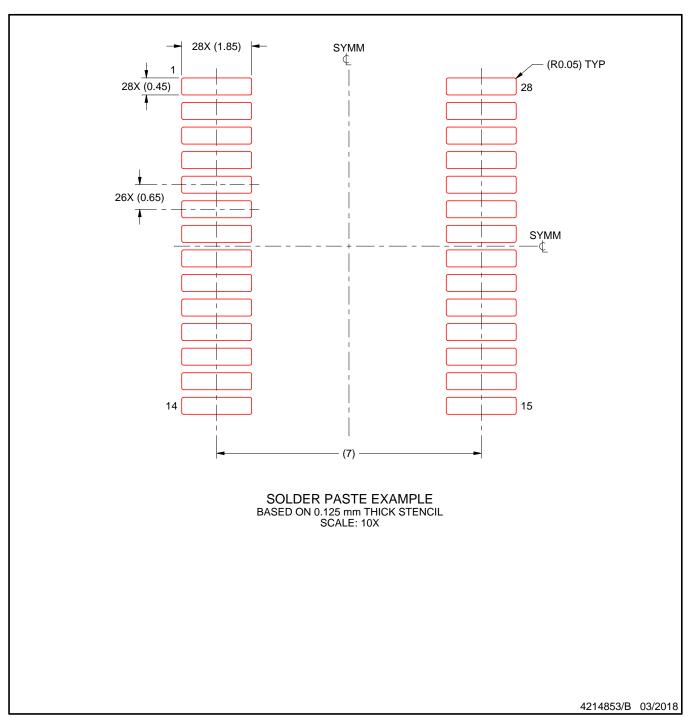

- Small 28-Lead SSOP Package

## **APPLICATIONS**

- A/V Receivers

- SACD Players

- DVD Players

- HDTV Receivers

- Car Audio Systems

- Digital Multi-Track Recorders

- Other Applications Requiring 24-Bit Audio

#### DESCRIPTION

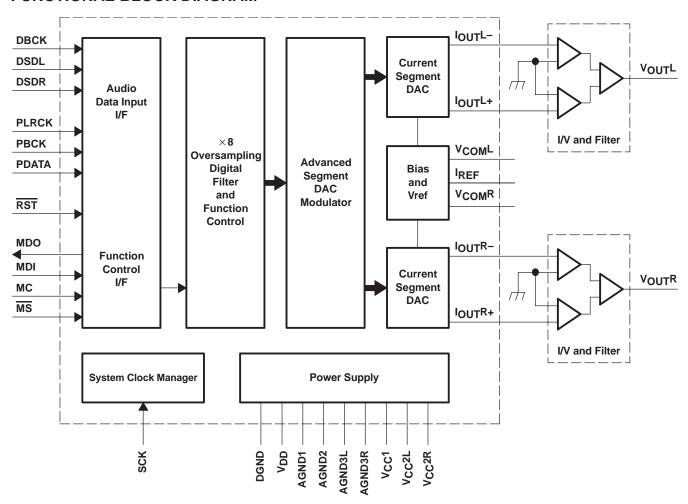

The DSD1796 is a monolithic CMOS integrated circuit that includes stereo digital-to-analog converters and support circuitry in a small 28-lead SSOP package. The data converters use TI's advanced-segment DAC architecture to achieve excellent dynamic performance and improved tolerance to clock jitter. The DSD1796 provides balanced current outputs, allowing the user to optimize analog performance externally. The DSD1796 accepts the PCM and DSD audio data formats, providing easy interfacing to audio DSP and decoder chips. The DSD1796 also interfaces with external digital filter devices (DF1704, DF1706, PMD200). Sampling rates up to 200 kHz are supported. A full set of user-programmable functions is accessible through an SPI serial control port, which supports register write and readback functions. The DSD1796 also supports the time-division-multiplexed command and audio (TDMCA) data format.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **ORDERING INFORMATION**

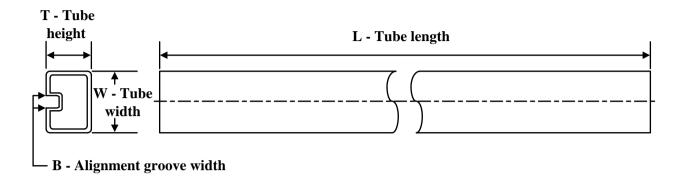

| PRODUCT   | PACKAGE      | PACKAGE CODE | OPERATION<br>TEMPERATURE RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA |

|-----------|--------------|--------------|--------------------------------|--------------------|--------------------|--------------------|

| D0D4700DD | 00 l 1 00 OD | 0000         | 0500 1- 0500                   | D0D4700            | DSD1796DB          | Tube               |

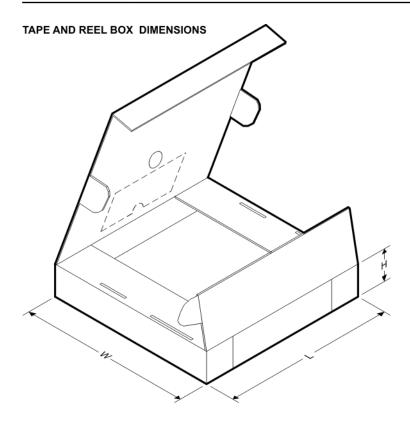

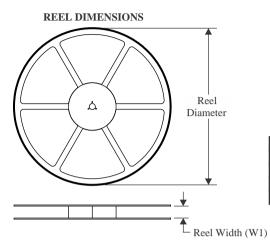

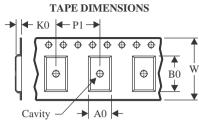

| DSD1796DB | 28-lead SSOP | 28DB         | −25°C to 85°C                  | DSD1796            | DSD1796DBR         | Tape and reel      |

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                                                                                                                     |                                                                      | DSD1796                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Cumply voltage                                                                                                                      | V <sub>CC</sub> 1, V <sub>CC</sub> 2L, V <sub>CC</sub> 2R            | -0.3 V to 6.5 V                                                             |

| Supply voltage  VDD  Supply voltage differences: VCC1, VCC2L, VCC2R  Ground voltage differences: AGND1, AGND2, AGND3L, AGND3R, DGND | V <sub>DD</sub>                                                      | -0.3 V to 4 V                                                               |

| Supply voltage differe                                                                                                              | nces: V <sub>CC</sub> 1, V <sub>CC</sub> 2L, V <sub>CC</sub> 2R      | ±0.1 V                                                                      |

| Ground voltage differen                                                                                                             | ences: AGND1, AGND2, AGND3L, AGND3R, DGND                            | ±0.1 V                                                                      |

| Digital input valence                                                                                                               | PLRCK, PDATA, PBCK, SCK, RST, MS(2), MDI, MC, DSDL(2), DSDR(2), DBCK | -0.3 V to 6.5 V                                                             |

| Digital input voltage                                                                                                               | DSDL(3), DSDR(3), MS(3), MDO                                         | -0.3 V to (V <sub>DD</sub> + 0.3 V) < 4 V                                   |

| Analog input voltage                                                                                                                |                                                                      | $-0.3 \text{ V to } (\text{V}_{\text{CC}} + 0.3 \text{ V}) < 6.5 \text{ V}$ |

| Input current (any pins                                                                                                             | s except supplies)                                                   | ±10 mA                                                                      |

| Ambient temperature                                                                                                                 | under bias                                                           | -40°C to 125°C                                                              |

| Storage temperature                                                                                                                 |                                                                      | −55°C to 150°C                                                              |

| Junction temperature                                                                                                                |                                                                      | 150°C                                                                       |

| Lead temperature (sol                                                                                                               | dering)                                                              | 260°C, 5 s                                                                  |

| Package temperature                                                                                                                 | (IR reflow, peak)                                                    | 260°C                                                                       |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

all specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2L = V_{CC}2R = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 44.1$  kHz, system clock = 256  $f_S$ , and 24-bit data unless otherwise noted

| DADAMETED |                             | TEGT CONDITIONS |                                            |               |                        |      |

|-----------|-----------------------------|-----------------|--------------------------------------------|---------------|------------------------|------|

|           | PARAMETER                   | TEST CONDITIONS | MIN TYP MAX                                |               | UNIT                   |      |

| RESC      | OLUTION                     |                 |                                            | 24            |                        | Bits |

| DATA      | A FORMAT (PCM Mode)         |                 |                                            |               |                        |      |

|           | Audio data interface format |                 | Standard, I <sup>2</sup> S, left-justified |               |                        |      |

|           | Audio data bit length       |                 | 16-, 20-, 24-bit selectable                |               |                        |      |

|           | Audio data format           |                 | MSB first, 2s complement                   |               |                        |      |

| fS        | Sampling frequency          |                 | 10                                         |               | 200                    | kHz  |

|           | System clock frequency      |                 | 128, 192,                                  | 256, 384, 5   | 12, 768 f <sub>S</sub> |      |

| DATA      | A FORMAT (DSD Mode)         |                 |                                            |               |                        |      |

|           | Audio data interface format |                 | DSD (d                                     | direct stream | digital)               |      |

|           | Audio data bit length       |                 | 1 bit                                      |               |                        |      |

| fs        | Sampling frequency          |                 | 2.8224                                     |               |                        | MHz  |

|           | System clock frequency      |                 | 2.8224                                     |               | 11.2896                | MHz  |

<sup>(2)</sup> Input mode

<sup>(3)</sup> Output mode

## **ELECTRICAL CHARACTERISTICS (Continued)**

all specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2L = V_{CC}2R = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 44.1$  kHz, system clock = 256  $f_S$ , and 24-bit data unless otherwise noted

| -                | DADAMETER                              | TEGT COMPTIONS                              | 1   | OSD1796DE   | 3      |      |

|------------------|----------------------------------------|---------------------------------------------|-----|-------------|--------|------|

|                  | PARAMETER                              | TEST CONDITIONS                             | MIN | TYP         | MAX    | UNIT |

| DIGIT            | AL INPUT/OUTPUT                        | •                                           | •   |             |        |      |

|                  | Logic family                           |                                             | Т   | ΓL compatib | le     |      |

| VIH              | Input logic level                      |                                             | 2   |             |        | VDC  |

| VIL              | Triput logic level                     |                                             |     |             | 0.8    | VDC  |

| lн               | lament la sia commant                  | $V_{IN} = V_{DD}$                           |     |             | 10     | ^    |

| lıL              | Input logic current                    | V <sub>IN</sub> = 0 V                       |     |             | -10    | μΑ   |

| Vон              | Output logic lovel                     | I <sub>OH</sub> = -2 mA                     | 2.4 |             |        | VDC  |

| VOL              | Output logic level                     | $I_{OL} = 2 \text{ mA}$                     |     |             | 0.4    | VDC  |

| I <sub>OHZ</sub> | High-impedance output logic current(1) | V <sub>OUT</sub> = V <sub>DD</sub>          |     |             | 10     |      |

| lolz             | High-impedance output logic current(1) | VOUT = 0 V                                  |     |             | -10    | μΑ   |

| DYNA             | MIC PERFORMANCE (PCM MODE) (2)(3)      |                                             |     |             |        |      |

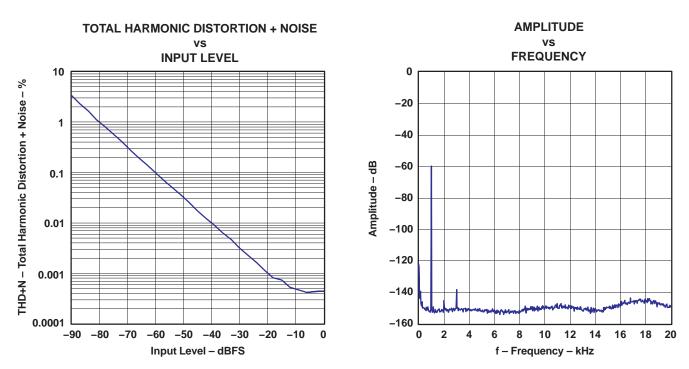

|                  |                                        | f <sub>S</sub> = 44.1 kHz                   |     | 0.0005%     | 0.001% |      |

|                  | THD+N at VOUT = 0 dB                   | f <sub>S</sub> = 96 kHz                     |     | 0.001%      |        |      |

|                  |                                        | f <sub>S</sub> = 192 kHz                    |     | 0.0015%     |        |      |

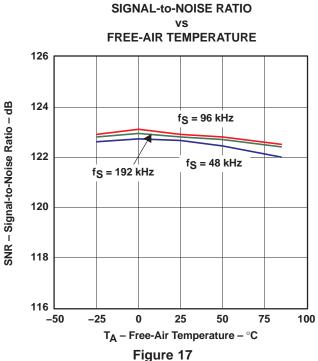

|                  |                                        | EIAJ, A-weighted, f <sub>S</sub> = 44.1 kHz | 120 | 123         |        |      |

|                  | Dynamic range                          | EIAJ, A-weighted, f <sub>S</sub> = 96 kHz   |     | 123         |        | dB   |

|                  |                                        | EIAJ, A-weighted, f <sub>S</sub> = 192 kHz  |     | 123         |        |      |

|                  |                                        | EIAJ, A-weighted, f <sub>S</sub> = 44.1 kHz | 120 | 123         |        |      |

|                  | Signal-to-noise ratio                  | EIAJ, A-weighted, f <sub>S</sub> = 96 kHz   |     | 123         |        | dB   |

|                  |                                        | EIAJ, A-weighted, f <sub>S</sub> = 192 kHz  |     | 123         |        |      |

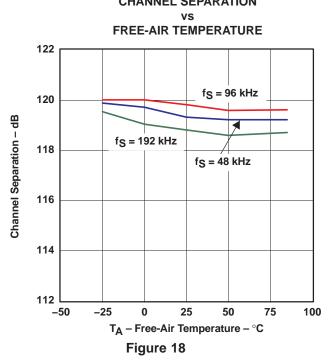

|                  |                                        | f <sub>S</sub> = 44.1 kHz                   | 116 | 119         |        |      |

|                  | Channel separation                     | f <sub>S</sub> = 96 kHz                     |     | 118         |        | dB   |

|                  |                                        | f <sub>S</sub> = 192 kHz                    |     | 117         |        |      |

|                  | Level linearity error                  | V <sub>OUT</sub> = −120 dB                  |     | ±1          |        | dB   |

| DYNA             | MIC PERFORMANCE (MONO MODE) (2)(3)     | )(4)                                        | •   |             | '      |      |

|                  |                                        | f <sub>S</sub> = 44.1 kHz                   |     | 0.0005%     |        |      |

|                  | THD+N at VOUT = 0 dB                   | f <sub>S</sub> = 96 kHz                     |     | 0.001%      |        |      |

|                  |                                        | f <sub>S</sub> = 192 kHz                    |     | 0.0015%     |        |      |

|                  |                                        | EIAJ, A-weighted, f <sub>S</sub> = 44.1 kHz |     | 126         |        |      |

|                  | Dynamic range                          | EIAJ, A-weighted, f <sub>S</sub> = 96 kHz   |     | 126         |        | dB   |

|                  | -                                      | EIAJ, A-weighted, f <sub>S</sub> = 192 kHz  |     | 126         |        |      |

|                  |                                        | EIAJ, A-weighted, f <sub>S</sub> = 44.1 kHz |     | 126         |        |      |

|                  | Signal-to-noise ratio                  | EIAJ, A-weighted, f <sub>S</sub> = 96 kHz   |     | 126         |        | dB   |

|                  | -                                      | EIAJ, A-weighted, f <sub>S</sub> = 192 kHz  |     | 126         |        |      |

<sup>(1)</sup> Pin 13 (MDO)

THD+N: 20-Hz HPF, 20-kHz AES17 LPF

Dynamic range: 20-Hz HPF, 20-kHz AES17 LPF, A-weighted Signal-to-noise ratio: 20-Hz HPF, 20-kHz AES17 LPF, A-weighted

Channel separation: 20-Hz HPF, 20-kHz AES17 LPF

Analog performance specifications are measured using the System Two™ Cascade audio measurement system by Audio Precision™ in the averaging mode.

<sup>(2)</sup> Filter condition:

<sup>(3)</sup> Dynamic performance and DC accuracy are specified at the output of the postamplifier as shown in Figure 32.

<sup>(4)</sup> Dynamic performance and DC accuracy are specified at the output of the measurement circuit as shown in Figure 34.

Other trademarks are the property of their respective owners.

otherwise noted

|                                       |                          | D                   | DSD1796DB         |                      |          |  |

|---------------------------------------|--------------------------|---------------------|-------------------|----------------------|----------|--|

| PARAMETER                             | TEST CONDITIONS          | MIN                 | TYP               | MAX                  | UNIT     |  |

| DSD MODE DYNAMIC PERFORMANCE (1) (2)  | (44.1 kHz, 64 fg)        |                     |                   |                      | •        |  |

| THD+N at FS                           | 2 V rms                  |                     | 0.0007%           |                      |          |  |

| Dynamic range                         | -60 dB, EIAJ, A-weighted |                     | 122               |                      | dB       |  |

| Signal-to-noise ratio                 | EIAJ, A-weighted         |                     | 122               |                      | dB       |  |

| ANALOG OUTPUT                         |                          |                     |                   |                      |          |  |

| Gain error                            |                          | -7                  | ±2                | 7                    | % of FSR |  |

| Gain mismatch, channel-to-channel     |                          | -3                  | ±0.5              | 3                    | % of FSR |  |

| Bipolar zero error                    | At BPZ                   | -2                  | ±0.5              | 2                    | % of FSR |  |

| Output current                        | Full scale (0 dB)        |                     | 4                 |                      | mA p-p   |  |

| Center current                        | At BPZ                   |                     | -3.5              |                      | mA       |  |

| DIGITAL FILTER PERFORMANCE            |                          |                     |                   |                      |          |  |

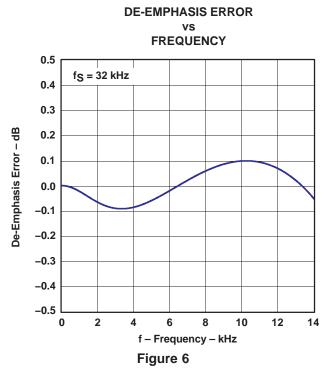

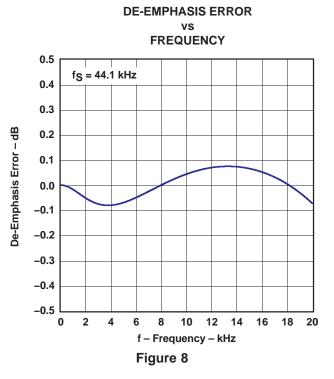

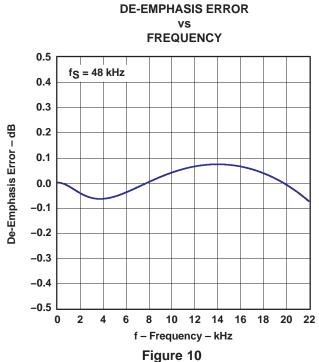

| De-emphasis error                     |                          |                     |                   | ±0.1                 | dB       |  |

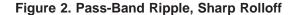

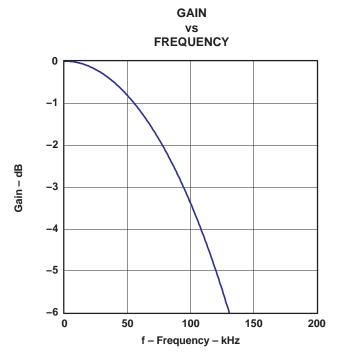

| FILTER CHARACTERISTICS-1: SHARP ROLLO | OFF                      |                     |                   |                      |          |  |

| Danahand                              | ±0.0002 dB               |                     |                   | 0.454 fg             |          |  |

| Pass band                             | -3 dB                    |                     |                   | 0.49 f <sub>S</sub>  |          |  |

| Stop band                             |                          | 0.546 fs            |                   |                      |          |  |

| Pass-band ripple                      |                          |                     |                   | ±0.0002              | dB       |  |

| Stop-band attenuation                 | Stop band = 0.546 fs     | -98                 |                   |                      | dB       |  |

| Delay time                            |                          |                     | 38/f <sub>S</sub> |                      | s        |  |

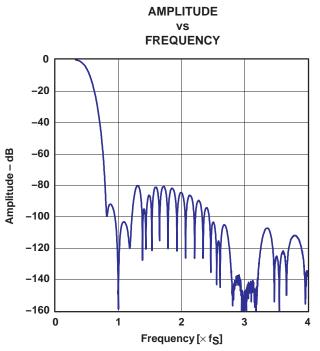

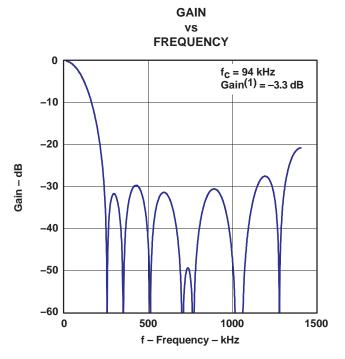

| FILTER CHARACTERISTICS-2: SLOW ROLLO  | FF                       |                     |                   |                      | •        |  |

| Danahand                              | ±0.001 dB                |                     |                   | 0.21 fg              |          |  |

| Pass band                             | -3 dB                    |                     |                   | 0.448 f <sub>S</sub> |          |  |

| Stop band                             |                          | 0.79 f <sub>S</sub> |                   |                      |          |  |

| Pass-band ripple                      |                          |                     |                   | ±0.001               | dB       |  |

| Stop-band attenuation                 | Stop band = 0.732 fs     | -80                 |                   |                      | dB       |  |

| Delay time                            |                          |                     | 38/f <sub>S</sub> |                      | S        |  |

<sup>(1)</sup> Filter condition:

THD+N: 20-Hz HPF, 20-kHz AES17 LPF

Dynamic range: 20-Hz HPF, 20-kHz AES17 LPF, A-weighted

Signal-to-noise ratio: 20-Hz HPF, 20-kHz AES17 LPF, A-weighted

Channel separation: 20-Hz HPF, 20-kHz AES17 LPF

Analog performance specifications are measured using the System Two Cascade audio measurement system by Audio Precision in the averaging

<sup>(2)</sup> Dynamic performance and DC accuracy are specified at the output of the postamplifier as shown in Figure 33.

## **ELECTRICAL CHARACTERISTICS (Continued)**

all specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2L = V_{CC}2R = 5 \text{ V}$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $f_S = 44.1 \text{ kHz}$ , system clock = 256  $f_S$ , and 24-bit data unless otherwise noted

|                    |                       | TEST COMPITIONS           | D                           | SD1796DB | 3    |      |  |

|--------------------|-----------------------|---------------------------|-----------------------------|----------|------|------|--|

|                    | PARAMETER             | TEST CONDITIONS           | EST CONDITIONS  MIN TYP MAX |          | UNIT |      |  |

| POWER              | R SUPPLY REQUIREMENTS |                           | _                           |          | _    |      |  |

| $V_{DD}$           |                       |                           | 3                           | 3.3      | 3.6  | VDC  |  |

| V <sub>CC</sub> 1  | Voltage vege          |                           |                             |          |      |      |  |

| V <sub>CC</sub> 2L | Voltage range         |                           | 4.75                        | 5        | 5.25 | VDC  |  |

| V <sub>CC</sub> 2R | <u> </u>              |                           |                             |          |      |      |  |

|                    |                       | f <sub>S</sub> = 44.1 kHz |                             | 7        | 9    |      |  |

| I <sub>DD</sub>    | (4)                   | f <sub>S</sub> = 96 kHz   |                             | 13       |      | mA   |  |

|                    |                       | f <sub>S</sub> = 192 kHz  |                             | 25       |      |      |  |

|                    | Supply current (1)    | f <sub>S</sub> = 44.1 kHz |                             | 18       | 23   |      |  |

| ICC                |                       | f <sub>S</sub> = 96 kHz   |                             | 19       |      | mA   |  |

|                    |                       | f <sub>S</sub> = 192 kHz  |                             | 20       |      |      |  |

|                    | •                     | f <sub>S</sub> = 44.1 kHz |                             | 115      | 150  |      |  |

|                    | Power dissipation (1) | f <sub>S</sub> = 96 kHz   |                             | 140      |      | mW   |  |

| •                  |                       | f <sub>S</sub> = 192 kHz  |                             | 180      |      |      |  |

| TEMPE              | RATURE RANGE          | •                         |                             |          |      |      |  |

|                    | Operation temperature |                           | -25                         |          | 85   | °C   |  |

| θЈА                | Thermal resistance    | 28-pin SSOP               |                             | 100      |      | °C/W |  |

<sup>(1)</sup> Input is BPZ data.

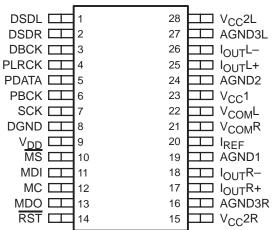

## **PIN ASSIGNMENTS**

## DSD1796 (TOP VIEW)

## **Terminal Functions**

| TERMINAL            |     |     |                                                                                                               |

|---------------------|-----|-----|---------------------------------------------------------------------------------------------------------------|

| NAME                | PIN | 1/0 | DESCRIPTIONS                                                                                                  |

| AGND1               | 19  | -   | Analog ground (internal bias)                                                                                 |

| AGND2               | 24  | _   | Analog ground (internal bias)                                                                                 |

| AGND3L              | 27  | -   | Analog ground (L-channel DACFF)                                                                               |

| AGND3R              | 16  | -   | Analog ground (R-channel DACFF)                                                                               |

| DBCK                | 3   | I   | Bit clock input for DSD mode (1)                                                                              |

| DGND                | 8   | _   | Digital ground                                                                                                |

| DSDL                | 1   | I/O | L-channel audio data input for DSD mode PCM mode zero flag for L-channel when in zero-flag output mode(2)     |

| DSDR                | 2   | I/O | R-channel audio data input for DSD mode<br>PCM mode zero flag for R-channel when in zero-flag output mode (2) |

| I <sub>OUT</sub> L+ | 25  | 0   | L-channel analog current output +                                                                             |

| IOUTL-              | 26  | 0   | L-channel analog current output –                                                                             |

| I <sub>OUT</sub> R+ | 17  | 0   | R-channel analog current output +                                                                             |

| I <sub>OUT</sub> R- | 18  | 0   | R-channel analog current output –                                                                             |

| I <sub>REF</sub>    | 20  | _   | Output current reference bias pin                                                                             |

| MC                  | 12  | I   | Mode control clock input <sup>(1)</sup>                                                                       |

| MDI                 | 11  | I   | Mode control data input (1)                                                                                   |

| MDO                 | 13  | 0   | Mode control readback data output (3)                                                                         |

| MS                  | 10  | I/O | Mode control chip-select input <sup>(2)</sup>                                                                 |

| PBCK                | 6   | I   | Bit clock input for PCM mode (1)                                                                              |

| PDATA               | 5   | I   | Serial audio data input for PCM mode (1)                                                                      |

| PLRCK               | 4   | I   | Left and right clock (fs) input for PCM mode (1)                                                              |

| RST                 | 14  | I   | Reset(1)                                                                                                      |

| SCK                 | 7   | I   | System clock input (1)                                                                                        |

| V <sub>CC</sub> 1   | 23  | _   | Analog power supply, 5 V                                                                                      |

| V <sub>CC</sub> 2L  | 28  | _   | Analog power supply (L-channel DACFF), 5 V                                                                    |

| V <sub>CC</sub> 2R  | 15  | _   | Analog power supply (R-channel DACFF), 5 V                                                                    |

| VCOML               | 22  | _   | L-channel internal bias decoupling pin                                                                        |

| V <sub>COM</sub> R  | 21  | _   | R-channel internal bias decoupling pin                                                                        |

| $V_{DD}$            | 9   | _   | Digital power supply, 3.3 V                                                                                   |

<sup>(1)</sup> Schmitt-trigger input, 5-V tolerant

(2) Schmitt-trigger input and output. 5-V tolerant input, and CMOS output

(3) 3-state output

## **FUNCTIONAL BLOCK DIAGRAM**

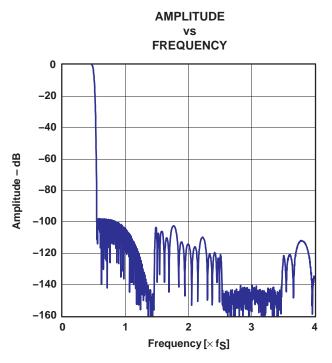

## **TYPICAL PERFORMANCE CURVES**

## **DIGITAL FILTER**

## **Digital Filter Response**

**AMPLITUDE FREQUENCY** 0.0005 0.0004 0.0003 0.0002 Amplitude – dB 0.0001 -0.0001 -0.0002-0.0003 -0.0004-0.0005 0.3 0.0 0.1 0.2 0.4 0.5 Frequency [ $\times$  fs]

Figure 1. Frequency Response, Sharp Rolloff

Figure 4. Transition Characteristics, Slow Rolloff

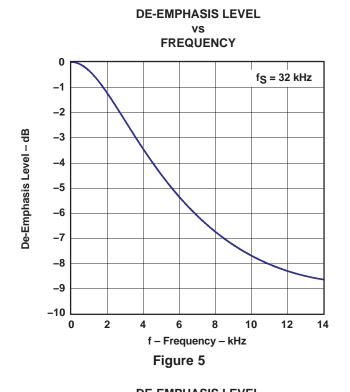

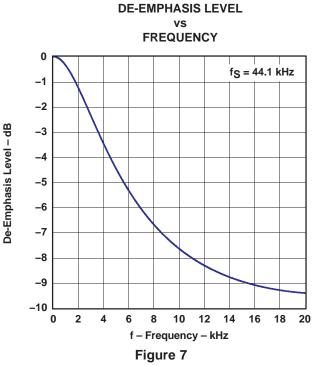

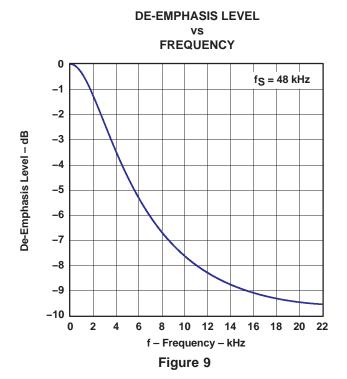

## **De-Emphasis Filter**

## **De-Emphasis Filter (Continued)**

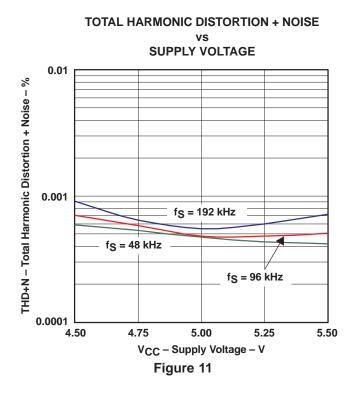

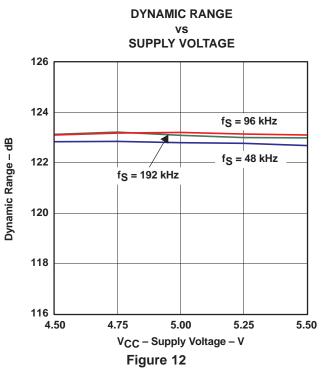

## **ANALOG DYNAMIC PERFORMANCE**

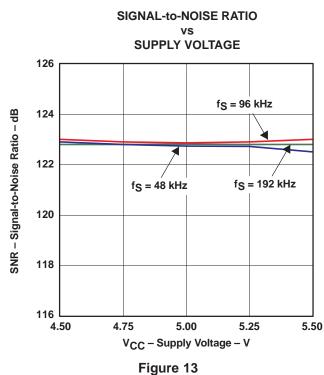

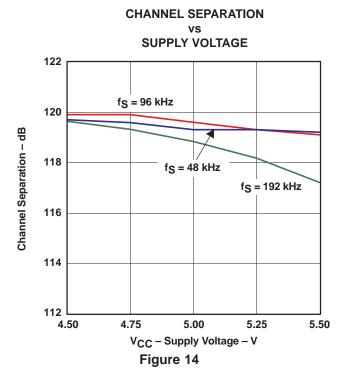

## **Supply Voltage Characteristics**

NOTE: PCM mode,  $T_A = 25$ °C,  $V_{DD} = 3.3$  V, measurement circuit is Figure 32.

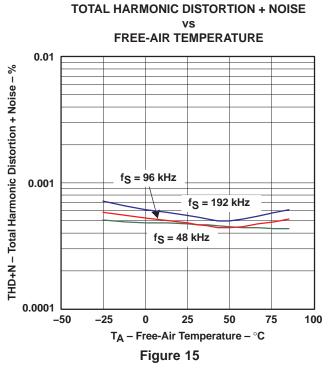

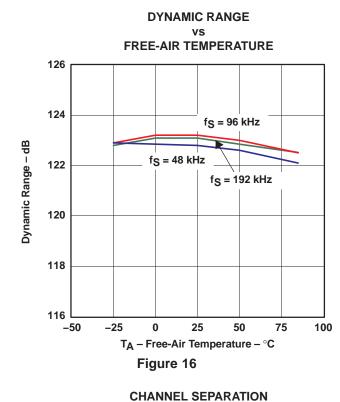

## **Temperature Characteristics**

NOTE: PCM mode,  $V_{CC} = 5 \text{ V}$ ,  $V_{DD} = 3.3 \text{ V}$ , measurement circuit is Figure 32.

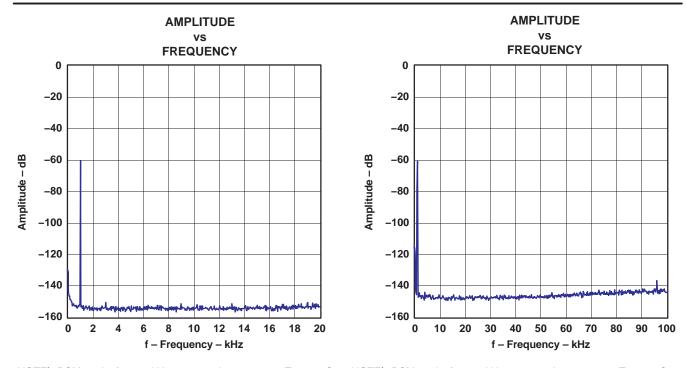

NOTE: PCM mode, fs = 48 kHz, 32768 point 8 average, T $_{A}$  = 25°C,  $V_{DD}$  = 3.3 V,  $V_{CC}$  = 5 V, measurement circuit is Figure 32.

NOTE: PCM mode,  $f_S = 96$  kHz, 32768 point 8 average,  $T_A = 25$ °C,  $V_{DD} = 3.3$  V,  $V_{CC} = 5$  V, measurement circuit is Figure 32.

Figure 19. –60-db Output Spectrum, BW = 20 kHz Figure 20. –60-db Output Spectrum, BW = 100 kHz

NOTE: PCM mode,  $f_S = 48$  kHz,  $T_A = 25$ °C,  $V_{DD} = 3.3$  V,  $V_{CC} = 5$  V, NOTE: DSD mode (FIR-2), 32768 point 8 average,  $T_A = 25$ °C, measurement circuit is Figure 32.  $V_{DD} = 3.3$  V,  $V_{CC} = 5$  V, measurement circuit is Figure 33.

Figure 21. THD+N vs Input Level, PCM Mode

Figure 22. -60-db Output Spectrum, DSD Mode

## SYSTEM CLOCK AND RESET FUNCTIONS

## **System Clock Input**

The DSD1796 requires a system clock for operating the digital interpolation filters and advanced segment DAC modulators. The system clock is applied at the SCK input (pin 7). The DSD1796 has a system clock detection circuit that automatically senses the frequency at which the system clock is operating. Table 1 shows examples of system clock frequencies for common audio sampling rates. If the oversampling rate of the delta-sigma modulator is selected as 128  $f_S$ , the system clock frequency is required to be over 256  $f_S$ .

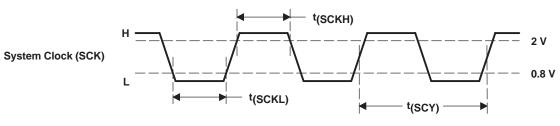

Figure 23 shows the timing requirements for the system clock input. For optimal performance, it is important to use a clock source with low phase jitter and noise. One of the Texas Instruments PLL1700 family of multiclock generators is an excellent choice for providing the DSD1796 system clock.

Table 1. System Clock Rates for Common Audio Sampling Frequencies

| CAMPI ING EDECLIENCY | SYSTEM CLOCK FREQUENCY (fSCK) (MHz) |                    |                    |                    |                    |                    |  |  |

|----------------------|-------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|

| SAMPLING FREQUENCY   | 128 f <sub>S</sub>                  | 192 f <sub>S</sub> | 256 f <sub>S</sub> | 384 f <sub>S</sub> | 512 f <sub>S</sub> | 768 f <sub>S</sub> |  |  |

| 32 kHz               | 4.096                               | 6.144              | 8.192              | 12.288             | 16.384             | 24.576             |  |  |

| 44.1 kHz             | 5.6488                              | 8.4672             | 11.2896            | 16.9344            | 22.5792            | 33.8688            |  |  |

| 48 kHz               | 6.144                               | 9.216              | 12.288             | 18.432             | 24.576             | 36.864             |  |  |

| 96 kHz               | 12.288                              | 18.432             | 24.576             | 36.864             | 49.152             | 73.728             |  |  |

| 192 kHz              | 24.576                              | 36.864             | 49.152             | 73.728             | _(1)               | _(1)               |  |  |

<sup>(1)</sup> This system clock rate is not supported for the given sampling frequency.

|         | PARAMETERS                        | MIN      | MAX | UNITS |

|---------|-----------------------------------|----------|-----|-------|

| t(SCY)  | System clock pulse cycle time     | 13       |     | ns    |

| t(SCKH) | System clock pulse duration, HIGH | 0.4(SCY) |     | ns    |

| t(SCKL) | System clock pulse duration, LOW  | 0.4(SCY) |     | ns    |

Figure 23. System Clock Input Timing

## **Power-On and External Reset Functions**

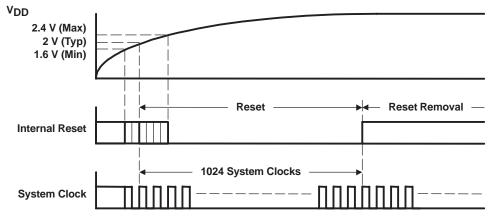

The DSD1796 includes a power-on reset function. Figure 24 shows the operation of this function. With  $V_{DD} > 2$  V, the power-on reset function is enabled. The initialization sequence requires 1024 system clocks from the time  $V_{DD} > 2$  V. After the initialization period, the DSD1796 is set to its default reset state, as described in the *MODE CONTROL REGISTERS* section of this data sheet.

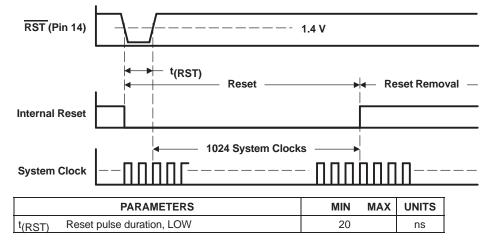

The DSD1796 also includes an external reset capability using the RST input (pin 14). This allows an external controller or master reset circuit to force the DSD1796 to initialize to its default reset state.

Figure 25 shows the external reset operation and timing. The RST pin is set to logic 0 for a minimum of 20 ns. The RST pin is then set to a logic 1 state, thus starting the initialization sequence, which requires 1024 system clock periods. The external reset is especially useful in applications where there is a delay between the DSD1796 power up and system clock activation.

Figure 24. Power-On Reset Timing

Figure 25. External Reset Timing

#### **AUDIO DATA INTERFACE**

#### **Audio Serial Interface**

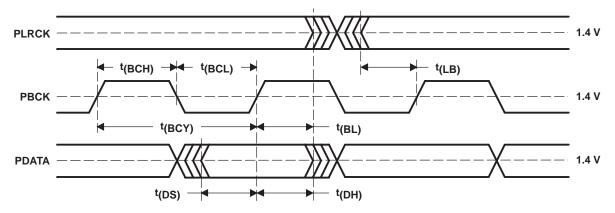

The audio interface port is a 3-wire serial port. It includes PLRCK (pin 4), PBCK (pin 6), and PDATA (pin 5). PBCK is the serial audio bit clock, and it is used to clock the serial data present on PDATA into the serial shift register of the audio interface. Serial data is clocked into the DSD1796 on the rising edge of PBCK. PLRCK is the serial audio left/right word clock.

The DSD1796 requires the synchronization of PLRCK and the system clock, but does not need a specific phase relation between PLRCK and the system clock.

If the relationship between PLRCK and the system clock changes more than  $\pm 6$  PBCK, internal operation is initialized within  $1/f_S$  and analog outputs are forced to the bipolar zero level until resynchronization between PLRCK and the system clock is completed.

#### **PCM Audio Data Formats and Timing**

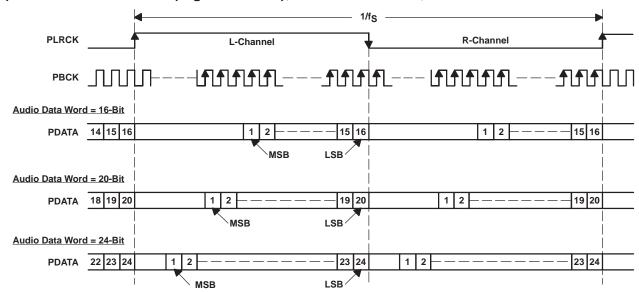

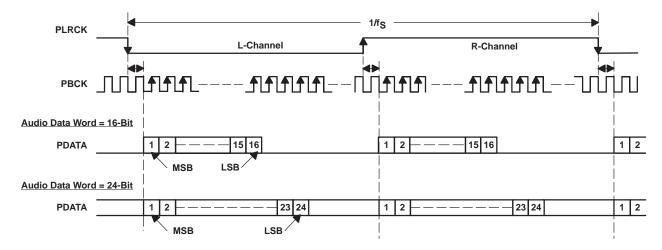

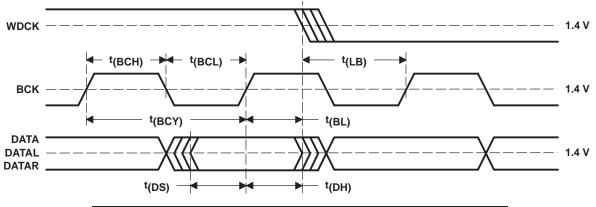

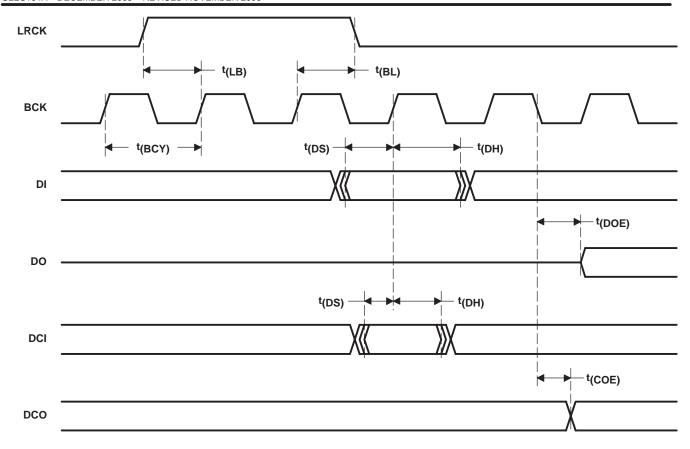

The DSD1796 supports industry-standard audio data formats, including standard right-justified, I<sup>2</sup>S, and left-justified. The data formats are shown in Figure 27. Data formats are selected using the format bits, FMT[2:0], in control register 18. The default data format is 24-bit I<sup>2</sup>S. All formats require binary 2s complement, MSB-first audio data. Figure 26 shows a detailed timing diagram for the serial audio interface.

|        | PARAMETERS                     | MIN                | MAX | UNITS |

|--------|--------------------------------|--------------------|-----|-------|

| t(BCY) | PBCK pulse cycle time          | 70                 |     | ns    |

| t(BCL) | PBCK pulse duration, LOW       | 30                 |     | ns    |

| t(BCH) | PBCK pulse duration, HIGH      | 30                 |     | ns    |

| t(BL)  | PBCK rising edge to PLRCK edge | 10                 |     | ns    |

| t(LB)  | PLRCK edge to PBCK rising edge | 10                 |     | ns    |

| t(DS)  | PDATA setup time               | 10                 |     | ns    |

| t(DH)  | PDATA hold time                | 10                 |     | ns    |

| _      | PLRCK clock data               | 50% ± 2 bit clocks |     | locks |

Figure 26. Timing of Audio Interface

## (1) Standard Data Format (Right-Justified); L-Channel = HIGH, R-Channel = LOW

## (2) Left-Justified Data Format; L-Channel = HIGH, R-Channel = LOW

## (3) I<sup>2</sup>S Data Format; L-Channel = LOW, R-Channel = HIGH

Figure 27. Audio Data Input Formats

## **External Digital Filter Interface and Timing**

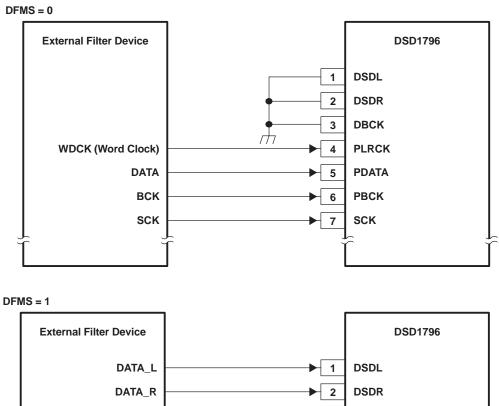

The DSD1796 supports an external digital filter interface comprising a 3- or 4-wire synchronous serial port, which allows the use of an external digital filter. External filters include the Texas Instruments DF1704 and DF1706, the Pacific Microsonics PMD200, or a programmable digital signal processor.

In the external DF mode, PLRCK (pin 4), PBCK (pin 6) and PDATA (pin 5) are defined as WDCK, the word clock; BCK, the bit clock; and DATA, the monaural data, respectively. The external digital filter interface is selected by using the DFTH bit of control register 20, which functions to bypass the internal digital filter of the DSD1796.

When the DFMS bit of control register 19 is set, the DSD1796 can process stereo data. In this case, DSDL (pin 1) and DSDR (pin 2) are defined as L-channel data and R-channel data input, respectively.

Detailed information for the external digital filter interface mode is provided in the APPLICATION FOR EXTERNAL DIGITAL FILTER INTERFACE section of this data sheet.

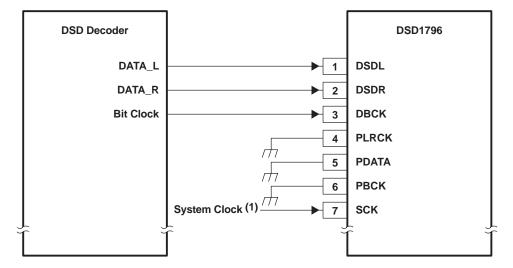

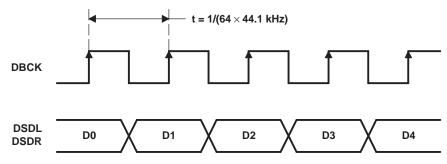

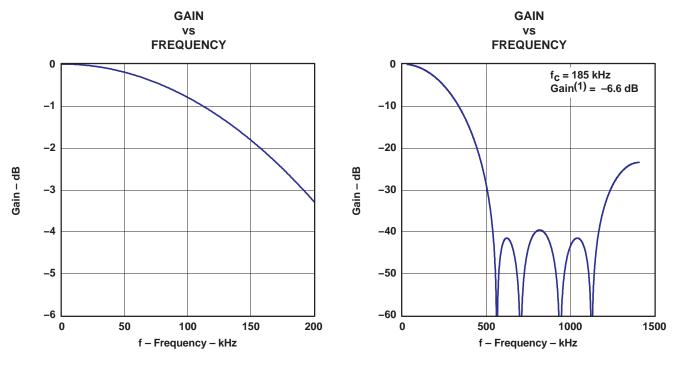

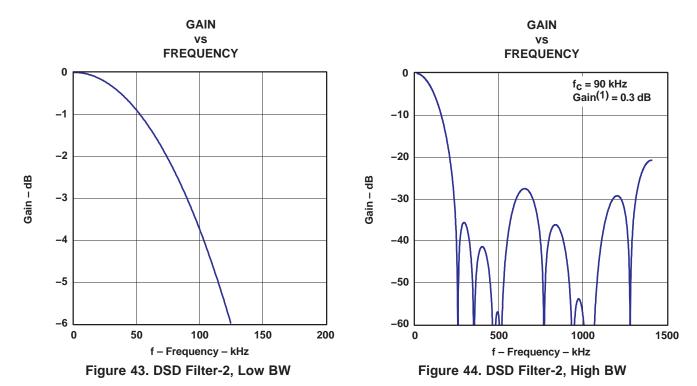

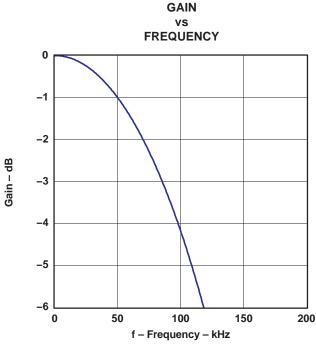

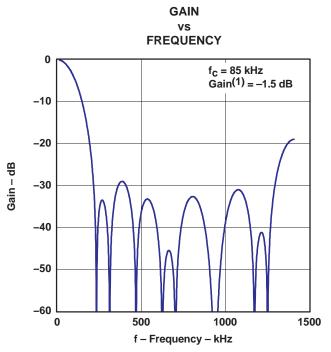

## **Direct Stream Digital (DSD) Format Interface and Timing**

The DSD1796 supports the DSD format interface operation, which includes out-of-band noise filtering using an internal analog FIR filter. The DSD format interface consists of a 3-wire synchronous serial port, which includes DBCK (pin 3), DSDL (pin 1), and DSDR (pin 2). DBCK is the serial bit clock. DSDL and DSDR are the L-channel and R-channel DSD data input, respectively. They are clocked into the DSD1796 on the rising edge of DBCK. PLRCK (pin 4) and PBCK (pin 6) must be connected to GND in the DSD mode. The DSD format (DSD mode) interface is activated by setting the DSD bit of control register 20.

Detailed information for the DSD mode is provided in the APPLICATION FOR DSD FORMAT (DSD MODE) INTERFACE section of this data sheet.

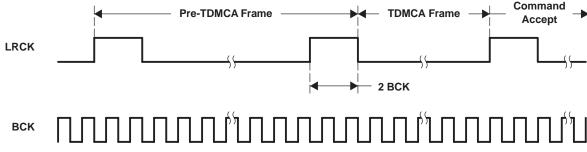

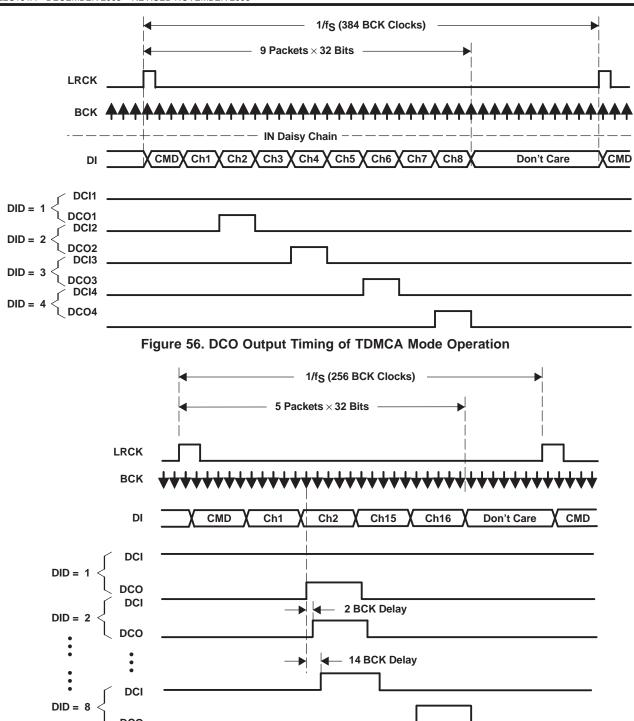

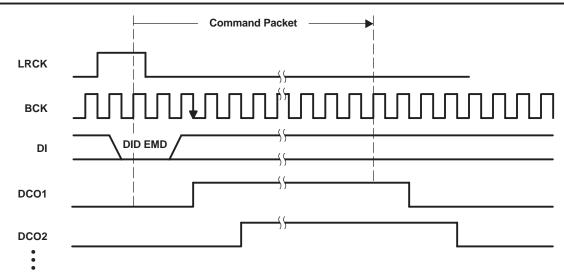

#### **TDMCA** Interface

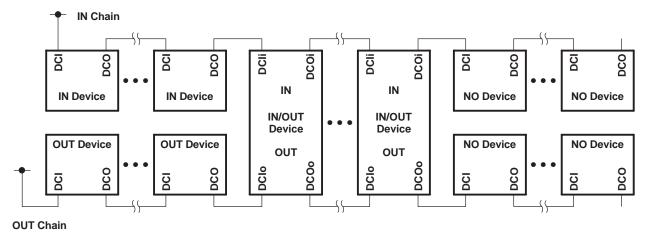

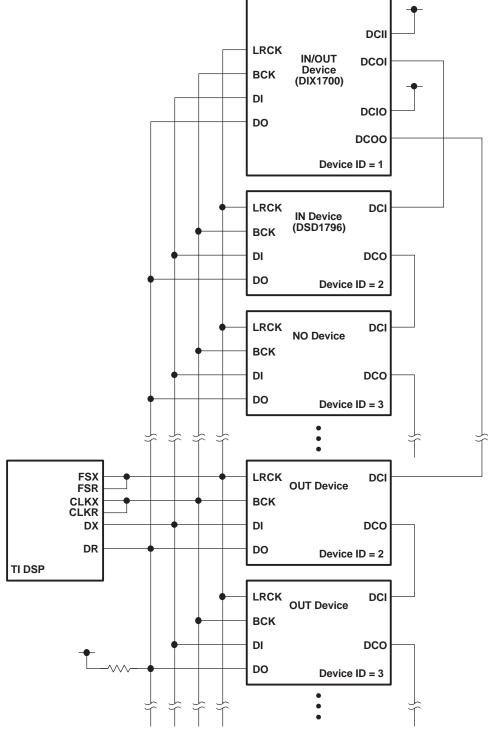

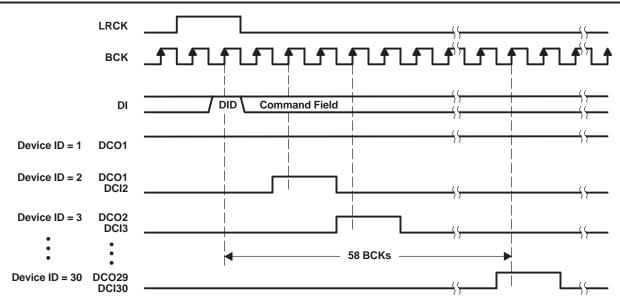

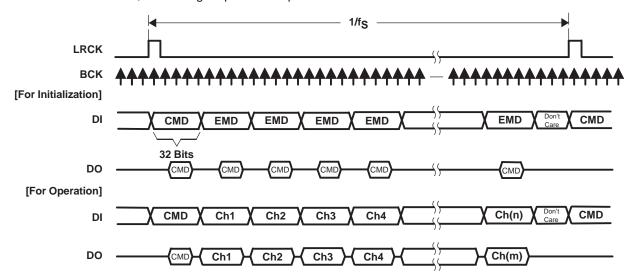

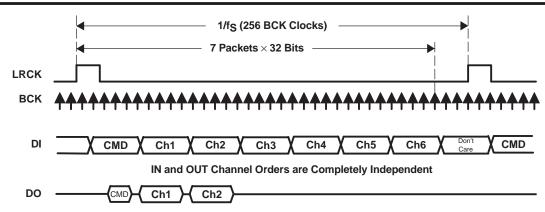

The DSD1796 supports the time-division-multiplexed command and audio (TDMCA) data format to enable control of and communication with a number of external devices over a single serial interface.

Detailed information for the TDMCA format is provided in the TDMCA INTERFACE FORMAT section of this data sheet.

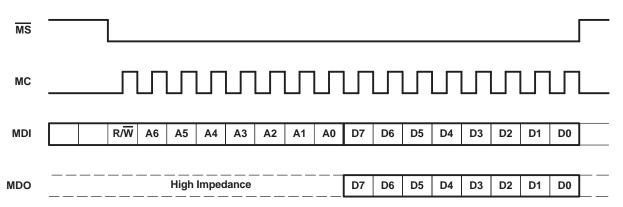

#### SERIAL CONTROL INTERFACE

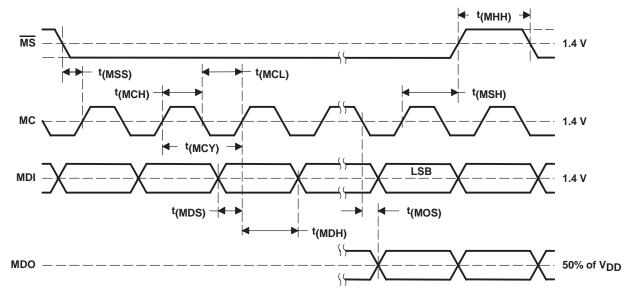

The serial control interface is a 4-wire synchronous serial port, which operates asynchronously with the serial audio interface and the system clock (SCK). The serial control interface is used to program and read the on-chip mode registers. The control interface includes MDO (pin 13), MDI (pin 11), MC (pin 12), and  $\overline{\rm MS}$  (pin 10). MDO is the serial data output, used to read back the values of the mode registers; MDI is the serial data input, used to program the mode registers; MC is the serial bit clock, used to shift data in and out of the control port; and  $\overline{\rm MS}$  is the mode control enable, used to enable the internal mode register access.

## **Register Read/Write Operation**

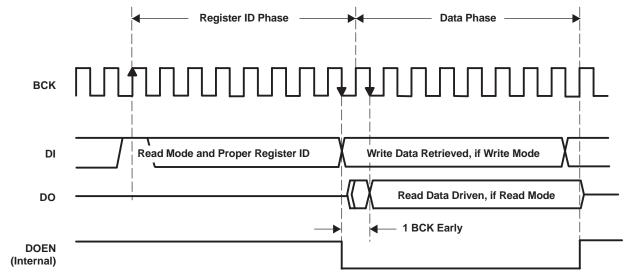

All read/write operations for the serial control port use 16-bit data words. Figure 28 shows the control data word format. The most significant bit is the read/write ( $R/\overline{W}$ ) bit. For write operations, the  $R/\overline{W}$  bit must be set to 0. For read operations, the  $R/\overline{W}$  bit must be set to 1. There are seven bits, labeled IDX[6:0], that hold the register index (or address) for the read and write operations. The least significant eight bits, D[7:0], contain the data to be written to, or the data that was read from, the register specified by IDX[6:0].

Figure 29 shows the functional timing diagram for writing or reading the serial control port.  $\overline{\text{MS}}$  is held at a logic 1 state until a register needs to be written or read. To start the register write or read cycle,  $\overline{\text{MS}}$  is set to logic 0. Sixteen clocks are then provided on MC, corresponding to the 16 bits of the control data word on MDI and readback data on MDO. After the eighth clock cycle has completed, the data from the indexed-mode control register appears on MDO during the read operation. After the sixteenth clock cycle has completed, the data is latched into the indexed-mode control register during the write operation. To write or read subsequent data,  $\overline{\text{MS}}$  must be set to 1 once.

Figure 28. Control Data Word Format for MDI

When Read Mode is Instructed

NOTE: Bit 15 is used for selection of write or read. Setting R/W = 0 indicates a write, while R/W = 1 indicates a read. Bits 14–8 are used for the register address. Bits 7–0 are used for register data.

Figure 29. Serial Control Format

|        | PARAMETER                         | MIN | MAX | UNITS |

|--------|-----------------------------------|-----|-----|-------|

| t(MCY) | MC pulse cycle time               | 100 |     | ns    |

| t(MCL) | MC low-level time                 | 40  |     | ns    |

| t(MCH) | MC high-level time                | 40  |     | ns    |

| t(MHH) | MS high-level time                | 80  |     | ns    |

| t(MSS) | MS falling edge to MC rising edge | 15  |     | ns    |

| t(MSH) | MS hold time(1)                   | 15  |     | ns    |

| t(MDH) | MDI hold time                     | 15  |     | ns    |

| t(MDS) | MDI setup time                    | 15  |     | ns    |

| t(MOS) | MC falling edge to MDO stable     |     | 30  | ns    |

(1) MC rising edge for LSB to MS rising edge

Figure 30. Control Interface Timing

## **MODE CONTROL REGISTERS**

## **User-Programmable Mode Controls**

The DSD1796 includes a number of user-programmable functions which are accessed via mode control registers. The registers are programmed using the serial control interface, which is previously desribed in the SERIAL CONTROL INTERFACE section of this data sheet. Table 2 lists the available mode control functions, along with their default reset conditions and associated register index.

**Table 2. User-Programmable Function Controls**

| FUNCTION                                                                                                                                                                | DEFAULT                           | REGISTER                   | BIT                                        | PCM | DSD    | DF<br>BYPASS |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|--------------------------------------------|-----|--------|--------------|

| Digital attenuation control 0 dB to -120 dB and mute, 0.5 dB step                                                                                                       | 0 dB                              | Register 16<br>Register 17 | ATL[7:0] (for L-ch)<br>ATR[7:0] (for R-ch) | yes |        |              |

| Attenuation load control—Disabled, enabled                                                                                                                              | Attenuation disabled              | Register 18                | ATLD                                       | yes |        |              |

| Input audio data format selection<br>16-, 20-, 24-bit standard (right-justified) format<br>24-bit MSB-first left-justified format<br>16-/24-bit I <sup>2</sup> S format | 24-bit I <sup>2</sup> S format    | Register 18                | FMT[2:0]                                   | yes |        | yes          |

| Sampling rate selection for de-emphasis<br>Disabled,44.1 kHz, 48 kHz, 32 kHz                                                                                            | De-emphasis disabled              | Register 18                | DMF[1:0]                                   | yes | yes(1) |              |

| De-emphasis control—Disabled, enabled                                                                                                                                   | De-emphasis disabled              | Register 18                | DME                                        | yes |        |              |

| Soft mute control—Mute disabled, enabled                                                                                                                                | Mute disabled                     | Register 18                | MUTE                                       | yes |        |              |

| Output phase reversal—Normal, reverse                                                                                                                                   | Normal                            | Register 19                | REV                                        | yes | yes    | yes          |

| Attenuation speed selection ×1 f <sub>S</sub> , ×(1/2)f <sub>S</sub> , ×(1/4)f <sub>S</sub> , ×(1/8)f <sub>S</sub>                                                      | ×1 fg                             | Register 19                | ATS[1:0]                                   | yes |        |              |

| DAC operation control—Enabled, disabled                                                                                                                                 | DAC operation enabled             | Register 19                | OPE                                        | yes | yes    | yes          |

| Zero flag pin operation control DSD data input, zero flag output                                                                                                        | DSD data input                    | Register 19                | ZOE                                        | yes |        | yes          |

| Stereo DF bypass mode select<br>Monaural, stereo                                                                                                                        | Monaural                          | Register 19                | DFMS                                       |     |        | yes          |

| Digital filter rolloff selection<br>Sharp rolloff, slow rolloff                                                                                                         | Sharp rolloff                     | Register 19                | FLT                                        | yes |        |              |

| Infinite zero mute control Disabled, enabled                                                                                                                            | Disabled                          | Register 19                | INZD                                       | yes |        | yes          |

| System reset control Reset operation , normal operation                                                                                                                 | Normal operation                  | Register 20                | SRST                                       | yes | yes    | yes          |

| DSD interface mode control DSD enabled, disabled                                                                                                                        | Disabled                          | Register 20                | DSD                                        | yes | yes    |              |

| Digital-filter bypass control DF enabled, DF bypass                                                                                                                     | DF enabled                        | Register 20                | DFTH                                       | yes |        | yes          |

| Monaural mode selection<br>Stereo, monaural                                                                                                                             | Stereo                            | Register 20                | MONO                                       | yes | yes    | yes          |

| Channel selection for monaural mode data L-channel, R-channel                                                                                                           | L-channel                         | Register 20                | CHSL                                       | yes | yes    | yes          |

| Delta-sigma oversampling rate selection ×64 fg, ×128 fg, ×32 fg                                                                                                         | ×64 fg                            | Register 20                | OS[1:0]                                    | yes | yes(2) | yes          |

| PCM zero output enable                                                                                                                                                  | Enabled                           | Register 21                | PCMZ                                       | yes |        | yes          |

| DSD zero output enable                                                                                                                                                  | Disabled                          | Register 21                | DZ[1:0]                                    |     | yes    |              |

| FUNCTION AVAILABLE ONLY FOR READ                                                                                                                                        |                                   |                            |                                            |     |        |              |

| Zero detection flag Not zero, zero detected                                                                                                                             | Not zero = 0<br>Zero detected = 1 | Register 22                | ZFGL (for L-ch)<br>ZFGR (for R-ch)         | yes | yes    | yes          |

| Device ID (at TDMCA)                                                                                                                                                    | -                                 | Register 23                | ID[4:0]                                    | yes |        |              |

| ·                                                                                                                                                                       |                                   | ·                          |                                            |     |        |              |

<sup>(1)</sup> When in DSD mode, DMF[1:0] is defined as DSD filter (analog FIR) performance selection.

<sup>(2)</sup> When in DSD mode, OS[1:0] is defined as DSD filter (analog FIR) operation rate selection.

## **Register Map**

The mode control register map is shown in Table 3. Registers 16–21 include an  $R/\overline{W}$  bit, which determines whether a register read ( $R/\overline{W} = 1$ ) or write ( $R/\overline{W} = 0$ ) operation is performed. Registers 22 and 23 are read-only.

**Table 3. Mode Control Register Map**

|             | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | В7   | В6   | B5   | B4   | В3   | B2   | B1   | В0   |

|-------------|-----|-----|-----|-----|-----|-----|----|----|------|------|------|------|------|------|------|------|

| Register 16 | R/W | 0   | 0   | 1   | 0   | 0   | 0  | 0  | ATL7 | ATL6 | ATL5 | ATL4 | ATL3 | ATL2 | ATL1 | ATL0 |

| Register 17 | R/W | 0   | 0   | 1   | 0   | 0   | 0  | 1  | ATR7 | ATR6 | ATR5 | ATR4 | ATR3 | ATR2 | ATR1 | ATR0 |

| Register 18 | R/W | 0   | 0   | 1   | 0   | 0   | 1  | 0  | ATLD | FMT2 | FMT1 | FMT0 | DMF1 | DMF0 | DME  | MUTE |

| Register 19 | R/W | 0   | 0   | 1   | 0   | 0   | 1  | 1  | REV  | ATS1 | ATS0 | OPE  | ZOE  | DFMS | FLT  | INZD |

| Register 20 | R/W | 0   | 0   | 1   | 0   | 1   | 0  | 0  | RSV  | SRST | DSD  | DFTH | MONO | CHSL | OS1  | OS0  |

| Register 21 | R/W | 0   | 0   | 1   | 0   | 1   | 0  | 1  | RSV  | RSV  | RSV  | RSV  | RSV  | DZ1  | DZ0  | PCMZ |

| Register 22 | R   | 0   | 0   | 1   | 0   | 1   | 1  | 0  | RSV  | RSV  | RSV  | RSV  | RSV  | RSV  | ZFGR | ZFGL |

| Register 23 | R   | 0   | 0   | 1   | 0   | 1   | 1  | 1  | RSV  | RSV  | RSV  | ID4  | ID3  | ID2  | ID1  | ID0  |

## **Register Definitions**

|             | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7   | B6   | B5   | B4   | B3   | B2   | B1   | B0   |

|-------------|-----|-----|-----|-----|-----|-----|----|----|------|------|------|------|------|------|------|------|

| Register 16 | R/W | 0   | 0   | 1   | 0   | 0   | 0  | 0  | ATL7 | ATL6 | ATL5 | ATL4 | ATL3 | ATL2 | ATL1 | ATL0 |

|             |     |     | ı   |     |     |     |    | ı  | I    | I    | I    |      |      |      |      |      |

| Register 17 | R/W | 0   | 0   | 1   | 0   | 0   | 0  | 1  | ATR7 | ATR6 | ATR5 | ATR4 | ATR3 | ATR2 | ATR1 | ATR0 |

#### R/W: Read/Write Mode Select

When  $R/\overline{W} = 0$ , a write operation is performed.

When  $R/\overline{W} = 1$ , a read operation is performed.

Default value: 0

#### ATx[7:0]: Digital Attenuation Level Setting

These bits are available for read and write.

Default value: 1111 1111b

Each DAC output has a digital attenuator associated with it. The attenuator can be set from 0 dB to –120 dB, in 0.5-dB steps. Alternatively, the attenuator can be set to infinite attenuation (or mute).

The attenuation data for each channel can be set individually. However, the data load control (the ATLD bit of control register 18) is common to both attenuators. ATLD must be set to 1 in order to change an attenuator setting. The attenuation level can be set using the following formula:

Attenuation level (dB) =  $0.5 \text{ dB} \bullet (ATx[7:0]_{DEC} - 255)$

where  $ATx[7:0]_{DEC} = 0$  through 255

For  $ATx[7:0]_{DEC} = 0$  through 14, the attenuator is set to infinite attenuation. The following table shows attenuation levels for various settings:

| ATx[7:0]   | Decimal Value | Attenuation Level Setting      |

|------------|---------------|--------------------------------|

| 1111 1111b | 255           | 0 dB, no attenuation (default) |

| 1111 1110b | 254           | –0.5 dB                        |

| 1111 1101b | 253           | −1.0 dB                        |

| :          | :             | :                              |

| 0001 0000b | 16            | –119.5 dB                      |

| 0000 1111b | 15            | –120.0 dB                      |

| 0000 1110b | 14            | Mute                           |

| :          | :             | i                              |

| 0000 0000b | 0             | Mute                           |

|             | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | B7   | В6   | B5   | B4   | В3   | B2   | B1  | В0   |

|-------------|-----|-----|-----|-----|-----|-----|----|----|------|------|------|------|------|------|-----|------|

| Register 18 | R/W | 0   | 0   | 1   | 0   | 0   | 1  | 0  | ATLD | FMT2 | FMT1 | FMT0 | DMF1 | DMF0 | DME | MUTE |

#### R/W: Read/Write Mode Select

When  $R/\overline{W} = 0$ , a write operation is performed. When  $R/\overline{W} = 1$ , a read operation is performed.

Default value: 0

#### **ATLD: Attenuation Load Control**

This bit is available for read and write.

Default value: 0

| ATLD = 0 | Attenuation control disabled (default) |

|----------|----------------------------------------|

| ATLD = 1 | Attenuation control enabled            |

The ATLD bit is used to enable loading of the attenuation data contained in registers 16 and 17. When ATLD = 0, the attenuation settings remain at the previously programmed levels, ignoring new data loaded from registers 16 and 17. When ATLD = 1, attenuation data written to registers 16 and 17 is loaded normally.

#### FMT[2:0]: Audio Interface Data Format

These bits are available for read and write.

Default value: 101

| FMT[2:0] | Audio Data Format Selection                   |

|----------|-----------------------------------------------|

| 000      | 16-bit standard format, right-justified data  |

| 001      | 20-bit standard format, right-justified data  |

| 010      | 24-bit standard format, right-justified data  |

| 011      | 24-bit MSB-first, left-justified format data  |

| 100      | 16-bit I <sup>2</sup> S-format data           |

| 101      | 24-bit I <sup>2</sup> S-format data (default) |

| 110      | Reserved                                      |

| 111      | Reserved                                      |

The FMT[2:0] bits are used to select the data format for the serial audio interface.

For the external digital filter interface mode (DFTH mode), this register is operated as shown in the APPLICATION FOR EXTERNAL DIGITAL FILTER INTERFACE section of this data sheet.

#### DMF[1:0]: Sampling Frequency Selection for the De-Emphasis Function

These bits are available for read and write.

Default value: 00

| DMF[1:0] | De-Emphasis Sampling Frequency Selection |

|----------|------------------------------------------|

| 00       | Disabled (default)                       |

| 01       | 48 kHz                                   |

| 10       | 44.1 kHz                                 |

| 11       | 32 kHz                                   |

The DMF[1:0] bits are used to select the sampling frequency used by the digital de-emphasis function when it is enabled by setting the DME bit. The de-emphasis curves are shown in the *TYPICAL PERFORMANCE CURVES* section of this data sheet.

For the DSD mode, analog FIR filter performance can be selected using this register. A register map and filter response plots are shown in the *APPLICATION FOR DSD FORMAT (DSD MODE) INTERFACE* section of this data sheet.

#### SLES101A - DECEMBER 2003 - REVISED NOVEMBER 2006

## **DME: Digital De-Emphasis Control**

This bit is available for read and write.

Default value: 0

| DME = 0 | De-emphasis disabled (default) |

|---------|--------------------------------|

| DME = 1 | De-emphasis enabled            |

The DME bit is used to enable or disable the de-emphasis function for both channels.

#### **MUTE: Soft Mute Control**

This bit is available for read and write.

Default value: 0

| MUTE = 0 | Mute disabled (default) |

|----------|-------------------------|

| MUTE = 1 | Mute enabled            |

The MUTE bit is used to enable or disable the soft mute function for both channels.

Soft mute is operated as a 256-step attenuator. The speed for each step to  $-\infty$  dB (mute) is determined by the attenuation rate selected in the ATS register.

|             | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7  | B6   | B5   | B4  | B3  | B2   | B1  | B0   |

|-------------|-----|-----|-----|-----|-----|-----|----|----|-----|------|------|-----|-----|------|-----|------|

| Register 19 | R/W | 0   | 0   | 1   | 0   | 0   | 1  | 1  | REV | ATS1 | ATS0 | OPE | ZOE | DFMS | FLT | INZD |

#### R/W: Read/Write Mode Select

When  $R/\overline{W} = 0$ , a write operation is performed.

When  $R/\overline{W} = 1$ , a read operation is performed.

Default value: 0

## **REV: Output Phase Reversal**

This bit is available for read and write.

Default value: 0

| REV = 0 | Normal output (default) |

|---------|-------------------------|

| REV = 1 | Inverted output         |

The REV bit is used to invert the output phase for both channels.

#### ATS[1:0]: Attenuation Rate Select

These bits are available for read and write.

Default value: 00

| ATS[1:0] | Attenuation Rate Selection |

|----------|----------------------------|

| 00       | Every PLRCK (default)      |

| 01       | PLRCK/2                    |

| 10       | PLRCK/4                    |

| 11       | PLRCK/8                    |

The ATS[1:0] bits are used to select the rate at which the attenuator is decremented/incremented during level transitions.

#### **OPE: DAC Operation Control**

This bit is available for read and write.

Default value: 0

| OPE = 0 | DAC operation enabled (default) |

|---------|---------------------------------|

| OPE = 1 | DAC operation disabled          |

The OPE bit is used to enable or disable the analog output for both channels. Disabling the analog outputs forces them to the bipolar zero level (BPZ) even if digital audio data is present on the input.

#### **ZOE: Zero Flag Pin Operation Control**

This bit is available for read and write.

Default value: 0

| ZOE = 0 | DSD data input (default) |

|---------|--------------------------|

| ZOE = 1 | Zero flag output         |

The ZOE bit is used to change the DSDL (pin 1) and DSDR (pin 2) pin assignments. When the ZOE bit is set to 0, DSDL and DSDR are inputs for L-channel and R-channel data. When the ZOE bit is set to 1, DSDL and DSDR become outputs for the L-channel and R-channel zero flags, respectively. See the PCMZ and DZ[1:0] bit descriptions of register 21.

#### **DFMS: Stereo DF Bypass Mode Select**

This bit is available for read and write.

Default value: 0

| DFMS = 0 | Monaural (default)   |

|----------|----------------------|

| DFMS = 1 | Stereo input enabled |

The DFMS bit is used to enable stereo operation in the DF bypass mode. In the DF bypass mode, when DFMS is set to 0, the pin for the input data is PDATA (pin 5) only, therefore the DSD1796 operates as a monaural DAC. When DFMS is set to 1, the DSD1796 can operate as a stereo DAC with inputs of input L-channel and R-channel data on DSDL (pin 1) and DSDR (pin 2), respectively.

#### **FLT: Digital Filter Rolloff Control**

This bit is available for read and write.

Default value: 0

| FLT = 0 | Sharp rolloff (default) |

|---------|-------------------------|

| FLT = 1 | Slow rolloff            |

The FLT bit is used to select the digital filter rolloff characteristic. The filter responses for these selections are shown in the TYPICAL PERFORMANCE CURVES section of this data sheet.

#### **INZD: Infinite Zero Detect Mute Control**

This bit is available for read and write.

Default value: 0

| INZD = 0 | Infinite zero detect mute disabled (default) |

|----------|----------------------------------------------|

| INZD = 1 | Infinite zero detect mute enabled            |

The INZD bit is used to enable or disable the zero detect mute function. Setting INZD to 1 forces muted analog outputs to hold a bipolar zero level when the DSD1796 detects zero data in both channels continuously for 1024 sampling periods (1/f<sub>S</sub>). The infinite zero detect mute function is not available in the DSD mode.

SLES101A - DECEMBER 2003 - REVISED NOVEMBER 2006

|             | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | В7  | В6   | B5  | В4   | В3   | B2   | B1  | В0  |

|-------------|-----|-----|-----|-----|-----|-----|----|----|-----|------|-----|------|------|------|-----|-----|

| Register 20 | R/W | 0   | 0   | 1   | 0   | 1   | 0  | 0  | RSV | SRST | DSD | DFTH | MONO | CHSL | OS1 | OS0 |

#### R/W: Read/Write Mode Select

When  $R/\overline{W} = 0$ , a write operation is performed.

When  $R/\overline{W} = 1$ , a read operation is performed.

Default value: 0

### **SRST: System Reset Control**

This bit is available for write only.

Default value: 0

| SRST = 0 | Normal operation (default)                        |

|----------|---------------------------------------------------|

| SRST = 1 | System reset operation (generate one reset pulse) |

The SRST bit is used to reset the DSD1796 to the initial system condition.

#### **DSD: DSD Interface Mode Control**

This bit is available for read and write.

Default value: 0

| DSD = 0 | DSD interface mode disabled (default) |

|---------|---------------------------------------|

| DSD = 1 | DSD interface mode enabled            |

The DSD bit is used to enable or disable the DSD interface mode.

#### **DFTH: Digital Filter Bypass (or Through Mode) Control**

This bit is available for read and write.

Default value: 0

| DFTH = 0 | Digital filter enabled (default)                    |

|----------|-----------------------------------------------------|

| DFTH = 1 | Digital filter bypassed for external digital filter |

The DFTH bit is used to enable or disable the external digital filter interface mode.

#### **MONO: Monaural Mode Selection**

This bit is available for read and write.

Default value: 0

| MONO = 0 | Stereo mode (default) |

|----------|-----------------------|

| MONO = 1 | Monaural mode         |

The MONO function is used to change the operation mode from the normal stereo mode to the monaural mode. When the monaural mode is selected, both DACs operate in a balanced mode for one channel of audio input data. Channel selection is available for L-channel or R-channel data, determined by the CHSL bit as described immediately following.

#### **CHSL: Channel Selection for Monaural Mode**

This bit is available for read and write.

Default value: 0

| CHSL = 0 | L-channel selected (default) |

|----------|------------------------------|

| CHSL = 1 | R-channel selected           |

This bit is available when MONO = 1.

The CHSL bit selects L-channel or R-channel data to be used in monaural mode.

## OS[1:0]: Delta-Sigma Oversampling Rate Selection

These bits are available for read and write.

Default value: 00

| OS[1:0] | Operation Speed Select            |

|---------|-----------------------------------|

| 00      | 64 times f <sub>S</sub> (default) |

| 01      | 32 times f <sub>S</sub>           |

| 10      | 128 times f <sub>S</sub>          |

| 11      | Reserved                          |

The OS bits are used to change the oversampling rate of delta-sigma modulation. Use of this function enables the designer to stabilize the conditions at the post low-pass filter for different sampling rates. As an application example, programming to set 128 times in 44.1-kHz operation, 64 times in 96-kHz operation, and 32 times in 192-kHz operation allows the use of only a single type (cutoff frequency) of post low-pass filter. The 128-f<sub>S</sub> oversampling rate is not available at sampling rates above 100 kHz. If the 128-f<sub>S</sub> oversampling rate is selected, a system clock of more than 256 f<sub>S</sub> is required.

In DSD mode, these bits are used to select the speed of the bit clock for DSD data coming into the analog FIR filter.

|             | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7  | B6  | B5  | B4  | В3  | B2  | B1  | В0   |

|-------------|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|------|

| Register 21 | R/W | 0   | 0   | 1   | 0   | 1   | 0  | 1  | RSV | RSV | RSV | RSV | RSV | DZ1 | DZ0 | PCMZ |

#### R/W: Read/Write Mode Select

When  $R/\overline{W} = 0$ , a write operation is performed.

When  $R/\overline{W} = 1$ , a read operation is performed.

Default value: 0

#### DZ[1:0]: DSD Zero Output Enable

These bits are available for read and write.

Default value: 00

| DZ[1:0] | Zero Output Enable  |

|---------|---------------------|

| 00      | Disabled (default)  |

| 01      | Even pattern detect |

| 1x      | 96h pattern detect  |

The DZ bits are used to enable or disable the output zero flags, and to select the zero pattern in the DSD mode. The DSD1796 sets zero flags when the numbers of 1s and 0s are equal in every 8 bits of DSD input data, or the DSD input data is 1001 0110 continuously for 23 ms.

#### **PCMZ: PCM Zero Output Enable**

These bits are available for read and write.

Default value: 1

| PCMZ = 0 | PCM zero output disabled          |

|----------|-----------------------------------|

| PCMZ = 1 | PCM zero output enabled (default) |

The PCMZ bit is used to enable or disable the output zero flags in the PCM mode and the external DF mode. The DSD1796 sets the zero flags when the input data is continuously zero for 1024 PLRCKs in the PCM mode or 1024 WDCKs in the external filter mode.

|             | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | B7  | B6  | B5  | B4  | В3  | B2  | B1   | В0   |

|-------------|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|------|------|

| Register 22 | R   | 0   | 0   | 1   | 0   | 1   | 1  | 0  | RSV | RSV | RSV | RSV | RSV | RSV | ZFGR | ZFGL |

#### R: Read Mode Select

Value is always 1, specifying the readback mode.

#### SLES101A - DECEMBER 2003 - REVISED NOVEMBER 2006

## **ZFGx: Zero-Detection Flag**

Where x = L or R, corresponding to the DAC output channel. These bits are available only for readback.

Default value: 00

| ZFGx = 0 | Not zero      |

|----------|---------------|

| ZFGx = 1 | Zero detected |

When the DSD1796 detects that audio input data is continuously zero, the ZFGx bit is set to 1 for the corresponding channel(s).

|             | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | B7  | В6  | B5  | B4  | В3  | B2  | B1  | В0  |

|-------------|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Register 23 | R   | 0   | 0   | 1   | 0   | 1   | 1  | 1  | RSV | RSV | RSV | ID4 | ID3 | ID2 | ID1 | ID0 |

#### R: Read Mode Select

Value is always 1, specifying the readback mode.

## ID[4:0]: Device ID

The ID[4:0] bits hold a device ID in the TDMCA mode.

#### APPLICATION INFORMATION

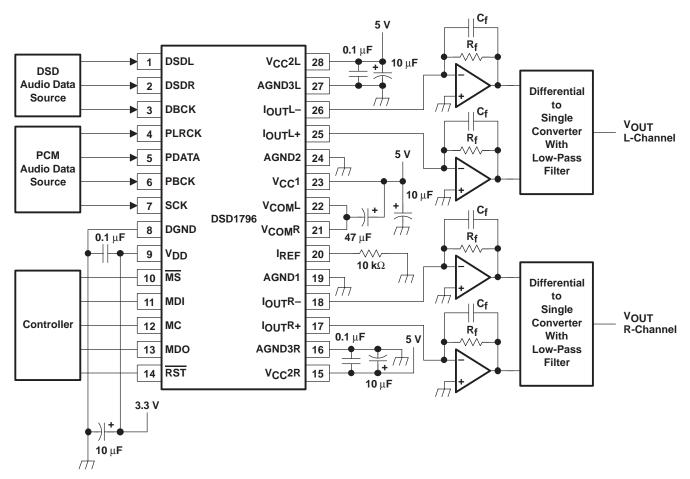

#### TYPICAL CONNECTION DIAGRAM

Figure 31. Typical Application Circuit

#### **APPLICATION CIRCUIT**

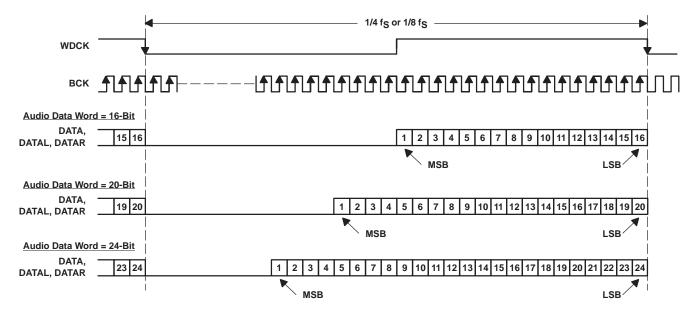

The design of the application circuit is very important in order to actually realize the high S/N ratio of which the DSD1796 is capable. This is because noise and distortion that are generated in an application circuit are not negligible.

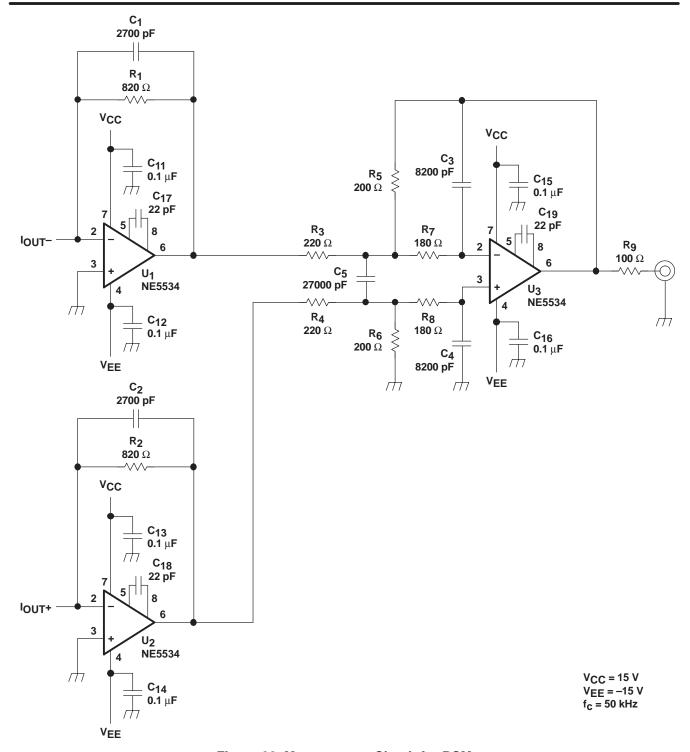

In the third-order LPF circuit of Figure 32, the output level is 2.1 V rms and 123 dB S/N is achieved.

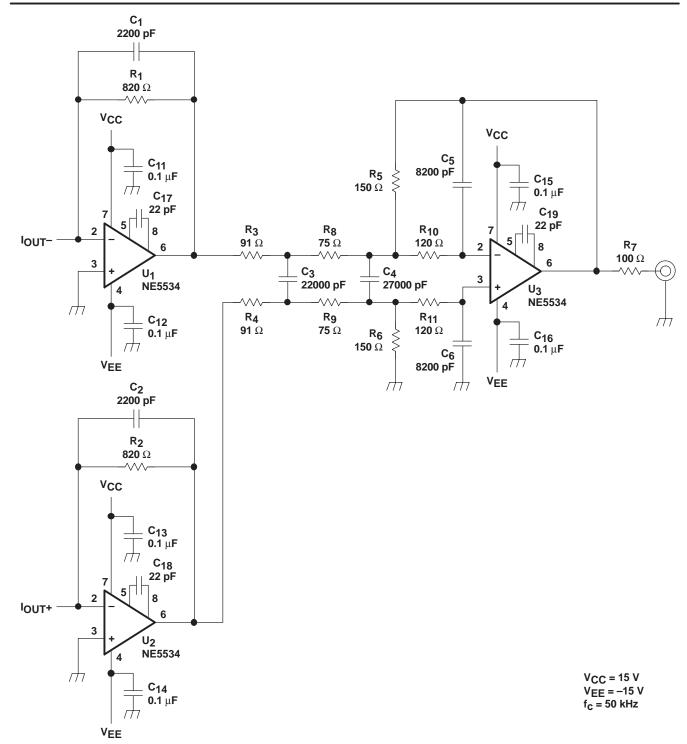

Figure 33 shows a circuit for the DSD mode, which is a fourth-order LPF in order to reduce the out-of-band noise.

#### I/V Section

The current of the DSD1796 on each of the output pins (I<sub>OUT</sub>L+, I<sub>OUT</sub>L-, I<sub>OUT</sub>R+, I<sub>OUT</sub>R-) is 4 mA p-p at 0 dB (full scale). The voltage output level of the I/V converter (Vi) is given by following equation:

$Vi = 4 \text{ mA p-p} \times R_f (R_f : feedback resistance of I/V converter)}$

An NE5534 operational amplifier is recommended for the I/V circuit to obtain the specified performance. Dynamic performance such as the gain bandwidth, settling time, and slew rate of the operational amplifier affects the audio dynamic performance of the I/V section.

#### **Differential Section**

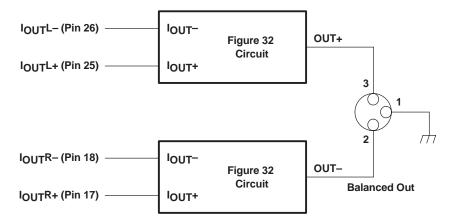

The DSD1796 voltage outputs are followed by differential amplifier stages, which sum the differential signals for each channel, creating a single-ended I/V op-amp output. In addition, the differential amplifiers provide a low-pass filter function.

The operational amplifier recommended for the differential circuit is the low-noise type.

Figure 32. Measurement Circuit for PCM

Figure 33. Measurement Circuit for DSD

Figure 34. Measurement Circuit for Monaural Mode

## APPLICATION FOR EXTERNAL DIGITAL FILTER INTERFACE

Figure 35. Connection Diagram for External Digital Filter (Internal DF Bypass Mode) Application

#### Application for Interfacing With an External Digital Filter

For some applications, it may be desirable to use an external digital filter to perform the interpolation function, as it can provide improved stop-band attenuation when compared to the internal digital filter of the DSD1796.

The DSD1796 supports several external digital filters, including:

- Texas Instruments DF1704 and DF1706

- Pacific Microsonics PMD200 HDCD filter/decoder IC

- Programmable digital signal processors

The external digital filter application mode is accessed by programming the following bit in the corresponding control register:

DFTH = 1 (register 20)

The pins used to provide the serial interface for the external digital filter are shown in the connection diagram of Figure 35. The word clock (WDCK) signal must be operated at  $8\times$  or  $4\times$  the desired sampling frequency,  $f_S$ .

## Pin Assignment When Using the External Digital Filter Interface

- PLRCK (pin 4): WDCK as word clock input

- PBCK (pin 6): BCK as bit clock for audio data

- PDATA (pin 5): DATA as monaural audio data input when the DFMS bit is not set to 1

- DSDL (pin 1): DATAL as L-channel audio data input when the DFMS bit is set to 1

- DSDR (pin 2): DATAR as R-channel audio data input when the DFMS bit is set to 1

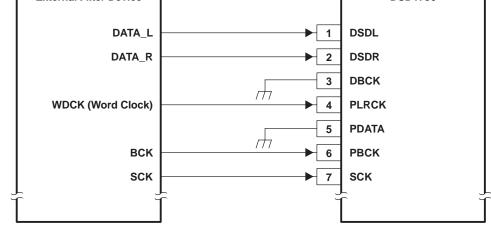

#### **Audio Format**

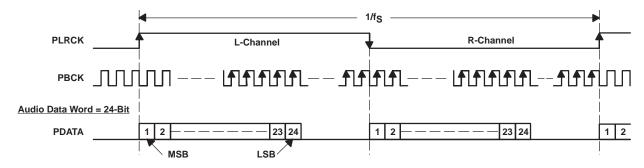

The DSD1796 in the external digital filter interface mode supports right-justified audio formats including 16-bit, 20-bit, and 24-bit audio data, as shown in Figure 36. The audio format is selected by the FMT[2:0] bits of control register 18.

Figure 36. Audio Data Input Format for External Digital Filter (Internal DF Bypass Mode) Application

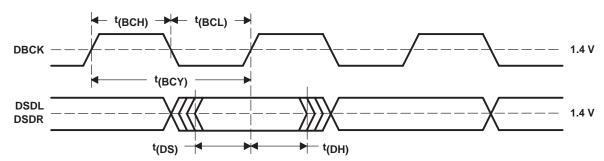

#### System Clock (SCK) and Interface Timing

The DSD1796 in an application using an external digital filter requires the synchronization of WDCK and the system clock. The system clock is phase-free with respect to WDCK. Interface timing among WDCK, BCK, DATA, DATAL, and DATAR is shown in Figure 37.

|        | PARAMETER                            | MIN | MAX | UNITS |

|--------|--------------------------------------|-----|-----|-------|

| t(BCY) | BCK pulse cycle time                 | 20  |     | ns    |

| t(BCL) | BCK pulse duration, LOW              | 7   |     | ns    |

| t(BCH) | BCK pulse duration, HIGH             | 7   |     | ns    |

| t(BL)  | BCK rising edge to WDCK falling edge | 5   |     | ns    |

| t(LB)  | WDCK falling edge to BCK rising edge | 5   |     | ns    |

| t(DS)  | DATA, DATAL, DATAR setup time        | 5   |     | ns    |

| t(DH)  | DATA, DATAL, DATAR hold time         | 5   |     | ns    |

Figure 37. Audio Interface Timing for External Digital Filter (Internal DF Bypass Mode) Application

#### Functions Available in the External Digital Filter Mode

The external digital filter mode is selected by setting DSD = 0 (register 20, B5) and DFTH = 1 (register 20. B4).

The external digital filter mode allows access to the majority of the DSD1796 mode control functions.

The following table shows the register mapping available when the external digital filter mode is selected, along with descriptions of functions which are modified when using this mode selection.

|             | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | В7  | В6   | B5   | B4   | В3   | B2   | B1   | В0   |

|-------------|-----|-----|-----|-----|-----|-----|----|----|-----|------|------|------|------|------|------|------|

| Register 16 | R/W | 0   | 0   | 1   | 0   | 0   | 0  | 0  | -   | -    | -    | -    | _    | -    | -    | _    |

| Register 17 | R/W | 0   | 0   | 1   | 0   | 0   | 0  | 1  | -   | -    | _    | -    | _    | _    | -    | _    |

| Register 18 | R/W | 0   | 0   | 1   | 0   | 0   | 1  | 0  | -   | FMT2 | FMT1 | FMT0 | -    | -    | -    | _    |

| Register 19 | R/W | 0   | 0   | 1   | 0   | 0   | 1  | 1  | REV | -    | _    | OPE  | _    | DFMS | -    | INZD |