Sample &

🖥 Buy

## TEXAS INSTRUMENTS

## DS90UB925Q-Q1

ZHCSCX8D - APRIL 2012 - REVISED OCTOBER 2014

DS90UB925Q-Q1 具有双向控制通道的 5 到 85 MHz 24 位 彩色 FPD-Link III 串行器

# 1 特性

- 具有 I<sup>2</sup>C 兼容串行控制总线的双向控制接口通道接口

- 支持高清 (720p) 数字视频格式

- 支持 RGB888 + VS, HS, DE 和 I2S 音频

- 支持两个 10 位摄像机视频流

- 支持 5 至 85MHz 并行时钟 (PCLK)

- 通过 1.8V 或 3.3V 兼容 LVCMOS I/O 接口实现

3.3V 单电源运行

- 长达 10 米的 AC 耦合生成树协议 (STP) 互连

- 并行 LVCMOS 视频输出

- 具有嵌入式时钟的直流均衡和扰频数据

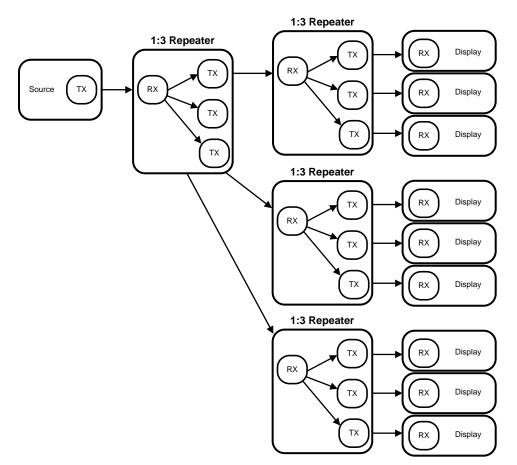

- 支持中继器应用

- 内部模式生成

- 低功率模式最大限度地减少了功率耗散

- 汽车应用级产品: 符合 AEC-Q100 2 级要求

- >8kV 人体模型 (HBM) 和 ISO 10605 静电放电 (ESD) 等级

- 向下兼容至 FPD-Link II

# 2 应用范围

- 汽车导航显示屏

- 后座娱乐系统

- 汽车驾驶员辅助系统

- 车载百万象素级摄像机系统

# 3 说明

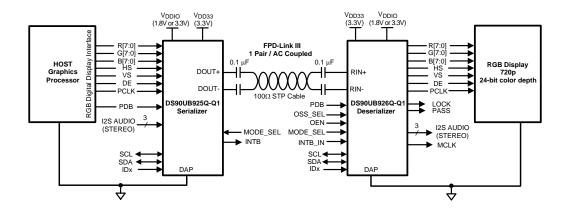

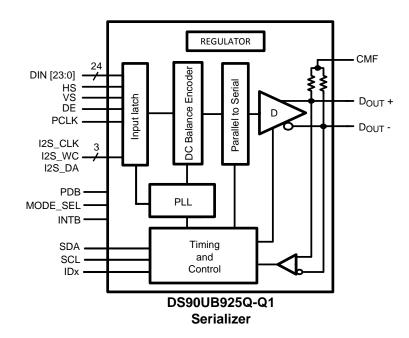

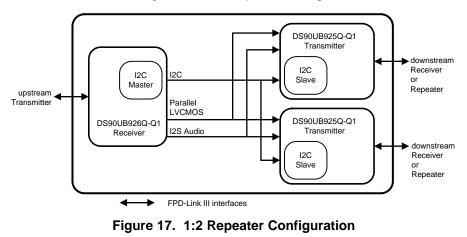

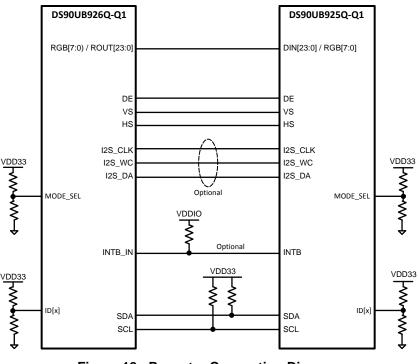

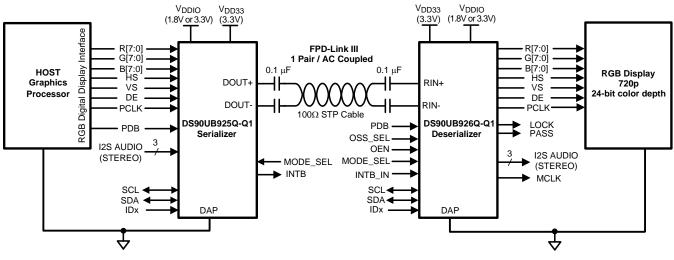

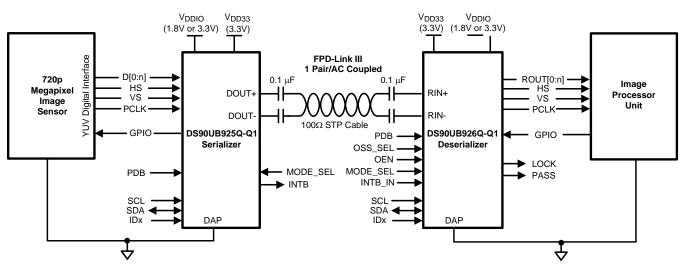

DS90UB925Q-Q1 串行器与 DS90UB926Q-Q1 解串器 相连,可提供完整的数字接口以实现汽车显示屏和图像 传感应用中高速视频、音频和控制数据的并行传输。

该芯片组非常适合高清 (HD) 格式的车载视频显示系统和具有百万象素级分辨率的车载视觉系统。

DS90UB925Q-Q1 整合了嵌入式双向控制通道和低延 迟 GPIO 控制。该芯片组将一个并行接口转换为一个 单对高速串行接口。 FPD-Link III 串行总线方案支持通 过单个差分链路实现高速视频数据传输和双向控制通信 的全双工控制。通过单个差分对整合视频数据和控制 可减少互连线尺寸和重量,同时还消除了偏差问题并简 化了系统设计。

DS90UB925Q-Q1 串行器内嵌时钟,可通过直流扰频 & 均衡数据有效载荷,并将信号电平转换为高速低压差 分信令。最多有 24 个数据位可随视频控制信号一同 串化。

串行传输通过用户可选的去加重功能进行优化。 低压 差分信令的使用、数据换序和随机生成以及展频定时兼 容性最大限度地减少了电磁干扰 (EMI)。

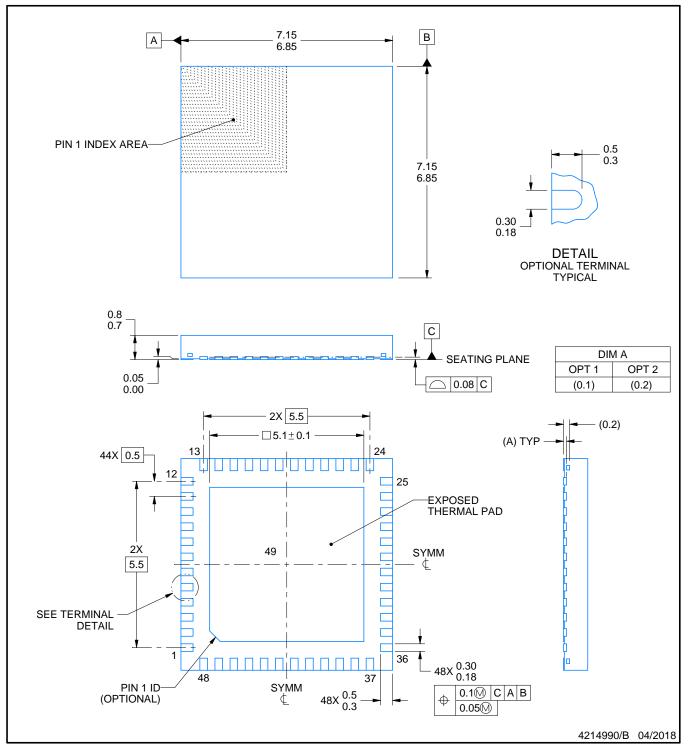

器件信息(1)

| 部件号           | 封装        | 封装尺寸(标称值)       |

|---------------|-----------|-----------------|

| DS90UB925Q-Q1 | WQFN (48) | 7.00mm x 7.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

## 目录

| 1 | 特性   |                                                  |

|---|------|--------------------------------------------------|

| 2 | 应用   | 范围1                                              |

| 3 | 说明   | 1                                                |

| 4 | 修订   | 历史记录 2                                           |

| 5 | Pin  | Configuration and Functions 4                    |

| 6 | Spe  | cifications7                                     |

|   | 6.1  | Absolute Maximum Ratings7                        |

|   | 6.2  | Handling Ratings7                                |

|   | 6.3  | Recommended Operating Conditions 7               |

|   | 6.4  | Thermal Information 8                            |

|   | 6.5  | DC Electrical Characteristics 8                  |

|   | 6.6  | AC Electrical Characteristics 10                 |

|   | 6.7  | Recommended Timing for the Serial Control Bus 11 |

|   | 6.8  | Switching Characteristics 13                     |

|   | 6.9  | Typical Charateristics 14                        |

| 7 | Deta | ailed Description 15                             |

|   | 7.1  | Overview 15                                      |

|   | 7.2  | Functional Block Diagram 15                      |

|   | 7.3  | Feature Description 15                           |

|    | 7.4  | Device Functional Modes           | 22 |

|----|------|-----------------------------------|----|

|    | 7.5  | Programming                       | 25 |

|    | 7.6  | Register Maps                     | 27 |

| 8  | Арр  | lication and Implementation       | 38 |

|    | 8.1  | Application Information           | 38 |

|    | 8.2  | Typical Application               | 38 |

| 9  | Pow  | er Supply Recommendations         | 41 |

|    | 9.1  | Power Up Requirements and PDB Pin | 41 |

|    | 9.2  | CML Interconnect Guidelines       | 41 |

| 10 | Lay  | out                               | 42 |

|    | 10.1 | Layout Guidelines                 | 42 |

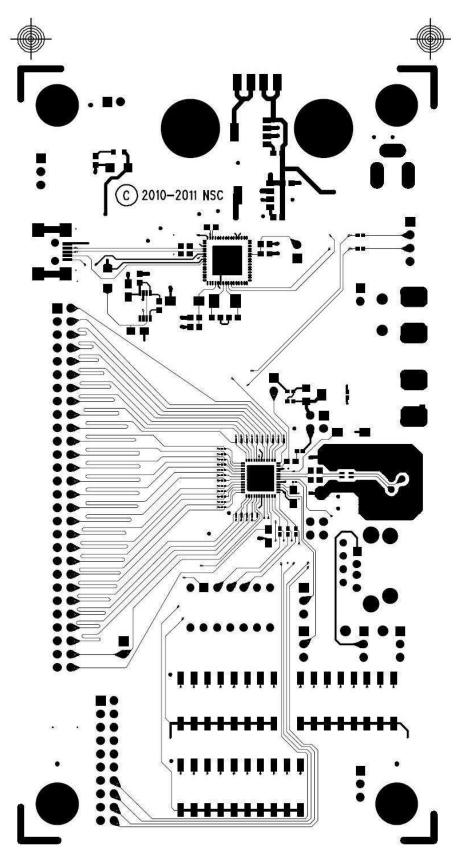

|    | 10.2 | Layout Example                    | 43 |

| 11 | 器件   | 和文档支持                             | 45 |

|    | 11.1 |                                   |    |

|    | 11.2 | 商标                                | 45 |

|    | 11.3 | 静电放电警告                            | 45 |

|    | 11.4 | 术语表                               | 45 |

| 12 | 机械   | 封装和可订购信息                          | 45 |

|    |      |                                   |    |

### 4 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision C (April 2013) to Revision D

## 已添加数据表流程和版面布局,以符合全新 TI 标准。已添加以下章节:处理额定值、器件功能模式;编程;电源建 议; 布局布线; 器件和文档支持; 机械封装和订购信息 ......1 已添加 器件信息表......1

## Changes from Revision B (August 2012) to Revision C

| • | 已更改 国家数据表布局至 TI 格式。 | <br>1 |

|---|---------------------|-------|

### Changes from Revision A (July 2012) to Revision B

| - |                                                                                                        |    |

|---|--------------------------------------------------------------------------------------------------------|----|

| • | Added typical charateristic graphics                                                                   | 14 |

|   | Added" Note: frequency range = 15 - 65MHz when LFMODE = 0 and frequency range = 5 - <15MHz when        |    |

|   | LFMODE = 1." under Functional Description.                                                             | 16 |

| • | Reformatted Table 2 and added clarification to notes                                                   | 19 |

| • | Added clarification to notes on Table 6, address 0x04[3:0] (backwards compatible and LFMODE registers) | 27 |

| Cł | hanges from Original (March 2012) to Revision A | Page |

|----|-------------------------------------------------|------|

| •  | 已转换为混合 TI 格式。                                   | 1    |

| •  | Corrected typo in SCL from pin 6 to pin 8       | 4    |

| •  | Corrected typo in SDA from pin 7 to pin 9       | 4    |

www.ti.com.cn

Page

Page

Page

2

| • | Added to Absolute Maximum Rating section, note (3): The maximum limit (V <sub>DDIO</sub> +0.3V) does not apply to the PDB pin during the transition to the power down state (PDB transitioning from HIGH to LOW) |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Deleted derate from Maximum Power Dissipation Capacity at 25°C                                                                                                                                                   |

| • | Added "Note: BIST is not available in backwards compatible mode." 20                                                                                                                                             |

| • | Corrected typo in Table 4 "I2S Channel B (18-bit Mode)" from L to H                                                                                                                                              |

| • | Corrected typo in Table 5 Ideal $V_{R2}(V)$ from 2.475 to 1.475                                                                                                                                                  |

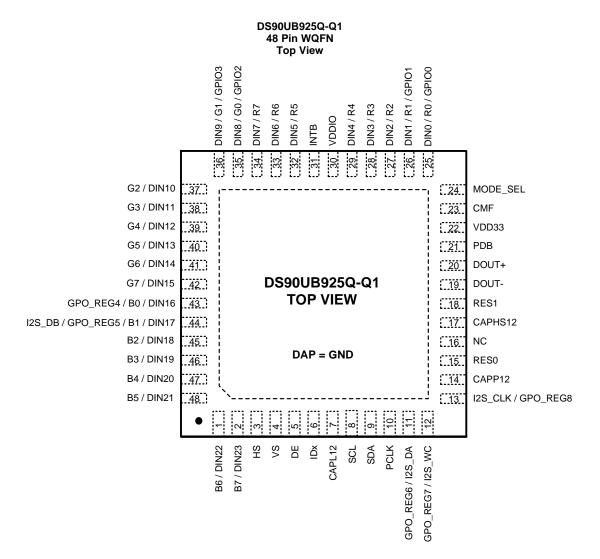

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN NAME                                    | PIN #                                                                                                                | I/O, TYPE                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LVCMOS PA                                   | VCMOS PARALLEL INTERFACE                                                                                             |                           |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| DIN[23:0] /<br>R[7:0],<br>G[7:0],<br>B[7:0] | 25, 26, 27, 28,<br>29, 32, 33, 34,<br>35, 36, 37, 38,<br>39, 40, 41, 42,<br>43, 44, 45, 46,<br>47, 48, 1, 2          | I, LVCMOS<br>w/ pull down | Parallel Interface Data Input Pins<br>Leave open if unused<br>DIN0 / R0 can optionally be used as GPIO0 and DIN1 / R1 can optionally be used as GPIO1<br>DIN8 / G0 can optionally be used as GPIO2 and DIN9 /G1 can optionally be used as GPIO3<br>DIN16 / B0 can optionally be used as GPIO4 and DIN17 / B1 can optionally be used as<br>GPIO5 |  |  |  |

| HS                                          | Control Signal Filter is enabled. There is no restriction the Control Signal Filter is disabled. The signal is limit |                           | Horizontal Sync Input Pin<br>Video control signal pulse width must be 3 PCLKs or longer to be transmitted when the<br>Control Signal Filter is enabled. There is no restriction on the minimum transition pulse when<br>the Control Signal Filter is disabled. The signal is limited to 2 transitions per 130 PCLKs.<br>See Table 6.            |  |  |  |

| VS                                          | 4                                                                                                                    | I, LVCMOS<br>w/ pull down | Vertical Sync Input Pin<br>Video control signal is limited to 1 transition per 130 PCLKs. Thus, the minimum pulse width<br>is 130 PCLKs.                                                                                                                                                                                                        |  |  |  |

# Pin Functions (continued)

| PIN NAME                      | PIN #                 | I/O, TYPE                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------|-----------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DE                            | 5                     | I, LVCMOS<br>w/ pull down   | Data Enable Input Pin<br>Video control signal pulse width must be 3 PCLKs or longer to be transmitted when the<br>Control Signal Filter is enabled. There is no restriction on the minimum transition pulse when<br>the Control Signal Filter is disabled. The signal is limited to 2 transitions per 130 PCLKs.<br>See Table 6.                   |

| PCLK                          | 10                    | I, LVCMOS<br>w/ pull down   | Pixel Clock Input Pin. Strobe edge set by RFB configuration register. See Table 6.                                                                                                                                                                                                                                                                 |

| I2S_CLK,<br>I2S_WC,<br>I2S_DA | 13, 12, 11            | I, LVCMOS<br>w/ pull down   | Digital Audio Interface Data Input Pins<br>Leave open if unused<br>I2S_CLK can optionally be used as GPO_REG8, I2S_WC can optionally be used as<br>GPO_REG7, and I2S_DA can optionally be used as GPO_REG6.                                                                                                                                        |

| OPTIONAL P                    | ARALLEL INTE          | RFACE                       |                                                                                                                                                                                                                                                                                                                                                    |

| I2S_DB                        | 44                    | I, LVCMOS<br>w/ pull down   | Second Channel Digital Audio Interface Data Input pin at 18–bit color mode and set by MODE_SEL pin or configuration register Leave open if unused I2S_DB can optionally be used as DIN17 or GPO_REG5.                                                                                                                                              |

| GPIO[3:0]                     | 36, 35, 26, 25        | I/O, LVCMOS<br>w/ pull down | General Purpose IOs. Available only in 18-bit color mode, and set by MODE_SEL pin or configuration register. See Table 6.<br>Leave open if unused.<br>Shared with DIN9, DIN8, DIN1 and DIN0                                                                                                                                                        |

| GPO_REG[<br>8:4]              | 13, 12, 11, 44,<br>43 | O, LVCMOS<br>w/ pull down   | General Purpose Outputs and set by configuration register. See Table 6.<br>Share with I2S_CLK, I2S_WC, I2S_DA, I2S_DB or DIN17, DIN16.                                                                                                                                                                                                             |

| CONTROL                       |                       |                             |                                                                                                                                                                                                                                                                                                                                                    |

| PDB                           | 21                    | I, LVCMOS<br>w/ pull-down   | Power-down Mode Input Pin<br>PDB = H, device is enabled (normal operation)<br>Refer to <i>Power Up Requirements and PDB Pin</i> section.<br>PDB = L, device is powered down.<br>When the device is in the powered down state, the Driver Outputs are both HIGH, the PLL is<br>shutdown, and IDD is minimized. Control Registers are <b>RESET</b> . |

| MODE_SEL                      | 24                    | I, Analog                   | Device Configuration Select. See Table 4.                                                                                                                                                                                                                                                                                                          |

| l <sup>2</sup> C              |                       |                             |                                                                                                                                                                                                                                                                                                                                                    |

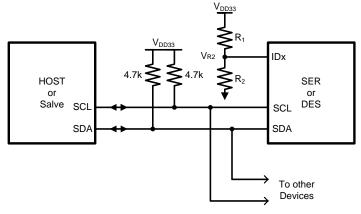

| IDx                           | 6                     | I, Analog                   | I <sup>2</sup> C Serial Control Bus Device ID Address Select<br>External pull-up to V <sub>DD33</sub> is required under all conditions, DO NOT FLOAT.<br>Connect to external pull-up and pull-down resistor to create a voltage divider. See Figure 19.                                                                                            |

| SCL                           | 8                     | I/O, LVCMOS<br>Open Drain   | $I^2C$ Clock Input / Output Interface Must have an external pull-up to V_{DD33}, DO NOT FLOAT. Recommended pull-up: 4.7k $\Omega$ .                                                                                                                                                                                                                |

| SDA                           | 9                     | I/O, LVCMOS<br>Open Drain   | $I^2C$ Data Input / Output Interface<br>Must have an external pull-up to V <sub>DD33</sub> , DO NOT FLOAT.<br>Recommended pull-up: 4.7k $\Omega$ .                                                                                                                                                                                                 |

| STATUS                        |                       |                             |                                                                                                                                                                                                                                                                                                                                                    |

| INTB                          | 31                    | O, LVCMOS<br>Open Drain     | Interrupt<br>INTB = H, normal<br>INTB = L, Interrupt request<br>Recommended pull-up: $4.7k\Omega$ to V <sub>DDIO</sub>                                                                                                                                                                                                                             |

| FPD-LINK III                  | SERIAL INTERI         | FACE                        |                                                                                                                                                                                                                                                                                                                                                    |

| DOUT+                         | 20                    | O, LVDS                     | True Output<br>The output must be AC-coupled with a 0.1µF capacitor.                                                                                                                                                                                                                                                                               |

| DOUT-                         | 19                    | O, LVDS                     | Inverting Output<br>The output must be AC-coupled with a 0.1µF capacitor.                                                                                                                                                                                                                                                                          |

| CMF                           | 23                    | Analog                      | Common Mode Filter.<br>Connect 0.1µF to GND                                                                                                                                                                                                                                                                                                        |

STRUMENTS

ÈXAS

# Pin Functions (continued)

| PIN NAME                                          | PIN #                                                                                                                                                                | I/O, TYPE | DESCRIPTION                                                                                       |  |  |  |  |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| POWER AND                                         | POWER AND GROUND <sup>(1)</sup>                                                                                                                                      |           |                                                                                                   |  |  |  |  |

| V <sub>DD33</sub>                                 | 22                                                                                                                                                                   | Power     | Power to on-chip regulator 3.0 V - 3.6 V. Requires 4.7 uF to GND                                  |  |  |  |  |

| V <sub>DDIO</sub>                                 | 30                                                                                                                                                                   | Power     | LVCMOS I/O Power 1.8 V ±5% OR 3.0 V - 3.6 V. Requires 4.7 uF to GND                               |  |  |  |  |

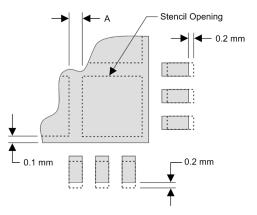

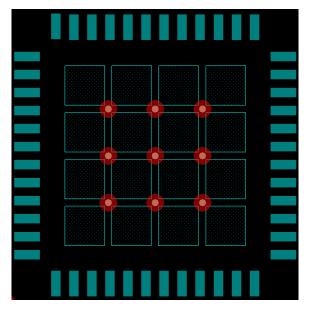

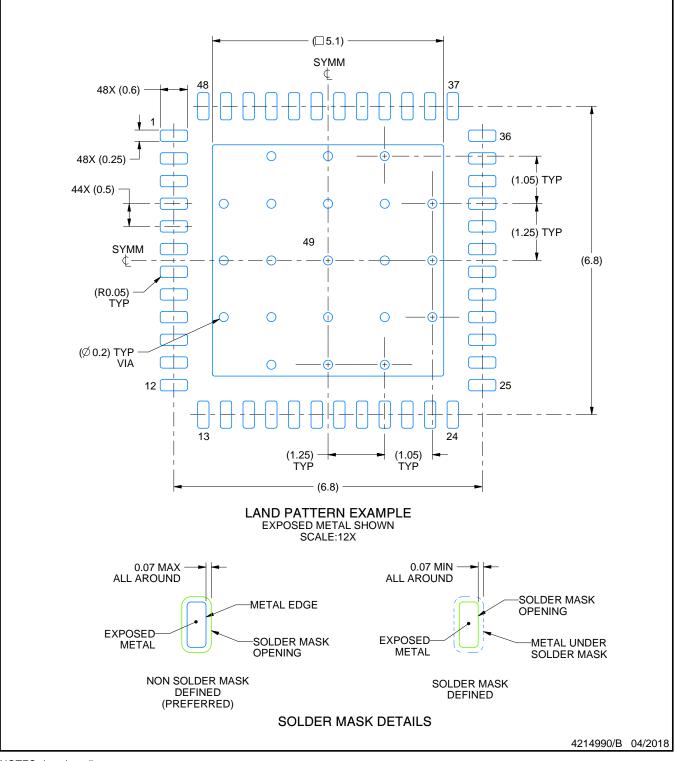

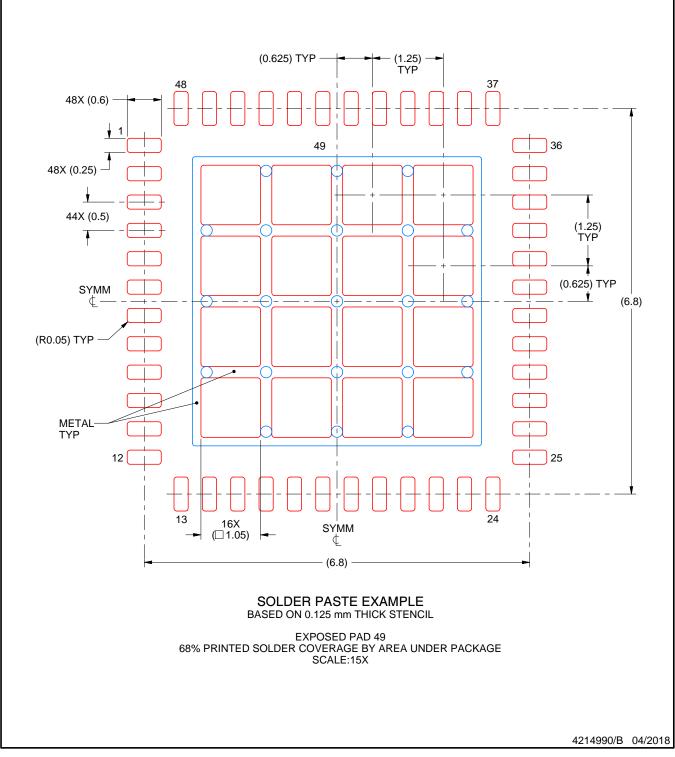

| GND                                               | GND DAP Ground DAP is the large metal contact at the bottom side, located at the center of the WQFN package. Connect to the ground plane (GND) with at least 9 vias. |           |                                                                                                   |  |  |  |  |

| REGULATO                                          | R CAPACITOR                                                                                                                                                          |           | •                                                                                                 |  |  |  |  |

| CAPHS12,<br>CAPP12                                |                                                                                                                                                                      |           |                                                                                                   |  |  |  |  |

| CAPL12 7 CAP Decoupling capacitor cor<br>CAP pin. |                                                                                                                                                                      | CAP       | Decoupling capacitor connection for on-chip regulator. Requires two 4.7uF to GND at this CAP pin. |  |  |  |  |

| OTHERS                                            |                                                                                                                                                                      |           |                                                                                                   |  |  |  |  |

| NC                                                | 16                                                                                                                                                                   | NC        | Do not connect.                                                                                   |  |  |  |  |

| RES[1:0]                                          | 18, 15                                                                                                                                                               | GND       | Reserved. Tie to Ground.                                                                          |  |  |  |  |

(1) The VDD (V\_{DD33} and V\_{DDIO}) supply ramp should be faster than 1.5 ms with a monotonic rise.

## 6 Specifications

### 6.1 Absolute Maximum Ratings <sup>(1) (2)</sup>

|                                    | MIN  | MAX                     | UNIT |

|------------------------------------|------|-------------------------|------|

| Supply Voltage – V <sub>DD33</sub> | -0.3 | +4.0                    | V    |

| Supply Voltage – V <sub>DDIO</sub> | -0.3 | +4.0                    | V    |

| LVCMOS I/O Voltage <sup>(3)</sup>  | -0.3 | V <sub>DDIO</sub> + 0.3 | V    |

| Serializer Output Voltage          | -0.3 | +2.75                   | V    |

| Junction Temperature               |      | +150                    | °C   |

(1) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(2) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

(3) The maximum limit (VDDIO +0.3V) does not apply to the PDB pin during the transition to the power down state (PDB transitioning from HIGH to LOW).

## 6.2 Handling Ratings

|                                             |                                                                     |                                                         | MIN   | MAX   | UNIT |

|---------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|-------|-------|------|

| T <sub>stg</sub>                            | Storage temperature range                                           | 9                                                       | -65   | +150  | °C   |

| V <sub>(ESD)</sub>                          |                                                                     | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±8    | ±8    | kV   |

|                                             | Electrostatic discharge                                             | Charged device model (CDM), per AEC Q100-011            | ±1.25 | ±1.25 | ĸv   |

|                                             |                                                                     | Machine Model (MM)                                      | ±250  | ±250  | V    |

| ESD Rating (IEC 61000-4-2, powered-up only) |                                                                     | Air Discharge<br>(DOUT+, DOUT-)                         | ±15   | ±15   |      |

|                                             |                                                                     | Contact Discharge<br>(DOUT+, DOUT-)                     | ±8    | ±8    | kV   |

| ESD Rating (ISO 10605)                      |                                                                     | Air Discharge<br>(DOUT+, DOUT-)                         | ±15   | ±15   | κV   |

|                                             | 0Ω, C <sub>S</sub> = 150pF/330pF<br>Ω, C <sub>S</sub> = 150pF/330pF | Contact Discharge<br>(DOUT+, DOUT-)                     | ±8    | ±8    |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

|                                                  | MIN  | NOM | MAX  | UNIT       |

|--------------------------------------------------|------|-----|------|------------|

| Supply Voltage (V <sub>DD33</sub> )              | 3.0  | 3.3 | 3.6  | V          |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> )       | 3.0  | 3.3 | 3.6  | V          |

| OR                                               |      |     |      |            |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> )       | 1.71 | 1.8 | 1.89 | V          |

| Operating Free Air Temperature (T <sub>A</sub> ) | -40  | +25 | +105 | °C         |

| PCLK Frequency                                   | 5    |     | 85   | MHz        |

| Supply Noise                                     |      |     | 100  | $mV_{P-P}$ |

INSTRUMENTS

XAS

www.ti.com.cn

### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | WQFN    |      |

|-----------------------|----------------------------------------------|---------|------|

|                       |                                              | 48 PINS | UNIT |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 35      |      |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 5.2     |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.5     | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.1     | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 5.5     |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.3     |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 DC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.<sup>(1) (2) (3)</sup>

|                  | PARAMETER                       | TEST C                                                                    | ONDITIONS                            | PIN/FREQ.                       | MIN                        | ТҮР | MAX                        | UNIT |

|------------------|---------------------------------|---------------------------------------------------------------------------|--------------------------------------|---------------------------------|----------------------------|-----|----------------------------|------|

| LVCMC            | OS I/O DC SPECIFICATION         | S                                                                         |                                      | ·                               |                            |     |                            |      |

| V <sub>IH</sub>  | High Level Input<br>Voltage     | $V_{DDIO} = 3.0 \text{ to } 3$                                            | .6V                                  |                                 | 2.0                        |     | V <sub>DDIO</sub>          | V    |

| V <sub>IL</sub>  | Low Level Input<br>Voltage      | $V_{DDIO} = 3.0 \text{ to } 3$                                            | .6V                                  | PDB                             | GND                        |     | 0.8                        | V    |

| I <sub>IN</sub>  | Input Current                   | $V_{IN} = 0V \text{ or } V_{DD}$                                          | <sub>IO</sub> = 3.0 to 3.6V          |                                 | -10                        | ±1  | +10                        | μA   |

| High Lovel Input | High Level Input                | $V_{DDIO} = 3.0$ to 3                                                     | .6V                                  |                                 | 2.0                        |     | V <sub>DDIO</sub>          | V    |

| V <sub>IH</sub>  | Voltage                         | $V_{DDIO} = 1.71$ to                                                      | 1.89V                                |                                 | 0.65*<br>V <sub>DDIO</sub> |     | V <sub>DDIO</sub>          | V    |

|                  | Low Level Input                 | $V_{DDIO} = 3.0 \text{ to } 3.6 \text{V}$                                 |                                      | DIN[23:0], HS,<br>VS, DE, PCLK, | GND                        |     | 0.8                        | V    |

| V <sub>IL</sub>  | Voltage                         | $V_{DDIO} = 1.71$ to                                                      | 1.89V                                | 12S_CLK,<br>12S_WC,             | GND                        |     | 0.35*<br>V <sub>DDIO</sub> | V    |

|                  | locut Current                   | V <sub>DDIO</sub> = 3.0 I2S_DA, I2S_DE<br>V <sub>IN</sub> = 0V or to 3.6V | 12S_DA, 12S_DB                       | -10                             | ±1                         | +10 | μA                         |      |

| I <sub>IN</sub>  | Input Current                   | V <sub>DDIO</sub>                                                         | V <sub>DDIO</sub> = 1.71<br>to 1.89V |                                 | -10                        | ±1  | +10                        | μA   |

|                  | High Level Output               | 4                                                                         | V <sub>DDIO</sub> = 3.0 to<br>3.6V   |                                 | 2.4                        |     | V <sub>DDIO</sub>          | V    |

| V <sub>OH</sub>  | Voltage                         | I <sub>OH</sub> = −4mA                                                    | V <sub>DDIO</sub> = 1.71<br>to 1.89V |                                 | V <sub>DDIO</sub> - 0.45   |     | V <sub>DDIO</sub>          | V    |

|                  | Low Level Output                |                                                                           | V <sub>DDIO</sub> = 3.0 to<br>3.6V   | GPIO[3:0],                      | GND                        |     | 0.4                        | V    |

| V <sub>OL</sub>  | Voltage                         | $I_{OL} = +4mA$                                                           | V <sub>DDIO</sub> = 1.71<br>to 1.89V | GPO_REG[8:4]                    | GND                        |     | 0.35                       | V    |

| I <sub>OS</sub>  | Output Short Circuit<br>Current | V <sub>OUT</sub> = 0V                                                     |                                      |                                 |                            | -50 |                            | mA   |

| I <sub>OZ</sub>  | TRI-STATE® Output<br>Current    | $V_{OUT} = 0V \text{ or } V_{E}$                                          | <sub>DDIO</sub> , PDB = L,           |                                 | -10                        |     | +10                        | μA   |

(1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

(2) Typical values represent most likely parametric norms at V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = +25 °C, and at the *Recommended Operating Conditions* at the time of product characterization and are not ensured.

(3) Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>, which are differential voltages.

# **DC Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified.<sup>(1) (2) (3)</sup>

|                     | PARAMETER                                                  | TEST CO                             | NDITIONS                   | PIN/FREQ.         | MIN                       | TYP                                                 | MAX                       | UNIT              |

|---------------------|------------------------------------------------------------|-------------------------------------|----------------------------|-------------------|---------------------------|-----------------------------------------------------|---------------------------|-------------------|

| FPD-LIN             | K III CML DRIVER DC SPE                                    | CIFICATIONS                         |                            |                   |                           |                                                     |                           |                   |

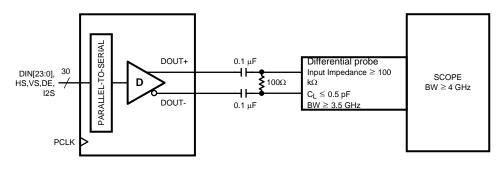

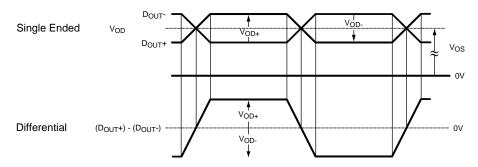

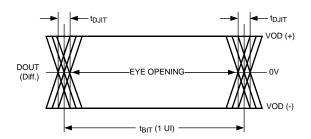

| V <sub>ODp-p</sub>  | Differential Output<br>Voltage<br>(DOUT+) – (DOUT-)        | $R_L = 100\Omega$ ,<br>See Figure 1 |                            |                   | 1160                      | 1250                                                | 1340                      | mV <sub>p-p</sub> |

| $\Delta V_{OD}$     | Output Voltage<br>Unbalance                                |                                     |                            |                   |                           | 1                                                   | 50                        | mV                |

| V <sub>OS</sub>     | Offset Voltage –<br>Single-ended                           | $R_L = 100\Omega$ ,<br>See Figure 1 |                            |                   |                           | 2.5-<br>0.25*V <sub>ODp-p</sub><br><sub>(TYP)</sub> |                           | V                 |

| ΔV <sub>OS</sub>    | Offset Voltage<br>Unbalance<br>Single-ended                |                                     |                            | — DOUT+, DOUT-    |                           | 1                                                   | 50                        | mV                |

| I <sub>OS</sub>     | Output Short Circuit<br>Current                            | DOUT+/- = 0V, P                     | DB = L or H                |                   |                           | -38                                                 |                           | mA                |

| R <sub>T</sub>      | Internal Termination<br>Resistor - Single<br>ended         |                                     |                            |                   | 40                        | 52                                                  | 62                        | Ω                 |

| SERIAL              | CONTROL BUS                                                | <u>+</u>                            |                            |                   |                           |                                                     |                           |                   |

| V <sub>IH</sub>     | Input High Level                                           | SDA and SCL                         |                            |                   | 0.7*<br>V <sub>DD33</sub> |                                                     | V <sub>DD33</sub>         | V                 |

| V <sub>IL</sub>     | Input Low Level<br>Voltage                                 | SDA and SCL                         |                            |                   | GND                       |                                                     | 0.3*<br>V <sub>DD33</sub> | V                 |

| V <sub>HY</sub>     | Input Hysteresis                                           |                                     |                            |                   |                           | >50                                                 |                           | mV                |

| V <sub>OL</sub>     |                                                            | SDA, I <sub>OL</sub> = 1.25 r       | nA                         |                   | 0                         |                                                     | 0.36                      | V                 |

| l <sub>in</sub>     |                                                            | SDA or SCL, V <sub>IN</sub>         | = V <sub>DD33</sub> or GND |                   | -10                       |                                                     | 10                        | μΑ                |

| C <sub>in</sub>     | Input Capacitance                                          | SDA or SCL                          |                            |                   |                           | <5                                                  |                           | pF                |

| SUPPLY              | CURRENT                                                    |                                     |                            |                   |                           |                                                     |                           |                   |

| I <sub>DD1</sub>    | Supply Current                                             | Checker Board                       | V <sub>DD33</sub> = 3.6V   | V <sub>DD33</sub> |                           | 148                                                 | 170                       | mA                |

|                     | (includes load current)                                    | Pattern,                            | $V_{DDIO} = 3.6V$          | N/                |                           | 90                                                  | 180                       | μA                |

| I <sub>DDIO1</sub>  | $R_L = 100\Omega$ , f = 85MHz                              | See Figure 2                        | $V_{DDIO} = 1.89V$         | V <sub>DDIO</sub> |                           | 1                                                   | 1.6                       | mA                |

| I <sub>DDS1</sub>   | Supply Current                                             | 0x01[7] = 1,                        | V <sub>DD33</sub> = 3.6V   | V <sub>DD33</sub> |                           | 1.2                                                 | 2.4                       | mA                |

|                     | Remote Auto Power deserializer is                          | $V_{DDIO} = 3.6V$                   | V <sub>DDIO</sub>          |                   | 65                        | 150                                                 | μA                        |                   |

| DDIOS1              | Down Mode                                                  | powered down                        | $V_{DDIO} = 1.89V$         | * DDIO            |                           | 55                                                  | 150                       | μA                |

| I <sub>DDS2</sub>   | PDB = L, All                                               |                                     | V <sub>DD33</sub> = 3.6V   | V <sub>DD33</sub> |                           | 1                                                   | 2                         | mA                |

|                     | Supply Current Power LVCMOS inputs<br>Down are floating or |                                     | $V_{DDIO} = 3.6V$          | V <sub>DDIO</sub> |                           | 65                                                  | 150                       | μA                |

| I <sub>DDIOS2</sub> |                                                            | tied to GND                         | $V_{DDIO} = 1.89V$         | * DDIO            |                           | 50                                                  | 150                       | μΑ                |

ZHCSCX8D-APRIL 2012-REVISED OCTOBER 2014

www.ti.com.cn

STRUMENTS

EXAS

### 6.6 AC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.<sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup>

|                   | PARAMETER                                                         | TEST CONDITIONS                           | PIN/FREQ.        | MIN   | TYP     | MAX   | UNIT |

|-------------------|-------------------------------------------------------------------|-------------------------------------------|------------------|-------|---------|-------|------|

| GPIO E            | BIT RATE                                                          |                                           |                  |       |         |       |      |

|                   | Forward Channel Bit Rate                                          |                                           | f = 5 - 85       |       | 0.25* f |       | Mbps |

| B <sub>R</sub>    | Back Channel Bit Rate                                             | See <sup>(4) (5)</sup>                    | MHz<br>GPIO[3:0] |       | 75      |       | kbps |

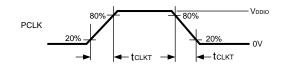

| RECO              | MMENDED TIMING FOR PCLK                                           |                                           |                  |       |         |       |      |

| t <sub>TCP</sub>  | PCLK Period                                                       |                                           |                  | 11.76 | Т       | 200   | ns   |

| t <sub>CIH</sub>  | PCLK Input High Time                                              | See <sup>(4) (5)</sup>                    | PCLK             | 0.4*T | 0.5*T   | 0.6*T | ns   |

| t <sub>CIL</sub>  | PCLK Input Low Time                                               |                                           |                  | 0.4*T | 0.5*T   | 0.6*T | ns   |

|                   | PCLK Input Transition Time,                                       |                                           | f = 5 MHz        | 4.0   |         |       | ns   |

| t <sub>CLKT</sub> | See Figure 3 <sup>(4) (5)</sup>                                   |                                           | f = 85 MHz       | 0.5   |         |       | ns   |

| t <sub>IJIT</sub> | PCLK Input Jitter Tolerance,<br>Bit Error Rate ≤10 <sup>−10</sup> | $f / 40 < Jitter Freq < f / 20^{(4)}$ (6) | f = 5 –<br>78MHz | 0.4   | 0.6     |       | UI   |

(1) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

Typical values represent most likely parametric norms at V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = +25 °C, and at the Recommended Operating Conditions at (2) the time of product characterization and are not ensured.

Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground (3) except  $V_{OD}$  and  $\Delta V_{OD}$ , which are differential voltages. Specification is ensured by characterization and is not tested in production.

(4)

Specification is ensured by design and is not tested in production. (5)

Jitter Frequency is specified in conjunction with DS90UB926 PLL bandwidth. (6)

UI - Unit Interval is equivalent to one serialized data bit width 1UI = 1 / (35\*PCLK). The UI scales with PCLK frequency. (7)

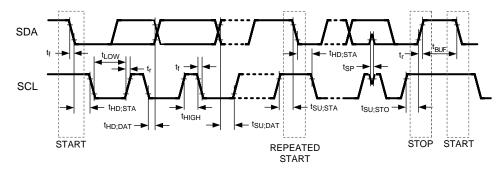

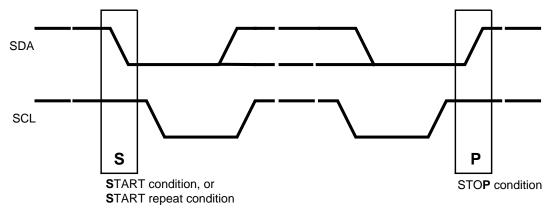

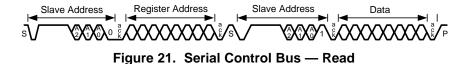

# 6.7 Recommended Timing for the Serial Control Bus

Over 3.3V supply and temperature ranges unless otherwise specified.

|                     |                                           |               | MIN | TYP   | MAX  | UNIT |

|---------------------|-------------------------------------------|---------------|-----|-------|------|------|

| f <sub>SCL</sub>    |                                           | Standard Mode | 0   |       | 100  | kHz  |

|                     | SCL Clock Frequency                       | Fast Mode     | 0   |       | 400  | kHz  |

| t <sub>LOW</sub>    | COL Law Daried                            | Standard Mode | 4.7 |       |      | μs   |

|                     | SCL Low Period                            | Fast Mode     | 1.3 |       |      | μs   |

| t <sub>HIGH</sub>   | COL Llink Daried                          | Standard Mode | 4.0 |       |      | μs   |

|                     | SCL High Period                           | Fast Mode     | 0.6 |       |      | μs   |

| t <sub>HD;STA</sub> | Hold time for a start or a                | Standard Mode | 4.0 |       |      | μs   |

|                     | repeated start condition,<br>See Figure 8 | Fast Mode     | 0.6 |       |      | μs   |

| t <sub>SU:STA</sub> | Set Up time for a start or a              | Standard Mode | 4.7 |       |      | μs   |

|                     | repeated start condition,<br>See Figure 8 | Fast Mode     | 0.6 |       |      | μs   |

| t <sub>HD;DAT</sub> | Data Hold Time,<br>See Figure 8           | Standard Mode | 0   | 0.615 | 3.45 | μs   |

| ,                   |                                           | Fast Mode     | 0   | 0.615 | 0.9  | μs   |

| t <sub>SU;DAT</sub> | Data Set Up Time,                         | Standard Mode | 250 | 0.56  |      | ns   |

|                     | See Figure 8                              | Fast Mode     | 100 | 0.56  |      | ns   |

| t <sub>SU;STO</sub> | Set Up Time for STOP                      | Standard Mode | 4.0 |       |      | μs   |

|                     | Condition,<br>See Figure 8                | Fast Mode     | 0.6 |       |      | μs   |

|                     | Bus Free Time                             | Standard Mode | 4.7 |       |      | μs   |

| t <sub>BUF</sub>    | Between STOP and START,<br>See Figure 8   | Fast Mode     | 1.3 |       |      | μs   |

|                     | SCL and SDA Rise Time,                    | Standard Mode |     | 430   | 1000 | ns   |

| t <sub>r</sub>      | See Figure 8                              | Fast Mode     |     | 430   | 300  | ns   |

|                     | SCL and SDA Fall Time,                    | Standard Mode |     | 20    | 300  | ns   |

| t <sub>f</sub>      | See Figure 8                              | Fast mode     |     | 20    | 300  | ns   |

| t <sub>sp</sub>     | input Filter                              |               |     | 50    |      | ns   |

Figure 1. Serializer V<sub>OD</sub> DC Output

Figure 2. Checkboard Data Pattern

Figure 6. Serializer Lock Time

Figure 7. Serializer CML Output Jitter

Figure 8. Serial Control Bus Timing Diagram

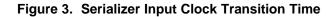

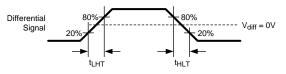

## 6.8 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                                                                                       | TEST CONDITIONS                  | TEST CONDITIONS PIN/FREQ.                                                   |     | TYP   | MAX  | UNIT |

|-------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------|-----|-------|------|------|

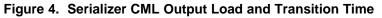

| t <sub>LHT</sub>  | CML Output Low-to-High<br>Transition Time                                                                       | See Figure 4                     | DOUT+,                                                                      |     | 80    | 130  | ps   |

| t <sub>HLT</sub>  | CML Output High-to-Low<br>Transition Time                                                                       | See Figure 4                     | DOUT-                                                                       |     | 80    | 130  | ps   |

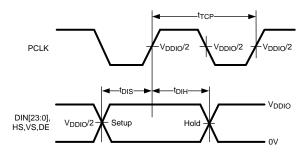

| t <sub>DIS</sub>  | Data Input Setup to PCLK                                                                                        |                                  | R[7:0],                                                                     | 2.0 |       |      | ns   |

| t <sub>DIH</sub>  | Data Input Hold from PCLK                                                                                       | See Figure 5                     | G[7:0],<br>B[7:0], HS,<br>VS, DE,<br>PCLK,<br>I2S_CLK,<br>I2S_WC,<br>I2S_DA | 2.0 |       |      | ns   |

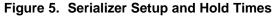

| t <sub>PLD</sub>  | Serializer PLL Lock Time                                                                                        | See Figure 6 <sup>(1)</sup>      | f = 15 -<br>45MHz                                                           |     | 131*T |      | ns   |

| t <sub>SD</sub>   | Delay — Latency                                                                                                 |                                  | f = 15 -<br>45MHz                                                           |     | 145*T |      | ns   |

| t <sub>TJIT</sub> | Output Total Jitter,<br>Bit Error Rate $\geq 10^{-10}$<br>Figure 7 <sup>(2)</sup> <sup>(3)</sup> <sup>(4)</sup> | $R_{L} = 100\Omega$<br>f = 45MHz | DOUT+,<br>DOUT-                                                             |     | 0.25  | 0.30 | UI   |

tPLD is the time required by the device to obtain lock when exiting power-down state with an active PCLK (1)

Specification is ensured by characterization and is not tested in production. (2)

Specification is ensured by design and is not tested in production.

(3) (4) UI – Unit Interval is equivalent to one serialized data bit width 1UI = 1 / (35\*PCLK). The UI scales with PCLK frequency.

#### DS90UB925Q-Q1 ZHCSCX8D – APRIL 2012–REVISED OCTOBER 2014

TEXAS INSTRUMENTS

www.ti.com.cn

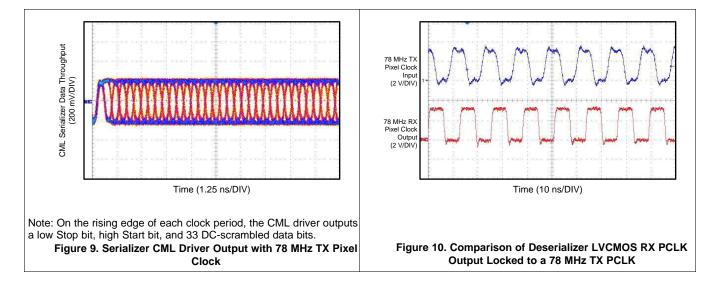

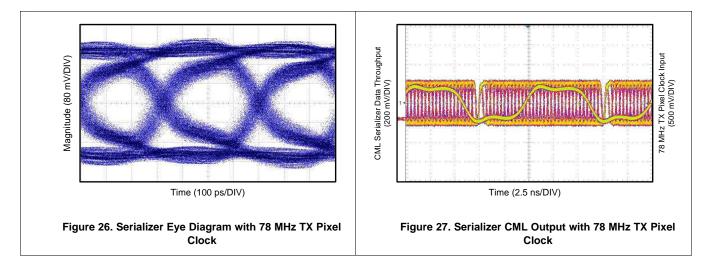

## 6.9 Typical Charateristics

# 7 Detailed Description

### 7.1 Overview

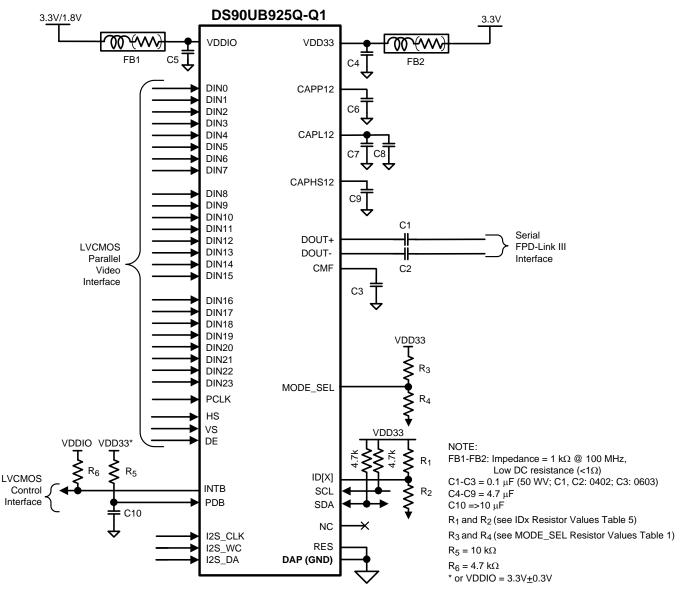

The DS90UB925Q-Q1 serializer transmits a 35-bit symbol over a single serial FPD-Link III pair operating up to 2.975 Gbps line rate. The serial stream contains an embedded clock, video control signals and DC-balanced video data and audio data which enhance signal quality to support AC coupling. The serializer is intended for use with the DS90UB926Q-Q1 deserializer, but is also backward compatible with DS90UR906Q or DS90UR908Q FPD-Link II deserializer.

The DS90UB925Q-Q1 serializer and DS90UB926Q-Q1 deserializer incorporate an I<sup>2</sup>C compatible interface. The I<sup>2</sup>C compatible interface allows programming of serializer or deserializer devices from a local host controller. In addition, the devices incorporate a bidirectional control channel (BCC) that allows communication between serializer/deserializer as well as remote I<sup>2</sup>C slave devices.

The bidirectional control channel is implemented via embedded signaling in the high-speed forward channel (serializer to deserializer) as well as lower speed signaling in the reverse channel (deserializer to serializer). Through this interface, the BCC provides a mechanism to bridge I<sup>2</sup>C transactions across the serial link from one I<sup>2</sup>C bus to another. The implementation allows for arbitration with other I<sup>2</sup>C compatible masters at either side of the serial link.

There are two operating modes available on DS90UB925Q-Q1, display mode and camera mode. In display mode,  $I^2C$  transactions originate from the host controller attached to the serializer and target either the deserializer or an  $I^2C$  slave attached to the deserializer. Transactions are detected by the  $I^2C$  slave in the serializer and forwarded to the  $I^2C$  master in the deserializer. Similarly, in camera mode,  $I^2C$  transactions originate from a controller attached to the deserializer and target either the serializer or an  $I^2C$  slave attached to the deserializer and target either the serializer or an  $I^2C$  slave attached to the deserializer and target either the serializer or an  $I^2C$  slave attached to the serializer. Transactions are detected by the  $I^2C$  slave in the deserializer and forwarded to the  $I^2C$  master in the serializer.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

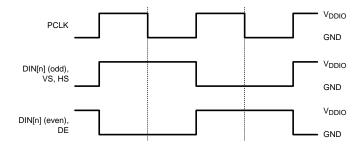

### 7.3.1 High Speed Forward Channel Data Transfer

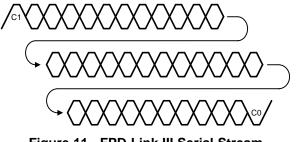

The High Speed Forward Channel (HS\_FC) is composed of 35 bits of data containing DIN[23:0] or RGB[7:0] or YUV data, sync signals, I<sup>2</sup>C, and I2S audio transmitted from Serializer to Deserializer. Figure 11 illustrates the serial stream per PCLK cycle. This data payload is optimized for signal transmission over an AC coupled link. Data is randomized, balanced and scrambled.

### **Feature Description (continued)**

Figure 11. FPD-Link III Serial Stream

The device supports clocks in the range of 5 MHz to 85 MHz. The application payload rate is 2.975 Gbps maximum (175 Mbps minimum) with the actual line rate of 2.975 Gbps maximum and 525 Mbps Minimum.

#### 7.3.2 Low Speed Back Channel Data Transfer

The Low-Speed Backward Channel (LS\_BC) of the DS90UB925Q-Q1 provides bidirectional communication between the display and host processor. The information is carried back from the Deserializer to the Serializer per serial symbol. The back channel control data is transferred over the single serial link along with the high-speed forward data, DC balance coding and embedded clock information. This architecture provides a backward path across the serial link together with a high speed forward channel. The back channel contains the I<sup>2</sup>C, CRC and 4 bits of standard GPIO information with 10 Mbps line rate.

#### 7.3.3 Backward Compatible Mode

The DS90UB925Q-Q1 is also backward compatible to DS90UR906Q and DS90UR908Q FPD Link II deserializers at 5-65 MHz of PCLK. It transmits 28-bits of data over a single serial FPD-Link II pair operating at the line rate of 140 Mbps to 1.82 Gbps. The backward configuration mode can be set via MODE\_SEL pin (Table 4) or the configuration register (Table 6). Note: frequency range = 15 - 65MHz when LFMODE = 0 and frequency range = 5 - <15MHz when LFMODE = 1.

#### 7.3.4 Common Mode Filter Pin (CMF)

The serializer provides access to the center tap of the internal termination. A capacitor must be placed on this pin for additional common-mode filtering of the differential pair. This can be useful in high noise environments for additional noise rejection capability. A 0.1  $\mu$ F capacitor must be connected to this pin to Ground.

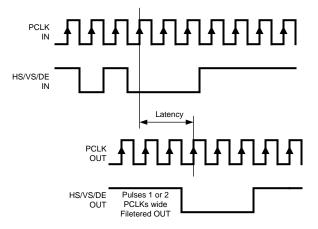

### 7.3.5 Video Control Signal Filter

When operating the devices in Normal Mode, the Video Control Signals (DE, HS, VS) have the following restrictions:

- Normal Mode with Control Signal Filter Enabled: DE and HS Only 2 transitions per 130 clock cycles are transmitted, the transition pulse must be 3 PCLK or longer.

- Normal Mode with Control Signal Filter Disabled: DE and HS Only 2 transitions per 130 clock cycles are transmitted, no restriction on minimum transition pulse.

- VS Only 1 transition per 130 clock cycles are transmitted, minimum pulse width is 130 clock cycles.

Video Control Signals are defined as low frequency signals with limited transitions. Glitches of a control signal can cause a visual display error. This feature allows for the chipset to validate and filter out any high frequency noise on the control signals. See Figure 12.

### Feature Description (continued)

Figure 12. Video Control Signal Filter Waveform

#### 7.3.6 EMI Reduction Features

#### 7.3.6.1 Input SSC Tolerance (SSCT)

The DS90UB925Q-Q1 serializer is capable of tracking a triangular input spread spectrum clocking (SSC) profile up to ±2.5% amplitude deviations (center spread), up to 35 kHz modulation at 5–85 MHz, from a host source.

### 7.3.7 LVCMOS V<sub>DDIO</sub> Option

1.8 V or 3.3 V Inputs and Outputs are powered from a separate  $V_{DDIO}$  supply to offer compatibility with external system interface signals.

#### NOTE

When configuring the  $V_{DDIO}$  power supplies, all the single-ended data and control input pins for device need to scale together with the same operating  $V_{DDIO}$  levels.

#### 7.3.8 Power Down (PDB)

The Serializer has a PDB input pin to ENABLE or POWER DOWN the device. This pin can be controlled by the host or through the V<sub>DDIO</sub>, where V<sub>DDIO</sub> = 3.0V to 3.6V or V<sub>DD33</sub>. To save power disable the link when the display is not needed (PDB = LOW). When the pin is driven by the host, make sure to release it after V<sub>DD33</sub> and V<sub>DDIO</sub> have reached final levels; no external components are required. In the case of driven by the V<sub>DDIO</sub> = 3.0V to 3.6V or V<sub>DD33</sub> directly, a 10 kohm resistor to the V<sub>DDIO</sub> = 3.0V to 3.6V or V<sub>DD33</sub>, and a >10uF capacitor to the ground are required (See Figure 23).

#### 7.3.9 Remote Auto Power Down Mode

The Serializer features a remote auto power down mode. During the power down mode of the pairing deserializer, the Serializer enters the remote auto power down mode. In this mode, the power dissipation of the Serializer is reduced significantly. When the Deserializer is powered up, the Serializer enters the normal power on mode automatically. This feature is enabled through the register bit 0x01[7] Table 6.

#### 7.3.10 Input PCLK Loss Detect

The serializer can be programmed to enter a low power SLEEP state when the input clock (PCLK) is lost. A clock loss condition is detected when PCLK drops below approximately 1MHz. When a PCLK is detected again, the serializer will then lock to the incoming PCLK. Note – when PCLK is lost, the Serial Control Bus Registers values are still RETAINED.

### Feature Description (continued)

### 7.3.11 Serial Link Fault Detect

The serial link fault detection is able to detect any of following seven (7) conditions:

- 1. cable open

- 2. "+" to "-" short

- 3. "+" short to GND

- 4. "-" short to GND

- 5. "+" short to battery

- 6. "-" short to battery

- 7. Cable is linked correctly

If any one of the fault conditions occurs, The Link Detect Status is 0 (cable is not detected) on bit 0 of address 0x0C Table 6.

### 7.3.12 Pixel Clock Edge Select (RFB)

The RFB control register bit selects which edge of the Pixel Clock is used. For the serializer, this pin determines the edge that the data is latched on. If RFB is HIGH ('1'), data is latched on the Rising edge of the PCLK. If RFB is LOW ('0'), data is latched on the Falling edge of the PCLK.

### 7.3.13 Low Frequency Optimization (LFMODE)

The LFMODE is set via register (0x04[1:0]) or MODE\_SEL Pin 24 (Table 4). It controls the operating frequency of the serializer. If LFMODE is Low (default), the PCLK frequency is between 15 MHz and 85 MHz. If LFMODE is High, the PCLK frequency is between 5 MHz and <15 MHz. Please note when the device LFMODE is changed, a PDB reset is required.

### 7.3.14 Interrupt Pin — Functional Description And Usage (INTB)

- 1. On DS90UB925, set register 0xC6[5] = 1 and 0xC6[0] = 1

- 2. DS90UB926Q-Q1 deserializer INTB\_IN (pin 16) is set LOW by some downstream device.

- 3. DS90UB925Q-Q1 serializer pulls INTB (pin 31) LOW. The signal is active low, so a LOW indicates an interrupt condition.

- 4. External controller detects INTB = LOW; to determine interrupt source, read ISR register .

- 5. A read to ISR will clear the interrupt at the DS90UB925, releasing INTB.

- 6. The external controller typically must then access the remote device to determine downstream interrupt source and clear the interrupt driving INTB\_IN. This would be when the downstream device releases the INTB\_IN (pin 16) on the DS90UB926Q-Q1. The system is now ready to return to step (1) at next falling edge of INTB\_IN.

### 7.3.15 Internal Pattern Generation

The DS90UB925Q-Q1 serializer supports the internal pattern generation feature. It allows basic testing and debugging of an integrated panel through the FPD-Link III output stream. The test patterns are simple and repetitive and allow for a quick visual verification of panel operation. As long as the device is not in power down mode, the test pattern will be displayed even if no parallel input is applied. If no PCLK is received, the test pattern can be configured to use a programmed oscillator frequency. For detailed information, refer to Application Note AN-2198 (SNLA132).

### 7.3.16 GPIO[3:0] and GPO\_REG[8:4]

In 18-bit RGB operation mode, the optional R[1:0] and G[1:0] of the DS90UB925Q-Q1 can be used as the general purpose IOs GPIO[3:0] in either forward channel (Inputs) or back channel (Outputs) application.

### 7.3.16.1 GPIO[3:0] Enable Sequence

See Table 1 for the GPIO enable sequencing.

#### Feature Description (continued)

**Step 1:** Enable the 18-bit mode either through the configuration register bit Table 6 on DS90UB925Q-Q1 only. DS90UB926Q-Q1 is automatically configured as in the 18-bit mode.

**Step 2:** To enable GPIO3 forward channel, write 0x03 to address 0x0F on DS90UB925Q-Q1, then write 0x05 to address 0x1F on DS90UB926Q-Q1.

| # | DESCRIPTION   | DEVICE        | FORWARD CHANNEL              | BACK CHANNEL                 |  |  |  |  |  |  |

|---|---------------|---------------|------------------------------|------------------------------|--|--|--|--|--|--|

| 1 | Enable 18-bit | DS90UB925Q-Q1 | 0x12 = 0x04                  | 0x12 = 0x04                  |  |  |  |  |  |  |

|   | mode          | DS90UB926Q-Q1 | Auto Load from DS90UB925Q-Q1 | Auto Load from DS90UB925Q-Q1 |  |  |  |  |  |  |

| 2 | GPIO3         | DS90UB925Q-Q1 | 0x0F = 0x03                  | 0x0F = 0x05                  |  |  |  |  |  |  |

|   |               | DS90UB926Q-Q1 | 0x1F = 0x05                  | 0x1F = 0x03                  |  |  |  |  |  |  |

| 3 | GPIO2         | DS90UB925Q-Q1 | 0x0E = 0x30                  | 0x0E = 0x50                  |  |  |  |  |  |  |

|   |               | DS90UB926Q-Q1 | 0x1E = 0x50                  | 0x1E = 0x30                  |  |  |  |  |  |  |

| 4 | GPIO1         | DS90UB925Q-Q1 | 0x0E = 0x03                  | 0x0E = 0x05                  |  |  |  |  |  |  |

|   |               | DS90UB926Q-Q1 | 0x1E = 0x05                  | 0x1E = 0x03                  |  |  |  |  |  |  |

| 5 | GPIO0         | DS90UB925Q-Q1 | 0x0D = 0x93                  | 0x0D = 0x95                  |  |  |  |  |  |  |

|   |               | DS90UB926Q-Q1 | 0x1D = 0x95                  | 0x1D = 0x93                  |  |  |  |  |  |  |

#### Table 1. GPIO Enable Sequencing Table

#### 7.3.16.2 GPO\_REG[8:4] Enable Sequence

GPO\_REG[8:4] are the outputs only pins. They must be programmed through the local register bits. See Table 2 for the GPO\_REG enable sequencing.

**Step 1:** Enable the 18-bit mode either through the configuration register bit Table 6 on DS90UB925Q-Q1 only. DS90UB926Q-Q1 is automatically configured as in the 18-bit mode.

Step 2: To enable GPO\_REG8 outputs an "1", write 0x90 to address 0x11 on DS90UB925Q.

| # | DESCRIPTION        | DEVICE        | LOCAL ACCESS | LOCAL OUTPUT |

|---|--------------------|---------------|--------------|--------------|

| 1 | Enable 18-bit mode | DS90UB925Q-Q1 | 0x12 = 0x04  |              |

| 2 | GPO_REG8           | DS90UB925Q-Q1 | 0x11 = 0x90  | "1"          |

|   |                    |               | 0x11 = 0x10  | "0"          |

| 3 | GPO_REG7           | DS90UB925Q-Q1 | 0x11 = 0x09  | "1"          |

|   |                    |               | 0x11 = 0x01  | "0"          |

| 4 | GPO_REG6           | DS90UB925Q-Q1 | 0x10 = 0x90  | "1"          |

|   |                    |               | 0x10 = 0x10  | "0"          |

| 5 | GPO_REG5           | DS90UB925Q-Q1 | 0x10 = 0x09  | "1"          |

|   |                    |               | 0x10 = 0x01  | "0"          |

| 6 | GPO_REG4           | DS90UB925Q-Q1 | 0x0F = 0x90  | "1"          |

|   |                    |               | 0x0F = 0x10  | "0"          |

Table 2. GPO\_REG Enable Sequencing Table

#### 7.3.17 I2S Transmitting

In normal 24-bit RGB operation mode, the DS90UB925Q-Q1 supports 3 bits of I2S. They are I2S\_CLK, I2S\_WC and I2S\_DA. The optionally packetized audio information can be transmitted during the video blanking (data island transport) or during active video (forward channel frame transport). Note: The bit rates of any I2S bits must maintain one fourth of the PCLK rate.

#### DS90UB925Q-Q1

ZHCSCX8D-APRIL 2012-REVISED OCTOBER 2014

#### 7.3.17.1 Secondary I2S Channel

In I2S Channel B operation mode, the secondary I2S data (I2S\_DB) can be used as the additional I2S audio in addition to the 3-bit of I2S. The I2S\_DB input must be synchronized to I2S\_CLK and aligned with I2S\_DA and I2S\_WC at the input to the serializer. This operation mode is enabled through either the MODE\_SEL pin (Table 4) or through the register bit 0x12[0] (Table 6).

Table 3 covers the range of I2S sample rates.

| SAMPLE RATE (kHz) | I2S DATA WORD SIZE (BITS) | I2S CLK (MHz) |  |  |  |  |

|-------------------|---------------------------|---------------|--|--|--|--|

| 32                | 16                        | 1.024         |  |  |  |  |

| 44.1              | 16                        | 1.411         |  |  |  |  |

| 48                | 16                        | 1.536         |  |  |  |  |

| 96                | 16                        | 3.072         |  |  |  |  |

| 192               | 16                        | 6.144         |  |  |  |  |

| 32                | 24                        | 1.536         |  |  |  |  |

| 44.1              | 24                        | 2.117         |  |  |  |  |

| 48                | 24                        | 2.304         |  |  |  |  |

| 96                | 24                        | 4.608         |  |  |  |  |

| 192               | 24                        | 9.216         |  |  |  |  |

| 32                | 32                        | 2.048         |  |  |  |  |

| 44.1              | 32                        | 2.822         |  |  |  |  |

| 48                | 32                        | 3.072         |  |  |  |  |

| 96                | 32                        | 6.144         |  |  |  |  |

| 192               | 32                        | 12.288        |  |  |  |  |

| Table 3. | Audio | Interface | Frequencies |

|----------|-------|-----------|-------------|

|----------|-------|-----------|-------------|

### 7.3.18 Built In Self Test (BIST)

An optional At-Speed Built In Self Test (BIST) feature supports the testing of the high speed serial link and the low-speed back channel. This is useful in the prototype stage, equipment production, in-system test and also for system diagnostics. Note: BIST is not available in backwards compatible mode.

### 7.3.18.1 BIST Configuration and Status

The BIST mode is enabled at the deseralizer by the Pin select (Pin 44 BISTEN and Pin 16 BISTC) or configuration register (Table 6) through the deserializer. When LFMODE = 0, the pin based configuration defaults to external PCLK or 33 MHz internal Oscillator clock (OSC) frequency. In the absence of PCLK, the user can select the desired OSC frequency (default 33 MHz or 25MHz) through the register bit. When LFMODE = 1, the pin based configuration defaults to external PCLK or 12.5MHz MHz internal Oscillator clock (OSC) frequency.

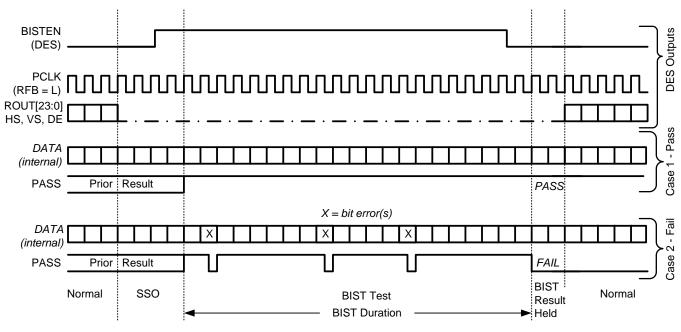

When BISTEN of the deserializer is high, the BIST mode enable information is sent to the serializer through the Back Channel. The serializer outputs a test pattern and drives the link at speed. The deserializer detects the test pattern and monitors it for errors. The PASS output pin toggles to flag any payloads that are received with 1 to 35 bit errors.

The BIST status is monitored real time on PASS pin. The result of the test is held on the PASS output until reset (new BIST test or Power Down). A high on PASS indicates NO ERRORS were detected. A Low on PASS indicates one or more errors were detected. The duration of the test is controlled by the pulse width applied to the deserializer BISTEN pin. This BIST feature also contains a Link Error Count and a Lock Status. If the connection of the serial link is broken, then the link error count is shown in the register. When the PLL of the deserializer is locked or unlocked, the lock status can be read in the register. See Table 6.

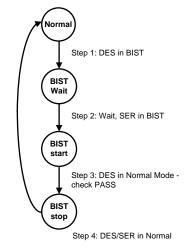

#### 7.3.18.1.1 Sample BIST Sequence

See Figure 13 for the BIST mode flow diagram.

**Step 1:** For the DS90UB925Q-Q1 and DS90UB926Q-Q1 FPD-Link III chipset, BIST Mode is enabled via the BISTEN pin of DS90UB926Q-Q1 FPD-Link III deserializer. The desired clock source is selected through BISTC pin.

**Step 2:** The DS90UB925Q-Q1 serializer is woken up through the back channel if it is not already on. The all zero pattern on the data pins is sent through the FPD-Link III to the deserializer. Once the serializer and the deserializer are in BIST mode and the deserializer acquires Lock, the PASS pin of the deserializer goes high and BIST starts checking the data stream. If an error in the payload (1 to 35) is detected, the PASS pin will switch low for one half of the clock period. During the BIST test, the PASS output can be monitored and counted to determine the payload error rate.

**Step 3:** To Stop the BIST mode, the deserializer BISTEN pin is set Low. The deserializer stops checking the data. The final test result is held on the PASS pin. If the test ran error free, the PASS output will be High. If there was one or more errors detected, the PASS output will be Low. The PASS output state is held until a new BIST is run, the device is RESET, or Powered Down. The BIST duration is user controlled by the duration of the BISTEN signal.

**Step 4:** The Link returns to normal operation after the deserializer BISTEN pin is low. Figure 14 shows the waveform diagram of a typical BIST test for two cases. Case 1 is error free, and Case 2 shows one with multiple errors. In most cases it is difficult to generate errors due to the robustness of the link (differential data transmission etc.), thus they may be introduced by greatly extending the cable length, faulting the interconnect, reducing signal condition enhancements (Rx Equalization).

Figure 13. Bist Mode Flow Diagram

### 7.3.18.2 Forward Channel And Back Channel Error Checking

While in BIST mode, the serializer stops sampling RGB input pins and switches over to an internal all-zero pattern. The internal all-zeroes pattern goes through scrambler, dc-balancing etc. and goes over the serial link to the deserializer. The deserializer on locking to the serial stream compares the recovered serial stream with all-zeroes and records any errors in status registers and dynamically indicates the status on PASS pin. The deserializer then outputs a SSO pattern on the RGB output pins.

The back-channel data is checked for CRC errors once the serializer locks onto back-channel serial stream as indicated by link detect status (register bit 0x0C[0]). The CRC errors are recorded in an 8-bit register. The register is cleared when the serializer enters the BIST mode. As soon as the serializer exits BIST mode, the functional mode CRC register starts recording the CRC errors. The BIST mode CRC error register is active in BIST mode only and keeps the record of last BIST run until cleared or enters BIST mode again.

DS90UB925Q-Q1 ZHCSCX8D – APRIL 2012 – REVISED OCTOBER 2014

www.ti.com.cn

**NSTRUMENTS**

ÈXAS

Figure 14. Bist Waveforms

### 7.4 Device Functional Modes

#### 7.4.1 Configuration Select (MODE\_SEL)

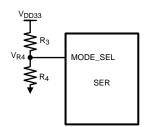

Configuration of the device may be done via the MODE\_SEL input pin, or via the configuration register bit. A pullup resistor and a pull-down resistor of suggested values may be used to set the voltage ratio of the MODE\_SEL input ( $V_{R4}$ ) and  $V_{DD33}$  to select one of the other 10 possible selected modes. See Figure 15 and Table 4.

Figure 15. MODE\_SEL Connection Diagram

### **Device Functional Modes (continued)**

|                                                        | Table 4. Configuration Select (MODE_SEL)                                                                                             |                                                                                                        |                                         |                                         |               |          |                            |                                      |  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|---------------|----------|----------------------------|--------------------------------------|--|

| #                                                      | IDEAL<br>RATIO<br>V <sub>R4</sub> /V <sub>DD33</sub>                                                                                 | ldeAl V <sub>R4</sub><br>(V)                                                                           | SUGGESTED<br>RESISTOR R3<br>kΩ (1% tol) | SUGGESTED<br>RESISTOR R4<br>kΩ (1% tol) | LFMODE        | REPEATER | BACKWARD<br>COMPATIBL<br>E | I2S Channel<br>B<br>(18–bit<br>Mode) |  |

| 1                                                      | 0                                                                                                                                    | 0                                                                                                      | Open                                    | 40.2 or Any                             | L             | L        | L                          | L                                    |  |

| 2                                                      | 0.164                                                                                                                                | 0.541                                                                                                  | 255                                     | 49.9                                    | L             | Н        | L                          | L                                    |  |