Support & training

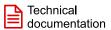

DS320PR1601 是一款 32 通道 (每个方向 16 通道)

或 x16(16 通道)低功耗高性能线性中继器或转接驱

动器,设计用于支持 PCIe 5.0、CXL 2.0、UPI 2.0 和

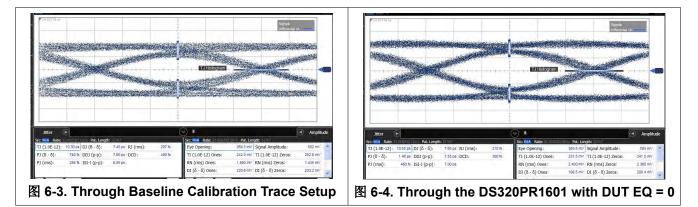

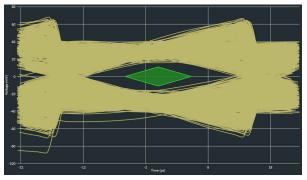

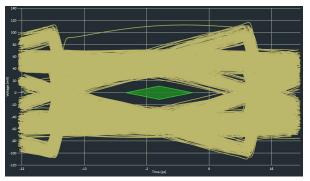

DS320PR1601 接收器部署了连续时间线性均衡器

(CTLE),用以提供可编程高频增强功能。均衡器可以

打开由于 PCB 布线等互连介质引起的码间串扰 (ISI)

而完全关闭的输入眼图。CTLE 接收器后跟一个线性输

出驱动器。DS320PR1601的线性数据路径保留了发射

预设信号特性。线性转接驱动器成为无源通道的一部

分,该通道作为一个整体进行链路训练,可获得更优发

送和接收均衡设置。对这种链路训练协议进行透明管理

可实现更优的电气链路和尽可能低的延迟。该器件具有

低通道间串扰、低附加抖动和超低的回波损耗,因此在

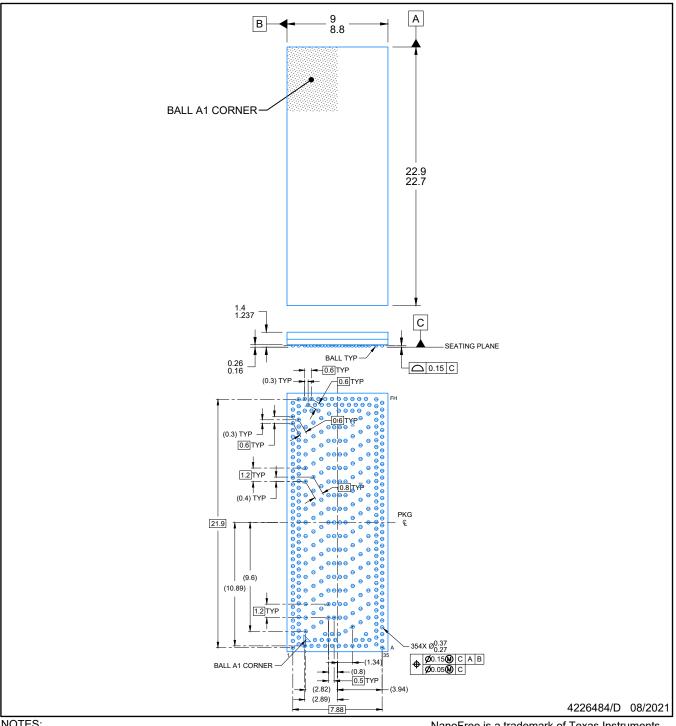

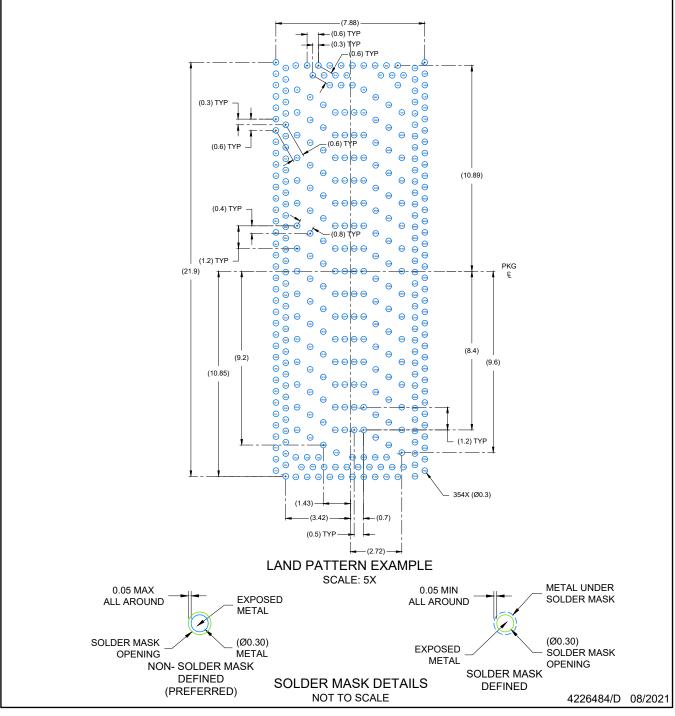

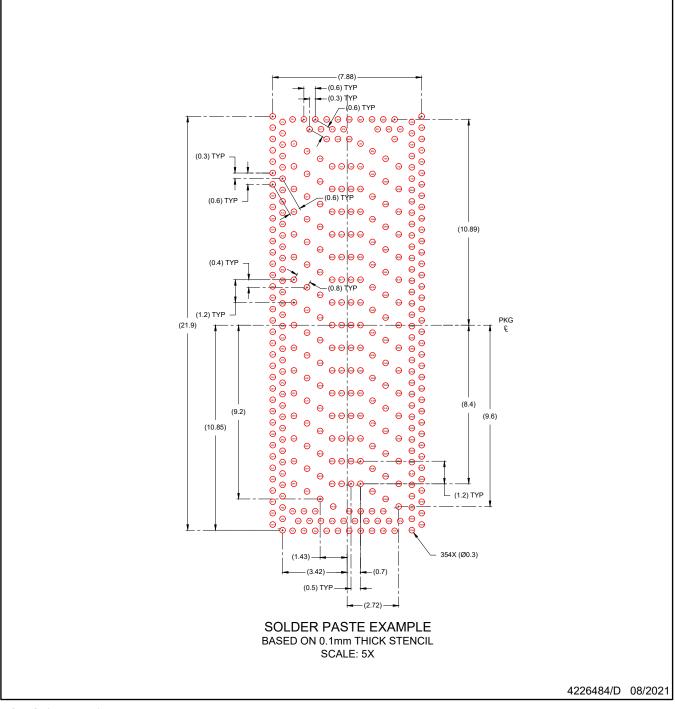

封装信息

如需了解所有可用封装,请参阅数据表末尾的可订购产品附

封装尺寸(长×宽)为标称值,并包括引脚(如适用)。

链路中几乎可用作无源元件,而又具有均衡功能。

封装<sup>(1)</sup>

ZDG (nfBGA、354)

其他接口,最高可支持 32Gbps 的传输速率。

DS320PR1601 ZHCSM45 - JUNE 2023

封装尺寸(2)

22.89 mm × 8.9 mm

# DS320PR1601 32Gbps 16 通道 PCle<sup>®</sup> 5.0、CXL 2.0 线性转接驱动器

3 说明

器件型号

DS320PR1601

录。

(1)

(2)

# 1 特性

- 支持 PCIe® 5.0、CXL 2.0、CCIX 和 UPI 2.0 的 16 通道线性转接驱动器

- 支持高达 32Gbps 的数据速率

- 与 Intel 重定时器通用封装兼容

- 封装内 Tx 引脚上有 64 个集成交流耦合电容器,可 节省布板空间

- CTLE 在 16GHz 时提升 21dB

- 130 ps 的超低延迟

- PRBS 数据的 50fs 低附加随机抖动

- 3.3V 单电源 •

- 164mW/通道的低有功功率

- I<sup>2</sup>C/SMBus 或 EEPROM 编程

- 针对 PCle 用例的自动接收器检测

- 无缝支持 PCle 链路训练

- 内部稳压器具有抗电源噪声能力

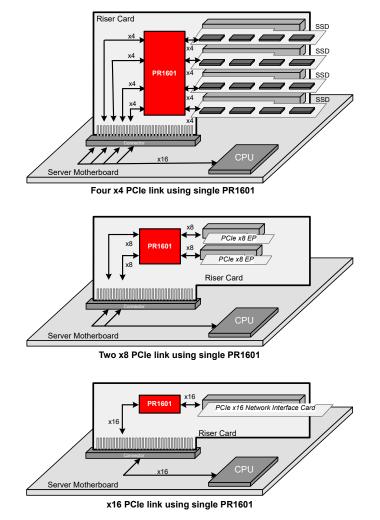

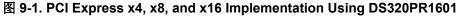

- 支持 x4、x8、x16 总线宽度

- 8.90mm × 22.80mm BGA 封装

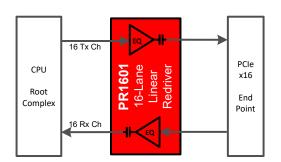

## 2 应用

- 机架式服务器、微服务器和塔式服务器

- 高性能计算

- 硬件加速器

- 网络连接存储

- 存储区域网络 (SAN) 和主机总线适配器 (HBA) 卡

- 网络接口卡 (NIC)

- 台式计算机或主板

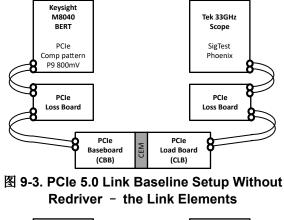

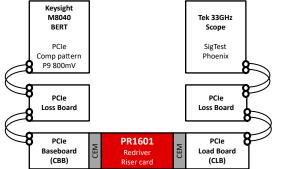

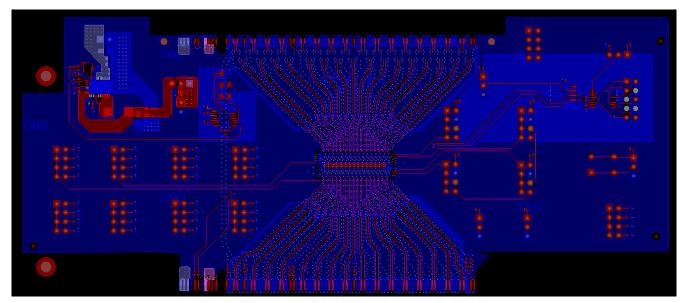

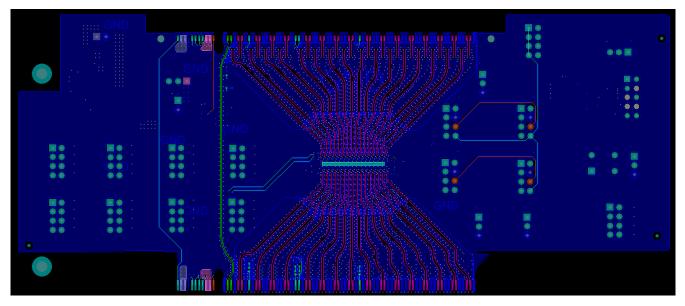

典型应用

# **Table of Contents**

| 1 | 特性                                                | 1    |

|---|---------------------------------------------------|------|

|   | 应用                                                |      |

|   | 说明                                                |      |

|   | Revision History                                  |      |

|   | Pin Configuration and Functions                   |      |

|   | Specifications                                    |      |

|   | 6.1 Absolute Maximum Ratings                      |      |

|   | 6.2 ESD and Latchup Ratings                       | .15  |

|   | 6.3 Recommended Operating Conditions              | .15  |

|   | 6.4 Thermal Information                           | .16  |

|   | 6.5 DC Electrical Characteristics                 | 16   |

|   | 6.6 High Speed Electrical Characteristics         | .17  |

|   | 6.7 SMBUS/I <sup>2</sup> C Timing Characteristics | .18  |

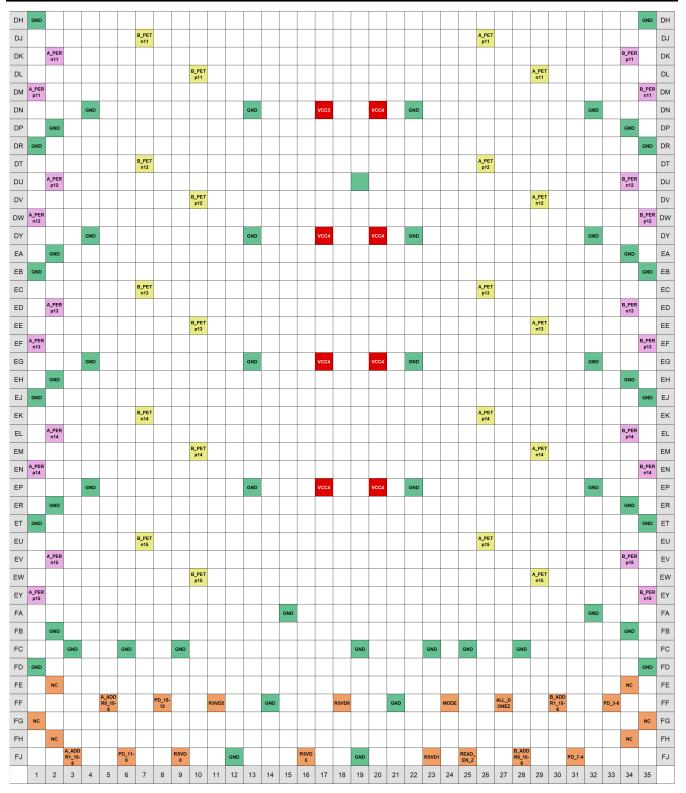

|   | 6.8 Typical Characteristics                       | .20  |

|   | 6.9 Typical Jitter Characteristics                | . 20 |

| 7 | Detailed Description                              | .21  |

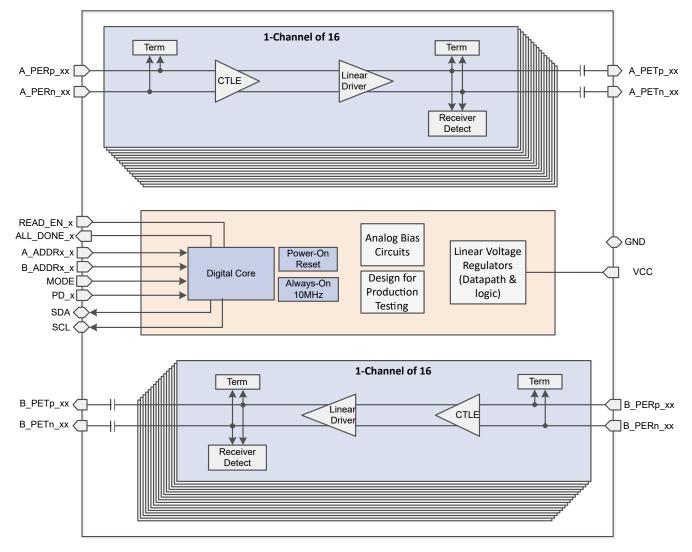

|   | 7.1 Overview                                      | .21  |

|   | 7.2 Functional Block Diagram                      | .21  |

|   | 7.3 Feature Description                           | .22  |

|   | 7.4 Device Functional Modes                       | .23  |

| 8 Programming                                            | 24              |

|----------------------------------------------------------|-----------------|

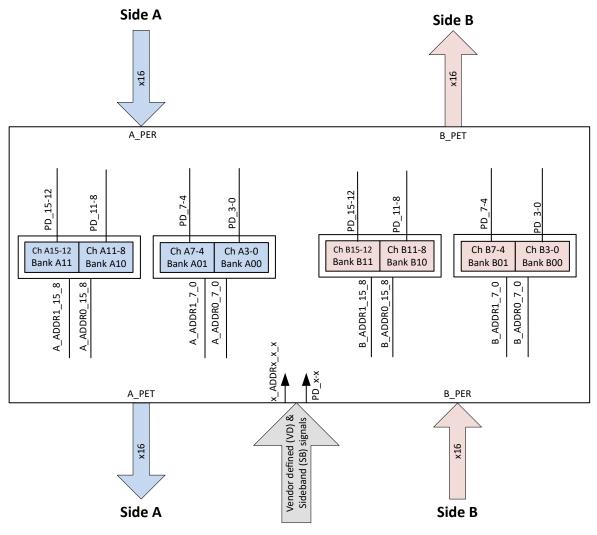

| 8.1 Pin Configurations for Lanes                         | 24              |

| 8.2 SMBUS/I <sup>2</sup> C Register Control Interface    |                 |

| 8.3 SMBus/I <sup>2</sup> C Controller Mode Configuration |                 |

| (EEPROM Self Load)                                       |                 |

| 9 Application and Implementation                         |                 |

| 9.1 Application Information                              | 30              |

| 9.2 Typical Applications                                 |                 |

| 9.3 Power Supply Recommendations                         |                 |

| 9.4 Layout                                               |                 |

| 10 Device and Documentation Support                      | <mark>36</mark> |

| 10.1 Documentation Support                               |                 |

| 10.2 接收文档更新通知                                            |                 |

| 10.3 支持资源                                                | 36              |

| 10.4 Trademarks                                          |                 |

| 10.5 静电放电警告                                              | 36              |

| 10.6 术语表                                                 |                 |

| 11 Mechanical, Packaging, and Orderable                  |                 |

| Information                                              | <mark>36</mark> |

|                                                          |                 |

# **4 Revision History**

| DATE      | REVISION | NOTES           |

|-----------|----------|-----------------|

| June 2023 | *        | Initial Release |

# **5** Pin Configuration and Functions

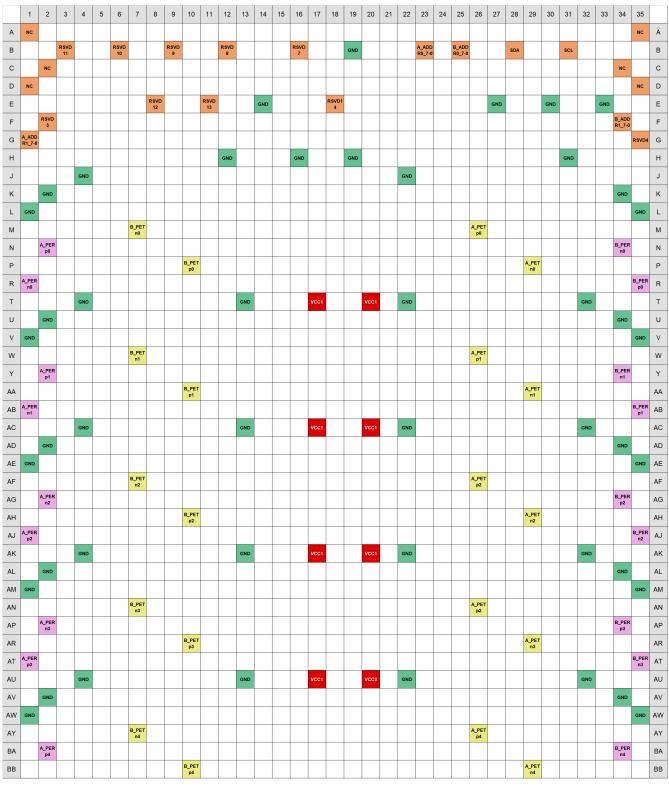

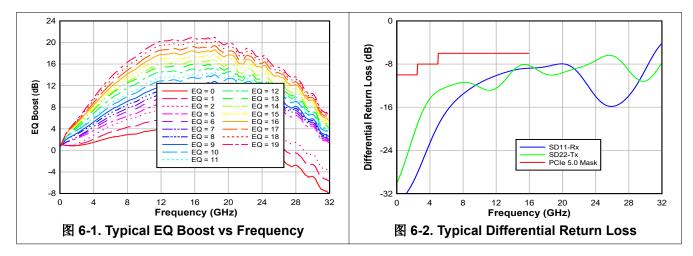

图 5-1. ZDG Package, 354-Pin BGA (Top View 1/3)

B\_PER p4 BC BC A\_PER BD GND VCC2 VCC2 GND BD GND GNE BE BE GND GND BF BF GND GNE B\_PET n5 A\_PET p5 BG BG A\_PER p5 B\_PEF n5 вн BH B\_PET p5 A\_PET n5 BJ BJ B\_PER p5 BK A\_PER BK BL BL GND GND GND GNE vcca BM BM GND BN BN GND B\_PET n6 A\_PET p6 BP BP A\_PER n6 B\_PER p6 BR BR B\_PET p6 A\_PET n6 BT BT B\_PER BU BU A\_PER BV GND GND GND BV GND BW GND GND вw BY BY GND GND CA B\_PET n7 A\_PET p7 CA A\_PER n7 B\_PER p7 СВ СВ В\_РЕТ p7 A\_PET n7 сс сс CD A\_PER B\_PER n7 CD CE GND GND CE GND VCC2 GND CF CF GND GND GND CG CG GND B\_PET n8 A\_PET p8 СН СН A\_PER p8 CJ B\_PER n8 CJ B\_PET p8 СК A\_PET n8 ск CL A\_PER n8 B\_PER p8 CL СМ vcc3 vcc3 СМ GND GND GND GND CN CN GND GND GND CP CP GND B\_PET n9 A\_PE1 p9 CR CR A\_PER p9 B\_PER n9 СТ СТ B\_PET p9 A\_PE1 n9 cu CU CV A\_PER B\_PER p9 CV cw GND GND vcca GND GND cw СҮ СҮ GND GNE DA DA GND GND B\_PET n10 A\_PE1 p10 DB DB A\_PER n10 B\_PER p10 DC DC B\_PE<sup>\*</sup> p10 A\_PE1 n10 DD DD B\_PER DE DE A\_PER p10 DF GND GND DF DG DG 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 1 2

ZHCSM45 - JUNE 2023

DS320PR1601 ZHCSM45 - JUNE 2023

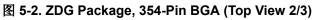

图 5-3. ZDG Package 354-Pin BGA Top View 3/3

| Legend |       |               |                    |                     |

|--------|-------|---------------|--------------------|---------------------|

| Ground | Power | IOs, RSVD /NC | Differential Input | Differential Output |

## 表 5-1. Pin Functions

| PIN |             |                   |                                                                                                                                                                                                                                                                                  |

|-----|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | TYPE              | DESCRIPTION                                                                                                                                                                                                                                                                      |

| A1  | N/C         | _                 | No internal connection.                                                                                                                                                                                                                                                          |

| A35 | N/C         | —                 | No internal connection.                                                                                                                                                                                                                                                          |

| B12 | RSVD8       | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| B16 | RSVD7       | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| B19 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| B23 | A_ADDR0_7-0 | Input             | 5-level input strap pins, as provided in 表 7-3. Sets SMBus/l <sup>2</sup> C target address, as provided in 表 8-1 and 表 8-2.                                                                                                                                                      |

| B25 | B_ADDR0_7-0 | Input             | 5-level input strap pins, as provided in 表 7-3. Sets SMBus/l^2C target address, as provided in 表 8-1 and 表 8-2.                                                                                                                                                                  |

| B28 | SDA         | Input /<br>Output | 3.3 V SMBus/l <sup>2</sup> C data IO pin SDA. External 1 k $\Omega$ to 5 k $\Omega$ pullup resistor is required as per SMBus / l <sup>2</sup> C interface standard. The device can alter between SMBus/l <sup>2</sup> C controller and target mode through exercising MODE pin.  |

| B3  | RSVD11      | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| B31 | SCL         | Input /<br>Output | 3.3 V SMBus/l <sup>2</sup> C clock IO pin SCL. External 1 k $\Omega$ to 5 k $\Omega$ pullup resistor is required as per SMBus / l <sup>2</sup> C interface standard. The device can alter between SMBus/l <sup>2</sup> C controller and target mode through exercising MODE pin. |

| B6  | RSVD10      | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| B9  | RSVD9       | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| C2  | N/C         | —                 | No internal connection.                                                                                                                                                                                                                                                          |

| C34 | N/C         | —                 | No internal connection.                                                                                                                                                                                                                                                          |

| D1  | N/C         | —                 | No internal connection.                                                                                                                                                                                                                                                          |

| D35 | N/C         | —                 | No internal connection.                                                                                                                                                                                                                                                          |

| E11 | RSVD13      | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| E14 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| E18 | RSVD14      | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| E27 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| E30 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| E33 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| E8  | RSVD12      | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| F2  | RSVD3       | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| F34 | B_ADDR1_7-0 | Input             | 5-level input strap pins, as provided in 表 7-3. Sets SMBus/l^2C target address, as provided in 表 8-1 and 表 8-2.                                                                                                                                                                  |

| G1  | A_ADDR1_7-0 | Input             | 5-level input strap pins, as provided 表 7-3. Sets SMBus/l^2C target address, as provided in 表 8-1 and 表 8-2.                                                                                                                                                                     |

| G35 | RSVD4       | —                 | Reserved for future use. No internal connection.                                                                                                                                                                                                                                 |

| H12 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| H16 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| H19 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| H31 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| J22 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| J4  | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| K2  | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| K34 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| L1  | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| L35 | GND         | Ground            | Ground                                                                                                                                                                                                                                                                           |

| M26 | A_PETp0     | Diff Output       | Differential transmit signal, side A, channel 0, positive                                                                                                                                                                                                                        |

| PIN  |         | TVDE        | 表 5-1. Pin Functions (continued)                          |

|------|---------|-------------|-----------------------------------------------------------|

| NO.  | NAME    | TYPE        | DESCRIPTION                                               |

| M7   | B_PETn0 | Diff Output | Differential transmit signal, side B, channel 0, negative |

| N2   | A_PERp0 | Diff Input  | Differential receive signal, side A, channel 0, positive  |

| N34  | B_PERn0 | Diff Input  | Differential receive signal, side B, channel 0, negative  |

| P10  | B_PETp0 | Diff Output | Differential transmit signal, side B, channel 0, positive |

| P29  | A_PETn0 | Diff Output | Differential transmit signal, side A, channel 0, negative |

| R1   | A_PERn0 | Diff Input  | Differential receive signal, side A, channel 0, negative  |

| R35  | B_PERp0 | Diff Input  | Differential receive signal, side B, channel 0, positive  |

| T13  | GND     | Ground      | Ground                                                    |

| T17  | VCC1    | Power       | 3.3 V Supply Voltage                                      |

| T20  | VCC1    | Power       | 3.3 V Supply Voltage                                      |

| T22  | GND     | Ground      | Ground                                                    |

| T32  | GND     | Ground      | Ground                                                    |

| T4   | GND     | Ground      | Ground                                                    |

| U2   | GND     | Ground      | Ground                                                    |

| U34  | GND     | Ground      | Ground                                                    |

| V1   | GND     | Ground      | Ground                                                    |

| V35  | GND     | Ground      | Ground                                                    |

| W26  | A_PETp1 | Diff Output | Differential transmit signal, side A, channel 1, positive |

| W7   | B_PETn1 | Diff Output | Differential transmit signal, side B, channel 1, negative |

| Y2   | A_PERp1 | Diff Input  | Differential receive signal, side A, channel 1, positive  |

| Y34  | B_PERn1 | Diff Input  | Differential receive signal, side B, channel 1, negative  |

| AA10 | B_PETp1 | Diff Output | Differential transmit signal, side B, channel 1, positive |

| AA29 | A_PETn1 | Diff Output | Differential transmit signal, side B, channel 1, negative |

| AB1  | A_PERn1 | Diff Input  | Differential receive signal, side A, channel 1, negative  |

| AB35 | B_PERp1 | Diff Input  | Differential receive signal, side B, channel 1, positive  |

| AC13 | GND     | Ground      | Ground                                                    |

| AC17 | VCC1    | Power       | 3.3 V Supply Voltage                                      |

| AC20 | VCC1    | Power       | 3.3 V Supply Voltage                                      |

| AC22 | GND     | Ground      | Ground                                                    |

| AC32 | GND     | Ground      | Ground                                                    |

| AC4  | GND     | Ground      | Ground                                                    |

| AD2  | GND     | Ground      | Ground                                                    |

| AD34 | GND     | Ground      | Ground                                                    |

| AE1  | GND     | Ground      | Ground                                                    |

| AE35 | GND     | Ground      | Ground                                                    |

| AF26 | A_PETp2 | Diff Output | Differential transmit signal, side A, channel 2, positive |

| AF7  | B_PETn2 | Diff Output | Differential transmit signal, side B, channel 2, negative |

| AG2  | A_PERn2 | Diff Input  | Differential receive signal, side A, channel 2, negative  |

| AG34 | B_PERp2 | Diff Input  | Differential receive signal, side B, channel 2, positive  |

| AH10 | B_PETp2 | Diff Output | Differential transmit signal, side B, channel 2, positive |

| AH29 | A_PETn2 | Diff Output | Differential transmit signal, side A, channel 2, negative |

| AJ1  | A_PERp2 | Diff Input  | Differential receive signal, side A, channel 2, positive  |

| AJ35 | B_PERn2 | Diff Input  | Differential receive signal, side B, channel 2, negative  |

| AK13 | GND     | Ground      | Ground                                                    |

|      | PIN     | TYPE        |                                                           |

|------|---------|-------------|-----------------------------------------------------------|

| NO.  | NAME    | TYPE        | DESCRIPTION                                               |

| AK17 | VCC1    | Power       | 3.3 V Supply Voltage                                      |

| AK20 | VCC1    | Power       | 3.3 V Supply Voltage                                      |

| AK22 | GND     | Ground      | Ground                                                    |

| AK32 | GND     | Ground      | Ground                                                    |

| AK4  | GND     | Ground      | Ground                                                    |

| AL2  | GND     | Ground      | Ground                                                    |

| AL34 | GND     | Ground      | Ground                                                    |

| AM1  | GND     | Ground      | Ground                                                    |

| AM35 | GND     | Ground      | Ground                                                    |

| AN26 | A_PETp3 | Diff Output | Differential transmit signal, side A, channel 3, positive |

| AN7  | B_PETn3 | Diff Output | Differential transmit signal, side B, channel 3, negative |

| AP2  | A_PERn3 | Diff Input  | Differential receive signal, side A, channel 3, negative  |

| AP34 | B_PERp3 | Diff Input  | Differential receive signal, side B, channel 3, positive  |

| AR10 | B_PETp3 | Diff Output | Differential transmit signal, side B, channel 3, positive |

| AR29 | A_PETn3 | Diff Output | Differential transmit signal, side A, channel 3, negative |

| AT1  | A_PERp3 | Diff Input  | Differential receive signal, side A, channel 3, positive  |

| AT35 | B_PERn3 | Diff Input  | Differential receive signal, side B, channel 3, negative  |

| AU13 | GND     | Ground      | Ground                                                    |

| AU17 | VCC1    | Power       | 3.3 V Supply Voltage                                      |

| AU20 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| AU22 | GND     | Ground      | Ground                                                    |

| AU32 | GND     | Ground      | Ground                                                    |

| AU4  | GND     | Ground      | Ground                                                    |

| AV2  | GND     | Ground      | Ground                                                    |

| AV34 | GND     | Ground      | Ground                                                    |

| AW1  | GND     | Ground      | Ground                                                    |

| AW35 | GND     | Ground      | Ground                                                    |

| AY26 | A_PETp4 | Diff Output | Differential transmit signal, side A, channel 4, positive |

| AY7  | B_PETn4 | Diff Output | Differential transmit signal, side B, channel 4, negative |

| BA2  | A_PERp4 | Diff Input  | Differential receive signal, side A, channel 4, positive  |

| BA34 | B_PERn4 | Diff Input  | Differential receive signal, side B, channel 4, negative  |

| BB10 | B_PETp4 | Diff Output | Differential transmit signal, side B, channel 4, positive |

| BB29 | A_PETn4 | Diff Output | Differential transmit signal, side A, channel 4, negative |

| BC1  | A_PERn4 | Diff Input  | Differential receive signal, side A, channel 4, negative  |

| BC35 | B_PERp4 | Diff Input  | Differential receive signal, side B, channel 4, positive  |

| BD13 | GND     | Ground      | Ground                                                    |

| BD17 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| BD20 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| BD22 | GND     | Ground      | Ground                                                    |

| BD32 | GND     | Ground      | Ground                                                    |

| BD4  | GND     | Ground      | Ground                                                    |

| BE2  | GND     | Ground      | Ground                                                    |

| BE34 | GND     | Ground      | Ground                                                    |

| BF1  | GND     | Ground      | Ground                                                    |

| PIN  |         | -           |                                                           |

|------|---------|-------------|-----------------------------------------------------------|

| NO.  | NAME    | TYPE        | DESCRIPTION                                               |

| BF35 | GND     | Ground      | Ground                                                    |

| BG26 | A_PETp5 | Diff Output | Differential transmit signal, side A, channel 5, positive |

| BG7  | B_PETn5 | Diff Output | Differential transmit signal, side B, channel 5, negative |

| BH2  | A_PERp5 | Diff Input  | Differential receive signal, side A, channel 5, positive  |

| BH34 | B_PERn5 | Diff Input  | Differential receive signal, side B, channel 5, negative  |

| BJ10 | B_PETp5 | Diff Output | Differential transmit signal, side B, channel 5, positive |

| BJ29 | A_PETn5 | Diff Output | Differential transmit signal, side A, channel 5, negative |

| BK1  | A_PERn5 | Diff Input  | Differential receive signal, side A, channel 5, negative  |

| BK35 | B_PERp5 | Diff Input  | Differential receive signal, side B, channel 5, positive  |

| BL13 | GND     | Ground      | Ground                                                    |

| BL17 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| BL20 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| BL22 | GND     | Ground      | Ground                                                    |

| BL32 | GND     | Ground      | Ground                                                    |

| BL4  | GND     | Ground      | Ground                                                    |

| BM2  | GND     | Ground      | Ground                                                    |

| BM34 | GND     | Ground      | Ground                                                    |

| BN1  | GND     | Ground      | Ground                                                    |

| BN35 | GND     | Ground      | Ground                                                    |

| BP26 | A_PETp6 | Diff Output | Differential transmit signal, side A, channel 6, positive |

| BP7  | B_PETn6 | Diff Output | Differential transmit signal, side B, channel 6, negative |

| BR2  | A_PERn6 | Diff Input  | Differential receive signal, side A, channel 6, negative  |

| BR34 | B_PERp6 | Diff Input  | Differential receive signal, side B, channel 6, positive  |

| BT10 | B_PETp6 | Diff Output | Differential transmit signal, side B, channel 6, positive |

| BT29 | A_PETn6 | Diff Output | Differential transmit signal, side A, channel 6, negative |

| BU1  | A_PERp6 | Diff Input  | Differential receive signal, side A, channel 6, positive  |

| BU35 | B_PERn6 | Diff Input  | Differential receive signal, side B, channel 6, negative  |

| BV13 | GND     | Ground      | Ground                                                    |

| BV17 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| BV20 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| BV22 | GND     | Ground      | Ground                                                    |

| BV32 | GND     | Ground      | Ground                                                    |

| BV4  | GND     | Ground      | Ground                                                    |

| BW2  | GND     | Ground      | Ground                                                    |

| BW34 | GND     | Ground      | Ground                                                    |

| BY1  | GND     | Ground      | Ground                                                    |

| BY35 | GND     | Ground      | Ground                                                    |

| CA26 | A_PETp7 | Diff Output | Differential transmit signal, side A, channel 7, positive |

| CA7  | B_PETn7 | Diff Output | Differential transmit signal, side B, channel 7, negative |

| CB2  | A_PERn7 | Diff Input  | Differential receive signal, side A, channel 7, negative  |

| CB34 | B_PERp7 | Diff Input  | Differential receive signal, side B, channel 7, positive  |

| CC10 | B_PETp7 | Diff Output | Differential transmit signal, side B, channel 7, positive |

| CC29 | A_PETn7 | Diff Output | Differential transmit signal, side A, channel 7, negative |

| CD1  | A_PERp7 | Diff Input  | Differential receive signal, side A, channel 7, positive  |

|      | PIN     |             |                                                           |

|------|---------|-------------|-----------------------------------------------------------|

| NO.  | NAME    | TYPE        | DESCRIPTION                                               |

| CD35 | B_PERn7 | Diff Input  | Differential receive signal, side B, channel 7, negative  |

| CE13 | GND     | Ground      | Ground                                                    |

| CE17 | VCC2    | Power       | 3.3 V Supply Voltage                                      |

| CE20 | VCC3    | Power       | 3.3 V Supply Voltage                                      |

| CE22 | GND     | Ground      | Ground                                                    |

| CE32 | GND     | Ground      | Ground                                                    |

| CE4  | GND     | Ground      | Ground                                                    |

| CF2  | GND     | Ground      | Ground                                                    |

| CF34 | GND     | Ground      | Ground                                                    |

| CG1  | GND     | Ground      | Ground                                                    |

| CG35 | GND     | Ground      | Ground                                                    |

| CH26 | A_PETp8 | Diff Output | Differential transmit signal, side A, channel 8, positive |

| CH7  | B_PETn8 | Diff Output | Differential transmit signal, side B, channel 8, negative |

| CJ2  | A_PERp8 | Diff Input  | Differential receive signal, side A, channel 8, positive  |

| CJ34 | B_PERn8 | Diff Input  | Differential receive signal, side B, channel 8, negative  |

| CK10 | B_PETp8 | Diff Output | Differential transmit signal, side B, channel 8, positive |

| CK29 | A_PETn8 | Diff Output | Differential transmit signal, side A, channel 8, negative |

| CL1  | A_PERn8 | Diff Input  | Differential receive signal, side A, channel 8, negative  |

| CL35 | B_PERp8 | Diff Input  | Differential receive signal, side B, channel 8, positive  |

| CM13 | GND     | Ground      | Ground                                                    |

| CM17 | VCC3    | Power       | 3.3 V Supply Voltage                                      |

| CM20 | VCC3    | Power       | 3.3 V Supply Voltage                                      |

| CM22 | GND     | Ground      | Ground                                                    |

| CM32 | GND     | Ground      | Ground                                                    |

| CM4  | GND     | Ground      | Ground                                                    |

| CN2  | GND     | Ground      | Ground                                                    |

| CN34 | GND     | Ground      | Ground                                                    |

| CP1  | GND     | Ground      | Ground                                                    |

| CP35 | GND     | Ground      | Ground                                                    |

| CR26 | A_PETp9 | Diff Output | Differential transmit signal, side A, channel 9, positive |

| CR7  | B_PETn9 | Diff Output | Differential transmit signal, side B, channel 9, negative |

| CT2  | A_PERp9 | Diff Input  | Differential receive signal, side A, channel 9, positive  |

| CT34 | B_PERn9 | Diff Input  | Differential receive signal, side B, channel 9, negative  |

| CU10 | B_PETp9 | Diff Output | Differential transmit signal, side B, channel 9, positive |

| CU29 | A_PETn9 | Diff Output | Differential transmit signal, side A, channel 9, negative |

| CV1  | A_PERn9 | Diff Input  | Differential receive signal, side A, channel 9, negative  |

| CV35 | B_PERp9 | Diff Input  | Differential receive signal, side B, channel 9, positive  |

| CW13 | GND     | Ground      | Ground                                                    |

| CW17 | VCC3    | Power       | 3.3 V Supply Voltage                                      |

| CW20 | VCC3    | Power       | 3.3 V Supply Voltage                                      |

| CW22 | GND     | Ground      | Ground                                                    |

| CW32 | GND     | Ground      | Ground                                                    |

| CW4  | GND     | Ground      | Ground                                                    |

| CY2  | GND     | Ground      | Ground                                                    |

| PIN  |          |             |                                                            |

|------|----------|-------------|------------------------------------------------------------|

| NO.  | NAME     | TYPE        | DESCRIPTION                                                |

| CY34 | GND      | Ground      | Ground                                                     |

| DA1  | GND      | Ground      | Ground                                                     |

| DA35 | GND      | Ground      | Ground                                                     |

| DB26 | A_PETp10 | Diff Output | Differential transmit signal, side A, channel 10, positive |

| DB7  | B_PETn10 | Diff Output | Differential transmit signal, side B, channel 10, negative |

| DC2  | A_PERn10 | Diff Input  | Differential receive signal, side A, channel 10, negative  |

| DC34 | B_PERp10 | Diff Input  | Differential receive signal, side B, channel 10, positive  |

| DD10 | B_PETp10 | Diff Output | Differential transmit signal, side B, channel 10, positive |

| DD29 | A_PETn10 | Diff Output | Differential transmit signal, side A, channel 10, negative |

| DE1  | A_PERp10 | Diff Input  | Differential receive signal, side A, channel 10, positive  |

| DE35 | B_PERn10 | Diff Input  | Differential receive signal, side B, channel 10, negative  |

| DF13 | GND      | Ground      | Ground                                                     |

| DF17 | VCC3     | Power       | 3.3 V Supply Voltage                                       |

| DF20 | VCC3     | Power       | 3.3 V Supply Voltage                                       |

| DF22 | GND      | Ground      | Ground                                                     |

| DF32 | GND      | Ground      | Ground                                                     |

| DF4  | GND      | Ground      | Ground                                                     |

| DG2  | GND      | Ground      | Ground                                                     |

| DG34 | GND      | Ground      | Ground                                                     |

| DH1  | GND      | Ground      | Ground                                                     |

| DH35 | GND      | Ground      | Ground                                                     |

| DJ26 | A_PETp11 | Diff Output | Differential transmit signal, side A, channel 11, positive |

| DJ7  | B_PETn11 | Diff Output | Differential transmit signal, side B, channel 11, negative |

| DK2  | A_PERn11 | Diff Input  | Differential receive signal, side A, channel 11, negative  |

| DK34 | B_PERp11 | Diff Input  | Differential receive signal, side B, channel 11, positive  |

| DL10 | B_PETp11 | Diff Output | Differential transmit signal, side B, channel 11, positive |

| DL29 | A_PETn11 | Diff Output | Differential transmit signal, side A, channel 11, negative |

| DM1  | A_PERp11 | Diff Input  | Differential receive signal, side A, channel 11, positive  |

| DM35 | B_PERn11 | Diff Input  | Differential receive signal, side B, channel 11, negative  |

| DN13 | GND      | Ground      | Ground                                                     |

| DN17 | VCC3     | Power       | 3.3 V Supply Voltage                                       |

| DN20 | VCC4     | Power       | 3.3 V Supply Voltage                                       |

| DN22 | GND      | Ground      | Ground                                                     |

| DN32 | GND      | Ground      | Ground                                                     |

| DN4  | GND      | Ground      | Ground                                                     |

| DP2  | GND      | Ground      | Ground                                                     |

| DP34 | GND      | Ground      | Ground                                                     |

| DR1  | GND      | Ground      | Ground                                                     |

| DR35 | GND      | Ground      | Ground                                                     |

| DT26 | A_PETp12 | Diff Output | Differential transmit signal, side A, channel 12, positive |

| DT7  | B_PETn12 | Diff Output | Differential transmit signal, side B, channel 12, negative |

| DU2  | A_PERp12 | Diff Input  | Differential receive signal, side A, channel 12, positive  |

| DU34 | B_PERn12 | Diff Input  | Differential receive signal, side B, channel 12, negative  |

| DV10 | B_PETp12 | Diff Output | Differential transmit signal, side B, channel 12, positive |

Copyright © 2023 Texas Instruments Incorporated

|      | PIN      | TYPE        | DECODIDATION                                               |

|------|----------|-------------|------------------------------------------------------------|

| NO.  | NAME     | TYPE        | DESCRIPTION                                                |

| DV29 | A_PETn12 | Diff Output | Differential transmit signal, side A, channel 12, negative |

| DW1  | A_PERn12 | Diff Input  | Differential receive signal, side A, channel 12, negative  |

| DW35 | B_PERp12 | Diff Input  | Differential receive signal, side B, channel 12, positive  |

| DY13 | GND      | Ground      | Ground                                                     |

| DY17 | VCC4     | Power       | 3.3 V Supply Voltage                                       |

| DY20 | VCC4     | Power       | 3.3 V Supply Voltage                                       |

| DY22 | GND      | Ground      | Ground                                                     |

| DY32 | GND      | Ground      | Ground                                                     |

| DY4  | GND      | Ground      | Ground                                                     |

| EA2  | GND      | Ground      | Ground                                                     |

| EA34 | GND      | Ground      | Ground                                                     |

| EB1  | GND      | Ground      | Ground                                                     |

| EB35 | GND      | Ground      | Ground                                                     |

| EC26 | A_PETp13 | Diff Output | Differential transmit signal, side A, channel 13, positive |

| EC7  | B_PETn13 | Diff Output | Differential transmit signal, side B, channel 13, negative |

| ED2  | A_PERp13 | Diff Input  | Differential receive signal, side A, channel 13, positive  |

| ED34 | B_PERn13 | Diff Input  | Differential receive signal, side B, channel 13, negative  |

| EE10 | B_PETp13 | Diff Output | Differential transmit signal, side B, channel 13, positive |

| EE29 | A_PETn13 | Diff Output | Differential transmit signal, side A, channel 13, negative |

| EF1  | A_PERn13 | Diff Input  | Differential receive signal, side A, channel 13, negative  |

| EF35 | B_PERp13 | Diff Input  | Differential receive signal, side B, channel 13, positive  |

| EG13 | GND      | Ground      | Ground                                                     |

| EG17 | VCC4     | Power       | 3.3 V Supply Voltage                                       |

| EG20 | VCC4     | Power       | 3.3 V Supply Voltage                                       |

| EG22 | GND      | Ground      | Ground                                                     |

| EG32 | GND      | Ground      | Ground                                                     |

| EG4  | GND      | Ground      | Ground                                                     |

| EH2  | GND      | Ground      | Ground                                                     |

| EH34 | GND      | Ground      | Ground                                                     |

| EJ1  | GND      | Ground      | Ground                                                     |

| EJ35 | GND      | Ground      | Ground                                                     |

| EK26 | A_PETp14 | Diff Output | Differential transmit signal, side A, channel 14, positive |

| EK7  | B_PETn14 | Diff Output | Differential transmit signal, side B, channel 14, negative |

| EL2  | A_PERn14 | Diff Input  | Differential receive signal, side A, channel 14, negative  |

| EL34 | B_PERp14 | Diff Input  | Differential receive signal, side B, channel 14, positive  |

| EM10 | B_PETp14 | Diff Output | Differential transmit signal, side B, channel 14, positive |

| EM29 | A_PETn14 | Diff Output | Differential transmit signal, side A, channel 14, negative |

| EN1  | A_PERp14 | Diff Input  | Differential receive signal, side A, channel 14, positive  |

| EN35 | B_PERn14 | Diff Input  | Differential receive signal, side B, channel 14, negative  |

| EP13 | GND      | Ground      | Ground                                                     |

| EP17 | VCC4     | Power       | 3.3 V Supply Voltage                                       |

| EP20 | VCC4     | Power       | 3.3 V Supply Voltage                                       |

| EP22 | GND      | Ground      | Ground                                                     |

| EP32 | GND      | Ground      | Ground                                                     |

| PIN  |          | TVDE        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.  | NAME     | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EP4  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ER2  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ER34 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ET1  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ET35 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EU26 | A_PETp15 | Diff Output | Differential transmit signal, side A, channel 15, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EU7  | B_PETn15 | Diff Output | Differential transmit signal, side B, channel 15, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EV2  | A_PERn15 | Diff Input  | Differential receive signal, side A, channel 15, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EV34 | B_PERp15 | Diff Input  | Differential receive signal, side B, channel 15, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EW10 | B_PETp15 | Diff Output | Differential transmit signal, side B, channel 15, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EW29 | A_PETn15 | Diff Output | Differential transmit signal, side A, channel 15, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EY1  | A_PERp15 | Diff Input  | Differential receive signal, side A, channel 15, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EY35 | B_PERn15 | Diff Input  | Differential receive signal, side B, channel 15, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FA15 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FA32 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FB2  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FB34 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FC19 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FC23 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FC25 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FC28 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FC3  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FC6  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FC9  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FD1  | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FD35 | GND      | Ground      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FE2  | N/C      | _           | No internal connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |