DAC7551-Q1

ZHCS226B - JUNE 2011 - REVISED MARCH 2015

# DAC7551-Q1 12 位、超低毛刺脉冲、电压输出 数模转换器

### 特性

- 符合汽车应用要求

- 相对精度 (INL): ±0.35 LSB

- 超低毛刺脉冲能量: 0.1nV-s

- 低功耗运行: 2.7V 时为 100µA

- 上电复位为零量程

- 电源: 2.7V 至 5.5V 单一电源

- 断电: 2.7V 时为 0.05µA

- 12 位线性和单调性

- 轨到轨电压输出

- 稳定时间: 5µs(最大)

- 具有施密特触发输入的 SPI 兼容串行接口: 高达 50MHz

- 菊花链功能

- 异步硬件清除为零量程

- 特定温度范围: -40°C 至 +105°C

- 小型 2mm x 3mm 12 引脚 USON 封装

- 名称带Z后缀的器件改善了分层现象

### 2 应用

- 便携式电池供电仪器

- 数字增益和偏移调整

- 可编程电压源和电流源

- 可编程衰减器

- 工业过程控制

- ADAS 雷达应用

- 碰撞预警

- 盲点检测

### 3 说明

DAC7551-Q1 器件是一款单通道电压输出数模转换器 (DAC),它具有优异的线性和单调性,并且采用一种专 有架构 可以最大限度减小毛刺脉冲能量。 DAC7551-Q1 器件功耗很低,可通过 2.7V 到 5.5V 的单电源供电 运行。 DAC7551-Q1 输出放大器可驱动 2kΩ、200pF 的轨到轨负载,稳定时间仅为5µs。 其输出范围通过 外部电压基准进行设置。

3 线串行接口可以高达 50MHz 的时钟速率运行且与 SPITM, QSPITM、microwire 和 DSP 接口标准兼容。 该器件集成有上电复位 (POR) 电路, 可确保在器件发 生有效写入周期之前,将 DAC 输出电压保持为 OV, 其包含的断电功能可使器件的电流消耗降至 2uA 以 下。

DAC7551-Q1 器件体积小,功耗低,是电池供电便携 式应用的理想选择。 其功耗典型值在 5V 时为 0.5mW, 在 3V 时为

0.23mW, 在断电模式下降至 1μW。

DAC7551-Q1 器件采用 12 引脚 USON 封装,额定工 作温度范围为 -40℃ 到 +105℃。 名称带有 Z 后缀的 器件与标准器件相比,分层现象有所减少。

### 器件信息(1)

| 器件型号       | 封装        | 封装尺寸 (标称值)      |

|------------|-----------|-----------------|

| DAC7551-Q1 | USON (12) | 2.00mm x 3.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

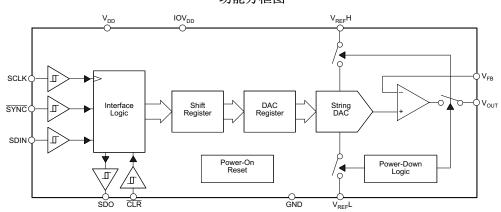

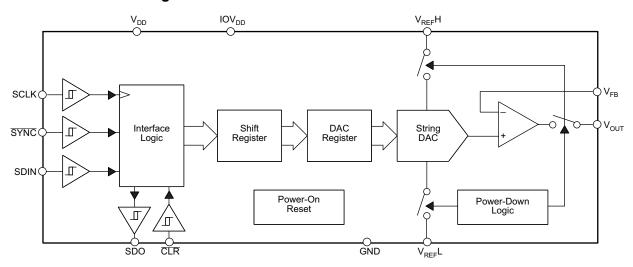

#### 功能方框图

|   | 目表                                   | 录 |    |                    |                      |    |

|---|--------------------------------------|---|----|--------------------|----------------------|----|

| 1 | 特性1                                  |   |    | 7.3 Feature        | e Description        | 11 |

| 2 | 应用 1                                 |   |    | 7.4 Device         | Functional Modes     | 13 |

| 3 | 说明1                                  |   |    | 7.5 Progran        | mming                | 14 |

| 4 | 修订历史记录 2                             |   | 8  | <b>Application</b> | n and Implementation | 15 |

| 5 | Pin Configuration and Functions      |   |    | 8.1 Applicat       | tion Information     | 15 |

| 6 | Specifications                       |   |    | 8.2 Typical        | Application          | 16 |

| U | 6.1 Absolute Maximum Ratings         |   | 9  | Power Supp         | ply Recommendations. | 17 |

|   | 6.2 ESD Ratings                      |   | 10 | Layout             |                      | 18 |

|   | 6.3 Recommended Operating Conditions |   |    | 10.1 Layout        | t Guidelines         | 18 |

|   | 6.4 Thermal Information              |   |    | 10.2 Layout        | t Example            | 18 |

|   | 6.5 Electrical Characteristics       |   | 11 | 器件和文档              | 支持                   | 19 |

|   | 6.6 Timing Requirements              |   |    | 11.1 文档支           | 7持                   | 19 |

|   | 6.7 Typical Characteristics          |   |    | 11.2 商标            |                      | 19 |

| 7 | Detailed Description                 |   |    | 11.3 静电放           | 文电警告                 | 19 |

|   | 7.1 Overview 11                      |   |    | 11.4 术语表           | ₹                    | 19 |

|   | 7.2 Functional Block Diagram         |   | 12 | 机械封装和              | 可订购信息                | 19 |

# 4 修订历史记录

| Changes               | from Revision A (February 2015) to Revision B                                                                               | Page |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| <ul><li>己添加</li></ul> | TADAS 雷达、碰撞预警和盲点检测至应用列表                                                                                                     | 1    |

| • Chang               | ged the thermal information values for the DRN (USON) package in the Thermal Information table                              | 4    |

|                       |                                                                                                                             |      |

| Changes               | from Original (June 2011) to Revision A                                                                                     | Page |

| <ul><li>己添加</li></ul> | from Original (June 2011) to Revision A  I ESD 额定值表、建议运行条件表、特性描述部分、器件功能模式部分、应用和实施部分、电源相关建议部分、 II 分、器件和文档支持部分以及机械、封装和可订购信息部分 |      |

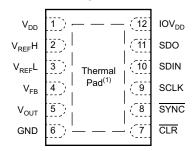

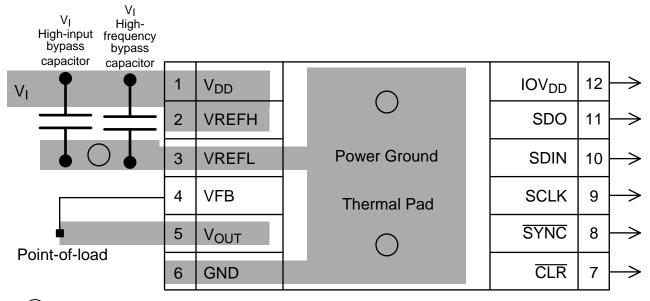

# 5 Pin Configuration and Functions

#### DRN Package 12-Pin USON With Exposed Thermal Pad Top View

(1) The thermal pad should be connected to GND.

#### **Pin Functions**

| PIN |                    | 1/0 | DESCRIPTION                                                                                                                                                |

|-----|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME               | 1/0 | DESCRIPTION                                                                                                                                                |

| 1   | $V_{DD}$           | I   | Analog voltage supply input                                                                                                                                |

| 2   | V <sub>REF</sub> H | I   | Positive reference voltage input                                                                                                                           |

| 3   | V <sub>REF</sub> L | I   | Negative reference voltage input                                                                                                                           |

| 4   | $V_{FB}$           | I   | DAC amplifier sense input.                                                                                                                                 |

| 5   | V <sub>OUT</sub>   | 0   | Analog output voltage from DAC                                                                                                                             |

| 6   | GND                | _   | Ground.                                                                                                                                                    |

| 7   | CLR                | I   | Asynchronous input to clear the DAC registers. When the $\overline{\text{CLR}}$ pin is low, the DAC register is set to 000h and the output voltage to 0 V. |

| 8   | SYNC               | ı   | Frame synchronization input. The falling edge of the SYNC pulse indicates the start of a serial data frame shifted out to the DAC7551-Q1 device.           |

| 9   | SCLK               | I   | Serial clock input                                                                                                                                         |

| 10  | SDIN               | I   | Serial data input                                                                                                                                          |

| 11  | SDO                | 0   | Serial data output                                                                                                                                         |

| 12  | IOV <sub>DD</sub>  | I   | I/O voltage supply input                                                                                                                                   |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted). (1)

|                                          | MIN                               | MAX            | UNIT |

|------------------------------------------|-----------------------------------|----------------|------|

| $V_{DD}$ , $IOV_{DD}$ to $GND$           | -0.3                              | 6              | V    |

| Digital input voltage to GND             | -0.3                              | $V_{DD} + 0.3$ | V    |

| V <sub>OUT</sub> to GND                  | -0.3                              | $V_{DD} + 0.3$ | V    |

| Operating temperature range              | -40                               | 105            | °C   |

| Junction temperature, T <sub>J</sub> max |                                   | 150            | °C   |

| Power dissipation (DRN)                  | $(T_J max - T_A) / R_{\theta JA}$ |                |      |

| Storage temperature, T <sub>stg</sub>    | -65                               | 150            | °C   |

<sup>(1)</sup> Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                          |                                                         |                               | VALUE | UNIT |

|--------------------|--------------------------|---------------------------------------------------------|-------------------------------|-------|------|

|                    |                          | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                               | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge  | 01 11 1 11 (0011) 450                                   | All pins                      | ±500  | V    |

| V (ESD)            | Licotrostatio disoriarge | Charged-device model (CDM), per AEC Q100-011            | Corner pins (1, 6, 7, and 12) | ±750  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|         |                                |                    | MIN  | NOM | MAX        | UNIT |

|---------|--------------------------------|--------------------|------|-----|------------|------|

|         |                                | $V_{DD}$           | 2.7  |     | 5.5        |      |

|         |                                | $V_{REF}H$         | 0.25 |     | $V_{DD}$   |      |

|         |                                | V <sub>REF</sub> L | 0    | GND | $V_{DD}$   |      |

|         |                                | $V_{FB}$           | 0    |     | $V_{DD}$   |      |

| $V_{I}$ | Input voltage                  | IOV <sub>DD</sub>  | 1.8  |     | $V_{DD}$   | V    |

|         |                                | CLR                | 0    |     | $IOV_{DD}$ |      |

|         |                                | SYNC               | 0    |     | $IOV_{DD}$ |      |

|         |                                | SCLK               | 0    |     | $IOV_{DD}$ |      |

|         |                                | SDIN               | 0    |     | $IOV_DD$   |      |

| V       | Output voltage                 | SDO                | 0    |     | $IOV_{DD}$ | V    |

| Vo      | Output voltage                 | V <sub>OUT</sub>   | 0    |     | $V_{DD}$   | V    |

| $T_{J}$ | Operating junction temperature | ·                  |      | ·   | 150        | °C   |

#### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | DRN (USON)<br>12 PINS | UNIT  |

|-----------------------|----------------------------------------------|-----------------------|-------|

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 49.8                  |       |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 45.8                  |       |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 18.2                  | 9C/M/ |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.8                   | °C/W  |

| ΨЈВ                   | Junction-to-board characterization parameter | 18.3                  |       |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.9                   |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

all specifications at -40°C to +105°C,  $V_{DD} = 2.7$  to 5.5 V,  $V_{REF}H = V_{DD}$ ,  $V_{REF}L = GND$ ,  $R_L = 2$  k $\Omega$  to GND, and  $C_L = 200$  pF to GND (unless otherwise noted).

| PARAMETER                         | TEST CONDITIONS                   | MIN | TYP   | MAX   | UNIT             |  |  |

|-----------------------------------|-----------------------------------|-----|-------|-------|------------------|--|--|

| STATIC PERFORMANCE <sup>(1)</sup> | STATIC PERFORMANCE <sup>(1)</sup> |     |       |       |                  |  |  |

| Resolution                        |                                   | 12  |       |       | Bits             |  |  |

| Relative accuracy                 |                                   |     | ±0.35 | ±1    | LSB              |  |  |

| Differential nonlinearity         | Specified monotonic by design     |     | ±0.08 | ±0.5  | LSB              |  |  |

| Offset error                      |                                   |     |       | ±12   | mV               |  |  |

| Zero-scale error                  | All zeroes loaded to DAC register |     |       | ±12   | mV               |  |  |

| Gain error                        |                                   |     |       | ±0.15 | %FSR             |  |  |

| Full-scale error                  |                                   |     |       | ±0.5  | %FSR             |  |  |

| Zero-scale error drift            |                                   |     | 7     |       | μV/°C            |  |  |

| Gain temperature coefficient      |                                   |     | 3     |       | ppm of<br>FSR/°C |  |  |

<sup>(1)</sup> Linearity tested using a reduced code range of 30 to 4065; output unloaded.

### **Electrical Characteristics (continued)**

all specifications at –40°C to +105°C,  $V_{DD}$  = 2.7 to 5.5 V,  $V_{REF}H = V_{DD}$ ,  $V_{REF}L = GND$ ,  $R_L = 2 \text{ k}\Omega$  to GND, and  $C_L = 200 \text{ pF}$  to GND (unless otherwise noted).

|                   | PARAME                            | TER                                     | TEST CONDITIONS                                                               | MIN                       | TYP  | MAX                      | UNIT               |

|-------------------|-----------------------------------|-----------------------------------------|-------------------------------------------------------------------------------|---------------------------|------|--------------------------|--------------------|

| PSRR              | Power-supply rejecti              | on ratio                                | $V_{DD} = 5 V$                                                                |                           | 0.75 |                          | mV/V               |

| OUTPU             | T CHARACTERISTIC                  | S <sup>(2)</sup>                        |                                                                               |                           |      |                          |                    |

|                   | Output voltage range              | е                                       |                                                                               | 2 ×<br>V <sub>REF</sub> L |      | $V_{REF}H$               | V                  |

|                   | Output voltage settlii            | ng time                                 | $R_L = 2 \text{ k}\Omega, 0 \text{ pF} < C_L < 200 \text{ pF}$                |                           |      | 5                        | μs                 |

|                   | Slew rate                         |                                         |                                                                               |                           | 1.8  |                          | V/µs               |

|                   | Canacitive land stab              | :114.                                   | R <sub>L</sub> = ∞                                                            |                           | 470  |                          | pF                 |

|                   | Capacitive load stability         |                                         | $R_L = 2 \text{ k}\Omega$                                                     |                           | 1000 |                          | þг                 |

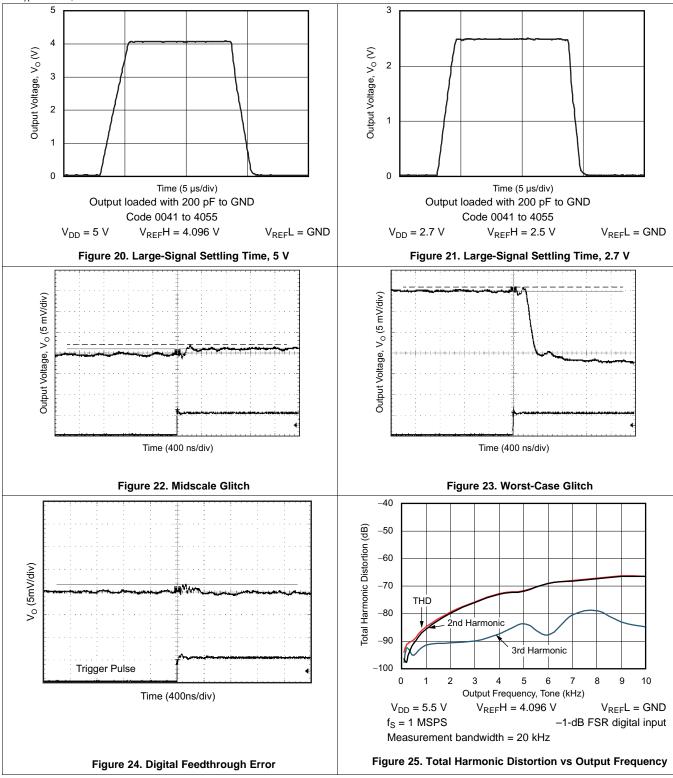

|                   | Digital-to-analog glite           | ch impulse                              | 1 LSB change around major carry                                               |                           | 0.1  |                          | nV-s               |

|                   | Digital feedthrough               |                                         |                                                                               |                           | 0.1  |                          | nV-s               |

|                   | Output noise density              | 1                                       | 10kHz offset frequency                                                        |                           | 120  |                          | nV/√ <del>Hz</del> |

| ΓHD               | Total harmonic disto              | rtion                                   | $f_{OUT} = 1 \text{ kHz}, f_{S} = 1 \text{ MSPS}, BW = 20 \text{ kHz}$        |                           | -85  |                          | dB                 |

|                   | DC output impedance               | ce                                      |                                                                               |                           | 1    |                          | Ω                  |

|                   | Short-circuit current             |                                         | $V_{DD} = 5 \text{ V}$                                                        |                           | 50   |                          | mA                 |

|                   | Short-circuit current             |                                         | $V_{DD} = 3 \text{ V}$                                                        |                           | 20   |                          | IIIA               |

|                   | Dower up time                     |                                         | Coming out of power-down mode, $V_{DD} = 5 \text{ V}$                         |                           | 15   |                          |                    |

|                   | Power-up time                     |                                         | Coming out of power-down mode, $V_{DD} = 3 \text{ V}$                         |                           | 15   |                          | μs                 |

| REFER             | ENCE INPUT                        |                                         |                                                                               | ·                         |      | •                        |                    |

|                   | V <sub>REF</sub> H input range    |                                         |                                                                               | 0                         |      | $V_{DD}$                 | V                  |

|                   | V <sub>REF</sub> L input range    |                                         | $V_{REF}L < V_{REF}H$                                                         | 0                         | GND  | $V_{DD}$                 | V                  |

|                   | Reference input imp               | edance                                  |                                                                               |                           | 100  |                          | kΩ                 |

|                   | Deference ourrent                 |                                         | $V_{REF} = V_{DD} = 5 \text{ V}$                                              |                           | 50   | 100                      |                    |

|                   | Reference current                 |                                         | $V_{REF} = V_{DD} = 3 \text{ V}$                                              |                           | 30   | 60                       | μΑ                 |

| LOGIC             | INPUTS <sup>(2)</sup>             |                                         |                                                                               |                           |      |                          |                    |

|                   | Input current                     |                                         |                                                                               |                           |      | ±1                       | μΑ                 |

| V <sub>IN_L</sub> | Input low voltage                 |                                         | IOV <sub>DD</sub> ≥ 2.7 V                                                     |                           |      | 0.3<br>IOV <sub>DD</sub> | V                  |

| V <sub>IN_H</sub> | Input high voltage                |                                         | $IOV_{DD} \ge 2.7 \text{ V}$                                                  | 0.7<br>IOV <sub>DD</sub>  |      |                          | V                  |

|                   | Pin capacitance                   |                                         |                                                                               |                           |      | 3                        | pF                 |

| POWER             | REQUIREMENTS                      |                                         |                                                                               |                           |      |                          |                    |

| / <sub>DD</sub>   | Supply voltage                    |                                         |                                                                               | 2.7                       |      | 5.5                      | V                  |

| $OV_{DD}$         | I/O supply voltage (3)            |                                         |                                                                               | 1.8                       |      | $V_{DD}$                 | V                  |

|                   |                                   | Normal operation                        | $V_{DD} = 3.6 \text{ to } 5.5 \text{ V}, \ V_{IH} = IOV_{DD}, \ V_{IL} = GND$ |                           | 150  | 200                      |                    |

| DD                | Supply current <sup>(4)</sup>     | (DAC active and excluding load current) | $V_{DD}$ = 2.7 to 3.6 V, $V_{IH}$ = IOV $_{DD},V_{IL}$ = GND                  |                           | 100  | 150                      | μA                 |

| טט                | Supply current                    | A.I                                     | $V_{DD}$ = 3.6 to 5.5 V, $V_{IH}$ = $IOV_{DD}$ , $V_{IL}$ = $GND$             |                           | 0.2  | 2                        |                    |

|                   |                                   | All power-down modes                    | $V_{DD}$ = 2.7 to 3.6 V, $V_{IH}$ = $IOV_{DD}$ , $V_{IL}$ = $GND$             |                           | 0.05 | 2                        | μA                 |

| POWER EFFICIENCY  |                                   |                                         |                                                                               |                           |      |                          |                    |

|                   | I <sub>OUT</sub> /I <sub>DD</sub> |                                         | $I_{LOAD} = 2 \text{ mA}, V_{DD} = 5 \text{ V}$                               |                           | 93%  |                          |                    |

| ЕМРЕ              | RATURE RANGE                      |                                         |                                                                               | ,                         |      | 11                       |                    |

|                   | Specified performan               | ce                                      |                                                                               | -40                       |      | 105                      | °C                 |

Specified by design and characterization; not production tested. For 1.8 V < IOV\_DD < 2.7 V, TI recommends that  $V_{IH} \ge 0.8 \ IOV_{DD}$ , and  $V_{IL} \le 0.2 \; IOV_{DD}$ . IOV poperates down to 1.8 V with slightly degraded timing, as long as  $V_{IH} \ge 0.8 \; IOV_{DD}$  and  $V_{IL} \le 0.2 \; IOV_{DD}$ . IoD tested with digital input code = 0032.

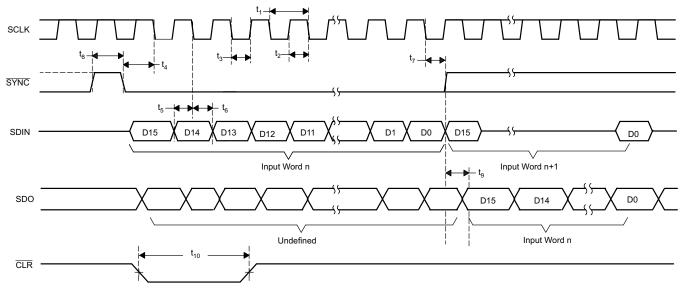

# 6.6 Timing Requirements(1)

All specifications at  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $V_{DD}$  = 2.7 to 5.5 V, and  $R_{L}$  = 2 k $\Omega$  to GND (unless otherwise noted). See Figure 1.

|                               |                                                   |                                            | MIN | MAX                         | UNIT |

|-------------------------------|---------------------------------------------------|--------------------------------------------|-----|-----------------------------|------|

| ± (2)                         | CCLIV aviale time                                 | V <sub>DD</sub> = 2.7 V to 3.6 V           | 20  |                             |      |

| t <sub>1</sub> <sup>(2)</sup> | SCLK cycle time                                   | V <sub>DD</sub> = 3.6 V to 5.5 V           | 20  |                             | ns   |

|                               | SCL K HIGH time                                   | V <sub>DD</sub> = 2.7 V to 3.6 V           | 6.5 |                             |      |

| t <sub>2</sub>                | SCLK HIGH time                                    | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 6.5 |                             | ns   |

|                               | SCLK LOW time                                     | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 6.5 |                             |      |

| t <sub>3</sub>                | SCLK LOW time                                     | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 6.5 |                             | ns   |

|                               | CVNC falling adds to CCLK falling adds saturation | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 4   |                             |      |

| t <sub>4</sub>                | SYNC falling edge to SCLK falling edge setup time | V <sub>DD</sub> = 3.6 V to 5.5 V           | 4   |                             | ns   |

|                               | Data action times                                 | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 3   |                             |      |

| t <sub>5</sub>                | Data setup time                                   | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 3   |                             | ns   |

|                               | Data hald time                                    | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 3   |                             |      |

| t <sub>6</sub>                | Data hold time                                    | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 3   |                             | ns   |

|                               | CCL // falling adge to CVNC vision adge           | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 0   | $t_1 - 10 \text{ ns}^{(3)}$ |      |

| t <sub>7</sub>                | SCLK falling edge to SYNC rising edge             | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 0   | $t_1 - 10 \text{ ns}^{(3)}$ | ns   |

| +                             | Minimum SYNC HIGH time                            | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 20  |                             | no   |

| t <sub>8</sub>                | Millimum STNC HIGH time                           | $V_{DD} = 3.6 \text{ V to } 5.5 \text{ V}$ | 20  |                             | ns   |

|                               | SCLK falling adge to SDO valid                    | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ | 10  |                             | no   |

| t <sub>9</sub>                | SCLK falling edge to SDO valid                    | V <sub>DD</sub> = 3.6 V to 5.5 V           | 10  |                             | ns   |

|                               | CLP pulse width low                               | V <sub>DD</sub> = 2.7 V to 3.6 V           | 10  |                             | no.  |

| t <sub>10</sub>               | CLR pulse width low                               | V <sub>DD</sub> = 3.6 V to 5.5 V           | 10  | -                           | ns   |

- (1) All input signals are specified with  $t_R = t_F = 1$  ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ ) / 2.

- (2) Maximum SCLK frequency is 50 MHz at V<sub>DD</sub> = 2.7 to 5.5 V.

- (3) SCLK falling edge to  $\overline{\text{SYNC}}$  rising edge time shold not exceed (t<sub>1</sub> 10 ns) to latch the correct data.

Figure 1. Serial Write Operation Timing Diagram

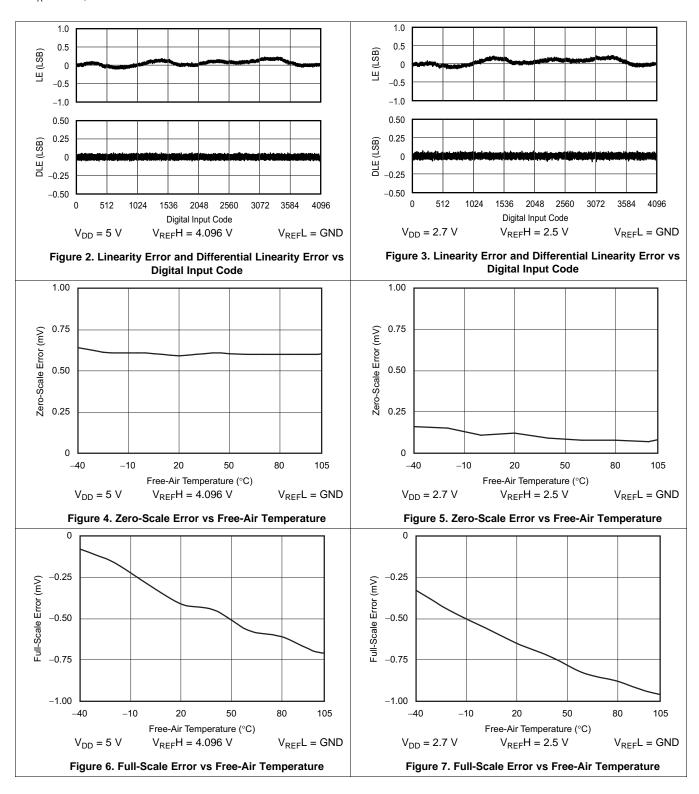

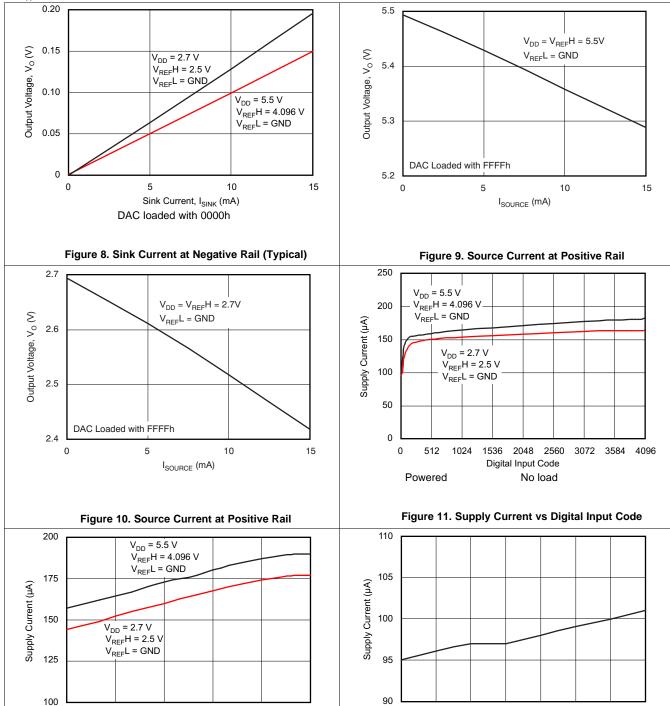

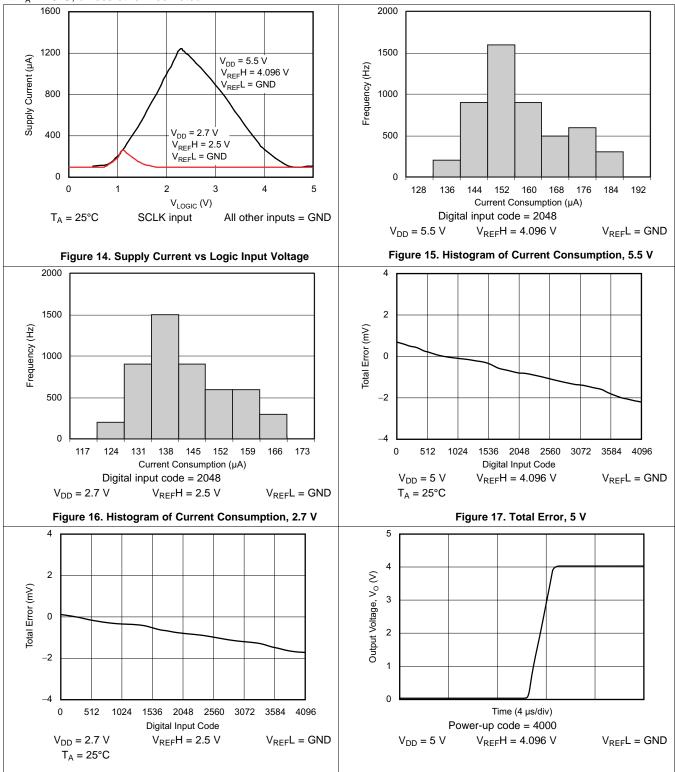

### 6.7 Typical Characteristics

At  $T_A = 25$ °C, unless otherwise noted.

# TEXAS INSTRUMENTS

### **Typical Characteristics (continued)**

At  $T_A = 25$ °C, unless otherwise noted.

2.7

DAC powered, no load

3.1

3.5

3.9

4.3

$V_{REF}H = 2.5 V$

Supply Voltage (V)

Figure 13. Supply Current vs Supply Voltage

5.1

5.5

$V_{REF}L = GND$

80

110

-40

Powered

-10

20

50

No load

Free-Air Temperature (°C)

Figure 12. Supply Current vs Free-Air Temperature

# **Typical Characteristics (continued)**

At  $T_A = 25$ °C, unless otherwise noted.

Figure 18. Total Error, 2.7 V

Figure 19. Exiting Power-Down Mode

# TEXAS INSTRUMENTS

### **Typical Characteristics (continued)**

At  $T_A = 25$ °C, unless otherwise noted.

### 7 Detailed Description

#### 7.1 Overview

The DAC7551-Q1 device is a 12-bit resistor-string digital-to-analog converter (DAC). Unbuffered external reference inputs allow for a positive voltage reference as low as 0.25 V and as high as  $V_{DD}$ . An amplifier-feedback input is available for better DC accuracy at the load point. The device is controlled over a 16-bit word three-wire serial peripheral interface (SPI) up to 50 MHz with an option to daisy-chain multiple devices. An asynchronous clear function along with power-down features allows for software controlled resets and low-power consumption. A separate logic-supply input means the device can be used with different logic families across a wide range of supply voltages.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

#### 7.3.1 Digital-to-Analog Converter

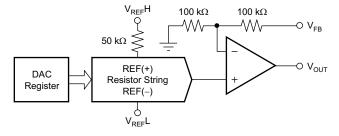

The architecture of the DAC7551-Q1 device consists of a string DAC followed by an output buffer amplifier. Figure 26 shows a generalized block diagram of the DAC architecture.

Figure 26. Typical DAC Architecture

The input coding to the DAC7551-Q1 device is unsigned binary, which gives the ideal output voltage as show in Equation 1.

$$V_{OUT} = 2 \times V_{REF}L + (V_{REF}H - V_{REF}L) \times D / 4096$$

where

• D is the decimal equivalent of the binary code that is loaded to the DAC register, which ranges from 0 to 4095.

(1)

### **Feature Description (continued)**

#### 7.3.2 Resistor String

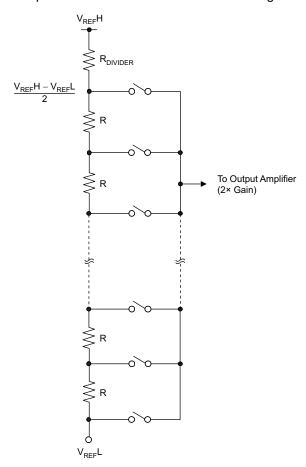

Figure 27 shows the resistor string section. This section is simply a string of resistors, each of value R. The digital code loaded to the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier. The voltage is tapped off by closing one of the switches connecting the string to the amplifier. The output of the DAC is specified monotonic because it is a string of resistors.

Figure 27. Typical Resistor String

#### 7.3.3 Output Buffer Amplifiers

The output buffer amplifier is capable of generating rail-to-rail voltages on the output, providing an output range of 0 V to  $V_{DD}$ . The amplifier is capable of driving a load of 2 k $\Omega$  in parallel with up to 1000 pF to ground. Figure 8, Figure 9, and Figure 10 show the sink and source capabilities of the output amplifier. The slew rate is 1.8 V/µs with a half-scale settling time of 3 µs with the output unloaded.

### 7.3.3.1 DAC External Reference Input

The DAC7551-Q1 device contains  $V_{REF}H$  and  $V_{REF}L$  reference inputs which are unbuffered. The  $V_{REF}H$  reference voltage can be as low as 0.25 V, and as high as  $V_{DD}$  because there is no restriction of headroom and footroom from any reference amplifier.

Using a buffered reference in the external circuit is recommended (for example, the REF3140 device). The input impedance is typically 100 k $\Omega$ .

### **Feature Description (continued)**

#### 7.3.3.2 Amplifier Sense Input

The DAC7551-Q1 device contains an amplifier-feedback input pin,  $V_{FB}$ . For voltage output operation,  $V_{FB}$  must be externally connected to  $V_{OUT}$ . For better DC accuracy, this connection should be made at load points. The  $V_{FB}$  pin is also useful for a variety of applications, including digitally-controlled current sources. The feedback input pin is internally connected to the DAC amplifier negative input terminal through a 100-k $\Omega$  resistor. The amplifier negative input terminal internally connects to ground through another 100-k $\Omega$  resistor (see Figure 26). These connections form a gain-of-two, noninverting, amplifier configuration. Overall gain remains 1 because the resistor string has a divide-by-two configuration. The resistance seen at the  $V_{FB}$  pin is approximately 200 k $\Omega$  to ground.

#### 7.3.3.3 Power-On Reset

On power up, all registers are cleared and the DAC channel is updated with zero-scale voltage. The DAC output remains in this state until valid data are written. This setup is particularly useful in applications where knowing the state of the DAC output while the device is powering up is important. To not turn on ESD protection devices,  $V_{DD}$  and  $IOV_{DD}$  should be applied before any other pin (such as  $V_{REF}H$ ) is brought high. The power-up sequence of  $V_{DD}$  and  $IOV_{DD}$  is irrelevant. Therefore,  $IOV_{DD}$  can be brought up before  $V_{DD}$ , or the other way around.

#### 7.3.3.4 Power Down

The DAC7551-Q1 device has a flexible power-down capability. During a power-down condition, the user has flexibility to select the output impedance of the DAC. During power-down operation, the DAC can have either  $1k\Omega$ ,  $100k\Omega$ , or Hi-Z output impedance to ground.

### 7.3.3.5 Asynchronous Clear

The DAC7551-Q1 output is asynchronously set to zero-scale voltage immediately after the  $\overline{\text{CLR}}$  pin is brought low. The  $\overline{\text{CLR}}$  signal resets all internal registers and therefore functions similar to the power-on reset. The DAC7551-Q1 device updates at the first rising edge of the  $\overline{\text{SYNC}}$  signal that occurs after the  $\overline{\text{CLR}}$  pin is brought back to high.

#### 7.3.3.6 IOVDD and Level Shifters

The DAC7551-Q1 device can be used with different logic families that require a wide range of supply voltages. To enable this useful feature, the  $IOV_{DD}$  pin must be connected to the logic supply voltage of the system. All DAC7551-Q1 digital input and output pins are equipped with level-shifter circuits. Level shifters at the input pins ensure that external logic-high voltages are translated to the internal logic-high voltage, with no additional power dissipation. Similarly, the level shifter for the SDO pin translates the internal logic-high voltage ( $V_{DD}$ ) to the external logic-high level ( $IOV_{DD}$ ). For single-supply operation, the  $IOV_{DD}$  pin can be tied to the  $V_{DD}$  pin.

#### 7.3.4 Integral and Differential Linearity

The DAC7551-Q1 device uses precision thin-film resistors providing exceptional linearity and monotonicity. Integral linearity error is typically within  $\pm 0.35$  LSBs, and differential linearity error is typically within  $\pm 0.08$  LSBs.

### 7.3.5 Glitch Energy

The DAC7551-Q1 device uses a proprietary architecture that minimizes glitch energy. The code-to-code glitches are so low that they are usually buried within the wide-band noise and cannot be easily detected. The DAC7551-Q1 glitch is typically well under 0.1 nV-s. Such low glitch energy provides more than a ten-time improvement over industry alternatives.

#### 7.4 Device Functional Modes

The DAC7551-Q1 device uses four modes of operation. These modes are accessed by setting bit PD0 (DB13) and PD1 (DB14) in the control register. Table 1 shows how to control the operating mode with data bits PD0 (DB13) and PD1 (DB14). The DAC7551-Q1 device treats the power-down condition as data; all the operation modes are still valid for power down. Broadcasting a power-down condition to all the DAC7551-Q1 devices in a system is possible. Powering down a channel and updating data on other channels is also possible. Furthermore, writing to the DAC register or buffer of the DAC channel that is powered down is also possible. When the DAC is the powered on, the DAC contains this new value.

### **Device Functional Modes (continued)**

When both the PD0 and PD1 bits are set to 0, the device works normally with the typical consumption of 100  $\mu$ A at 2.7 V. For the three power-down modes, the supply current falls to 0.05  $\mu$ A at 2.7 V. As listed in Table 1, three different power-down options are available. The VOUT pin can be connected internally to GND through a 1-k $\Omega$  resistor or a 100-k $\Omega$  resistor or can be open circuited (High-Z). In other words, DB14 and DB13 = 11 represent a power-down condition with High-Z output impedance for a selected channel. DB14 and DB13 = 01 and 10 represent a power-down condition with a 1-k $\Omega$  and 100-k $\Omega$  output impedance respectively.

### 7.5 Programming

#### 7.5.1 Serial Interface

The DAC7551-Q1 device is controlled over a versatile 3-wire serial interface, which operates at clock rates up to 50 MHz and is compatible with SPI, QSPI, Microwire, and DSP interface standards.

|      | CON  | TROL          |               | DATA BITS |                 |

|------|------|---------------|---------------|-----------|-----------------|

| DB15 | DB14 | DB13<br>(PD1) | DB12<br>(PD0) | DB11-DB0  | FUNCTION        |

| X    | X    | 0             | 0             | data      | Normal mode     |

| X    | X    | 0             | 1             | X         | Powerdown 1kΩ   |

| X    | X    | 1             | 0             | X         | Powerdown 100kΩ |

| Х    | Х    | 1             | 1             | X         | Powerdown Hi-Z  |

**Table 1. Serial Interface Programming**

#### 7.5.1.1 16-Bit Word and Input Shift Register

The input shift register is 16 bits wide. DAC data are loaded into the device as a 16-bit word under the control of a serial clock input, SCLK, as shown in Figure 1. The 16-bit word, listed in Table 1, consists of four control bits followed by 12 bits of DAC data. The data format is straight binary with all 0s corresponding to 0-V output and all 1s corresponding to full-scale output ( $V_{REF} - 1$  LSB). Data are loaded MSB first (bit 15) where the first two bits (DB15 and DB14) are *don't care* bits. Bit 13 and bit 12 (DB13 and DB12) determine either normal mode operation or power-down mode (see Table 1).

The SYNC input is a level-triggered input that acts as a frame synchronization signal and chip enable. Data can only be transferred into the device while the SYNC pin is low. To begin the serial data transfer, the SYNC pin should be taken low, observing the minimum SYNC-to-SCLK falling edge setup time, t<sub>4</sub>. After the SYNC pin goes low, serial data is shifted into the device input shift register on the falling edges of SCLK for 16 clock pulses.

The SPI is enabled after the SYNC pin becomes low and the data are continuously shifted into the shift register at each falling edge of the SCLK input. When the SYNC pin is brought high, the last 16 bits stored in the shift register are latched into the DAC register, and the DAC updates.

#### 7.5.1.2 Daisy-Chain Operation

Daisy-chain operation is used for updating serially-connected devices on the rising edge of the SYNC in.

As long as the \$\overline{\text{SYNC}}\$ pin is high, the SDO pin is in a high-impedance state. When the \$\overline{\text{SYNC}}\$ pin is brought low the output of the internal shift register is tied to the SDO pin. As long as the \$\overline{\text{SYNC}}\$ pin is low, the SDO pin duplicates the SDIN signal with a 16-cycle delay. To support multiple devices in a daisy chain, the \$CLK\$ and \$\overline{\text{SYNC}}\$ signals are shared across all devices, and the \$\overline{\text{SDO}}\$ pin of one DAC7551-Q1 device should be tied to the \$\overline{\text{SDIN}}\$ pin of the next DAC7551-Q1 device. For \$n\$ devices in such a daisy chain, \$16n\$ \$CLK\$ cycles are required to shift the entire input data stream. After \$16n\$ \$CLK\$ falling edges are received, following a falling \$\overline{\text{SYNC}}\$ signal, the data stream becomes complete and the \$\overline{\text{SYNC}}\$ pin can be brought high to update \$n\$ devices simultaneously. \$\overline{\text{SDO}}\$ operation is specified at a maximum \$\overline{\text{SCLK}}\$ speed of 10 MHz.

In daisy-chain mode, the use of a weak pulldown resistor on the SDO output pin, which provides the SDIN data for the next device in the chain, is recommended. For standalone operation, the maximum clock speed is 50 MHz. For daisy-chain operation, the maximum clock speed is 10 MHz.

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

#### 8.1.1 Waveform Generation

As a result of the exceptional linearity and low glitch of the DAC7551-Q1 device, the device is well-suited for waveform generation (from DC to 10kHz). The DAC7551-Q1 large-signal settling time is 5 µs, supporting an update rate of 200 kSPS. However, the update rates can exceed 1 MSPS if the waveform to be generated consists of small voltage steps between consecutive DAC updates. To obtain a high dynamic range, the REF3140 device (4.096 V) or the REF02 device (5 V) is recommended for reference-voltage generation.

#### 8.1.2 Generating ±5-V, ±10-V, and ±12-V Outputs For Precision Industrial Control

Industrial control applications can require multiple feedback loops consisting of sensors, analog-to-digital converters (ADCs), microcontrollers (MCUs), DACs, and actuators. Loop accuracy and loop speed are the two important parameters of such control loops.

#### 8.1.2.1 Loop Accuracy

DAC offset, gain, and the integral linearity errors are not factors in determining the accuracy of the loop. As long as a voltage exists in the transfer curve of a monotonic DAC, the loop can find this voltage and settle to it. On the other hand, DAC resolution and differential linearity do determine the loop accuracy, because each DAC step determines the minimum incremental change the loop can generate. A DNL error less than –1 LSB (non-monotonicity) can create loop instability. A DNL error greater than 1 LSB implies unnecessarily large voltage steps and missed voltage targets. With high DNL errors, the loop loses stability, resolution, and accuracy. Offering 12-bit ensured monotonicity and ±0.08-LSB typical DNL error, the DAC755x devices are great choices for precision control loops.

#### 8.1.2.2 Loop Speed

Many factors determine the control-loop speed, such as ADC conversion time, MCU speed, and DAC settling time. Typically, the ADC conversion time, and the MCU computation time are the two major factors that dominate the time constant of the loop. DAC settling time is rarely a dominant factor because ADC conversion times usually exceed DAC conversion times. DAC offset, gain, and linearity errors can slow the loop down only during the startup. When the loop reaches the steady-state operation, these errors do not affect loop speed any further. Depending on the ringing characteristics of the loop-transfer function, DAC glitches can also slow the loop down. With a 1-MSPS (small-signal) maximum data-update rate, the DAC7551-Q1 device can support high-speed control loops. Ultralow glitch energy of the DAC7551-Q1 device significantly improves loop stability and loop settling time.

#### 8.2 Typical Application

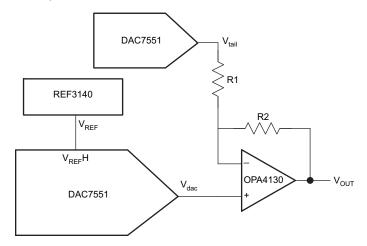

#### 8.2.1 Generating Industrial Voltage Ranges

For control-loop applications, DAC gain and offset errors are not important parameters. This consideration could be exploited to lower trim and calibration costs in a high-voltage control-circuit design. Using a quad operational amplifier (OPA4130), and a voltage reference (REF3140), the DAC7551-Q1 can generate the wide voltage swings required by the control loop.

Figure 28. Low-cost, Wide-swing Voltage Generator for Control-Loop Applications

#### 8.2.1.1 Design Requirements

For ±5-V operation:

$R1 = 10 k\Omega$

$R2 = 15 k\Omega$

$V_{tail} = 3.33 \text{ V}$

$V_{RFF} = 4.096 V$

For ±10-V operation:

$R1 = 10 k\Omega$

$R2 = 39 k\Omega$

$V_{tail} = 2.56 \text{ V}$

$V_{RFF} = 4.096 V$

For ±12-V operation:

$R1 = 10 k\Omega$

$R2 = 49 k\Omega$

$V_{tail} = 2.45 \text{ V}$

$V_{RFF} = 4.096 V$

### 8.2.1.2 Detailed Design Procedure

Use Equation 2 to calculate the output voltage of the configuration.

$$V_{OUT} = V_{REF} \left( \frac{R2}{R1} + 1 \right) \frac{SDIN}{4096} - V_{tail} \left( \frac{R2}{R1} \right)$$

(2)

Fixed R1 and R2 resistors can be used to coarsely set the gain required in the first term of the equation. When R2 and R1 set the gain to include some minimal over-range gain, a single DAC7551-Q1 device can be used to set the required offset voltages. Residual errors are not an issue for loop accuracy because offset and gain errors can be tolerated. One DAC7551-Q1 device can provide the  $V_{tail}$  voltages, while four additional DAC7551-Q1 devices can provide the  $V_{dac}$  voltages to generate four high-voltage outputs. A single SPI is sufficient to control all five DAC7551-Q1 devices in a daisy-chain configuration.

### **Typical Application (continued)**

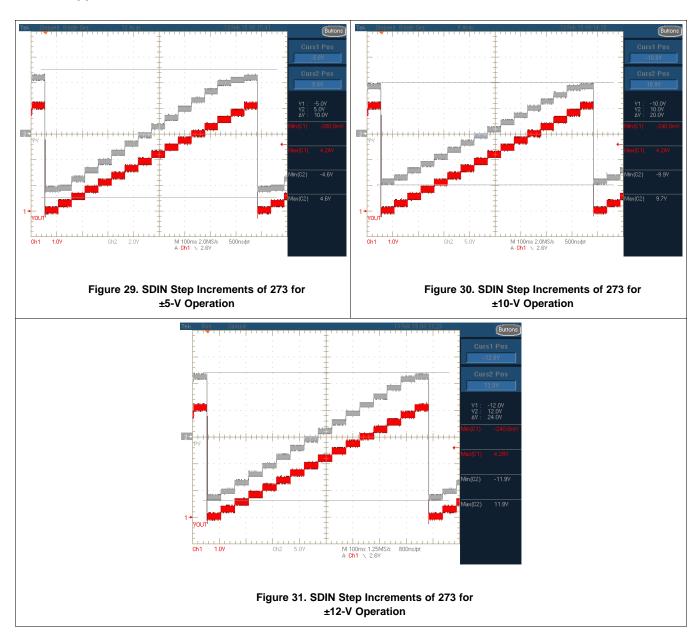

#### 8.2.1.3 Application Curves

### 9 Power Supply Recommendations

The power applied to the  $V_{DD}$  pin should be well regulated and low noise. Switching power supplies and DC-DC converters often have high frequency glitches or spikes riding on the output voltage. In addition, digital components can create similar high-frequency spikes as the internal logic switches states. This noise can easily couple into the DAC output voltage through various paths between power connections and analog output. As with the GND connection, the  $V_{DD}$  pin should be connected to a power-supply plane of trace that is separate from the connection for digital logic until they are connected at the power-entry point. In addition, the use of a 1- $\mu$ F and 10- $\mu$ F capacitor and a 0.1- $\mu$ F bypass capacitor is strongly recommended. In some situations, additional bypassing may be required, such as a 100- $\mu$ F electrolytic capacitor or even a Pi filter made up of inductors and capacitors. These bypassing methods are all designed to low-pass filter the supply and remove the high-frequency noise.

17

### 10 Layout

### 10.1 Layout Guidelines

A precision analog component requires careful layout, adequate bypassing, and clean, well-regulated power supplies. The DAC7551-Q1 device offers single-supply operation, and is often used in close proximity with digital logic, microcontrollers, microprocessors, digital signal processors, or a combination. The more digital logic present in the design and the higher the switching speed, the more difficult it is to prevent digital noise from appearing at the output. As a result of the single ground pin of the DAC7551-Q1 device, all return currents (including digital and analog return currents for the DAC) must flow through a single point. Ideally, the GND should be connected directly to an analog ground plane. This plane should be separate from the ground connection for the digital components until these components were connected at the power-entry point of the system.

### 10.2 Layout Example

- Via to power ground plane

- → Connection to MCU, MPU, or DSP

Figure 32. DAC7551-Q1 Layout Example

### 11 器件和文档支持

#### 11.1 文档支持

#### 11.1.1 相关文档

相关文档如下:

- 《OPA4130 低功耗、精密 FET 输入运算放大器》, SBOS053

- 《REF02 +5V 精密电压基准》, SBVS003

- 《REF3140 最大 15ppm/°C、100µA、SOT23-3 串联电压基准》, SBVS046

#### 11.2 商标

SPI, QSPI are trademarks of Motorola, Inc.

All other trademarks are the property of their respective owners.

### 11.3 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 11.4 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、首字母缩略词和定义。

### 12 机械封装和可订购信息

以下页中包括机械封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

### PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| DAC7551TDRNRQ1   | ACTIVE | USON         | DRN                | 12   | 3000           | RoHS & Green | NIPDAUAG                      | Level-2-260C-1 YEAR | -40 to 105   | RAN                     | Samples |

| DAC7551ZTDRNRQ1  | ACTIVE | USON         | DRN                | 12   | 3000           | RoHS & Green | NIPDAUAG                      | Level-2-260C-1 YEAR | -40 to 105   | SJT                     | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 6-May-2023

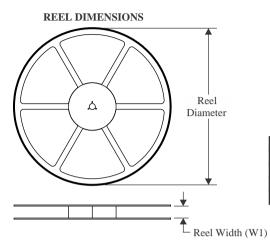

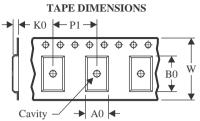

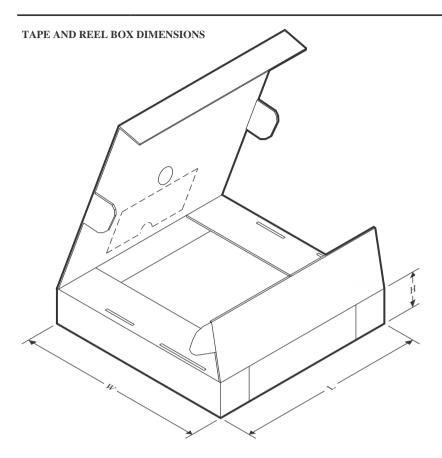

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

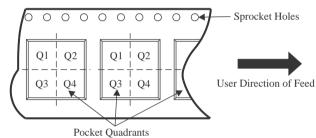

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DAC7551TDRNRQ1  | USON            | DRN                | 12 | 3000 | 330.0                    | 12.4                     | 2.3        | 3.3        | 0.7        | 4.0        | 12.0      | Q1               |

| DAC7551ZTDRNRQ1 | USON            | DRN                | 12 | 3000 | 330.0                    | 12.4                     | 2.3        | 3.3        | 0.7        | 4.0        | 12.0      | Q1               |

www.ti.com 6-May-2023

### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DAC7551TDRNRQ1  | USON         | DRN             | 12   | 3000 | 338.0       | 355.0      | 50.0        |

| DAC7551ZTDRNRQ1 | USON         | DRN             | 12   | 3000 | 338.0       | 355.0      | 50.0        |

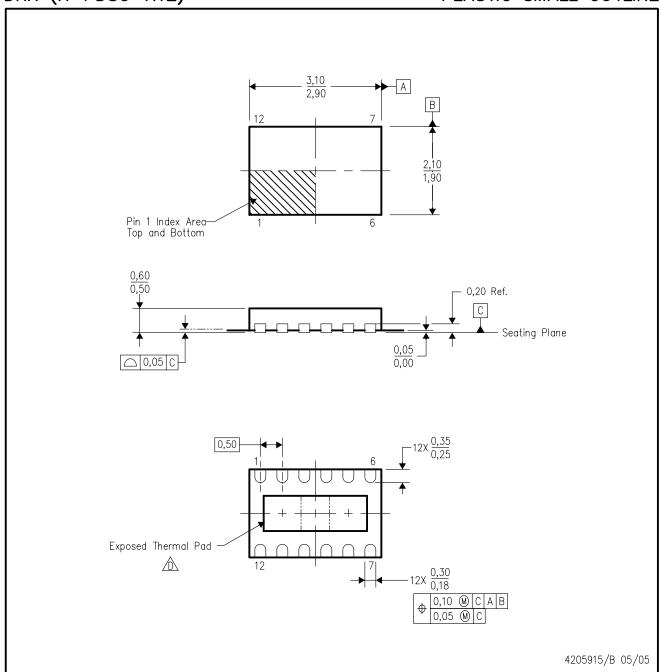

# DRN (R-PDSO-N12)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. SON (Small Outline No-Lead) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- E. Package complies to JEDEC MO-229.

### 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司