bq33100

ZHCSEJ8B - JANUARY 2011-REVISED DECEMBER 2015

# bq33100 超级电容管理器

## 1 特性

- 全集成超级电容管理器,适用于 2、3、4 或 5 个电容串联

- 在不提供单独电容监视和均衡功能的前提下,可与 多达 9 个串联的电容搭配使用

- 有源电容电压均衡

- 防止超级电容在充电过程中发生过压

- 电容健康状况监视

- 电容学习

- 等效串联电阻 (ESR) 测量

- 运行状态

- 充电状态

- 健康状况

- 充电电压和电流报告

- 带可选引脚指示的安全报警

- 集成保护监控

- 过压

- 短路

- 过热

- 过量电容泄漏

- 2 线 SMBus 串行通信

- 高精度 16 位 Σ-Δ ADC,通过 16 通道多路复用器进行测量

- 用于电压、电流和温度

- 低功耗

- < 660µA(正常运行模式)

- <1µA (关断模式)

- 宽运行温度范围: -40°C 至 +85°C

## 2 应用

- 备用电池的替代产品

- 缓存控制器

- RAID 系统

- 刀锋服务器卡

- 不间断电源 (UPS)

- 医疗与测试设备

- 便携式仪器

## 3 说明

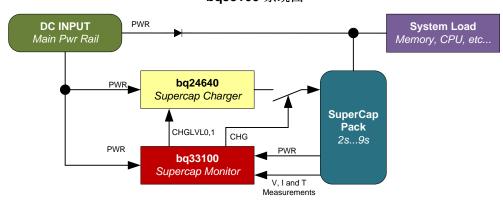

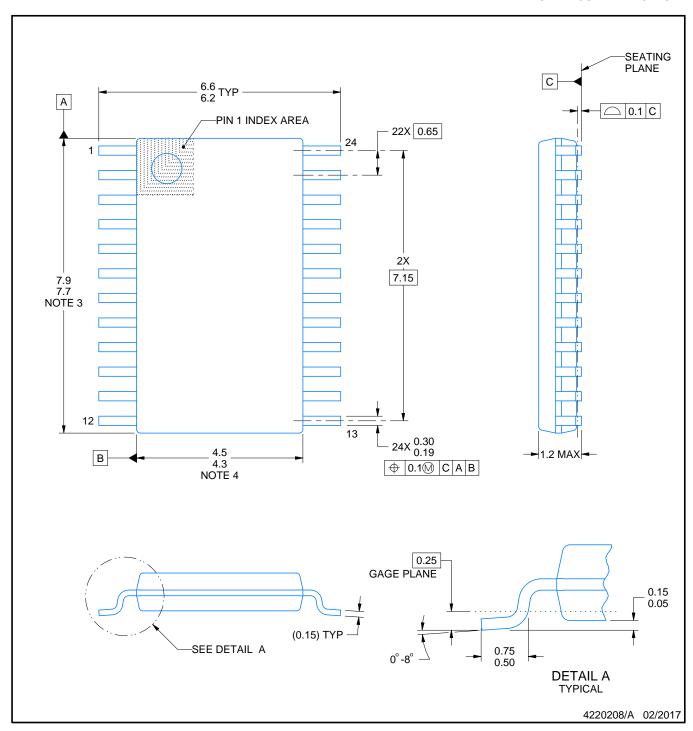

德州仪器 (TI) 的 bq33100 超级电容管理器是一款全集成单片解决方案,其提供有丰富的充电控制、监视和保护 功能,不仅可为 2、3、4 或 5 个串联超级电容提供单独电容监视与均衡功能,还能够为多达 9 个串联电容提供电池组电压测量。bq33100 采用紧凑型7.8mm × 6.4mm 24 引脚薄型小外形尺寸 (TSSOP) 封装,最大限度丰富功能和提高安全性的同时,还为超级电容应用极大地改善了易用性、削减了解决方案成本并减小了解决方案 尺寸。

## 器件信息(1)

| 器件型号    | 封装         | 封装尺寸 (标称值)      |

|---------|------------|-----------------|

| bq33100 | TSSOP (24) | 7.80mm × 4.40mm |

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

## bq33100 系统图

$\triangle$

| _ |     |

|---|-----|

| ш |     |

| п | 717 |

|   |     |

|   |     |

| 1 | 特性1                                                   |     | 7.19 Current Protection Thresholds |    |

|---|-------------------------------------------------------|-----|------------------------------------|----|

| 2 | 应用                                                    |     | 7.20 Current Protection Timing     | 9  |

| 3 | 说明 1                                                  |     | 7.21 Timing Requirements: SMBus    | 10 |

| 4 | 修订历史记录                                                |     | 7.22 Typical Characteristics       | 11 |

| 5 | 说明(续)3                                                | 8   | Detailed Description               | 12 |

| 6 | Pin Configuration and Functions 3                     |     | 8.1 Overview                       | 12 |

| - | _                                                     |     | 8.2 Functional Block Diagram       | 14 |

| 7 | Specifications4                                       |     | 8.3 Feature Description            | 14 |

|   | 7.1 Absolute Maximum Ratings                          |     | 8.4 Device Functional Modes        | 29 |

|   | 7.2 ESD Ratings                                       |     | 8.5 Programming                    | 30 |

|   | 7.3 Recommended Operating Conditions                  | 9   | Application and Implementation     |    |

|   | 7.4 Thermal Information                               |     | 9.1 Application Information        |    |

|   | 7.5 Electrical Characteristics: General Purpose I/O 5 |     | 9.2 Typical Application            |    |

|   | 7.6 Supply Current                                    | 10  | Power Supply Recommendations       |    |

|   | 7.7 REG27 LDO                                         | 11  | Layout                             |    |

|   | 7.8 Coulomb Counter                                   | • • | 11.1 Layout Guidelines             |    |

|   | 7.9 ADC                                               |     | 11.2 Layout Example                |    |

|   | 7.10 External Capacitor Voltage Balance Drive         | 12  | 器件和文档支持                            |    |

|   | 7.11 Capacitor Voltage Monitor                        | 12  | 12.1 文档支持                          |    |

|   | 7.12 Internal Temperature Sensor                      |     | 12.2 社区资源                          |    |

|   | 7.13 Thermistor Measurement Support                   |     | 12.3 商标                            |    |

|   | 7.14 Internal Thermal Shutdown                        |     | 12.4 静电放电警告                        |    |

|   | 7.15 High-Frequency Oscillator                        |     | 12.5 Glossary                      |    |

|   | 7.16 Low-Frequency Oscillator 8                       | 12  | -                                  |    |

|   | 7.17 RAM Backup                                       | 13  | 机械、封装和可订购信息                        | 00 |

|   | 7.18 Flash 8                                          |     |                                    |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

## Changes from Revision A (March 2011) to Revision B

Page

- Changes from Original (January 2011) to Revision A

## Page

| • | Changed SYSTEM PARTITIONING DIAGRAM                               | 14 |

|---|-------------------------------------------------------------------|----|

| • | Changed Voltage as Current During Learning graphic.               | 15 |

| • | Changed equation 1 denominator from (V[D] - [C]) to (V[C] - V[D]) | 15 |

| • | Changed Application Reference Schematic.                          | 54 |

## 5 说明 (续)

bq33100 利用其集成的高性能模拟外设,测量超级电容的可用电容、健康状况、电压、电流、温度和其他关键参数,保留准确的数据记录,并通过 2 线 SMBus 1.1 兼容接口将这些信息报告给系统主机控制器。

bq33100 通过固件提供了过压、过温及过充保护,并通过硬件提供有放电过流及充放电短路保护。

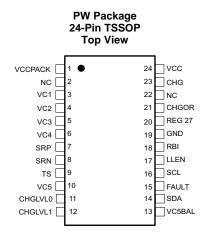

## 6 Pin Configuration and Functions

## **Pin Functions**

| PIN     |     | TVD=(1)                    | DECODINE                                                                                                                                                                                                                    |  |  |

|---------|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO. | <b>TYPE</b> <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                 |  |  |

| CHG     | 23  | 0                          | P-Channel FET drive for controlling charge                                                                                                                                                                                  |  |  |

| CHGLVL0 | 11  | 0                          | Charge Control Output 0                                                                                                                                                                                                     |  |  |

| CHGLVL1 | 12  | 0                          | Charge Control Output 1                                                                                                                                                                                                     |  |  |

| CHGOR   | 21  | I                          | Over Ride input. If not used connect to VSS                                                                                                                                                                                 |  |  |

| FAULT   | 15  | 0                          | high output to indicate fault condition.                                                                                                                                                                                    |  |  |

| GND     | 19  | Р                          | d                                                                                                                                                                                                                           |  |  |

| LLEN    | 17  | 0                          | Load Enable Output                                                                                                                                                                                                          |  |  |

| NC      | 2   | 0                          | Not used and must be connected to VCC                                                                                                                                                                                       |  |  |

| NC      | 22  | -                          | No connect, leave pin floating                                                                                                                                                                                              |  |  |

| RBI     | 18  | Р                          | RAM backup pin to provide backup potential to the internal DATA RAM if power is momentarily lost by using a capacitor attached between RBI and GND                                                                          |  |  |

| REG27   | 20  | Р                          | Internal power supply 2.7-V bias output                                                                                                                                                                                     |  |  |

| SCL     | 16  | I/OD                       | Serial clock input: Clocks data on SDA                                                                                                                                                                                      |  |  |

| SDA     | 14  | I/OD                       | Serial Data: Transmits and Receives data                                                                                                                                                                                    |  |  |

| SRN     | 8   | IA                         | Analog input pin connected to the internal ADC peripheral for measuring a small voltage between SRP and SRN where SRN is the bottom of the sense resistor.                                                                  |  |  |

| SRP     | 7   | IA                         | Analog input pin connected to the internal ADC peripheral for measuring a small voltage between SRP and SRN where SRP is the top of the sense resistor.                                                                     |  |  |

| TS      | 9   | IA                         | Thermistor input                                                                                                                                                                                                            |  |  |

| VC1     | 3   | IA                         | Sense voltage input terminal and external capacitor voltage balancing drive output for the 5th series capacitor, and stack measurement input. See <i>Series Capacitor Configuration</i> for systems with less than 5 series |  |  |

| VC2     | 4   | IA                         | Sense voltage input terminal and external capacitor voltage balancing drive output for the 4th series capacitor. See Series Capacitor Configuration for systems with less than 5 series                                     |  |  |

| VC3     | 5   | IA                         | Sense voltage input terminal and external capacitor voltage balancing drive output for the 3rd series capacitor. See Series Capacitor Configuration for systems with less than 5 series                                     |  |  |

## (1) I = Input, O = Output, P = Power, IA = Analog Input, OD = Open Drain

## Pin Functions (continued)

| PIN       | PIN |        | TYPE <sup>(1)</sup>                                                                                                                                                                            |  | DESCRIPTION |

|-----------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| NAME      | NO. | ITPE'/ | DESCRIPTION                                                                                                                                                                                    |  |             |

| VC4 6     |     | IA     | Sense voltage input terminal and external capacitor voltage balancing drive output for the 2nd series capacitor. See <i>Series Capacitor Configuration</i> for systems with less than 5 series |  |             |

| VC5 10    |     | IA     | Sense voltage input terminal and external capacitor voltage balancing drive output for the 1st capacitor. See<br>Series Capacitor Configuration for systems with less than 5 series            |  |             |

| VC5BAL    | 13  | 0      | Cell balance control output for the least positive capacitor (only used in 5-series capacitor configuration)                                                                                   |  |             |

| VCCPACK 1 |     | Р      | Power supply from the supercaps. The top of the supercap stack must be connected to this pin.                                                                                                  |  |             |

| VCC       | 24  | Р      | Positive input from power supply                                                                                                                                                               |  |             |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                   |                      |                                  | MIN                                           | MAX                                                    | UNIT |

|-------------------|----------------------|----------------------------------|-----------------------------------------------|--------------------------------------------------------|------|

| $V_{MAX}$         | Supply voltage       | VCC w.r.t. GND                   | -0.3                                          | 34                                                     | V    |

|                   |                      | VC1, VCC                         | V <sub>VC2</sub> - 0.3                        | V <sub>VC2</sub> + 8.5 or<br>34, whichever<br>is lower | V    |

| $V_{\text{IN}}$   |                      | VC2                              | V <sub>VC3</sub> - 0.3 V <sub>VC3</sub> + 8.5 |                                                        | V    |

|                   |                      | VC3                              | V <sub>VC4</sub> - 0.3                        | $V_{VC4} + 8.5$                                        | V    |

|                   | Input voltage        | VC4                              | $V_{SRP} - 0.3$                               | V <sub>SRP</sub> + 8.5                                 | V    |

|                   |                      | SRP, SRN                         | -0.3                                          | $V_{REG27}$                                            | V    |

|                   |                      | SDA, SCL                         | -0.3                                          | 6.0                                                    | V    |

|                   |                      | CHGOR                            | -0.3                                          | VCC                                                    | V    |

|                   |                      | TS, VC5, CHGLVL0, CHGLVL1, FAULT | -0.3                                          | $V_{REG27} + 0.3$                                      | V    |

|                   |                      | CHG                              | -0.3                                          | VCC                                                    | V    |

| Vo                | Output voltage       | VC5BAL                           | -0.3                                          | $V_{REG27} + 0.3$                                      | V    |

|                   |                      | RBI, REG27                       | -0.3                                          | 2.75                                                   | V    |

| I <sub>SS</sub>   | Maximum combined     | sink current for input pins      |                                               | 50                                                     | mA   |

| T <sub>FUNC</sub> | Functional temperatu | ıre                              | -40                                           | 110                                                    | °C   |

|                   | Storage temperature  |                                  | -65                                           | 150                                                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                       |                             |                                 | MIN              | NOM | MAX                  | UNIT |

|-----------------------|-----------------------------|---------------------------------|------------------|-----|----------------------|------|

|                       | Cumply voltogo              | VCC                             |                  |     | 25                   | V    |

|                       | Supply voltage              | VCC                             | 3.8              |     | V <sub>VC2</sub> + 5 | V    |

| V <sub>STARTUP</sub>  |                             | Start up voltage at VCC         |                  | 5.2 | 5.5                  | V    |

| V <sub>SHUTDOWN</sub> |                             | VCC or VCC, whichever is higher | 3                | 3.2 | 3.3                  | V    |

|                       |                             | VC1, VCC                        | V <sub>VC2</sub> |     | V <sub>VC2</sub> + 5 |      |

|                       |                             | VC2                             | V <sub>VC3</sub> |     | V <sub>VC3</sub> + 5 |      |

|                       |                             | VC3                             | $V_{VC4}$        |     | V <sub>VC4</sub> + 5 |      |

|                       |                             | VC4                             | V <sub>SRP</sub> |     | V <sub>SRP</sub> + 5 | V    |

| V <sub>IN</sub>       | Input voltage               | VCn - VC(n + 1), (n=1, 2, 3, 4) | 0                |     | 5                    |      |

|                       |                             | VC5                             | 0                |     | 1                    |      |

|                       |                             | VCC                             |                  |     | 25                   |      |

|                       |                             | CHGOR                           | 0                |     | VCC - 0.3            | V    |

|                       |                             | SRP to SRN                      | -0.3             |     | 1                    | V    |

| C <sub>REG27</sub>    | External 2.7-V REG capacito | г                               | 1                |     |                      | μF   |

| T <sub>OPR</sub>      | Operating temperature       |                                 | -40              |     | 85                   | °C   |

## 7.4 Thermal Information

|                        | Thermal information                          |            |      |  |  |  |  |  |

|------------------------|----------------------------------------------|------------|------|--|--|--|--|--|

|                        |                                              | bq33100    |      |  |  |  |  |  |

|                        | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |  |  |  |  |  |

|                        |                                              | 24 PINS    |      |  |  |  |  |  |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 83.6       | °C/W |  |  |  |  |  |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 16.5       | °C/W |  |  |  |  |  |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 39.4       | °C/W |  |  |  |  |  |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.4        | °C/W |  |  |  |  |  |

| ΨЈВ                    | Junction-to-board characterization parameter | 38.8       | °C/W |  |  |  |  |  |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | _          | °C/W |  |  |  |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics: General Purpose I/O

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                       | PARAMETER                 | TEST CONDITIONS                                                                | MIN                      | TYP | MAX  | UNIT |

|-----------------------|---------------------------|--------------------------------------------------------------------------------|--------------------------|-----|------|------|

| V <sub>IH</sub>       | High-level input voltage  | SDA, SCL, TS, VC5                                                              | 2                        |     |      | V    |

| V <sub>IL</sub>       | Low-level input voltage   | SDA, SCL, TS, VC5                                                              |                          |     | 0.8  | V    |

| V <sub>OH</sub>       | Output voltage high       | SDA, SCL, VC5BAL, CHGLVL0, CHGLVL1, LLEN, FAULT, $I_L = -0.5$ mA               | V <sub>REG27</sub> – 0.5 |     |      | V    |

| V <sub>OL</sub>       | Low-level output voltage  | SDA, SCL, VC5BAL, CHGLVL0, CHGLVL1, LLEN, FAULT, I <sub>L</sub> = 7 mA         |                          |     | 0.4  | V    |

| C <sub>IN</sub>       | Input capacitance         |                                                                                |                          | 5   |      | pF   |

| I <sub>lkg</sub>      | Input leakage current     | SDA, SCL, TS, VC5, CHGLVL0, CHGLVL1, LLEN, FAULT SDA and SCL pulldown disabled |                          |     | 1    | μΑ   |

| V <sub>CHGOR</sub>    | CHG Over Ride active high |                                                                                | 0.8                      | 2   | 3.2  | V    |

| R <sub>PD(SMBx)</sub> | SDA and SCL pulldown      | $T_A = -40$ °C to 100°C                                                        | 600                      | 950 | 1300 | kΩ   |

| R <sub>PAD</sub>      | Pad resistance            | TS                                                                             |                          | 87  | 110  | Ω    |

## 7.6 Supply Current

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                       | PARAMETER     | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|-----------------------|---------------|-----------------------------------|-----|-----|-----|------|

| I <sub>CC</sub>       | Normal mode   | Firmware running, no flash writes |     | 660 |     | μΑ   |

| I <sub>SHUTDOWN</sub> | Shutdown mode | $T_A = -40$ °C to 110°C           |     | 0.5 | 1   | μΑ   |

## 7.7 REG27 LDO

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                         | PARAMETER                                | TEST C                     | ONDITIONS                                          | MIN  | TYP   | MAX  | UNIT |

|-------------------------|------------------------------------------|----------------------------|----------------------------------------------------|------|-------|------|------|

| V <sub>REG</sub> -      | Regulator output voltage                 | I <sub>REG27</sub> = 10 mA | $T_A = -40$ °C to 85°C                             | 2.5  | 2.7   | 2.75 | V    |

| V <sub>REG27IT</sub> -  | Negative-going POR voltage               | At REG27                   |                                                    | 2.22 | 2.35  | 2.34 | V    |

| V <sub>REG27IT+</sub>   | Positive-going POR voltage               | At REG27                   |                                                    | 2.25 | 2.5   | 2.6  | V    |

| ΔV <sub>(REGTEMP)</sub> | Regulator output change with temperature | I <sub>REG</sub> = 10 mA   | $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ |      | ±0.5% |      |      |

| $\Delta V_{(REGLINE)}$  | Line regulation                          | I <sub>REG</sub> = 10 mA   |                                                    |      | ±2    | ±4   | mV   |

| $\Delta V_{(REGLOAD)}$  | Load regulation                          | $I_{REG}$ = 0.2 to 10 mA   |                                                    |      | ±20   | ±40  | mV   |

| I <sub>(REGMAX)</sub>   | Current limit                            |                            |                                                    | 25   |       | 50   | mA   |

### 7.8 Coulomb Counter

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

| PARAMETER                       | TEST CONDITIONS        | MIN   | TYP    | MAX    | UNIT   |

|---------------------------------|------------------------|-------|--------|--------|--------|

| Input voltage range             |                        | -0.2  |        | 0.25   | V      |

| Conversion time                 | Single conversion      |       | 250    |        | ms     |

| Effective resolution            | Single conversion      | 15    |        |        | Bits   |

| Integral nonlinearity           | $T_A = -25$ °C to 85°C |       | ±0.007 | ±0.034 | %FSR   |

| Offset error <sup>(1)</sup>     | $T_A = -25$ °C to 85°C |       | 10     |        | μV     |

| Offset error drift              |                        |       | 0.3    | 0.5    | μV/°C  |

| Full-scale error <sup>(2)</sup> |                        | -0.8% | 0.2%   | 0.8%   |        |

| Full-scale error drift          |                        |       |        | 150    | PPM/°C |

| Effective input resistance      |                        | 2.5   |        |        | ΜΩ     |

<sup>(1)</sup> Post Calibration Performance

#### 79 ADC

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

| PARAMETER                     | TEST CONDITION        | MIN   | TYP   | MAX                      | UNIT   |

|-------------------------------|-----------------------|-------|-------|--------------------------|--------|

| Input voltage range           | TS, VC5               | -0.2  |       | 0.8 × V <sub>REG27</sub> | V      |

| Conversion time               |                       |       | 31.5  |                          | ms     |

| Resolution (no missing codes) |                       | 16    |       |                          | Bits   |

| Effective resolution          |                       | 14    | 15    |                          | Bits   |

| Integral nonlinearity         |                       |       |       | ±0.02                    | %FSR   |

| Offset error <sup>(1)</sup>   |                       |       | 70    | 160                      | μV     |

| Offset error drift            |                       |       | 1     |                          | μV/°C  |

| Full-scale error              | V <sub>IN</sub> = 1 V | -0.8% | ±0.2% | 0.4%                     |        |

| Full-scale error drift        |                       |       |       | 150                      | PPM/°C |

| Effective input resistance    |                       | 8     |       |                          | ΜΩ     |

(1) Channel to channel offset

<sup>(2)</sup> Uncalibrated performance. This gain error can be eliminated with external calibration.

## 7.10 External Capacitor Voltage Balance Drive

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

| PARAMETER              |                                    | TEST CONDITIONS                                                                                | MIN | TYP  | MAX | UNIT |

|------------------------|------------------------------------|------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                        |                                    | Capacitor voltage balance ON for VC1,<br>VCi – VCi + 1 = 4 V, where i = 1 to approximately 4   |     | 5.7  |     |      |

| 5                      | Internal pulldown resistance for   | Capacitor voltage balance ON for VC2,<br>VCi – VCi + 1 = 4 V, where = i = 1 to approximately 4 |     | 3.7  |     | 1.0  |

| R <sub>BAL_drive</sub> | external capacitor voltage balance | Capacitor voltage balance ON for VC3,<br>VCi – VCi + 1 = 4 V, where = i = 1 to approximately 4 |     | 1.75 |     | kΩ   |

|                        |                                    | Capacitor voltage balance ON for VC4,<br>VCi – VCi + 1 = 4 V, where = i = 1 to approximately 4 |     | 0.85 |     |      |

## 7.11 Capacitor Voltage Monitor

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

| PARAMETER                               | TEST CONDITIONS                       | MIN | TYP | MAX | UNIT |

|-----------------------------------------|---------------------------------------|-----|-----|-----|------|

| CARACITOR Voltage Macourement Acquirect | $T_A = -10^{\circ}C$ to $60^{\circ}C$ |     | ±10 | ±20 | \/   |

| CAPACITOR Voltage Measurement Accuracy  | $T_A = -40$ °C to 85°C                |     | ±10 | ±35 | mV   |

## 7.12 Internal Temperature Sensor

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                     | PARAMETER                   | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|-----------------------------|-----------------|-----|-----|-----|------|

| T <sub>(TEMP)</sub> | Temperature sensor accuracy |                 |     | ±3% |     | °C   |

## 7.13 Thermistor Measurement Support

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                  | PARAMETER               | TEST CONDITIONS | MIN | TYP  | MAX | UNIT   |

|------------------|-------------------------|-----------------|-----|------|-----|--------|

| R <sub>ERR</sub> | Internal resistor drift |                 |     | -230 |     | ppm/°C |

| R                | Internal resistor       | TS              |     | 17   | 20  | kΩ     |

#### 7.14 Internal Thermal Shutdown

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                      | PARAMETER <sup>(1)</sup>        | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------------|---------------------------------|-----------------|-----|-----|-----|------|

| T <sub>MAX</sub>     | Maximum REG27 temperature       |                 | 125 |     | 175 | °C   |

| T <sub>RECOVER</sub> | Recovery hysteresis temperature |                 |     | 10  |     | °C   |

<sup>(1)</sup> Parameters assured by design. Not production tested

## 7.15 High-Frequency Oscillator

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                    | PARAMETER                        | TEST CONDITIONS        | MIN | TYP    | MAX | UNIT |  |  |  |

|--------------------|----------------------------------|------------------------|-----|--------|-----|------|--|--|--|

| f <sub>(OSC)</sub> | Operating frequency of CPU clock |                        |     | 2.097  |     | MHz  |  |  |  |

| 4                  | Fraguency arror(1)               | $T_A = -20$ °C to 70°C | -2% | ±0.25% | 2%  |      |  |  |  |

| f <sub>(EIO)</sub> | Frequency error <sup>(1)</sup>   | $T_A = -40$ °C to 85°C | -3% | ±0.25% | 3%  |      |  |  |  |

| t <sub>(SXO)</sub> | Start-up time <sup>(2)</sup>     | $T_A = -25$ °C to 85°C |     | 3      | 6   | ms   |  |  |  |

<sup>(1)</sup> The frequency drift is included and measured from the trimmed frequency at VCC = VCC = 14.4 V, T<sub>A</sub> = 25°C

<sup>(2)</sup> The start-up time is defined as the time it takes for the oscillator output frequency to be ±3% when the device is already powered.

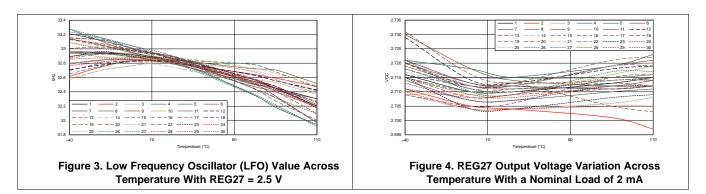

## 7.16 Low-Frequency Oscillator

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                     | PARAMETER                      | TEST CONDITIONS                              | MIN   | TYP    | MAX  | UNIT |

|---------------------|--------------------------------|----------------------------------------------|-------|--------|------|------|

| f <sub>(LOSC)</sub> | Operating frequency            |                                              |       | 32.768 |      | MHz  |

|                     | F(1)                           | $T_A = -20$ °C to 70°C                       | -1.5% | ±0.25% | 1.5% |      |

| †(LEIO)             | Frequency error <sup>(1)</sup> | $T_A = -40$ °C to 85°C                       | -2.5% | ±0.25% | 2.5% |      |

| t <sub>(LSXO)</sub> | Start-up time <sup>(2)</sup>   | $T_A = -25^{\circ}C \text{ to } 85^{\circ}C$ |       |        | 100  | ms   |

<sup>(1)</sup> The frequency drift is included and measured from the trimmed frequency at VCC = VCC = 14.4 V, T<sub>A</sub> = 25°C.

## 7.17 RAM Backup

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                    | PARAMETER                                 | TEST CONDITIONS                                                                            | MIN | TYP | MAX  | UNIT       |

|--------------------|-------------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|------|------------|

|                    | DDI data retention input current          | $V_{RBI} > V_{(RBI)MIN}$ , $V_{REG27} < V_{REG27IT}$ , $T_A = 70$ °C to 110°C              |     | 20  | 1500 | <b>~</b> ^ |

| I <sub>(RBI)</sub> | RBI data-retention input current          | $V_{RBI} > V_{(RBI)MIN}, V_{REG27} < V_{REG27IT-},$<br>$T_A = -40^{\circ}\text{C}$ to 70°C |     |     | 500  | nA         |

| V <sub>(RBI)</sub> | RBI data-retention voltage <sup>(1)</sup> |                                                                                            | 1   |     |      | V          |

<sup>(1)</sup> Specified by design. Not production tested.

## 7.18 Flash

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                          | PARAMETER <sup>(1)</sup>       | TEST CONDITIONS       | MIN | TYP | MAX | UNIT   |

|--------------------------|--------------------------------|-----------------------|-----|-----|-----|--------|

|                          | Data retention                 |                       | 10  |     |     | Years  |

|                          | Flash programming write-cycles |                       | 20k |     |     | Cycles |

| t <sub>(ROWPROG)</sub>   | Row programming time           |                       |     |     | 2   | ms     |

| t <sub>(MASSERASE)</sub> | Mass-erase time                |                       |     |     | 250 | ms     |

| t <sub>(PAGEERASE)</sub> | Page-erase time                |                       |     |     | 25  | ms     |

| I <sub>CC(PROG)</sub>    | Flash-write supply current     |                       |     | 4   | 6   | mA     |

| I <sub>CC(ERASE)</sub>   |                                | $T_A = -40$ °C to 0°C |     | 8   | 22  | A      |

|                          | Flash-erase supply current     | $T_A = 0$ °C to 85°C  |     | 3   | 15  | mA     |

<sup>(1)</sup> Specified by design. Not production tested

<sup>(2)</sup> The start-up time is defined as the time it takes for the oscillator output frequency to be ±3%.

## 7.19 Current Protection Thresholds

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                          | PARAMETER                                          | TEST C   | CONDITIONS         | MIN  | TYP | MAX  | UNIT |

|--------------------------|----------------------------------------------------|----------|--------------------|------|-----|------|------|

| \ /                      | OOD detection through ald and to account to be in- | RSNS = 0 |                    | 50   |     | 200  | >/   |

| $V_{(OCD)}$              | OCD detection threshold voltage range, typical     | RSNS = 1 |                    | 25   |     | 100  | mV   |

| A\/                      |                                                    | RSNS = 0 |                    |      | 10  |      | \/   |

| $\Delta V_{(OCDT)}$      | OCD detection threshold voltage program step       | RSNS = 1 |                    |      | 5   |      | mV   |

| \/                       | CCC detection throughold valters range tunical     | RSNS = 0 |                    | -100 |     | -300 | m)/  |

| $V_{(SCCT)}$             | SCC detection threshold voltage range, typical     | RSNS = 1 | RSNS is set in     | -50  |     | -225 | mV   |

| A\/                      |                                                    | RSNS = 0 | STATE_CTL register |      | -50 |      | \/   |

| $\Delta V_{(SCCT)}$      | SCC detection threshold voltage program step       | RSNS = 1 |                    |      | -25 |      | mV   |

| V                        | CCD detection threshold valtere range tunical      | RSNS = 0 |                    | 100  |     | 450  | m)/  |

| V <sub>(SCDT)</sub>      | SCD detection threshold voltage range, typical     | RSNS = 1 |                    | 50   |     | 225  | mV   |

| A\/                      |                                                    | RSNS = 0 |                    |      | 50  |      | \/   |

| $\Delta V_{(SCDT)}$      | SCD detection threshold voltage program step       | RSNS = 1 |                    |      | 25  |      | mV   |

| V <sub>(OFFSET)</sub>    | SCD, SCC and OCD offset                            |          |                    | -10  |     | 10   | m)/  |

| V <sub>(Scale_Err)</sub> | SCD, SCC and OCD scale error                       |          |                    | -10% |     | 10%  | mV   |

## 7.20 Current Protection Timing

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                          |                                                   |                                                                                                             | MIN  | NOM | MAX  | UNIT |

|--------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| t <sub>(OCDD)</sub>      | Overcurrent in discharge delay                    |                                                                                                             | 1    |     | 31   | ms   |

| t(OCDD_STEP)             | OCDD step options                                 |                                                                                                             |      | 2   |      | ms   |

|                          | Chart singuit in disabages dalar.                 | AFE.STATE_CNTL[SCDDx2] = 0                                                                                  | 0    |     | 915  |      |

| t(SCDD)                  | Short circuit in discharge delay                  | AFE.STATE_CNTL[SCDDx2] = 1                                                                                  | 0    |     | 1830 | μs   |

|                          | CCDD aton entions                                 | AFE.STATE_CNTL[SCDDx2] = 0                                                                                  |      | 61  |      |      |

| t(SCDD_STEP)             | SCDD step options                                 | AFE.STATE_CNTL[SCDDx2] = 1                                                                                  | 122  |     |      | μs   |

| t <sub>(SCCD)</sub>      | Short circuit in charge delay                     |                                                                                                             | 0    |     | 915  | μs   |

| t <sub>(SCCD_STEP)</sub> | SCCD step options                                 |                                                                                                             |      | 61  |      | μs   |

| t <sub>(DETECT)</sub>    | Current fault detect time                         | $V_{SRP-SRN} = V_{THRESH} + 12.5 \text{ mV},$<br>$T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$ |      | 35  | 160  | μs   |

|                          | Oversument and short sirewit                      | Accuracy of typical delay time with WDI active                                                              | -20% |     | 20%  |      |

| t <sub>ACC</sub>         | Overcurrent and short circuit delay time accuracy | Accuracy of typical delay time with no WDI input                                                            | -50% |     | 50%  |      |

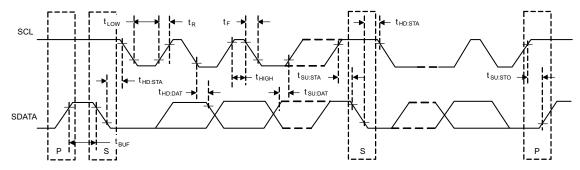

## 7.21 Timing Requirements: SMBus

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = VCC = 14.4 V, Minimum and maximum values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = VCC = 3.8 V to 25 V (unless otherwise noted)

|                       |                                         |                                        | MIN | NOM  | MAX  | UNIT |

|-----------------------|-----------------------------------------|----------------------------------------|-----|------|------|------|

| f <sub>SMB</sub>      | SMBus operating frequency               | Slave mode, SCL 50% duty cycle         | 10  |      | 100  | kHz  |

| f <sub>MAS</sub>      | SMBus master clock frequency            | Master mode, no clock low slave extend |     | 51.2 |      | kHz  |

| t <sub>BUF</sub>      | Bus free time between start and stop    |                                        | 4.7 |      |      | μs   |

| t <sub>HD:STA</sub>   | Hold time after (repeated) start        |                                        | 4   |      |      | μs   |

| t <sub>SU:STA</sub>   | Repeated start setup time               |                                        | 4.7 |      |      | μs   |

| t <sub>SU:STO</sub>   | Stop setup time                         |                                        | 4   |      |      | μs   |

|                       | Data hald Care                          | Receive mode                           | 0   |      |      |      |

| t <sub>HD:DAT</sub>   | Data hold time                          | Transmit mode                          | 300 |      |      | ns   |

| t <sub>SU:DAT</sub>   | Data setup time                         |                                        | 250 |      |      | ns   |

| t <sub>TIMEOUT</sub>  | Error signal and detect                 | See (1)                                | 25  |      | 35   | ms   |

| $t_{LOW}$             | Clock low period                        |                                        | 4.7 |      |      | μs   |

| t <sub>HIGH</sub>     | Clock high period                       | See (2)                                | 4   |      | 50   | μs   |

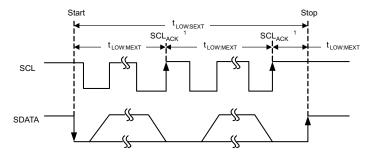

| t <sub>LOW:SEXT</sub> | Cumulative clock low slave extend time  | See (3)                                |     |      | 25   | ms   |

| t <sub>LOW:MEXT</sub> | Cumulative clock low master extend time | See <sup>(4)</sup>                     |     |      | 10   | ms   |

| t <sub>F</sub>        | Clock and data fall time                | See (5)                                |     |      | 300  | ns   |

| t <sub>R</sub>        | Clock and data rise time                | See <sup>(6)</sup>                     |     |      | 1000 | ns   |

- The bq33100 times out when any clock low exceeds  $t_{TIMEOUT}$   $t_{HIGH}$  maximum is the minimum bus idle time. SCL = SDA = 1 for t > 50  $\mu$ s causes reset of any transaction involving bq33100 that is in (2) progress.

- $L_{\text{LOW:SEXT}}$  is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.  $t_{\text{LOW:MEXT}}$  is the cumulative time a master device is allowed to extend the clock cycles in one message from initial start to the stop. Rise time  $t_{\text{R}} = V_{\text{ILMAX}} 0.15$ ) to  $(V_{\text{IHMIN}} + 0.15)$  Fall time  $t_{\text{F}} = 0.9V_{\text{DD}}$  to  $(V_{\text{ILMAX}} 0.15)$

- (5)

Figure 1. SMBus Timing

Figure 2. SMBus t<sub>TIMEOUT</sub>

# 7.22 Typical Characteristics

## 8 Detailed Description

#### 8.1 Overview

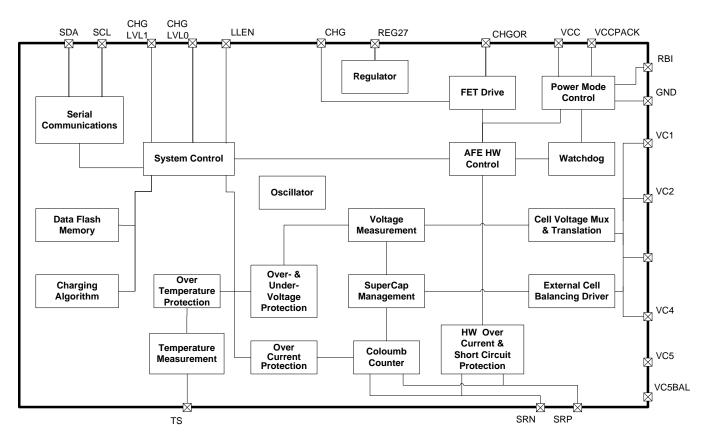

The bq33100 is a Super Capacitor monitor, balancing controller and overall system manger. The device can individually monitor up to 5 series capacitors and up to 9 when monitoring the total stack.

The device can also interact with a external charging solution to provide Capacitance and Effective Series Resistance (ESR) data on the stack.

#### NOTE

The following notation is used in this document, if SBS commands and Data Flash values are mentioned within a text block:

- SBS commands are set in italic, for example: Voltage

- SBS bits and flags are capitalized, set in italic and enclosed with square brackets, for example: [SS]

- Data Flash values are set in bold italic, for example: OV Threshold

- All Data Flash bits and flags are capitalized, set in bold italic and enclosed with square brackets, for example: [OV]

All SBS commands, Data Flash values and flags mentioned in a chapter are listed at the beginning of each chapter for reference.

The reference format for SBS commands is:

SBS:Command Name(Command No.):Manufacturer Access(MA No.)[Flag], for example:

SBS:Voltage(0x09), or SBS:ManufacterAccess(0x00):Seal Device(0x0020)

## 8.1.1 Super Capacitor Measurements

The bq33100 measures the series capacitor voltages or stack voltage, current and temperature using a deltasigma analog-to-digital converter (ADC). The bq33100 uses this measured data and advanced algorithms to determine the State-of-Health and available capacitance of the Super Capacitor.

## 8.1.1.1 Voltage

The bq33100 has two separate modes, Normal mode and Stack mode, where measurements and taken and managed differently. The setting of *Operation Cfg [STACK]* to 1 enables Stack mode otherwise the bq33100 operates in normal mode.

The bq33100 updates the individual series capacitor voltages and stack voltage at one (1) second intervals when in Normal mode and measurers the stack voltage at one (1) second intervals when in Stack mode. The internal ADC of the bq33100 measures the voltage, scales, and offsets, and calibrates it appropriately. To ensure an accurate differential voltage sensing, the IC ground must be connected directly to the most negative terminal of the Super Capacitor stack, not to the positive side of the sense resistor. This minimizes the voltage drop across the PCB trace.

## 8.1.1.2 Current, Charge and Discharge Counting

The delta-sigma ADC measures the system current of the Super Capacitor by measuring the voltage drop across a small-value sense resistor (typically 5 m $\Omega$  to 20 m $\Omega$  typical) between the SRP and SRN pins. The ADC measures bipolar signals from -0.20 V to 0.25 V.

#### 8.1.1.3 Device Calibration

The bq33100 requires voltage calibration to maximize accuracy of the monitoring system, the bq33100 evaluation software can perform this calibration. The external filter resistors, connected from each capacitor to the VCx input of the bq33100, are required to be 1 k $\Omega$ .

The bq33100 can automatically calibrate its offset between the A to D converter and the input of the high voltage translation circuit during normal operation for maximum capacitor voltage measurement accuracy.

## **Overview (continued)**

### 8.1.1.4 Temperature

The bq33100 has an internal temperature sensor and input for an external temperature sensor input, TS. The external input is used in conjunction with an NTC thermistor (default is Semitec 103AT) to sense the Super Capacitor temperature. The bq33100 can be configured to use internal or external temperature sensors.

## 8.1.1.5 Series Capacitor Configuration

The bq33100 can be used to monitor 2, 3, 4 or 5 capacitors in series. The appropriate connectivity for the different options are detailed in Table 1.

**Table 1. Series Capacitor Connectivity**

| bq33100 PIN | 5-SERIES                            | 4-SERIES                            | 3-SERIES                            | 2-SERIES                            |

|-------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| VC1         | P of Top (5th) Cap                  | P of 4th Cap                        | Short to VC2                        | Short to VC2                        |

| VC2         | P of 4th Cap, N of 5th Cap          | P of 3rd Cap, N of 4th<br>Cap       | P of 3rd Cap                        | Short to VC3                        |

| VC3         | P of 3rd Cap, N of 4th Cap          | P of 2nd Cap, N of 3rd<br>Cap       | P of 2nd Cap, N of 3rd Cap          | P of 2nd Cap                        |

| VC4         | P of 2nd Cap, N of 3rd Cap          | P of Bottom (1st) Cap, N of 2nd Cap | P of Bottom (1st) Cap, N of 2nd Cap | P of Bottom (1st) Cap, N of 2nd Cap |

| VC5         | P of Bottom (1st) Cap, N of 2nd Cap | N of Bottom Cap (1st)               | N of Bottom Cap (1st)               | N of Bottom Cap (1st)               |

| VSS         | N of Bottom Cap (1st)               | Short to VC5                        | Short to VC5                        | Short to VC5                        |

#### NOTE

The CC0...CC2 bits in Operation Cfg must be programmed to match the corresponding configuration.

When in Stack mode (Operation Cfg [STACK] =1) VC1 must be connected to VC2 and VC3 connected to VC4. Additionally a *divide-by-2* resistor divider must connect between the top and bottom of the capacitor array with VC1,2 being the top and VC3,4 being the middle and VSS being the bottom. In this configuration pins VC5 and VC5BAL are not used and must be connected to VSS.

### 8.2 Functional Block Diagram

## 8.3 Feature Description

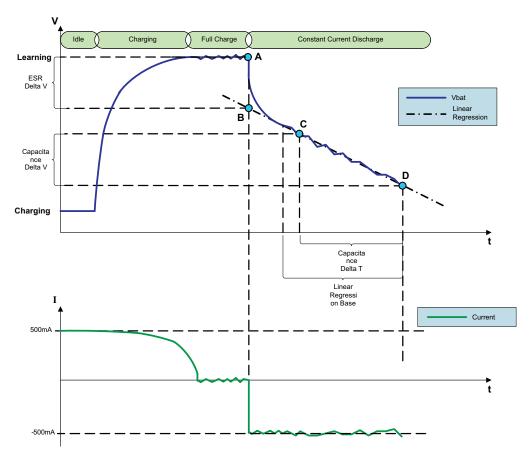

## 8.3.1 Capacitance Monitoring and Learning

## 8.3.1.1 Monitoring and Control Operational Overview

The bq33100 periodically determines the capacitance and equivalent series resistance (ESR) of the super capacitor array during normal operation. The *Learning Frequency* is a register that sets the time between automatic learning cycles of the Super Capacitor which can also be manually executed by issuing a *Learn* command. The bq33100 uses the learning cycles to update the *Capacitance* and *ESR* registers accordingly and both are accessible through the SMBus interface.

Learning process is a multi-step procedure fully controlled by the bq33100 that will perform the following sequence to learn Capacitance and ESR:

- 1. Charge to V Learn Max

- Discharge using constant current load to a minimum voltage of the present charging voltage and internally record voltage and time

- 3. Charge to V Learn Max

- 4. Discharge using constant current load and internally record current and time

- 5. Calculate Capacitance and ESR based on recorded voltage and current

- 6. Determine new Charging Voltage

## **Feature Description (continued)**

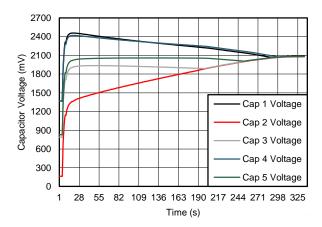

Figure 5. Voltage as Current During Learning

where:

$$C = I \times (t[D] - t[C])/(V[C] - V[D]) \tag{1}$$

and

$$ESR = (V[A]-V[B])/I \tag{2}$$

### 8.3.1.2 Main Monitoring Registers

**Capacitance** represents the total capacitance in the capacitor array and presents the value in units of F (Farads) to 1 decimal place.

On initialization, the bq33100 sets *Capacitance* to the data flash value stored in *Initial Capacitance*. During subsequent learning cycles, the bq33100 updates *Capacitance* with the last measured capacitance of the . Once updated, the bq33100 writes the new *Capacitance* value to data flash to *Capacitance*. *Capacitance* represents the full Super Capacitor reference for relative state of charge calculations.

InitialCapacitance — The first updated value of Super Capacitor capacitance and represented in units of F.

RelativeStateOfCharge (RSOC) represents the % of available energy. Use Equation 3 to calculate the RSOC.

**Learning Frequency** — The Learning Frequency register sets the time between automatic learning cycles of the Super Capacitor which can also be manually executed by issuing a *ManufacturerAccess Learn* command. The bq33100 uses the learning cycles to measure the Super Capacitor capacitance and update the Capacitance register accordingly. When the bq33100 is in Unsealed Mode then a value of 250 is used to set the Learning Frequency to 10 minutes for test purposes.

## **Feature Description (continued)**

### 8.3.1.3 Initial Capacitance at Device Reset

The bq33100 estimates the initial capacitance of a at device reset, which is the case when the capacitors are first attached to the application circuit. This gives a reasonably accurate Capacitance and RSOC value, however, Super Capacitor capacitance learning is required in order to improve the accuracy of Capacitance and RSOC.

### 8.3.1.4 Qualified Capacitance Learning

The bq33100 updates Capacitance with an amount based on the value learned during a qualified learning cycle. Once updated, the bq33100 writes the new *Capacitance* value to data flash to *Capacitance*.

The bq33100 sets [CL] = 1 and clears [LPASS] in Operation Status when a qualified capacitance learning cycle begins. The period of time that the learning takes is set by **CL Time** although the first learning cycle after a device reset will not occur until after an elapsed time of **Learning Frequency**. When a qualified learn has occurred [LPASS] in Operation Status is set.

During the learning process there are specific timeouts to protect from over charge or over discharge of the super capacitor array. At the beginning of each phase of charge and discharge a timer is started. If the timer exceeds *Max Discharge Time* during the discharging phase then *Operation Status [LDTO]* is set if the timer exceeds *Max Charge Time* for the charging phase then *Operation Status [LCTO]* is set, the flags are cleared upon the beginning of the next learning cycle.

#### 8.3.1.5 Health Determination

The bq33100 uses Equation 4 to determine the relative health of the capacitor.

Health = (Capacitance / InitialCapacitance)

(4)

The bq33100 will determine a new *ChargingVoltage* at end of the learning cycle based on the newly learned *Capacitance*. The following warnings will be set based on the changes in *ChargingVoltage* and the capacitors ability to provide the minimum power needs.

Charging Voltage = V Chg Nominal then Safety Status [HLOW], [HWARN] and [HFAIL] are cleared.

If Charging Voltage is set to V Chg A or V Chg B then Safety Status [HLOW] is set.

If Charging Voltage is set to **V Chg Max** then Safety Status [HWARN] is set.

If Charging Voltage is set to **V Chg Max** and the bq33100 determines that the newly learned Capacitance cannot provide the minimum power requirements then SafetyStatus [HFAIL] is set.

The minimum power requirements is determined by the *Min Power*, *Required Time* and *Min Voltage* data flash values.

If the corresponding **[HLOW]**, **[HWARN]** or **[HFAIL]** bits are set in **FAULT** when the **SafetyStatus[HLOW]** or **[HWARN]** bit is set then the FAULT pin is set.

## 8.3.1.6 ESR Measurement

The bq33100 measures the voltage on the capacitor stack when the LLEN pin (pin 17) is high with the initial learned value stored in *Initial ESR* which is only updated once. The LLEN pin is controlled by firmware to enable a circuit that presents a constant current load to the full capacitor stack. With the known voltage and known current the ESR of the capacitor array can be determined. The final reported value of *ESR* is also adjusted by the data flash value of *ESR Offset*. The original value of the capacitor array *ESR* is stored in *Design ESR* but is not used by the bq33100.

The final value of *ESR* can be read from the bq33100 through *ESR* which is in  $m\Omega$ .

## 8.3.1.7 Monitor Operating Modes

Entry and exit of each mode is controlled by data flash parameters. In Discharge Mode, the [DSG] flag in Operation Status is set. Discharge mode is entered when Current goes below (-)Dsg Current Threshold. Discharge mode is exited when Current goes above Chg Current Threshold threshold for more than 1 second.

Charge mode is entered when *Current* goes above *Chg Current Threshold*. Charge mode is exited when *Current* goes below *Dsg Current Threshold* for more than 1 second.

## **Feature Description (continued)**

## 8.3.2 Capacitor Voltage Balancing

Capacitor voltage balancing in the bq33100 is accomplished by connecting an external parallel bypass load to each capacitor, and enabling the bypass load depending on each individual capacitors voltage level. The bypass load is typically formed by a P-ch MOSFET and a resistor connected in series across each capacitor. The filter resistors that connect the capacitor tabs to VC1 to approximately VC4 pins of the bq33100 are required to be 1 k ohms to support this function on all capacitors other than the lowest. The lowest capacitor bypass is enabled through the VC5BAL pin. Capacitor Voltage Balancing is only operational after the *ManufacturerAccess* Lifetime and Capacitor Balancing Enable (0x21) command is sent to the bq33100.

Using this circuit, the bq33100 balances the capacitors during charge and after charge termination by discharging those capacitors with voltage above the threshold set in *CB Threshold* and if the  $\Delta V$  in capacitor voltages exceeds the value programmed in *CB Min*. During capacitor voltage balancing, the bq33100 measures the capacitor voltages periodically (during which time the voltage balancing circuit is turned off) and based on the capacitor voltages, the bq33100 selects the appropriate capacitor to discharge. When  $\Delta V$  of *CapacitorVoltage5...1* < *CB Min* then capacitor voltage balancing stops. Capacitor voltage balancing restarts when  $\Delta V$  of *CapacitorVoltage5...1*  $\geq$  *CB Restart* to avoid balancing start-stop oscillations.

Capacitor voltage balancing only occurs when:

- Charging current is detected (Current > Chg Current Threshold OR

- The [FC] flag in OperationStatus has been set AND

- ΔCapacitorVoltage5...1 ≥ CB Restart

Capacitor voltage balancing stops when:

- ΔCapacitorVoltage5...1 < **CB Min**

- Discharging current detected (Current > Dsg Current Threshold)

This feature is disabled when in Stack mode, when *Operation Cfg [STACK]* =1.

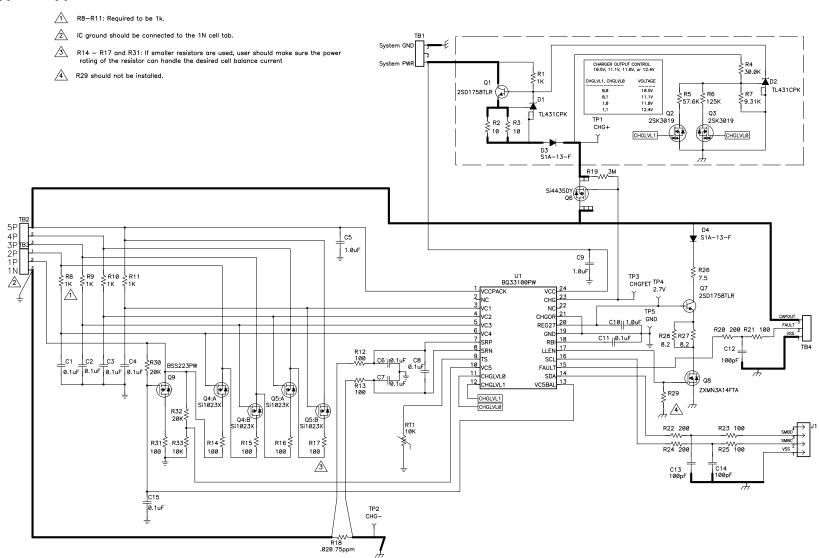

#### 8.3.3 Charge Control

The bq33100 supports two main charge control architectures, discrete control and smart control. In a discrete charge control implementation the CHGLVL0 and CHGLVL1 pins can be used to adjust the charging voltage of an external supply (see reference schematic for example).

As the super capacitors age a higher charging voltage can be configured to offset the deteriorating super capacitor ESR and Capacitance due to aging. With the discrete control method there are 4 levels of charging voltages that can be chosen, **V Chg Nominal**, **V Chg A**, **V Chg B** and **V Chg Max**. The setting of the charging voltage is determined by the value of the latest determined required *Charging Voltage*.

The CHGLVL0 and CHGLVL1 pin states are defined by the V Chg X parameters selected per Table 2:

**Table 2. ChargingVoltage Parameters**

| CHARGINGVOLTAGE | CHGLVL1 (PIN 12) | CHGLVL0 (PIN11) |

|-----------------|------------------|-----------------|

| V Chg Nominal   | 0                | 0               |

| V Chg A         | 0                | 1               |

| V Chg B         | 1                | 0               |

| V Chg Max       | 1                | 1               |

In a smart control architecture the bq33100 makes the appropriate maximum charging current and charging voltage per the charging algorithm available through the *ChargingCurrent* and *ChargingVoltage* SMBus commands respectively. This enables either an SMBus master or smart charger to manage the charging of the super capacitor pack.

## 8.3.3.1 Charge Termination

The bq33100 determines charge termination if:

- The average charge current < Taper Current during 2 consecutive Current Taper Window time periods, AND

- Voltage + Taper Voltage ≥ ChargingVoltage

#### NOTE

To make sure that the charge terminates properly, TI recommends that *Taper Current* be set to a value greater than the maximum charger voltage inaccuracy. In other words, the charger taper current must be set to a lower value than the taper current programmed in the dataflash to ensure proper charge termination and the FC bit gets set.

The bq33100 sets the [FC] flag in Operation Status when a valid charge termination occurs and cleared when RelativeStateOfCharge is less than FC Clear %.

The *taper voltage* must be set to a value less than the *OV threshold*. This prevents an over voltage condition from occurring after the CL bit clears upon learning completion.

The bq33100 can also determine charge termination if the RSOC is at a value equal to or greater than *FC set* %. If this is not the desired means of charge termination, *FC set* % must be set to -1%.

#### 8.3.3.2 CHG Over Ride Control

During the normal operation of the bq33100 the CHG output of the bq33100 is typically controlled automatically but can be over ridden through the CHGOR pin (pin 21). On a low-to-high transition the CHG output is released turning off the external CHG FET and on a high-to-low transition the CHG output is pulled low after a programmable delay **CHG Enable Delay**. If **CHG Enable Delay** is programmed to 0 the delay is a maximum of 250 ms. If the CHG over ride function is not needed then the CHGOR pin must connect to VSS.

## 8.3.4 Lifetime Data Gathering

## 8.3.4.1 Lifetime Maximum Temperature

During the operation lifetime of the bq33100 it gathers temperature data. During this time the bq33100 can be enabled to record the maximum value that the measured temperature reached. If the [LTE] flag is set in OperationStatus, **Lifetime Max Temp** value is updated if one of the following conditions are met:

- internal measurement temperature Lifetime Max Temp > 1 °C.

- internal measurement temperature > Lifetime Max Temp for a period > 60 seconds

- internal measurement temperature > Lifetime Max Temp AND any other lifetime value is updated.

**Table 3. Lifetime Maximum Temperature**

| SUBCL |   | SUBCLASS<br>NAME | OFFSET | NAME                 | FORMAT  | SIZE IN<br>BYTES | MIN<br>VALUE | MAX<br>VALUE | DEFAULT<br>VALUE | UNIT  |

|-------|---|------------------|--------|----------------------|---------|------------------|--------------|--------------|------------------|-------|

| 59    | ) | Lifetime Data    | 0      | Lifetime Max<br>Temp | Integer | 2                | 0            | 1400         | 350              | 0.1°C |

## 8.3.4.2 Lifetime Minimum Temperature

During the operation lifetime of the bq33100 it gathers temperature data. During this time the bq33100 can be enabled to record the Minimum value that the measured temperature reached. If the [*LTE*] flag is set, *Lifetime Min Temp* is updated if one of the following conditions are met:

- Lifetime Min Temp internal measurement temperature > 1 °C.

- Lifetime Min Temp > internal measurement temperature for a period > 60 seconds

- Lifetime Min Temp > internal measurement temperature > AND any other lifetime value is updated.

## **Table 4. Lifetime Minimum Temperature**

| SUBCLASS<br>ID | SUBCLASS<br>NAME | OFFSET | NAME                 | FORMAT  | SIZE IN<br>BYTES | MIN<br>VALUE | MAX<br>VALUE | DEFAULT<br>VALUE | UNIT  |

|----------------|------------------|--------|----------------------|---------|------------------|--------------|--------------|------------------|-------|

| 59             | Lifetime Data    | 2      | Lifetime Min<br>Temp | Integer | 2                | -600         | 1400         | 50               | 0.1°C |

### 8.3.4.3 Lifetime Maximum Capacitor Voltage

During the operation lifetime of the bq33100 it gathers voltage data and if in Single mode (*Operation Cfg [STACK ]* =0). During this time the bq33100 can be enabled to record the Maximum value that the measured voltage reached. If the [*LTE*] flag is set, *Lifetime Max Capacitor Voltage* is updated if one of the following conditions are met:

- any internally measured capacitor voltage Lifetime Max Capacitor Voltage > 25 mV

- any internally measured capacitor voltage > Lifetime Max Capacitor Voltage for a period > 60 seconds

- any internally measured capacitor voltage Lifetime Max Capacitor Voltage AND any other lifetime value is updated.

**Table 5. Lifetime Max Capacitor Voltage**

| SUBCLASS ID | SUBCLASS<br>NAME | OFFSET | NAME                                 | FORMAT  | SIZE IN<br>BYTES | MIN<br>VALUE | MAX<br>VALUE | DEFAULT<br>VALUE | UNIT |

|-------------|------------------|--------|--------------------------------------|---------|------------------|--------------|--------------|------------------|------|

| 59          | Lifetime Data    | 4      | Lifetime Max<br>Capacitor<br>Voltage | Integer | 2                | 0            | 32767        | 0                | mV   |

#### 8.3.5 Safety Detection Features

The bq33100 supports a wide range of Super Capacitor and system safety detection and protection features that are easily configured or enabled through the integrated data flash. These features are intended, through various configuration options, to provide a level of safety from external influences causing damage to components with the power path, for example: limiting the period of time the CHG FET is exposed to high current pulse charge conditions

### 8.3.5.1 Capacitor Overvoltage (OV)

The bq33100 can detect capacitor overvoltage condition and protect capacitors from damage.

When any CapacitorVoltage5...1 exceeds (ChargingVoltage / number of capacitors (see **Operation Cfg** [CC2,1,0]) + OV Threshold) the [OV] flag in SafetyAlert is set.

When any CapacitorVoltage5...1 exceeds (ChargingVoltage / number of capacitors (see **Operation Cfg** [CC2,1,0]) + OV Threshold) for a period greater than OV Time the [OV] flag in SafetyStatus is set.

When the bq33100 is configured for Pack Mode, when *Operation Cfg [STACK]* =1, then a fault is detected when *Voltage* exceeds (*ChargingVoltage* + *OV Threshold*) the [OV] flag in *SafetyAlert* is set.

When the bq33100 is configured for Pack Mode, when *Operation Cfg [STACK]* =1, then a fault is detected when *Voltage* exceeds (*ChargingVoltage* + *OV Threshold*) for a period greater than *OV Time* the [OV] flag in *SafetyStatus* is set.

This function is disabled if **OV Time** is set to zero.

In an overvoltage condition charging is disabled and the CHG FET is turned off, *ChargingCurrent* and *ChargingVoltage* are set to zero.

The bq33100 recovers from a capacitor overvoltage condition if all *CapacitorVoltages5..1* are equal to or lower than (*ChargingVoltage /* number of capacitors (see *Operation Cfg [CC2,1,0]*) + *OV Recovery*. If the bq33100 is configured for Pack Mode then the recover occurs when *Voltage* is equal to or lower than (*ChargingVoltage* + *OV Recovery*.

On recovery the [OV] flag is reset, and ChargingCurrent and ChargingVoltage are set back to appropriate values per the charging algorithm.

#### NOTE

When *ChargingVoltage* has been set to 0 due to a detected condition then the capacitor overvoltage function is suspended.

## 8.3.5.2 Capacitor Voltage Imbalance (CIM)

The bq33100 starts capacitor voltage imbalance detection when *Current* is less than or equal to *CIM Current* AND ALL *CapacitorVoltage5..1* > *Min CIM Check Voltage*.

When the difference between highest capacitor voltage and lowest capacitor voltage exceeds **CIM Fail Voltage** the [CIM] flag in SafetyAlert is set.

When the difference between highest capacitor voltage and lowest capacitor voltage exceeds **CIM Fail Voltage** for a period greater than **CIM Time** the [CIM] flag in SafetyStatus is set and ChargingCurrent and ChargingVoltage are set to 0 and the CHG FET is turned off. SafetyStatus() [CIM] is cleared and CHG FET is allowed to turn ON when the differences between the highest capacitor voltage and lowest capacitor voltage is less than **CIM Recovery**.

This function is disabled if **CIM Time** is set to zero.

The capacitor voltage imbalance detection is cleared when the difference between highest capacitor voltage and lowest capacitor voltage is less than *CIM Fail Voltage*. When this is detected then the CHG FET is allowed to be turned on, if other safety and configuration states permit, *ChargingCurrent* and *ChargingVoltage* are set to the appropriate value per the charging algorithm, and the *[CIM]* flag in *SafetyStatus* is reset.

### 8.3.5.3 Weak Capacitor (CLBAD)

When the capacitor array has been fully charged (indicated by *OperationStatus [FC]* being set) then it is monitored for excessive leakage.

When Current exceeds CLBAD Current the [CLBAD] flag in SafetyAlert is set.

When Current exceeds CLBAD for a period greater than CLBAD Time the [CLBAD] flag in SafetyStatus is set.

This function is disabled if **CLBAD Time** is set to zero.

In a weak capacitor condition charging is disabled and the CHG FET is turned off, *ChargingCurrent* and *ChargingVoltage* are set to zero.

The weak capacitor fault is cleared when *Current* falls equal to or below the *CLBAD Recovery* limit. When the recovery condition is detected, then the CHG FET is allowed to be turned on, if other safety and configuration states permit, *ChargingCurrent* and *ChargingVoltage* are set to the appropriate value per the charging algorithm, and the *[CLBAD]* flag in *SafetyStatus* is reset.

## 8.3.5.4 Overtemperature (OT)

The bq33100 has overtemperature protection to prevent charging at excessive temperatures.

When Temperature exceeds OT Chg the [OT] flag in SafetyAlert is set.

When Temperature exceeds OT Chg for a period greater than OT Chg Time the [OT] flag in SafetyStatus is set.

This function is disabled if *OT Chg Time* is set to zero.

In an overtemperature condition charging is disabled and the CHG FET is turned off, *ChargingCurrent* and *ChargingVoltage* are set to zero.

The overtemperature fault is cleared when *Temperature* falls equal to or below the *OT Chg Recovery* limit. When the recovery condition is detected, then the CHG FET is allowed to be turned on, if other safety and configuration states permit, *ChargingCurrent* and *ChargingVoltage* are set to the appropriate value per the charging algorithm, and the *[OT]* flag in *SafetyStatus* is reset.

## 8.3.5.5 Overcurrent During Charging (OC Chg)

The bg33100 has an independent level of recoverable overcurrent protection during charging.

When Current exceeds OC Chg the [OCC] flag in SafetyAlert is set.

When Current exceeds **OC Chg** for a period greater than **OC Chg Time** the [OCC] flag in SafetyStatus is set and ChargingCurrent and ChargingVoltage are set to 0.

This function is disabled if *OC Chg Time* is set to zero.

The overcurrent fault is cleared when *Current* falls below *OC Chg Recovery*. When a charging-fault recovery condition is detected, then the CHG FET is allowed to be turned on, if other safety and configuration states permit, *ChargingCurrent* and *ChargingVoltage* are set to the appropriate value per the charging algorithm, and the *[OCC]* flag in *SafetyStatus* is reset.

### 8.3.5.6 Overcurrent During Discharging (OC Dsg)

The bq33100 overcurrent is discharge detection executed by the integrated AFE is configured by the bq33100 data flash *OC Dsg* and *OC Dsg Time* registers.

When the integrated AFE detects a overcurrent in discharge condition the charge FET is turned off and the [OCD] flag in SafetyStatus is set, the internal current recovery timer is reset and ChargingCurrent and ChargingVoltage are set to 0.

The recovery is controlled by the bq33100 and requires that *Current* be  $\leq$  *OC Dsg Recovery* threshold and that the internal AFE current recovery timer  $\geq$  *Current Recovery Time*.

When the recovery condition is detected, *ChargingCurrent* and *ChargingVoltage* are set to the appropriate value per the charging algorithm, and the *[OCD]* flag in *SafetyStatus* is reset.

## 8.3.5.7 Short-Circuit During Charging (SC Chg)

The bq33100 short-circuit during charging protection is executed by the integrated AFE is configured by the bq33100 data flash **SC Chg Cfg** register.

When the integrated AFE detects a short circuit fault the charge FET is turned off and the [SCC] flag in SafetyStatus is set, the internal current recovery timer is reset and ChargingCurrent and ChargingVoltage are set to 0.

The recovery is controlled by the bq33100 and requires that AverageCurrent be  $\leq$  **SC Recovery** threshold and that the internal AFE current recovery timer  $\geq$  **Current Recovery Time**.

When the recovery condition is detected, *ChargingCurrent* and *ChargingVoltage* are set to the appropriate value per the charging algorithm, and the *[SCC]* flag in *SafetyStatus* is reset.

### 8.3.5.8 Short-Circuit During Discharging (SC Dsg)

The bq33100 short-circuit during discharging detection is executed by the integrated AFE is configured by the bq33100 data flash **SC Dsg Cfg** register.

When the integrated AFE detects a short circuit fault the charge FET is turned off and the [SCD] flag in SafetyStatus is set, the internal current recovery timer is reset and ChargingCurrent and ChargingVoltage are set to 0.

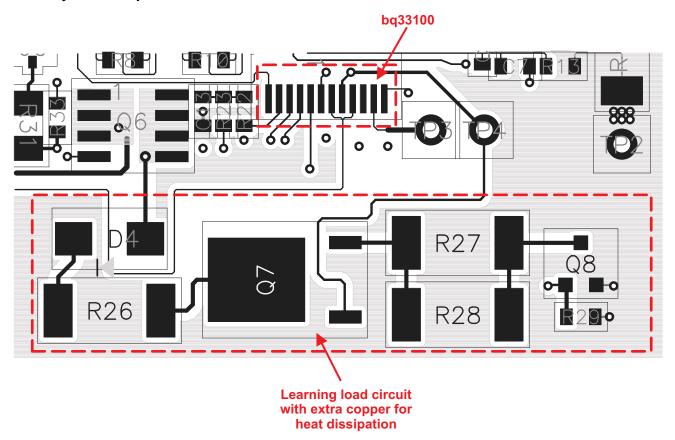

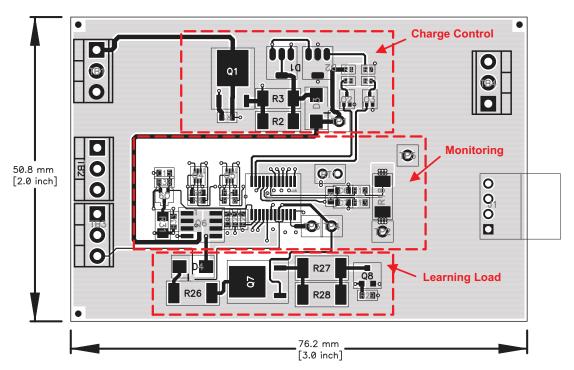

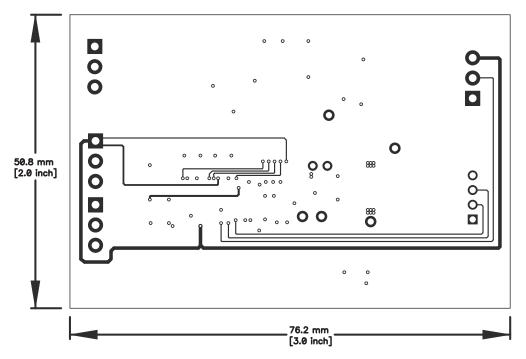

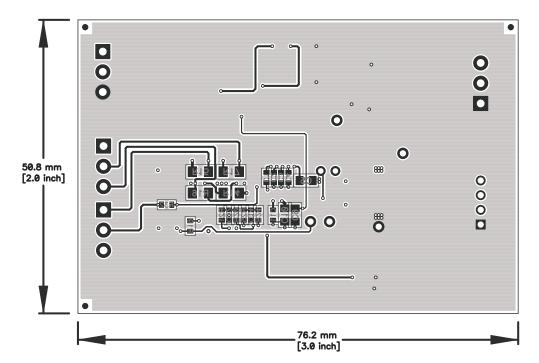

The recovery is controlled by the bq33100 and requires that *Current* be  $\leq$  *SC Recovery* threshold and that the internal AFE current recovery timer  $\geq$  *Current Recovery Time*.