ADS131B23

ZHCSR89A - DECEMBER 2022 - REVISED AUGUST 2023

## ADS131B23 具有 SPI 和 3 个 ADC 通道且 用于电压、电流和温度检测的高压电池包监测器

## 1 特性

**TEXAS**

INSTRUMENTS

- 两个用于电流分流测量的同步采样 24 位 ADC (ADC1A、ADC1B)

- 可编程满标量程:

- ±39mV 至 ±312.5mV

- 支持多种分流电阻器值和电流测量范围

- 通过以下特性实现高精度电流分流测量:

- 失调电压误差:±1.5µV(最大值)

- 增益漂移: 20ppm/°C (最大值)

- 可编程数据速率: 500SPS 至 64kSPS

- 每个 ADC 具有可编程阈值的数字过流比较器, 可实现快速过流检测

- 一个用于电压和温度测量的多路复用 16 位 ADC (ADC2A)

- 8路模拟输入

- 可编程满量程范围:

- ±312.5mV 至 ±1.25V

- 通道序列发生器

- 监控和诊断功能,用于缓解和检测随机硬件故障

- 电源电压范围: 2.9V 至 16V •

- 与 SPI 兼容的接口

- 9 个具有 PWM 功能的 GPIO

## 2 应用

- 电池储能系统 (ESS):

- 电流分流测量

- 使用外部电阻分压器实现电压测量

- 使用热敏电阻或模拟输出温度传感器实现温度测 量

## 3 说明

录。

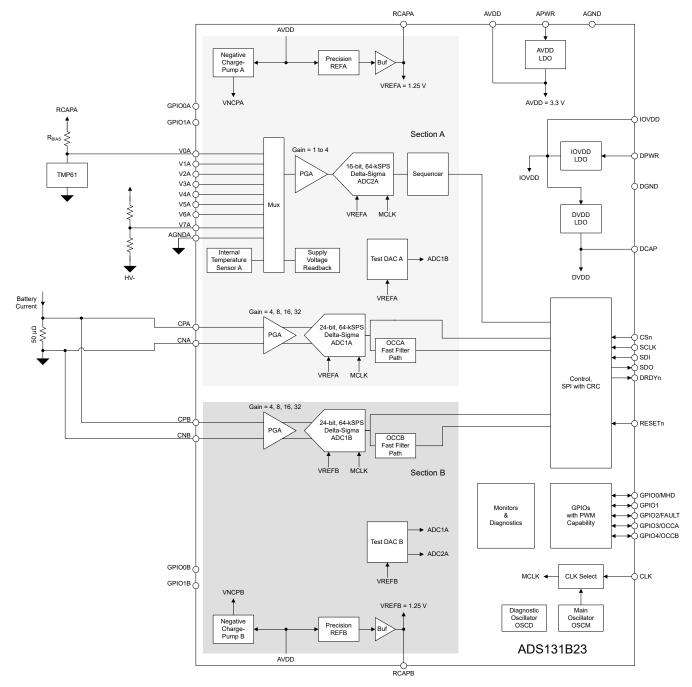

ADS131B23 是一款适用于工业电池管理系统 (BMS) 的完全集成式高压电池包监测器。

ADS131B23 集成两个同步采样、高精度、24 位 ADC 通道(ADC1A、ADC1B),可使用外部分流电阻器来 以高分辨率和高精度测量电池电流。两个独立的数字比 较器可与两个 ADC 并联来实现快速过流检测。

#### 封装信息

| 器件型号      | <b>封装</b> <sup>(1)</sup> | 封装尺寸 <sup>(2)</sup> |

|-----------|--------------------------|---------------------|

| ADS131B23 | PHP(HTQFP、<br>48)        | 9mm × 9mm           |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

(2) 封装尺寸(长×宽)为标称值,并包括引脚(如适用)。

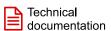

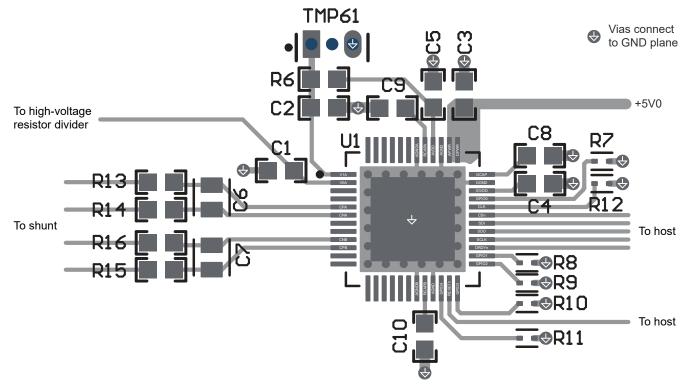

## BMS 高压测量单元 (HMU) 系统方框图

ZHCSR89A - DECEMBER 2022 - REVISED AUGUST 2023

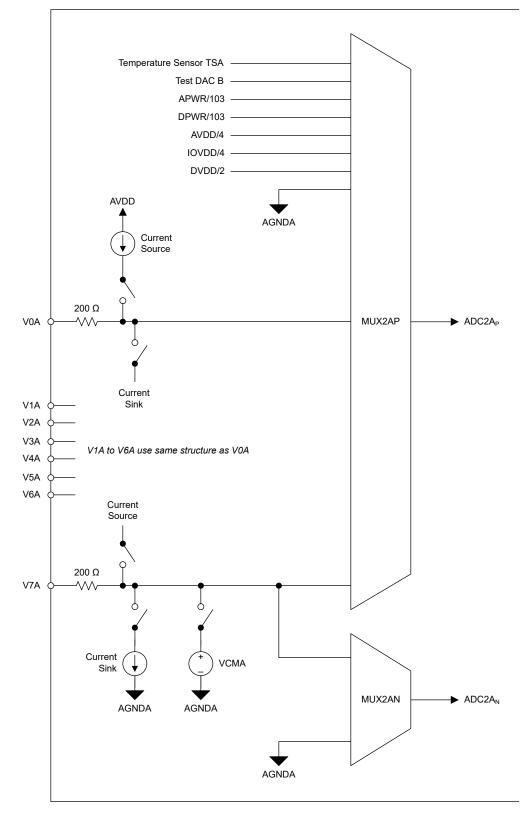

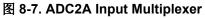

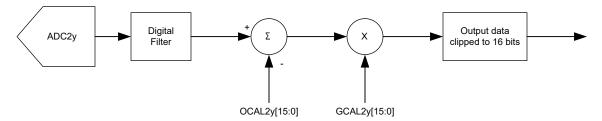

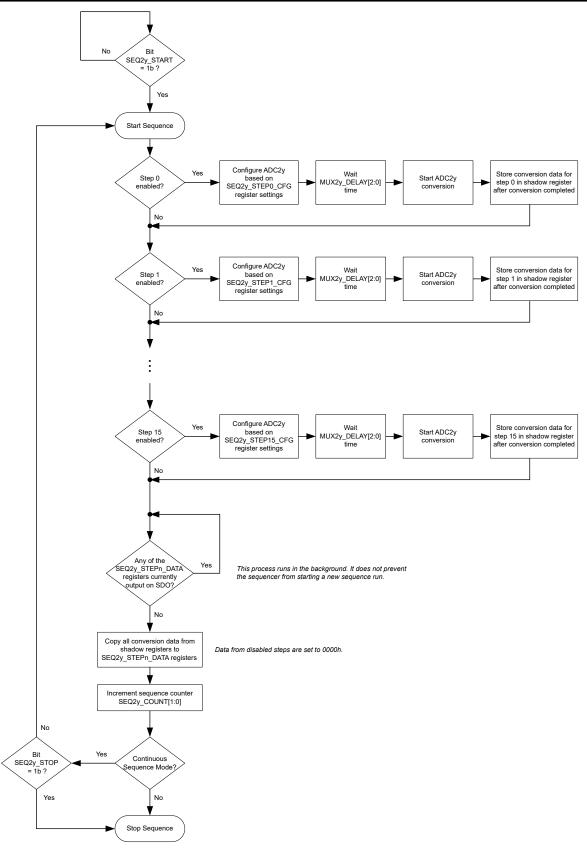

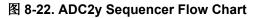

另外还提供一个多路复用的 16 位 ADC (ADC2A),可使用外部高压电阻分压器来测量分流器温度和系统中的其他 电压,例如电池包电压。分流器温度通过热敏电阻或模拟输出温度传感器等外部温度传感器进行测量。ADC2A 配 备一个通道序列发生器,后者会自动逐步调试配置的多路复用器输入,以减少 SPI 上的通信。

该器件集成了多种监控和诊断功能,可缓解和检测随机硬件故障,从而帮助开发功能安全的 BMS。

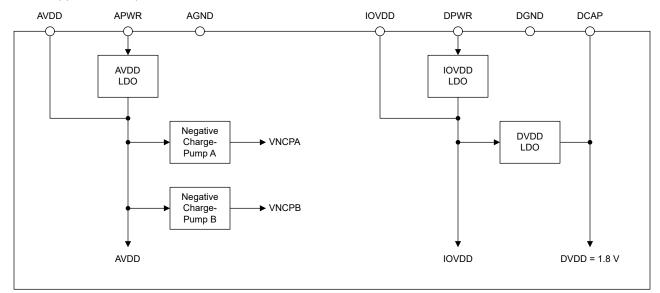

输入范围高达 16V 的内部线性稳压器支持使用非稳压直流/直流转换器为器件供电。

ADS131B23 采用 48 引脚 HTQFP 封装,额定汽车级温度范围为-40°C 至+105°C。

## **Table of Contents**

| 1 | 特性                                   | . 1 |

|---|--------------------------------------|-----|

| 2 | 应用                                   | . 1 |

| 3 | 说明                                   | . 1 |

|   | Revision History                     |     |

|   | Pin Configuration and Functions      |     |

|   | Specifications                       |     |

|   | 6.1 Absolute Maximum Ratings         |     |

|   | 6.2 ESD Ratings                      |     |

|   | 6.3 Recommended Operating Conditions |     |

|   | 6.4 Thermal Information              |     |

|   | 6.5 Electrical Characteristics       |     |

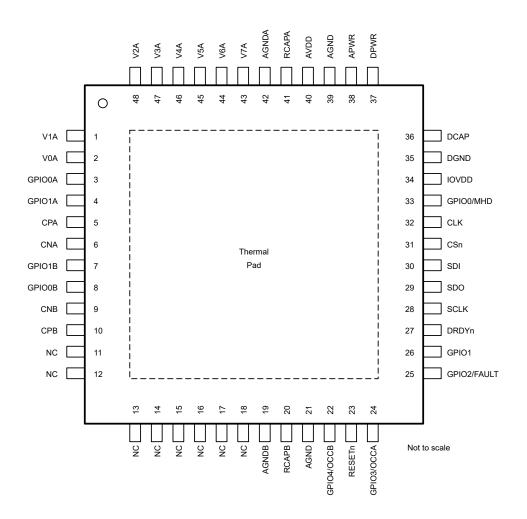

|   | 6.6 Timing Requirements              | 15  |

|   | 6.7 Switching Characteristics        |     |

|   | 6.8 Timing Diagram                   | 16  |

|   | 6.9 Typical Characteristics          | 17  |

| 7 | Parameter Measurement Information    | 23  |

|   | 7.1 Offset Drift Measurement         | 23  |

|   | 7.2 Gain Drift Measurement           | 23  |

|   | 7.3 Noise Performance                |     |

| 8 | Detailed Description                 | 25  |

|   | 8.1 Overview                         | 25  |

| 8.6 Register Map.       .7         9 Application and Implementation.       21         9.1 Application Information.       21         9.2 Typical Application.       21         9.3 Power Supply Recommendations.       21         9.4 Layout.       22         10 器件和文档支持.       22         10.1 文档支持.       22         10.3 支持资源.       22         10.4 商标.       22         10.5 静电放电警告.       22         10.6 术语表.       22         11 Mechanical, Packaging, and Orderable |                              |                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------|

| 8.4 器件功能模式                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.2 Functional Block Diagram | 26              |

| 8.4 器件功能模式                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.3 Feature Description      | <mark>27</mark> |

| 8.5 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |                 |

| 8.6 Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |                 |

| 9 Application and Implementation       21         9.1 Application Information       21         9.2 Typical Application       21         9.3 Power Supply Recommendations       21         9.4 Layout       22         10 器件和文档支持       22         10.1 文档支持       22         10.3 支持资源       22         10.4 商标       22         10.5 静电放电警告       22         10.6 术语表       22         11 Mechanical, Packaging, and Orderable                                               |                              |                 |

| 9.1 Application Information       21         9.2 Typical Application       21         9.3 Power Supply Recommendations       21         9.4 Layout       22         10 器件和文档支持       22         10.1 文档支持       22         10.2 接收文档更新通知       22         10.3 支持资源       22         10.4 商标       22         10.5 静电放电警告       22         10.6 术语表       22         11 Mechanical, Packaging, and Orderable                                                                  |                              |                 |

| 9.2 Typical Application.       21         9.3 Power Supply Recommendations.       21         9.4 Layout.       22         10 器件和文档支持.       22         10.1 文档支持.       22         10.2 接收文档更新通知.       22         10.3 支持资源.       22         10.4 商标.       22         10.5 静电放电警告.       22         10.6 术语表.       22         11 Mechanical, Packaging, and Orderable                                                                                                     |                              |                 |

| 9.3 Power Supply Recommendations.       21         9.4 Layout.       22         10 器件和文档支持.       22         10.1 文档支持.       22         10.2 接收文档更新通知.       22         10.3 支持资源.       22         10.4 商标.       22         10.5 静电放电警告.       22         10.6 术语表.       22         11 Mechanical, Packaging, and Orderable                                                                                                                                               | 9.2 Typical Application      | 214             |

| 10 器件和文档支持       22         10.1 文档支持       22         10.2 接收文档更新通知       22         10.3 支持资源       22         10.4 商标       22         10.5 静电放电警告       22         10.6 术语表       22         11 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                      |                              |                 |

| 10 器件和文档支持       22         10.1 文档支持       22         10.2 接收文档更新通知       22         10.3 支持资源       22         10.4 商标       22         10.5 静电放电警告       22         10.6 术语表       22         11 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                      | 9.4 Layout                   |                 |

| 10.1 文档支持                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |                 |

| 10.3 支持资源                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |                 |

| 10.4 商标                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10.2 接收文档更新通知                | 223             |

| 10.4 商标                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10.3 支持资源                    | 223             |

| 10.6 术语表                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.4 商标                      | 223             |

| 10.6 术语表                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.5 静电放电警告                  | 223             |

| 11 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |                 |

| Information22                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              | 223             |

## **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

# Changes from December 23, 2022 to August 21, 2023 (from Revision \* (December 2022) to Revision A (August 2023))

| R | evision A (August 2023))                                                                                                                                                                | Page             |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| • | 更改了文档标题                                                                                                                                                                                 | 1                |

| • | 将 <i>特性</i> 部分中的 ADC1y 增益漂移 规格从 25ppm/°C 更改为 20ppm/°C                                                                                                                                   | 1                |

| • | 更改了 <i>说明</i> 部分的第一段                                                                                                                                                                    | 1                |

| • | 将英文版中 <i>封装信息</i> 表中的 Body Size 更改为 Package Size                                                                                                                                        | 1                |

| • | 更改了说明部分中的系统方框图                                                                                                                                                                          | 1                |

| • | Changed description of IOVDD pin in Pin Functions table                                                                                                                                 | <mark>5</mark>   |

| • | Changed AVDD to AGND maximum specification in Absolute Maximum Ratings table                                                                                                            | 7                |

| • | Changed ADC1y gain drift typical and maximum specifications in Electrical Characteristics table                                                                                         | 9                |

| • | Changed ADC1y gain match minimum, typical, and maximum specifications in Electrical Characteristics table.                                                                              | s<br>9           |

| • | Changed ADC2A gain drift typical and maximum specifications in Electrical Characteristics table                                                                                         | 9                |

| • | Changed REFy temperature drift typical and maximum specifications in Electrical Characteristics table.                                                                                  | 9                |

| • | Changed TDACy drift, negative output voltages maximum specification in Electrical Characteristics table                                                                                 | e <mark>9</mark> |

| • | Added Digital Inputs/Outputs (GPIO0A, GPIO1A, GPIO0B, GPIO1B) input current specification to Elect                                                                                      | rical            |

|   | Characteristics table                                                                                                                                                                   | 9                |

| • | Removed ADC1y_OR_TH and ADC2y_OR_TH specifications from Electrical Characteristics table                                                                                                | 9                |

| • | Added <i>t<sub>p(AVDD_POR)</sub></i> , <i>t<sub>p(IOVDD_POR)</sub></i> , and <i>t<sub>p(DVDD_POR)</sub></i> specifications to <i>Electrical Characteristics</i> table                   | 9                |

| • | Changed APWR supply current in active mode, all ADCs disabled typical specification in Electrical                                                                                       |                  |

|   | Characteristics table                                                                                                                                                                   | 9                |

| • | Changed APWR supply current per individual ADC for ADC1y typical specification in Electrical                                                                                            |                  |

|   | Characteristics table                                                                                                                                                                   | 9                |

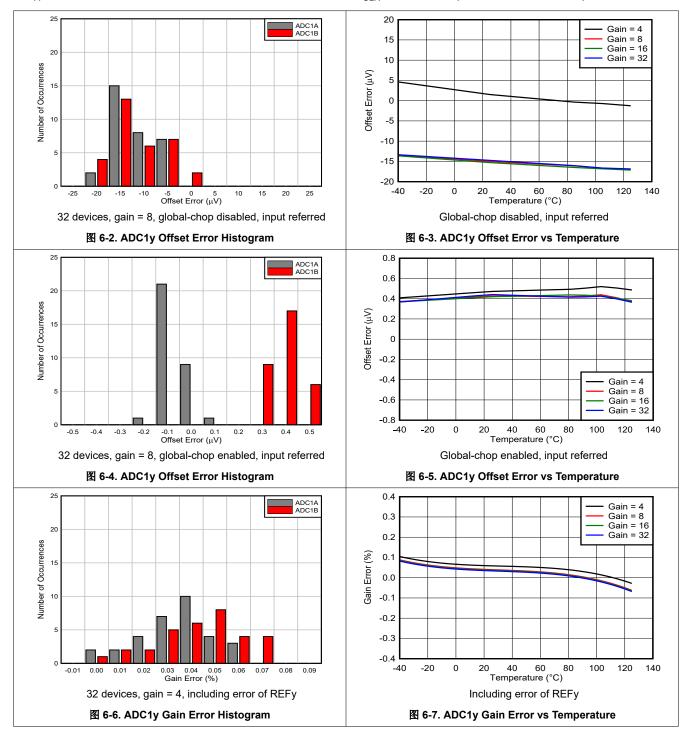

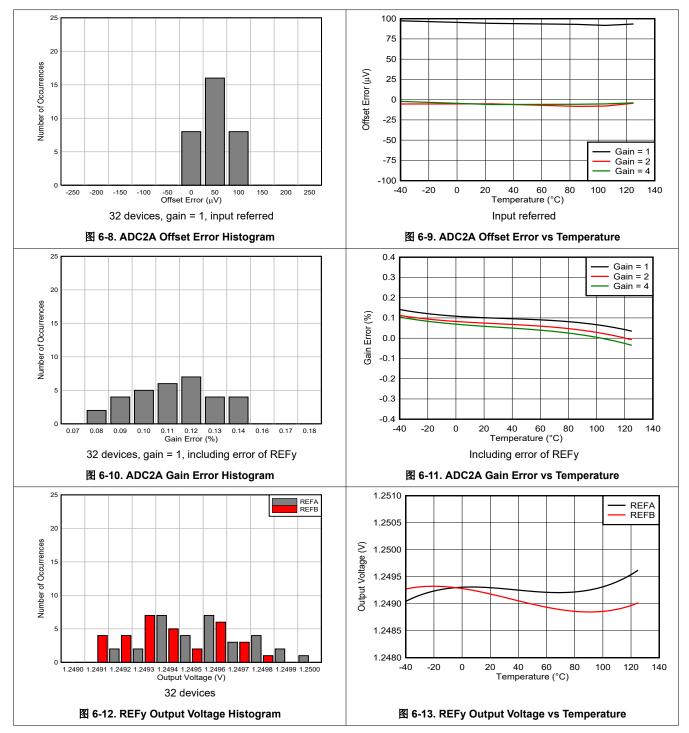

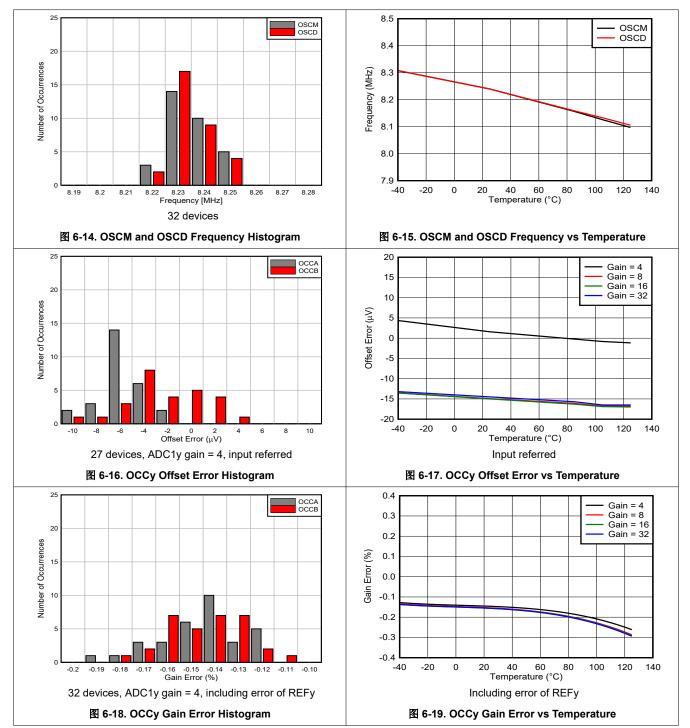

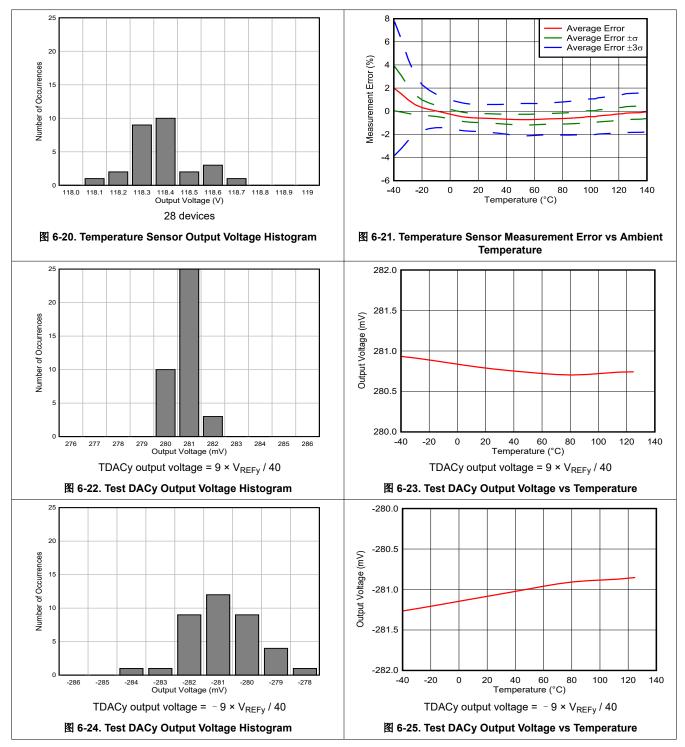

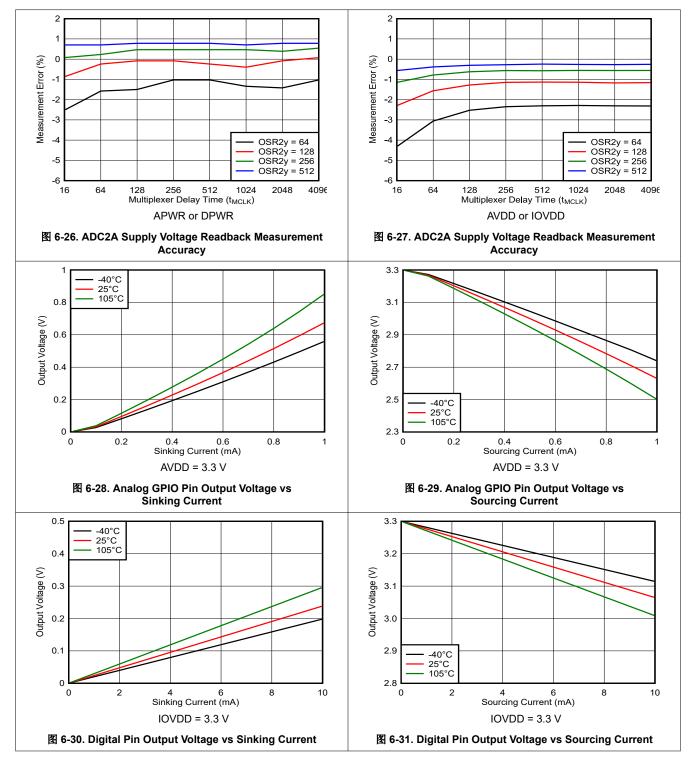

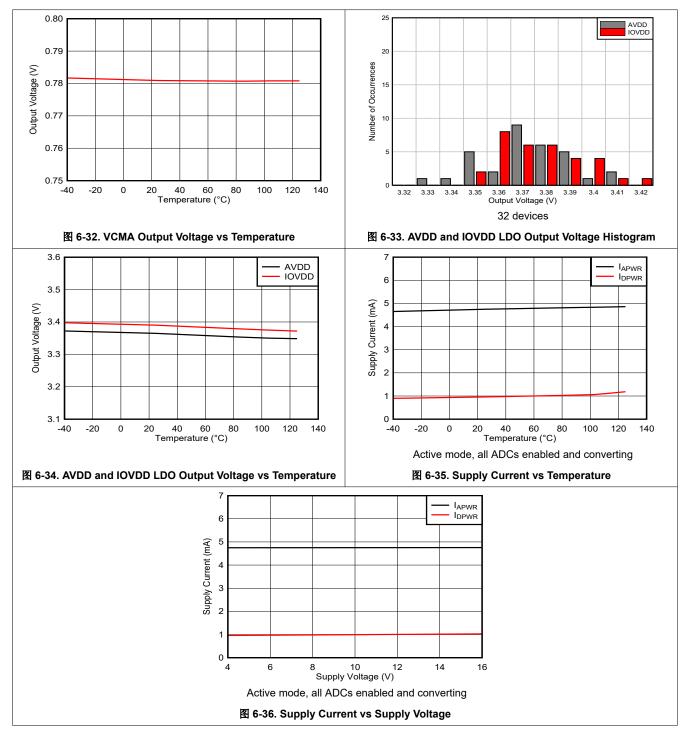

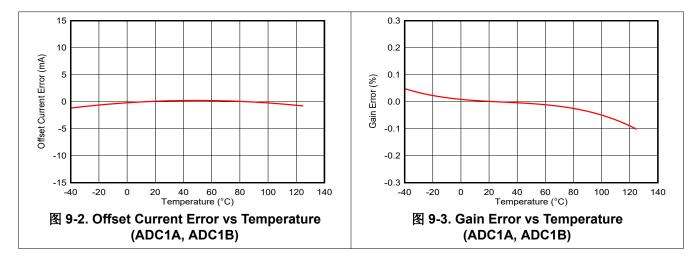

| • | Changed ADC1y Gain Error vs Temperature, ADC2A Gain Error vs Temperature, REFy Output Voltage Temperature, and OCCy Gain Error vs Temperature curves in Typical Characteristics section |                  |

ADS131B23 ZHCSR89A - DECEMBER 2022 - REVISED AUGUST 2023

| • | Added Analog GPIO Pin Output Voltage vs Sinking Current, Analog GPIO Pin Output Voltage vs Sourcing Current, Digital Pin Output Voltage vs Sinking Current, Digital Pin Output Voltage vs Sourcing Current, and |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Supply Current vs Supply Voltage curves to Typical Characteristics section                                                                                                                                      |

| • | Removed ADC overrange monitors from bulleted list and changed first paragraph of Overview section                                                                                                               |

| • | Deleted ADC Monitors and Diagnostics section from Monitor and Diagnostic Overview table in Monitors and                                                                                                         |

|   | Diagnostics section                                                                                                                                                                                             |

| • | Changed register name from ADC_STATUS to CLOCK_STATUS in Monitor and Diagnostic Overview table in                                                                                                               |

|   | Monitors and Diagnostics section                                                                                                                                                                                |

| • | Deleted ADC Monitors section                                                                                                                                                                                    |

| • | Deleted all occurrences of ADC fault flags from Fault Flags and Fault Masking section                                                                                                                           |

| • | Changed register names ADC_FAULTn to CLOCK_FAULTn, ADC_STATUS to CLOCK_STATUS, and                                                                                                                              |

|   | ADC_FAULT_MASK to CLOCK_FAULT_MASK in Fault Flags and Fault Masking section                                                                                                                                     |

| • | Changed equation in <i>Temperature Sensor (TSA)</i> section                                                                                                                                                     |

| • | Moved Missing Host Detection and MHD Pin section                                                                                                                                                                |

| • | Changed discussion of POR process in <i>Power-On Reset (POR)</i> section                                                                                                                                        |

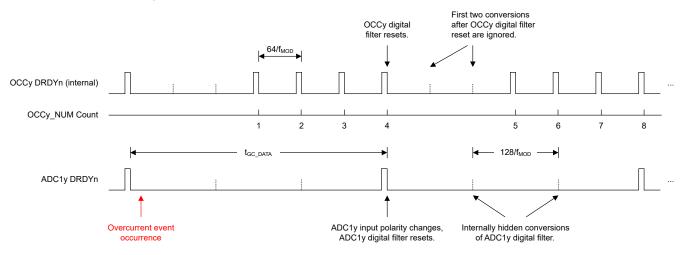

| • | Changed Overcurrent Indication Response Time in Global-Chop Mode section                                                                                                                                        |

| • | Changed bit name ADC_FAULTn to CLOCK_FAULTn in the STATUS_MSB register and changed all                                                                                                                          |

|   | information in the ADC_FAULTn bit field from ADC fault to clock fault                                                                                                                                           |

| • | Changed register name ADC_STATUS to CLOCK_STATUS and changed all ADCxy_ORn bits in the                                                                                                                          |

|   | ADC_STATUS register to RO RESERVED bits                                                                                                                                                                         |

| • | Changed register name ADC_MONITOR_CFG to CLOCK_MONITOR_CFG and changed all ADCxy_OR_EN bits in the ADC_MONITOR_CFG register to RW RESERVED bits                                                                 |

|   | Changed register name ADC_MONITOR_DIAGNOSTIC_CFG to CLOCK_MONITOR_DIAGNOSTIC_CFG                                                                                                                                |

|   |                                                                                                                                                                                                                 |

| • | Changed register name ADC_FAULT_MASK to CLOCK_FAULT_MASK and changed all ADCxy_OR_MASK                                                                                                                          |

|   | bits in the ADC FAULT_MASK register to RW RESERVED bits                                                                                                                                                         |

| • | Changed bit name ADC_FAULT_MASK to CLOCK_FAULT_MASK in the FAULT_PIN_MASK register and                                                                                                                          |

|   | changed all information in the ADC_FAULT_MASK bit field from ADC fault to clock fault                                                                                                                           |

| • | Changed reset values of SCLK_COUNTER_EN and TIMEOUT_EN bits from 1b to 0b in the                                                                                                                                |

|   | DEVICE_MONITOR_CFG register                                                                                                                                                                                     |

| • | Changed reset values of AVDD_OV_EN, AVDD_UV_EN, IOVDD_OV_EN, IOVDD_UV_EN, DVDD_OV_EN,                                                                                                                           |

|   | DVDD_UV_EN, AVDD_OSC_EN, IOVDD_OSC_EN, DVDD_OSC_EN, AVDD_OTW_EN, IOVDD_OTW_EN,                                                                                                                                  |

|   | AVDD_CL_EN, IOVDD_CL_EN, AGNDA_DISC_EN, AGNDB_DISC_EN, and DGND_DISC_EN bits from 1b                                                                                                                            |

|   | to 0b in the SUPPLY_MONITOR_CFG1 register                                                                                                                                                                       |

| • | Changed reset values of MCLK_MON_EN, OSCD_WD_EN, and MCLK_WD_EN bits from 1b to 0b in the ADC_MONITOR_CFG register                                                                                              |

| • | Changed RESETn pin bullet in Unused Inputs and Outputs section                                                                                                                                                  |

| • | Changed <i>Gain Error vs Temperature (ADC1A, ADC1B)</i> figure in <i>Application Curves</i> section                                                                                                             |

| - | onanged Gain Litor vs temperature (ADOTA, ADOTD) ligure in Application Guives section                                                                                                                           |

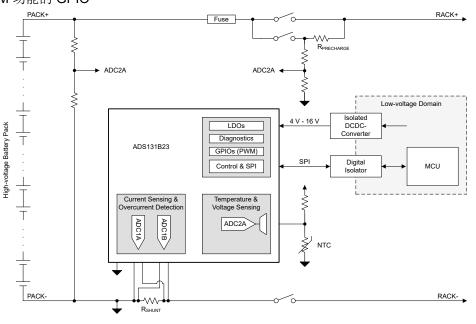

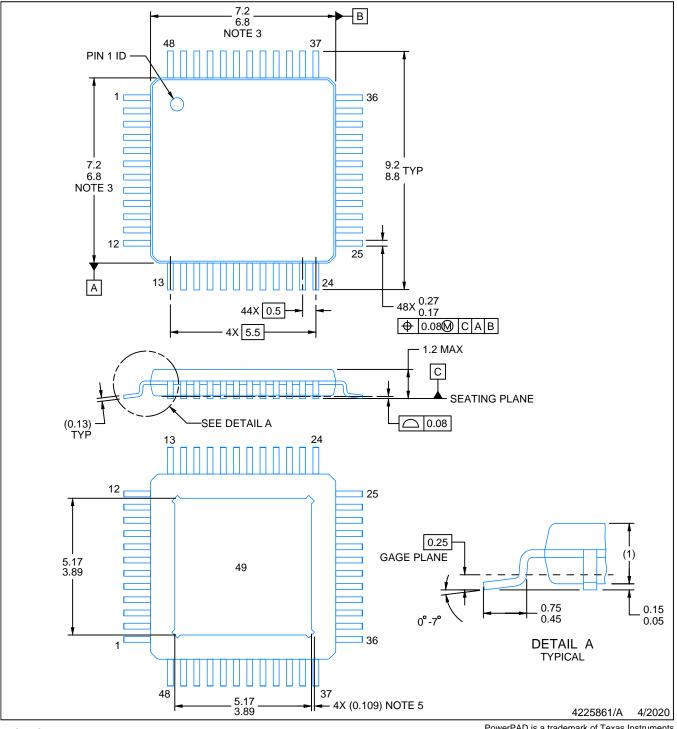

## **5** Pin Configuration and Functions

#### 图 5-1. PHP Package, 48-Pin HTQFP (Top View)

#### 表 5-1. Pin Functions

| PIN   |     | ТҮРЕ          | DESCRIPTION <sup>(1)</sup>                                                                                          |

|-------|-----|---------------|---------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. |               |                                                                                                                     |

| AGND  | 39  | Analog supply | Analog ground.                                                                                                      |

| AGND  | 21  | Analog supply | Analog ground.                                                                                                      |

| AGNDA | 42  | Analog supply | Section A analog ground. Connect to AGND.                                                                           |

| AGNDB | 19  | Analog supply | Section B analog ground. Connect to AGND.                                                                           |

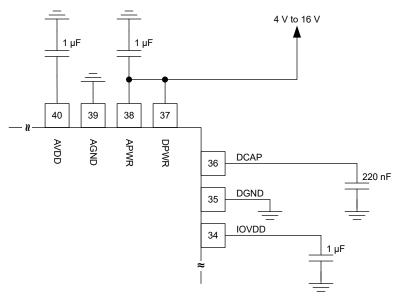

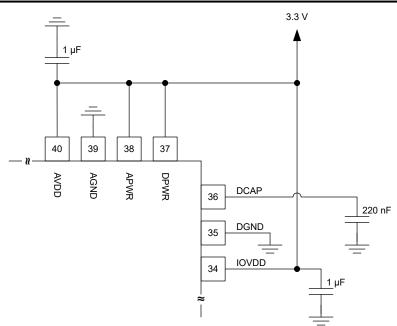

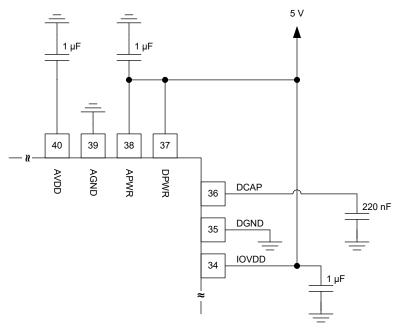

| APWR  | 38  | Analog supply | Analog power supply. Connect a 1- µ F capacitor to AGND.                                                            |

| AVDD  | 40  | Analog supply | Analog supply. Connect a 1- µ F capacitor to AGND.<br>Sets the logic levels for GPIO0A, GPIO1A, GPIO0B, and GPIO1B. |

| CLK   | 32  | Digital I/O   | Main clock input. <sup>(4)</sup>                                                                                    |

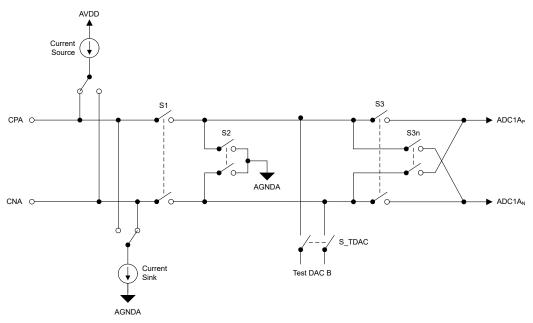

| CNA   | 6   | Analog input  | ADC1A negative analog input.                                                                                        |

| CNB   | 9   | Analog input  | ADC1B negative analog input.                                                                                        |

| СРА   | 5   | Analog input  | ADC1A positive analog input.                                                                                        |

| СРВ   | 10  | Analog input  | ADC1B positive analog input.                                                                                        |

Copyright © 2023 Texas Instruments Incorporated

#### 表 5-1. Pin Functions (continued)

| PIN         |          |                |                                                                                                                                                           |

|-------------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.      | TYPE           | DESCRIPTION <sup>(1)</sup>                                                                                                                                |

| CSn         | 31       | Digital input  | Chip-select input; active low. Internal pullup resistor to IOVDD. <sup>(4)</sup>                                                                          |

| DCAP        | 36       | Digital supply | DVDD LDO output. Connect a 220-nF capacitor to DGND.                                                                                                      |

| DGND        | 35       | Digital supply | Digital ground.                                                                                                                                           |

| DPWR        | 37       | Digital supply | Digital power supply. Connect a 1- µ F capacitor to DGND.                                                                                                 |

| DRDYn       | 27       | Digital output | Data-ready output; active low. <sup>(2) (4)</sup>                                                                                                         |

| GPIO0A      | 3        | Digital I/O    | General-purpose digital input/output 0A. <sup>(2) (3)</sup>                                                                                               |

| GPIO0B      | 8        | Digital I/O    | General-purpose digital input/output 0B. <sup>(2) (3)</sup>                                                                                               |

| GPIO0/MHD   | 33       | Digital I/O    | General-purpose digital input/output 0. <sup>(2) (4)</sup><br>Missing host detect output. <sup>(2) (4)</sup>                                              |

| GPIO1       | 26       | Digital I/O    | General-purpose digital input/output 1. <sup>(2)</sup> (4)                                                                                                |

| GPIO1A      | 4        | Digital I/O    | General-purpose digital input/output 1A. <sup>(2) (3)</sup>                                                                                               |

| GPIO1B      | 7        | Digital I/O    | General-purpose digital input/output 1B. <sup>(2) (3)</sup>                                                                                               |

| GPIO2/FAULT | 25       | Digital I/O    | General-purpose digital input/output 2. <sup>(2) (4)</sup><br>Fault output. <sup>(2) (4)</sup>                                                            |

| GPIO3/OCCA  | 24       | Digital I/O    | General-purpose digital input/output 3. <sup>(2) (4)</sup><br>Overcurrent comparator A output. <sup>(2) (4)</sup>                                         |

| GPIO4/OCCB  | 22       | Digital I/O    | General-purpose digital input/output 4. <sup>(2) (4)</sup><br>Overcurrent comparator B output. <sup>(2) (4)</sup>                                         |

| IOVDD       | 34       | Digital supply | Digital I/O supply. Connect a 1- $\mu$ F capacitor to DGND.<br>Sets the logic levels for the digital I/Os, except for GPIO0A, GPIO1A, GPIO0B, and GPIO1B. |

| NC          | 11 to 18 | NC             | No connect. Leave these pins floating or connected to AGNDB.                                                                                              |

| RCAPA       | 41       | Analog output  | REFA voltage reference output. Connect a 1- µ F capacitor to AGNDA.                                                                                       |

| RCAPB       | 20       | Analog output  | REFB voltage reference output. Connect a 1- µ F capacitor to AGNDB.                                                                                       |

| RESETn      | 23       | Digital input  | Reset input; active low. Internal pulldown resistor to DGND.                                                                                              |

| SCLK        | 28       | Digital input  | Serial data clock input. <sup>(4)</sup>                                                                                                                   |

| SDI         | 30       | Digital input  | Serial data input. <sup>(4)</sup>                                                                                                                         |

| SDO         | 29       | Digital output | Serial data output. <sup>(2) (4)</sup>                                                                                                                    |

| V0A         | 2        | Analog input   | ADC2A analog input 0A.                                                                                                                                    |

| V1A         | 1        | Analog input   | ADC2A analog input 1A.                                                                                                                                    |

| V2A         | 48       | Analog input   | ADC2A analog input 2A.                                                                                                                                    |

| V3A         | 47       | Analog input   | ADC2A analog input 3A.                                                                                                                                    |

| V4A         | 46       | Analog input   | ADC2A analog input 4A.                                                                                                                                    |

| V5A         | 45       | Analog input   | ADC2A analog input 5A.                                                                                                                                    |

| V6A         | 44       | Analog input   | ADC2A analog input 6A.                                                                                                                                    |

| V7A         | 43       | Analog input   | ADC2A analog input 7A.                                                                                                                                    |

| Thermal Pad | Pad      | —              | Thermal power pad. Connect to AGND.                                                                                                                       |

See the *Unused Inputs and Outputs* section for details on how to connect unused pins. Push-pull output. (1)

(2) (3) Logic levels referenced to AVDD. Logic levels referenced to IOVDD.

(4)

## **6** Specifications

#### 6.1 Absolute Maximum Ratings

see (1)

|                       |                                                                                                   | MIN         | MAX         | UNIT |  |

|-----------------------|---------------------------------------------------------------------------------------------------|-------------|-------------|------|--|

|                       | APWR to AGND                                                                                      | - 0.3       | 20          |      |  |

|                       | DPWR to DGND                                                                                      | - 0.3       | 20          |      |  |

|                       | AGND, AGNDy to DGND                                                                               | - 0.3       | 0.3         |      |  |

| Power-supply voltage  | AVDD to AGND                                                                                      | - 0.3       | 4           | V    |  |

|                       | IOVDD to DGND                                                                                     | - 0.3       | 7           |      |  |

|                       | DCAP to DGND                                                                                      | - 0.3       | 2.2         |      |  |

|                       | RCAPy to AGND                                                                                     | - 0.3       | 2.2         |      |  |

| Analog input voltage  | CPy, CNy, Vxy                                                                                     | AGND - 1.6  | AVDD + 0.3  | V    |  |

| Digital input voltage | CSn, SCLK, SDI, SDO, RESETn, DRDYn, CLK, GPIO0/MHD,<br>GPIO1, GPIO2/FAULT, GPIO3/OCCA, GPIO4/OCCB | DGND - 0.3  | IOVDD + 0.3 |      |  |

|                       | GPIO0A, GPIO1A                                                                                    | AGNDA - 0.3 | AVDD + 0.3  | V    |  |

|                       | GPIO0B, GPIO1B                                                                                    | AGNDB - 0.3 | AVDD + 0.3  |      |  |

| Input current         | Continuous, all pins except power-supply pins                                                     | - 10        | 10          | mA   |  |

| <b>-</b> ,            | Junction, T <sub>J</sub>                                                                          |             | 150         | °C   |  |

| Temperature           | Storage, T <sub>stg</sub>                                                                         | - 60        | 150         | 50   |  |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional – this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | 2000  | V    |

| V <sub>(ESD)</sub> |                         | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 500   |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                                     |                                  |                                                                                                             | MIN                        | NOM   | MAX                      | UNIT |

|-------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------|-------|--------------------------|------|

| POWER SUF                           | PLY                              |                                                                                                             |                            |       |                          |      |

|                                     |                                  | APWR to AGND                                                                                                | 4                          |       | 16                       |      |

|                                     |                                  | APWR = AVDD to AGND<br>(APWR shorted to AVDD, AVDD LDO<br>bypassed)                                         | 2.9                        | 3.3   | 3.6                      |      |

|                                     | Power supply                     | DPWR to DGND                                                                                                | 4                          |       | 16                       | V    |

|                                     |                                  | DPWR = IOVDD to DGND<br>(DPWR shorted to IOVDD, IOVDD LDO<br>bypassed)                                      | 2.9                        | 3.3   | 5.5                      |      |

|                                     |                                  | AGND, AGNDy to DGND                                                                                         | - 0.2                      | 0     | 0.2                      |      |

| ANALOG INI                          | PUTS ADC1A, ADC1B <sup>(1)</sup> |                                                                                                             |                            |       |                          |      |

| V <sub>CPy</sub> , V <sub>CNy</sub> | Absolute input voltage           | Gain = 4, 8, 16, 32                                                                                         | AGND - 0.3125              |       | AVDD - 2.4               | V    |

| V <sub>IN1y</sub>                   | Differential input voltage       | V <sub>IN1y</sub> = V <sub>CPy</sub> - V <sub>CNy</sub>                                                     | - V <sub>REFy</sub> / Gain |       | V <sub>REFy</sub> / Gain | V    |

| ANALOG INI                          | PUTS ADC2A <sup>(1)</sup>        |                                                                                                             |                            |       |                          |      |

| . <i>(</i>                          | y Absolute input voltage         | Gain = 1, 2                                                                                                 | AGND - 0.1                 |       | AVDD - 1.2               | v    |

| V <sub>Vxy</sub>                    |                                  | Gain = 4                                                                                                    | AGND - 0.3125              |       | AVDD - 2.4               |      |

| V <sub>IN2y</sub>                   | Differential input voltage       | $ \begin{array}{l} V_{1N2y} = V_{Vxy} & - \ V_{AGNDy} \ or \\ V_{1N2y} = V_{Vxy} & - \ V_{7y} \end{array} $ | - V <sub>REFy</sub> / Gain |       | V <sub>REFy</sub> / Gain | V    |

| EXTERNAL                            | CLOCK SOURCE <sup>(2)</sup>      |                                                                                                             |                            |       |                          |      |

| f <sub>CLK</sub>                    | External clock frequency         |                                                                                                             | 7.8                        | 8.192 | 8.4                      | MH   |

|                                     | Duty cycle                       |                                                                                                             | 40%                        | 50%   | 60%                      |      |

| DIGITAL INP                         | UTS                              |                                                                                                             |                            |       |                          |      |

|                                     | Input voltage                    | CSn, SCLK, SDI, SDO, RESETn, DRDYn,<br>CLK, GPIO0/MHD, GPIO1, GPIO2/FAULT,<br>GPIO3/OCCA, GPIO4/OCCB        | DGND                       |       | IOVDD                    | V    |

|                                     | pat tonago                       | GPIO0A, GPIO1A                                                                                              | AGNDA                      |       | AVDD                     |      |

|                                     |                                  | GPIO0B, GPIO1B                                                                                              | AGNDB                      |       | AVDD                     |      |

| EXTERNAL                            | CAPACITORS                       |                                                                                                             |                            |       |                          |      |

|                                     |                                  | APWR, DPWR                                                                                                  |                            | 1     |                          |      |

|                                     | Capacitor value <sup>(3)</sup>   | AVDD, IOVDD                                                                                                 | 0.5                        | 1     | 2                        | μF   |

|                                     |                                  | RCAPA, RCAPB                                                                                                | 0.5                        | 1     | 1.4                      |      |

|                                     |                                  | DCAP                                                                                                        |                            | 220   |                          | nF   |

| TEMPERATU                           | JRE RANGE                        |                                                                                                             |                            |       |                          |      |

| T <sub>A</sub>                      | Specified ambient temperature    |                                                                                                             | - 40                       |       | 105                      | °C   |

| 'A                                  | Operating ambient temperature    |                                                                                                             | - 45                       | - 45  | 125                      | ÷۲   |

(1) The subscript y refers to section A or section B.

The subscript *x* refers to analog input channel *x* on ADC2y.

(2) An external clock is not required when the internal oscillator is used.

(3) Capacitor values that need to be met over temperature and lifetime. See the *Power-Supply Decoupling* section for additional information.

## 6.4 Thermal Information

|                        | THERMAL METRIC <sup>(1)</sup>                | TQFP (PHP) | UNIT |

|------------------------|----------------------------------------------|------------|------|

|                        |                                              | 48 PINS    |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 23.7       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 15.3       | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 7.8        | °C/W |

| Ψ <sub>JT</sub>        | Junction-to-top characterization parameter   | 0.2        | °C/W |

| Ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 7.7        | °C/W |

| R n JC(bot)            | Junction-to-case (bottom) thermal resistance | 1.3        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

|                   | PARAMETER                     | TEST CONDITIONS                                                                                              | MIN     | ТҮР          | MAX   | UNIT              |

|-------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------|---------|--------------|-------|-------------------|

| CURRENT           | MEASUREMENT ADCS (ADC1A, AD   | DC1B)                                                                                                        |         |              |       |                   |

|                   | Resolution                    |                                                                                                              | 24      |              |       | Bits              |

|                   | Gain settings                 |                                                                                                              |         | 4, 8, 16, 32 |       | V/V               |

| f <sub>DATA</sub> | Output data rate              | f <sub>CLK</sub> = 8.192 MHz                                                                                 | 500     |              | 64k   | SPS               |

|                   | Absolute input current        | All data rates, all gains, global-chop enabled or disabled, $V_{CPy} = V_{CNy} = 0 V$                        |         | ±0.5         |       | nA                |

|                   | Differential input current    | All data rates, all gains, global-chop enabled or disabled, $V_{CPy} = V_{CNy} = 0 V$                        | - 5     | ±1           | 5     | nA                |

|                   | Differential input impedance  | All data rates, all gains, global-chop enabled or disabled                                                   |         | 1.8          |       | MΩ                |

|                   |                               | Gain = 4, global-chop disabled                                                                               |         | ±1           |       |                   |

|                   | Offset error (input referred) | Gain = 8 to 32, global-chop disabled                                                                         |         | ±15          |       | μV                |

|                   |                               | All gains, global-chop enabled                                                                               | - 1.5   | ±0.5         | 1.5   | Í                 |

|                   | Offset drift                  | All gains, global-chop disabled                                                                              |         | 20           | 100   | nV/°C             |

|                   |                               | All gains, global-chop enabled                                                                               |         | 1            | 7     | IIV/ C            |

|                   | Gain error                    | $T_{A}$ = 25°C, all gains, single-ended operation with CNy held at AGNDy, including initial accuracy of REFy | - 0.15% | ±0.05%       | 0.15% |                   |

|                   | Gain drift                    | All gains, single-ended operation with CNy held at AGNDy, including drift of REFy                            |         | 5            | 20    | ppm/°C            |

|                   | Gain match                    | Between gain settings                                                                                        | - 0.12% | ±0.03%       | 0.12% |                   |

|                   | Noise (input referred)        | Gain = 8, f <sub>DATA</sub> = 1 kSPS                                                                         |         | 0.65         |       | μV <sub>RMS</sub> |

| CMRR              | Common-mode rejection ratio   | At DC, global-chop disabled                                                                                  |         | 110          |       | dB                |

| CIVIER            |                               | At DC, global-chop enabled                                                                                   |         | 113          |       | uВ                |

|                   |                               | APWR at DC, global-chop enabled or disabled                                                                  |         | 133          |       |                   |

| PSRR              | Power-supply rejection ratio  | DPWR at DC, global-chop enabled or disabled                                                                  |         | 133          |       | dB                |

|                   |                               | AVDD at DC, global-chop enabled or disabled                                                                  |         | 115          |       |                   |

|                   |                               | IOVDD at DC, global-chop enabled or disabled                                                                 |         | 131          |       |                   |

|                                          | PARAMETER                     | TEST CONDITIONS                                                        | MIN     | TYP     | MAX   | UNIT   |

|------------------------------------------|-------------------------------|------------------------------------------------------------------------|---------|---------|-------|--------|

| VOLTAGE AN                               | ND TEMPERATURE MEASUREME      | NT ADC (ADC2A)                                                         |         |         |       |        |

|                                          | Resolution                    |                                                                        | 16      |         |       | Bits   |

|                                          | Gain settings                 |                                                                        |         | 1, 2, 4 |       | V/V    |

|                                          | Absolute input current        | OSR2y = 64, all gains, V <sub>Vxy</sub> = 0 V                          |         | ±0.2    |       | nA     |

|                                          | Differential input current    | OSR2y = 64, all gains, V <sub>Vxy</sub> = 0 V                          |         | ±0.4    |       | nA     |

|                                          |                               | OSR2y = 64, all gains                                                  |         | 15      |       |        |

|                                          | Differential input impedance  | OSR2y = 128, all gains                                                 |         | 30      |       | MΩ     |

|                                          | Differential input impedance  | OSR2y = 256, all gains                                                 |         | 60      |       |        |

|                                          |                               | OSR2y = 512, all gains                                                 |         | 120     |       |        |

|                                          | Offset error (input referred) | Gain = 1                                                               | - 350   | ±85     | 350   | μV     |

|                                          |                               | Gain = 2 and 4                                                         | - 25    | ±5      | 25    | μν     |

|                                          | Offset drift                  | Gain = 1                                                               |         | 60      | 300   | nV/°C  |

|                                          |                               | Gain = 2 and 4                                                         |         | 30      | 150   |        |

|                                          | Gain error                    | $T_A = 25^{\circ}$ C, all gains,<br>including initial accuracy of REFy | - 0.3%  | ±0.1%   | 0.3%  |        |

|                                          | Gain drift                    | All gains, including drift of REFy                                     |         | 5       | 20    | ppm/°C |

|                                          | Gain match                    | Between gain settings                                                  | - 0.15% | ±0.06%  | 0.15% |        |

| CMRR                                     | Common-mode rejection ratio   | At DC                                                                  |         | 95      |       | dB     |

|                                          |                               | APWR at DC                                                             |         | 103     |       |        |

|                                          | Device complexed action actio | DPWR at DC                                                             |         | 103     |       |        |

| PSRR                                     | Power-supply rejection ratio  | AVDD at DC                                                             |         | 91      |       | dB     |

|                                          |                               | IOVDD at DC                                                            |         | 96      |       |        |

| PRECISION                                | VOLTAGE REFERENCES (REFA, F   | REFB)                                                                  |         |         |       |        |

| V <sub>REFA</sub> ,<br>V <sub>REFB</sub> | Reference voltage             |                                                                        |         | 1.25    |       | V      |

|                                          | Accuracy                      | T <sub>A</sub> = 25°C                                                  | - 0.15% | ±0.05%  | 0.15% |        |

|                                          | Temperature drift             |                                                                        |         | 3       | 15    | ppm/°C |

|                                          | Output current                | Source only,<br>available for external loads on RCAPy pin              |         |         | 250   | μA     |

|                                          | Short-circuit current limit   | Sink or source                                                         | - 10    |         | 10    | mA     |

|                                          | Start-up time                 | 1- μ F capacitor on RCAPy, 0.01% settling                              |         | 8       |       | ms     |

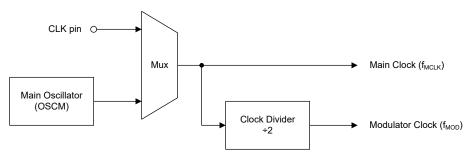

| MAIN OSCIL                               | LATOR (OSCM)                  | I                                                                      |         |         |       |        |

| f <sub>oscм</sub>                        | Frequency                     |                                                                        |         | 8.192   |       | MHz    |

|                                          | Accuracy                      |                                                                        | - 2.5%  |         | 2.5%  |        |

| DIAGNOSTIC                               | C OSCILLATOR (OSCD)           | 1                                                                      |         |         |       |        |

| OSCD                                     | Frequency                     |                                                                        |         | 8.192   |       | MHz    |

|                                          | Accuracy                      |                                                                        | - 2.5%  |         | 2.5%  |        |

| OVERCURRE                                | ENT COMPARATORS (OCCA, OCC    | )<br>CB)                                                               |         |         |       |        |

|                                          | Offset error (input referred) | All gains                                                              | - 500   | ±20     | 500   | μV     |

|                                          | Gain error                    | All gains, including error of REFy                                     | - 0.5%  | ±0.2%   | 0.5%  | · ·    |

| TEMPERATU                                | JRE SENSOR (TSA)              |                                                                        |         |         |       |        |

| TS <sub>Offset</sub>                     | Output voltage                | T <sub>A</sub> = 25°C                                                  |         | 118.4   |       | mV     |

|                                          |                               |                                                                        | 1       |         |       |        |

|                  | PARAMETER                        | TEST CONDITIONS                           | MIN               | ТҮР                                                                                                                                                                                                                                               | MAX         | UNIT   |

|------------------|----------------------------------|-------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|

| COMMON-          | MODE OUTPUT BUFFERS (VCMA)       | 1                                         |                   |                                                                                                                                                                                                                                                   |             |        |

| V <sub>CMA</sub> | Common-mode output voltage       |                                           | 0.75              | 0.78                                                                                                                                                                                                                                              | 0.81        | V      |

|                  | Output current                   | Sink or source                            | - 1               |                                                                                                                                                                                                                                                   | 1           | mA     |

|                  | Short-circuit current limit      | Sink or source                            | - 5               |                                                                                                                                                                                                                                                   | 5           | mA     |

|                  | Capacitive load                  |                                           |                   |                                                                                                                                                                                                                                                   | 100         | pF     |

| TEST DAC         | S (TDACA, TDACB)                 | 1                                         |                   |                                                                                                                                                                                                                                                   |             |        |

|                  | Output voltage settings          |                                           |                   | $\begin{array}{c} 1 \times V_{REFy} / 40 \\ 2 \times V_{REFy} / 40 \\ 4 \times V_{REFy} / 40 \\ 9 \times V_{REFy} / 40 \\ 18 \times V_{REFy} / 40 \\ 36 \times V_{REFy} / 40 \\ - 4 \times V_{REFy} / 40 \\ - 9 \times V_{REFy} / 40 \end{array}$ |             | V      |

|                  | Accuracy                         |                                           |                   | ±0.3%                                                                                                                                                                                                                                             |             |        |

|                  | Drift                            | Positive output voltages                  |                   | 6                                                                                                                                                                                                                                                 | 35          | ppm/°C |

|                  | Dint                             | Negative output voltages                  |                   | 12                                                                                                                                                                                                                                                | 80          | ppm/ C |

| OPEN-WIR         | E DETECTION CURRENT SOURCES      | S AND SINKS (OWD1A, OWD1B, OWD2A)         | 1                 |                                                                                                                                                                                                                                                   |             |        |

|                  | Current source settings          |                                           |                   | 4, 40, 240                                                                                                                                                                                                                                        |             | μA     |

|                  | Current sink settings            |                                           |                   | 4, 40, 240                                                                                                                                                                                                                                        |             | μA     |

|                  | Current source accuracy          |                                           |                   | ±8%                                                                                                                                                                                                                                               |             |        |

|                  | Current sink accuracy            |                                           |                   | ±8%                                                                                                                                                                                                                                               |             |        |

| DIGITAL IN       | IPUTS/OUTPUTS (GPIO0A, GPIO1A,   | GPIO0B, GPIO1B)                           |                   |                                                                                                                                                                                                                                                   |             |        |

| V <sub>IL</sub>  | Logic input level, low           |                                           | AGNDy             |                                                                                                                                                                                                                                                   | 0.3 AVDD    | V      |

| V <sub>IH</sub>  | Logic input level, high          |                                           | 0.7 AVDD          |                                                                                                                                                                                                                                                   | AVDD        | V      |

| V <sub>OL</sub>  | Logic output level, low          | I <sub>OL</sub> = - 100 μA                |                   |                                                                                                                                                                                                                                                   | 0.2 AVDD    | V      |

| V <sub>OH</sub>  | Logic output level, high         | I <sub>OH</sub> = 100 μA                  | 0.8 AVDD          |                                                                                                                                                                                                                                                   |             | V      |

| I <sub>IN</sub>  | Input current                    | AGNDy < V <sub>Digital Input</sub> < AVDD | - 1               |                                                                                                                                                                                                                                                   | 1           | μA     |

| DIGITAL IN       | IPUTS/OUTPUTS (CSn, SCLK, SDI, S | SDO, RESETn, DRDYn, CLK, GPIO0/MHD, GF    | PIO1, GPIO2/FAULT | , GPIO3/OCCA, G                                                                                                                                                                                                                                   | SPIO4/OCCB) |        |

| V <sub>IL</sub>  | Logic input level, low           |                                           | DGND              |                                                                                                                                                                                                                                                   | 0.3 IOVDD   | V      |

| V <sub>IH</sub>  | Logic input level, high          |                                           | 0.7 IOVDD         |                                                                                                                                                                                                                                                   | IOVDD       | V      |

| V <sub>OL</sub>  | Logic output level, low          | I <sub>OL</sub> = - 1 mA                  |                   |                                                                                                                                                                                                                                                   | 0.2 IOVDD   | V      |

| V <sub>OH</sub>  | Logic output level, high         | I <sub>OH</sub> = 1 mA                    | 0.8 IOVDD         |                                                                                                                                                                                                                                                   |             | V      |

| I <sub>IN</sub>  | Input current                    | DGND < V <sub>Digital Input</sub> < IOVDD | - 1               |                                                                                                                                                                                                                                                   | 1           | μA     |

|                         | PARAMETER                                                    | TEST CONDITIONS                                                                | MIN  | TYP                       | MAX  | UNIT             |

|-------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|------|---------------------------|------|------------------|

| CLOCK MONITO            | RS                                                           |                                                                                |      |                           |      |                  |

| f <sub>MCLK_WD_TH</sub> | Main clock (MCLK) watchdog<br>frequency threshold            | Watchdog indicates a fault when MCLK frequency drops below frequency threshold |      |                           | 300  | kHz              |

| foscd_wd_th             | Diagnostic oscillator (OSCD)<br>watchdog frequency threshold | Watchdog indicates a fault when OSCD frequency drops below frequency threshold |      |                           | 300  | kHz              |

| MCLK_FAULT_<br>TH       | Main clock fault detection<br>frequency threshold            | Difference in clock frequencies between MCLK and OSCD to generate a fault      |      | 10%                       |      |                  |

| POWER SUPPLY            | MONITORS                                                     | · · · · · ·                                                                    |      |                           |      |                  |

| AVDD_UV_TH              | AVDD undervoltage threshold                                  |                                                                                | 2.9  | 2.95                      | 3.0  | V                |

| AVDD_OV_TH              | AVDD overvoltage threshold                                   |                                                                                | 3.8  | 3.9                       | 4.0  | V                |

|                         |                                                              | IOVDD_UV_TH = 1b                                                               | 2.9  | 2.95                      | 3.0  | .,               |

| IOVDD_UV_TH             | IOVDD undervoltage threshold                                 | IOVDD_UV_TH = 0b                                                               | 4.2  | 4.3                       | 4.4  | V                |

|                         |                                                              | IOVDD_OV_TH = 1b                                                               | 3.8  | 3.9                       | 4.0  |                  |

| IOVDD_OV_TH             | IOVDD overvoltage threshold                                  | IOVDD_OV_TH = 0b                                                               | 5.6  | 5.75                      | 5.9  | V                |

| DVDD_UV_TH              | DVDD undervoltage threshold                                  |                                                                                | 1.55 | 1.6                       | 1.65 | V                |

| <br>DVDD_OV_TH          | DVDD overvoltage threshold                                   |                                                                                | 1.90 | 1.95                      | 2.0  | V                |

| <br>AVDD_OSC_MA<br>G    | 5                                                            | Amplitude required to generate fault                                           | 500  |                           |      | mV <sub>pp</sub> |

| AVDD_OSC_FR<br>EQ       | AVDD oscillation detection input frequency                   | Oscillation frequency range to generate fault                                  | 2    |                           | 500  | kHz              |

| IOVDD_OSC_M<br>AG       | IOVDD oscillation detection magnitude                        | Amplitude required to generate fault                                           | 500  |                           |      | mV <sub>pp</sub> |

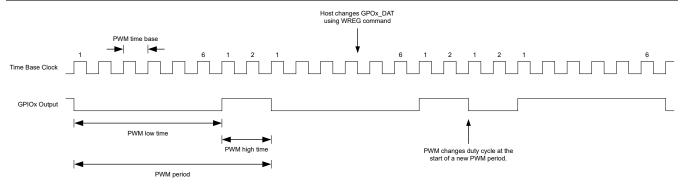

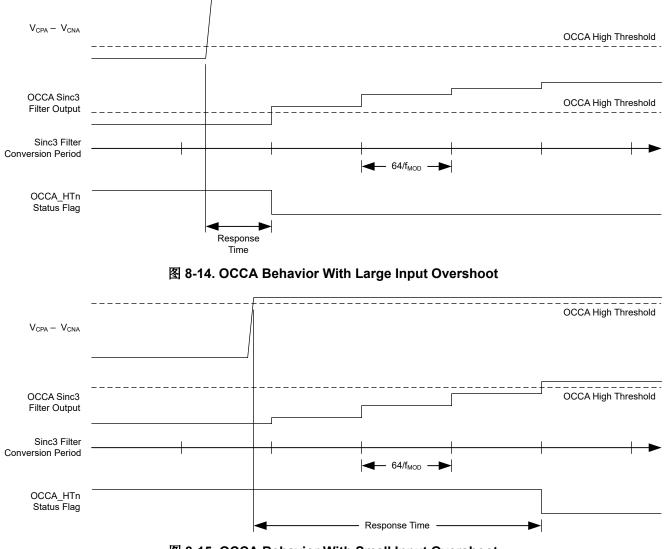

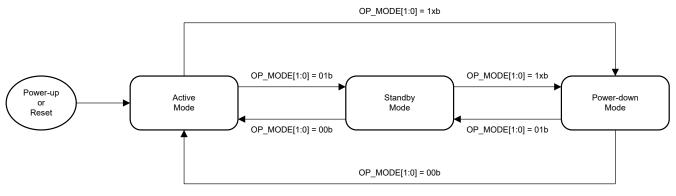

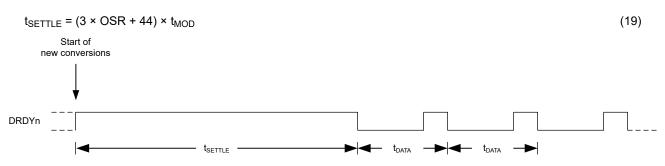

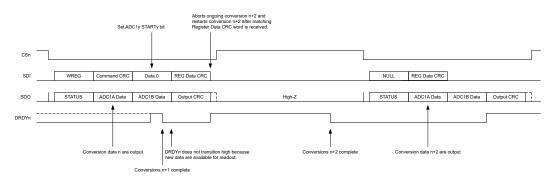

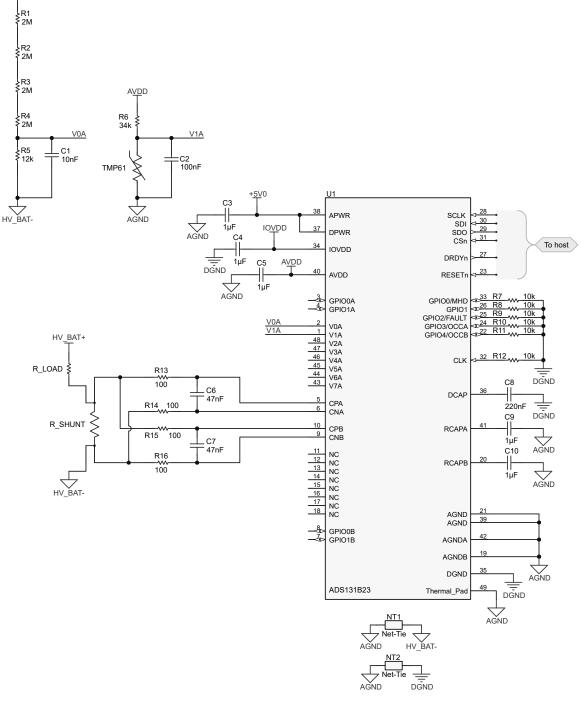

| IOVDD_OSC_F<br>REQ      | IOVDD oscillation detection input frequency                  | Oscillation frequency range to generate fault                                  | 2    |                           | 500  | kHz              |