Now

#### bg76PL536A-Q1

ZHCS267A - MAY 2011 - REVISED DECEMBER 2016

适用于 EV 和 HEV 的 bq76PL536A-Q1 3 至 6 节锂离子电池监控器和 保护 IC单元

#### 特性 1

- 符合汽车应用 应用认证

- 具有符合 AEC-Q100 标准的下列结果:

- 器件温度 2 级: -40℃ 至 +105℃ 的环境运行温 度范围

- 器件人体模型 (HBM) 分类等级 2

- 器件充电器件模型 (CDM) 分类等级 C4B

- 3节至6节电池支持,所有化合物

- 热插拔

- 用于数据通信的高速串行外设接口 (SPI)

- 支持垂直堆叠的接口

- 器件之间无需隔离组件

- 高精度模数转换器 (ADC): ٠

- ±1mV 典型精度

- 14 位分辨率,6µs 转换时间

- 九个 ADC 输入

- 支持同步测量的专用引脚

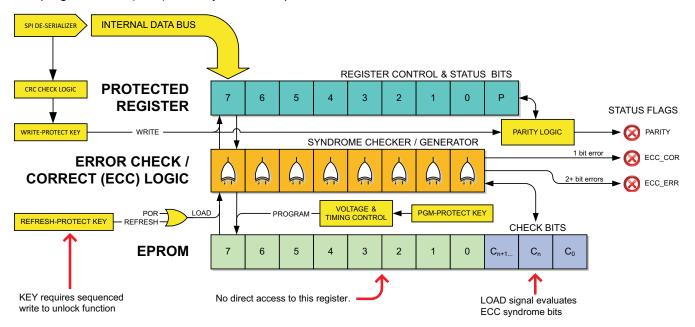

- 配置数据存储在具有差错校验/纠正 (ECC) 功能的 一次性可编程 (OTP) 寄存器中

- 内置比较器(二级保护器)支持:

- 过压和欠压保护

- 过热保护

- 可编程的阈值和延迟时间

- 专用故障信号

- 支持安全超时功能的电芯均衡控制输出 ٠

- 通过外部组件设置均衡电流

- 电源电压范围: 7.2V 至 27V 连续电压以及 36V 峰 • 值

- 低功耗:

- 休眠电流典型值为 12µA, 空闲电流典型值为 45µA

- 集成 5V、3mA 高精度 LDO

- 2 应用

- 电动车与混合动力电动车

- 不间断电源系统 (UPS)

- 电动自行车和电动踏板车

- 大型电池系统

# 3 说明

bq

bq76PL536A-Q1 器件是用于三至六节串联锂离子电池 的可堆叠电池监控器和保护器。bq76PL536A-Q1 集成 了模拟前端 (AFE) 以及精密模数转换器 (ADC),用于 精确测量电池电压。使用一个单独的 ADC 来测量温 度。

除测量温度外,该器件还对各通道提供过压和欠压监控 保护。通过非易失性存储器来存储用户可编程的保护阈 值和延迟时间。一旦超出其中某个阈值,就会输出故障 信号。

可通过堆叠式 bq76PL536A-Q1 器件来实现对由 192 节电池组成的电池组的支持。所有器件通过高速 SPI 接口进行连接。

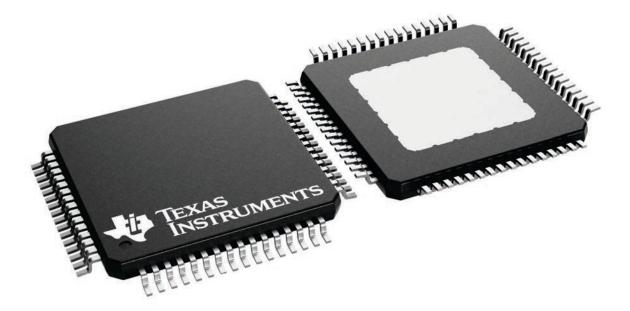

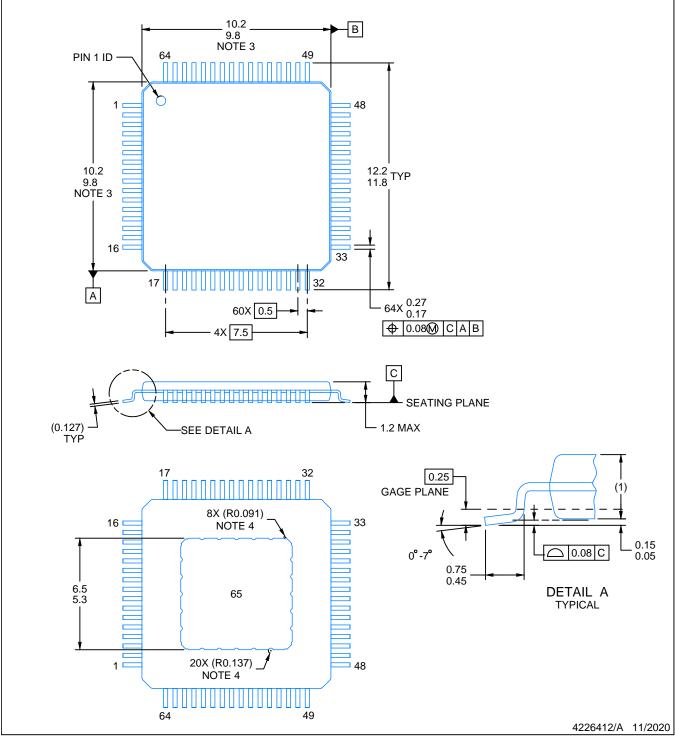

# 器件信息(1)

| 器件型号        | 封装         | 封装尺寸(标称值)         |

|-------------|------------|-------------------|

| 76PL536A-Q1 | HTQFP (64) | 10.00mm x 10.00mm |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

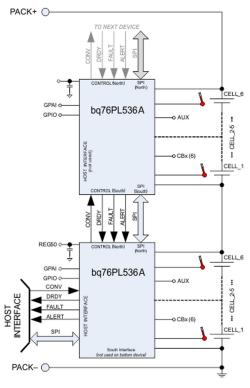

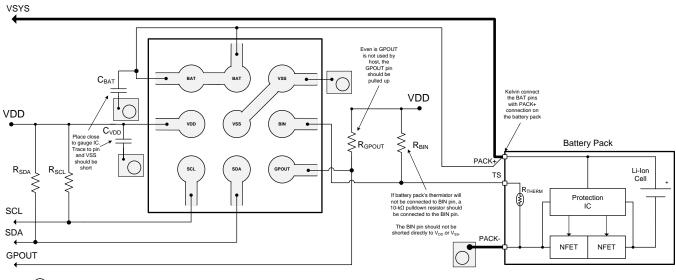

# 简化的系统连接

Copyright © 2016, Texas Instruments Incorporated

# 目录

7.5

7.6

8

9

| 1 | 特性   |                                               |

|---|------|-----------------------------------------------|

| 2 | 应用   | 1                                             |

| 3 | 说明   | 1                                             |

| 4 | 修订   | 历史记录                                          |

| 5 | Pin  | Configuration and Functions 4                 |

| 6 | Spe  | cifications6                                  |

|   | 6.1  | Absolute Maximum Ratings 6                    |

|   | 6.2  | ESD Ratings6                                  |

|   | 6.3  | Recommended Operating Conditions              |

|   | 6.4  | Thermal Information7                          |

|   | 6.5  | Electrical Characteristics                    |

|   | 6.6  | Timing Requirements: AC SPI Data Interface 12 |

|   | 6.7  | Vertical Communications Bus 13                |

|   | 6.8  | Typical Characteristics 14                    |

| 7 | Deta | ailed Description 16                          |

|   | 7.1  | Overview                                      |

|   | 7.2  | Functional Block Diagram 16                   |

|   | 7.3  | Feature Description                           |

# 4 修订历史记录

2

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Original (May 2011) to Revision A

| • | 已添加 ESD 额定值表,特性 描述部分,器件功能模式,应用和实施部分,电源相关建议部分,布局部分,器件和文<br>档支持部分以及机械、封装和可订购信息部分                                 | 1    |

|---|----------------------------------------------------------------------------------------------------------------|------|

| • | 已更改 将电源电压范围从"6V 至 30V"更改为"7.2V 至 27V"(特性部分)                                                                    | 1    |

| • | 已更改 描述 以使其更为简洁                                                                                                 |      |

| • | Changed graphic pin 54 alignment and part number                                                               | 4    |

| • | Changed AUX description                                                                                        |      |

| • | Listed values and removed VCn to VCn-1 row and updated Input Voltage Range and Output Voltage Range informatio | n 6  |

| • | 已更改 "V <sub>BAT</sub> = 20 V" to "V <sub>BAT</sub> = 22 V" throughout data sheet                               |      |

| • | 已更改 value to 27 V                                                                                              |      |

| • | Combined Electrical Characteristics tables into one table                                                      | 8    |

| • | 已更改 lower range to 7.2                                                                                         | 8    |

| • | 已更改 format of bottom two rows and added notes                                                                  | 9    |

| • | 已删除 MAX value for V <sub>IH</sub>                                                                              |      |

| • | 已删除 MIN value for V <sub>IL</sub>                                                                              |      |

| • | 已更改 120 to 125                                                                                                 |      |

| • | 已更改 test condition                                                                                             | 9    |

| • | 已删除 note                                                                                                       | 10   |

| • | 已添加 error range                                                                                                | 10   |

| • | 已更改 table values and format                                                                                    | 10   |

| • | 已更改 min value                                                                                                  | 10   |

| • | 已更改 test conditions, Min and Nom values, and added note 4                                                      | . 10 |

| • | 已更改 the section to be switching characteristics                                                                | . 11 |

| • | 已更改 units in equations to match unit in corresponding row                                                      | . 11 |

| • | Moved figure after timing requirements                                                                         | 13   |

| • | 已更改 name from VC0 to VSS                                                                                       | 17   |

Application and Implementation528.1Application Information528.2Typical Application53Power Supply Recommendations59

www.ti.com.cn

Page

# 修订历史记录 (接下页)

| • | 已添加 TNOM table note                                                     | 25 |

|---|-------------------------------------------------------------------------|----|

| • | 已更改 note wording for LDODx                                              | 27 |

| • | 已更改 warning to caution                                                  | 28 |

| • | 已更改 text to a warning                                                   | 29 |

| • | 已更改 text to a caution and added SLEEP State in text                     | 34 |

| • | 已更改 TS1(2) to TS1:TS2 throughout document                               | 34 |

| • | 已更改 SHADOW_LOAD to REFRESH                                              | 37 |

| • | 已更改 paragraph text and added cross-reference to section                 | 42 |

|   | 已更改 definition of 1 value                                               |    |

| • | 已更改 text to Caution format                                              | 47 |

| • | 已更改 anti-aliasing VCn input to VC6-VC1                                  | 52 |

| • | 已更改 "SN76PL536-Q1" to "bq76PL536A-Q1" in <i>Power Supply Decoupling</i> | 59 |

| • | 已更改 note wording for LDODx                                              | 59 |

|   |                                                                         |    |

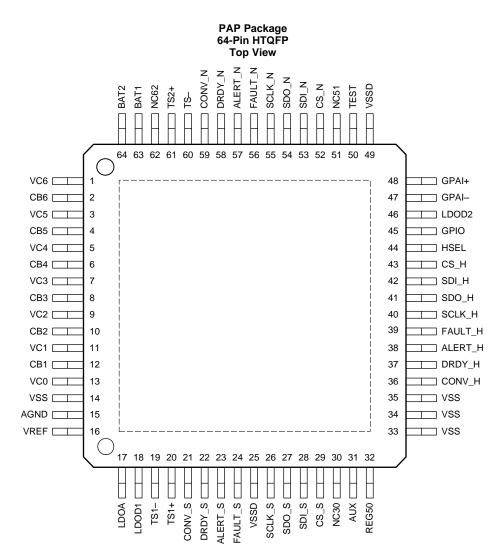

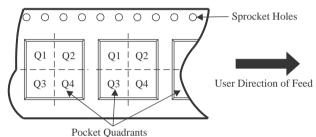

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN     |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                         |  |

|---------|-----|---------------------|-----------------------------------------------------------------------------------------------------|--|

| NAME    | NO. | ITPE                | DESCRIPTION                                                                                         |  |

| AGND    | 15  | AI                  | nternal analog V <sub>REF (-)</sub>                                                                 |  |

| ALERT_H | 38  | 0                   | Host-to-device interface – ALERT condition detected in this or higher (North) device                |  |

| ALERT_N | 57  | I                   | Current-mode input indicating a system status change from the next-higher bq76PL536A-Q1             |  |

| ALERT_S | 23  | OD                  | Current-mode output indicating a system status change to the next lower bq76PL536A-Q1               |  |

| AUX     | 31  | 0                   | Switched current-limited output from REG50                                                          |  |

| BAT1    | 63  | Р                   | ver-supply voltage, connect to most-positive cell +, tie to BAT2 on PCB                             |  |

| BAT2    | 64  | Р                   | wer-supply voltage, connect to most-positive cell +, tie to BAT1 on PCB                             |  |

| CB1     | 12  | 0                   | Cell-balance control output 1                                                                       |  |

| CB2     | 10  | 0                   | Cell-balance control output 2                                                                       |  |

| CB3     | 8   | 0                   | Cell-balance control output 3                                                                       |  |

| CB4     | 6   | 0                   | Cell-balance control output 4                                                                       |  |

| CB5     | 4   | 0                   | Cell-balance control output 5                                                                       |  |

| CB6     | 2   | 0                   | ell-balance control output 6                                                                        |  |

| CONV_H  | 36  | I                   | Host-to-device interface – initiates a synchronous conversion. Pin has 250-nA internal sink to VSS. |  |

# Pin Functions (continued)

| NAME    | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                       |  |

|---------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CONV_N  | 59  | OD                  | Current-mode output to the next-higher bq76PL536A-Q1 to initiate a conversion                                                                                                     |  |

| CONV_S  | 21  | I                   | Input from the adjacent lower bq76PL536A-Q1 to initiate a conversion                                                                                                              |  |

| CS_H    | 43  | I                   | Host-to-device interface – active-low chip select from host. Internal 100-k $\Omega$ pull-up resistor                                                                             |  |

| CS_N    | 52  | OD                  | Current-mode output used to select the next-higher bq76PL536A-Q1 for SPI communication                                                                                            |  |

| CS_S    | 29  | Ι                   | Current-mode input SPI chip-select (slave-select) from the next-lower bq76PL536A-Q1                                                                                               |  |

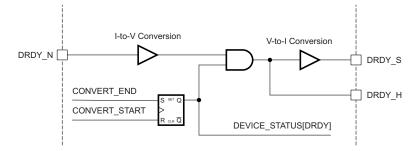

| DRDY_H  | 37  | 0                   | Host-to-device interface - conversion complete, data-ready indication                                                                                                             |  |

| DRDY_N  | 58  | I                   | Current-mode input indicating conversion data is ready from next-higher bq76PL536A-Q1                                                                                             |  |

| DRDY_S  | 22  | OD                  | Current-mode output indicating conversion data is ready to the next lower bq76PL536A-Q1                                                                                           |  |

| FAULT_H | 39  | 0                   | Host-to-device interface - FAULT condition detected in this or higher (North) device                                                                                              |  |

| FAULT_N | 56  | I                   | Current-mode input indicating a system status change from the next-higher bq76PL536A-Q1                                                                                           |  |

| FAULT_S | 24  | OD                  | Current-mode output                                                                                                                                                               |  |

| GPAI+   | 48  | AI                  | General-purpose (differential) analog input, connect to VSS if unused.                                                                                                            |  |

| GPAI–   | 47  | AI                  | General-purpose (differential) analog input, connect to VSS if unused.                                                                                                            |  |

| GPIO    | 45  | IOD                 | Digital open-drain I/O. A 10-k $\Omega$ to 2-M $\Omega$ pull-up is recommended.                                                                                                   |  |

| HSEL    | 44  | Ι                   | Host interface enable, 0 = enable, 1 = disable                                                                                                                                    |  |

| LDOA    | 17  | Р                   | Internal analog 5-V LDO bypass connection, requires 2.2-µF ceramic capacitor for stability                                                                                        |  |

| LDOD1   | 18  | Р                   | Internal digital 5-V LDO bypass connection 1, requires 2.2-µF ceramic capacitor for stability. This pin is tied internally to LDOD2. This pin should be tied to LDOD2 externally. |  |

| LDOD2   | 46  | Р                   | Internal digital 5-V LDO bypass connection 2, requires 2.2-µF ceramic capacitor for stability. This pin is tied internally to LDOD1. This pin should be tied to LDOD1 externally. |  |

| NC30    | 30  | _                   | No connection                                                                                                                                                                     |  |

| NC51    | 51  | _                   | No connection                                                                                                                                                                     |  |

| NC62    | 62  | _                   | No connection                                                                                                                                                                     |  |

| REG50   | 32  | Р                   | 5-V user LDO output, requires 2.2-µF ceramic capacitor for stability                                                                                                              |  |

| SCLK_H  | 40  | Ι                   | Host-to-device interface – SPI clock from host                                                                                                                                    |  |

| SCLK_N  | 55  | OD                  | Current-mode output SPI clock to the next-higher bq76PL536A-Q1                                                                                                                    |  |

| SCLK_S  | 26  | Ι                   | Current-mode input SPI clock from the next-lower bq76PL536A-Q1                                                                                                                    |  |

| SDI_H   | 42  | Ι                   | Host-to-device interface – data from host to device (host MOSI signal)                                                                                                            |  |

| SDI_N   | 53  | OD                  | Current-mode output for SPI data to the next-higher bq76PL536A-Q1                                                                                                                 |  |

| SDI_S   | 28  | I                   | Current-mode input for SPI data from the next-lower bq76PL536A-Q1                                                                                                                 |  |

| SDO_H   | 41  | 0                   | Host-to-device interface – data from device to host (host MISO signal), 3-state pin, 250-nA internal pull-up                                                                      |  |

| SDO_N   | 54  | I                   | Current-mode input for SPI data from the next-lower bq76PL536A-Q1                                                                                                                 |  |

| SDO_S   | 27  | OD                  | Current-mode output for SPI data to the next-lower bq76PL536A-Q1                                                                                                                  |  |

| TEST    | 50  | I                   | Factory test pin. Connect to VSS in user circuitry. This pin includes an approximately 100-k $\Omega$ internal pull-down                                                          |  |

| TS1+    | 20  | AI                  | Differential temperature sensor input                                                                                                                                             |  |

| TS1-    | 19  | AI                  | Differential temperature sensor input                                                                                                                                             |  |

| TS2+    | 61  | AI                  | Differential temperature sensor input                                                                                                                                             |  |

| TS2–    | 60  | AI                  | Differential temperature sensor input                                                                                                                                             |  |

| VC0     | 13  | AI                  | Sense-voltage input terminal for negative terminal of first cell (VSS)                                                                                                            |  |

| VC1     | 11  | AI                  | Sense voltage input terminal for positive terminal of the first cell                                                                                                              |  |

| VC2     | 9   | AI                  | Sense voltage input terminal for the positive terminal of the second cell                                                                                                         |  |

| VC3     | 7   | AI                  | Sense voltage input terminal for the positive terminal of the third cell                                                                                                          |  |

| VC4     | 5   | AI                  | Sense voltage input terminal for the positive terminal of the fourth cell                                                                                                         |  |

| VC5     | 3   | AI                  | Sense voltage input terminal for the positive terminal of the fifth cell                                                                                                          |  |

| VC6     | 1   | AI                  | Sense voltage input terminal for the positive terminal of the sixth cell                                                                                                          |  |

TRUMENTS

XAS

# **Pin Functions (continued)**

| PIN         |                   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                 |  |  |  |

|-------------|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME        | NO.               | ITPE'               | DESCRIPTION                                                                                                                                                                                                 |  |  |  |

| VREF        | 16                | Р                   | ernal analog voltage reference (+), requires 10-μF, low-ESR ceramic capacitor to AGND for<br>ibility                                                                                                        |  |  |  |

| VSS         | 14, 33, 34,<br>35 | Р                   | V <sub>SS</sub>                                                                                                                                                                                             |  |  |  |

| VSSD        | 25, 49            | Р                   | V <sub>SS</sub>                                                                                                                                                                                             |  |  |  |

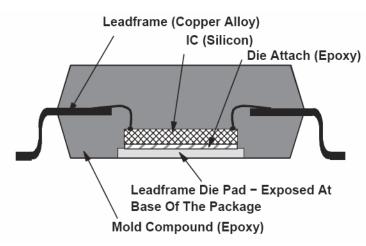

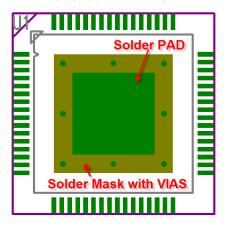

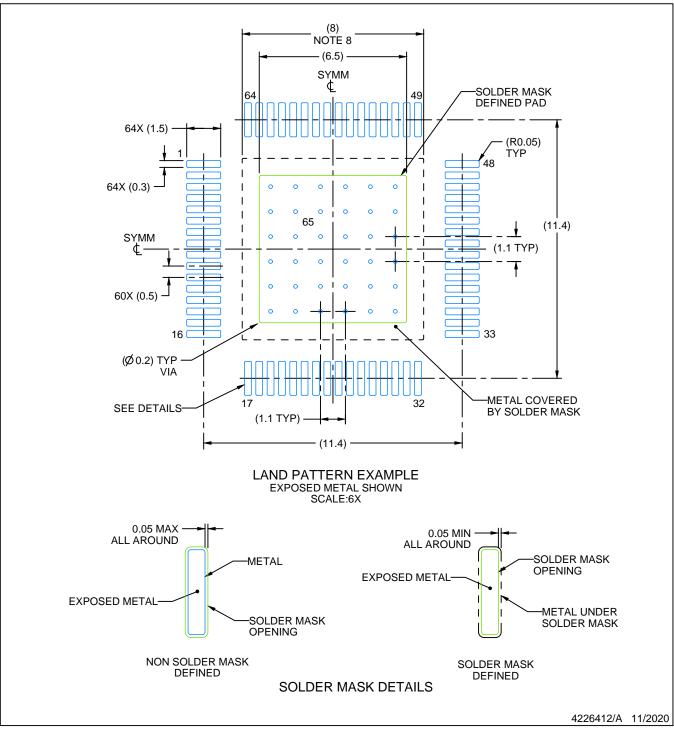

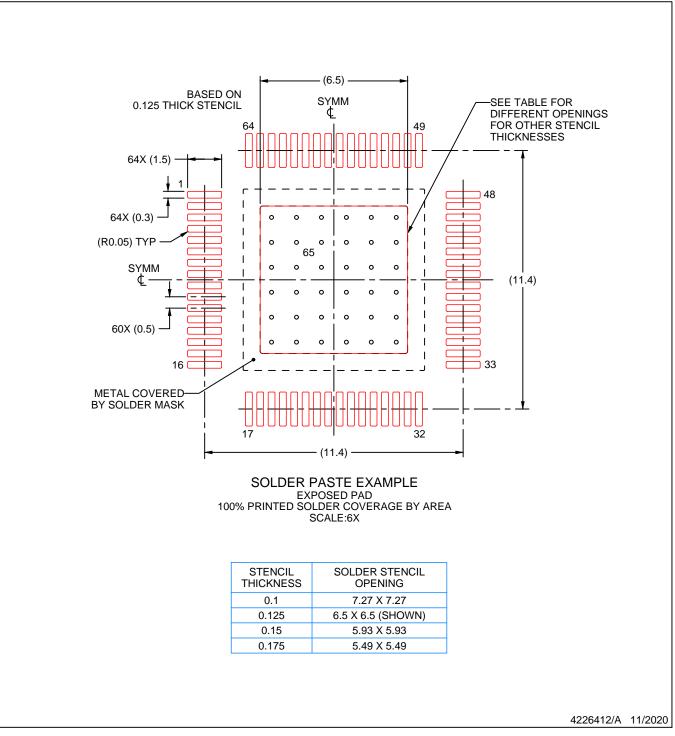

| Thermal pad | —                 | —                   | Thermal pad on bottom of PowerPAD <sup>™</sup> package; this must be soldered to similar-size copper area on PCB and connected to VSS, to meet stated specifications herein. Provides heat-sinking to part. |  |  |  |

(1) Key: I = digital input, AI = analog input, O = digital output, OD = open-drain output, T = 3-state output, P = power.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                  |                    |                                 | MIN                  | MAX                      | UNIT |

|------------------|--------------------|---------------------------------|----------------------|--------------------------|------|

| V <sub>MAX</sub> | Supply voltage     | BAT1, BAT2 <sup>(2)</sup>       | -0.3                 | 36                       | V    |

|                  |                    | VC1, VC2, VC3, VC4, VC5, VC6    | -0.3                 | 36                       |      |

| V <sub>IN</sub>  |                    | VC0                             | -0.3                 | 2                        |      |

|                  |                    | TS1+, TS1–, TS2+, TS2–          | -0.3                 | 6                        |      |

|                  | Innut voltogo      | GPAI                            | -0.3                 | 6                        | V    |

|                  | Input voltage      | GPIO                            | -0.3                 | V <sub>REG50</sub> + 0.3 | v    |

|                  |                    | DRDY_N, SDO_N, FAULT_N, ALERT_N | V <sub>BAT</sub> – 1 | V <sub>BAT</sub> + 2     |      |

|                  |                    | CONV_H, SDI_H, SCLK_H, CS_H     | -0.3                 | 6                        |      |

|                  |                    | CONV_S, SDI_S, SCLK_S, CS_S     | -2                   | 1                        |      |

|                  |                    | CONV_N, SDI_N, SCLK_N, CS_N     | -0.3                 | 36                       |      |

|                  |                    | SDO_H, FAULT_H, ALERT_H, DRDY_H | -0.3                 | 6                        |      |

| V                |                    | DRDY_S, SDO_S, FAULT_S, ALERT_S | -0.3                 | 5                        | V    |

| Vo               | Output voltage     | GPIO                            | -0.3                 | V <sub>REG50</sub> + 0.3 | v    |

|                  |                    | CB1CB6 (CBREF = 0x00)           | -0.3                 | 36                       |      |

|                  |                    | REG50, AUX                      | -0.3                 | 6                        |      |

| TJ               | Junction temperatu | Junction temperature            |                      | 150                      | °C   |

| T <sub>stg</sub> | Storage temperatur | e                               | -65                  | 150                      | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to VSS of this device, except where otherwise noted.

# 6.2 ESD Ratings

|                    |                         |                                                 |                                | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------|--------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100-           | 002 <sup>(1)</sup>             | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC             | All pins                       | ±500  | V    |

| * (ESD)            |                         | Charged-device model (CDM), per AEC<br>Q100-011 | Corner pins (1,16, 33, and 48) | ±750  | v    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

Typical values stated where  $T_A = 25^{\circ}$ C and  $V_{BAT} = 22$  V, Min/Max values stated where  $T_A = -40^{\circ}$ C to +105°C and  $V_{BAT} = 7.2$  V to 27 V (unless otherwise noted)

|                    |                                      |                                                         | MIN       | NOM     | MAX                   | UNIT |  |

|--------------------|--------------------------------------|---------------------------------------------------------|-----------|---------|-----------------------|------|--|

| V <sub>BAT</sub>   | Supply voltage                       | BAT                                                     | 7.2       |         | 27                    | V    |  |

|                    |                                      | $VCn-VC(n-1)^{(1)}$                                     | 1         |         | 4.5                   |      |  |

|                    |                                      | GPAI                                                    | 0         |         | 2.5                   |      |  |

|                    |                                      | GPIO                                                    | 0         |         | V <sub>REG50</sub>    |      |  |

|                    |                                      | CBn <sup>(1)</sup>                                      | VC(n - 1) |         | VCn                   |      |  |

|                    |                                      | TS1+, TS1–, TS2+, TS2–                                  | 0         |         | V <sub>REG50</sub> /2 |      |  |

| VI                 | Input voltage                        | Non-top IC in stack: DRDY_N, SDO_N,<br>FAULT_N, ALERT_N |           | BAT + 1 |                       | V    |  |

|                    |                                      | Top IC in stack: DRDY_N, SDO_N,<br>FAULT_N, ALERT_N     |           | BAT     |                       |      |  |

|                    |                                      | Non-bottom IC in stack: CONV_S, SDI_S, SCLK_S, CS_S     |           | -1      |                       |      |  |

|                    |                                      | Bottom IC in stack: CONV_S, SDI_S, SCLK_S, CS_S         |           | VSS     |                       |      |  |

|                    |                                      | Non-bottom IC in stack : CONV_N, SDI_N, SCLK_N, CS_N    |           | 1       |                       |      |  |

|                    | Outent ustrate                       | Bottom IC in stack: CONV_N, SDI_N, SCLK_N, CS_N         |           | VSS     |                       | V    |  |

| Vo                 | Output voltage                       | Non-top IC in stack: DRDY_S, SDO_S,<br>FAULT_S, ALERT_S |           | BAT – 1 |                       | V    |  |

|                    |                                      | Top IC in stack: DRDY_S, SDO_S,<br>FAULT_S, ALERT_S     |           | BAT     |                       |      |  |

| C <sub>REG50</sub> | External capacitor                   | REG50 pin                                               | 2.2       |         |                       | μF   |  |

| C <sub>VREF</sub>  | External capacitor                   | V <sub>REF</sub> pin                                    | 9.2       | 10      | 15                    | μF   |  |

| C <sub>LDO</sub>   | External capacitor                   | LDOx pin                                                | 2.2       |         | 3.3                   | μF   |  |

| T <sub>OPR</sub>   | Operating temperature <sup>(2)</sup> |                                                         | -40       |         | 105                   | °C   |  |

(1) n = 1 to 6

(2) Device specifications stated within this range.

# 6.4 Thermal Information

|                       |                                              | bq76PL536A-Q1 |      |

|-----------------------|----------------------------------------------|---------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PAP (HTQFP)   | UNIT |

|                       |                                              | 64 PINS       |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 24.6          | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 10            | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 8.1           | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3           | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 8             | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.4           | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

ZHCS267A-MAY 2011-REVISED DECEMBER 2016

www.ti.com.cn

STRUMENTS

ÈXAS

# 6.5 Electrical Characteristics

Typical values stated where  $T_A = 25^{\circ}$ C and  $V_{BAT} = 22$  V, Min/Max values stated where  $T_A = -40^{\circ}$ C to +105°C and  $V_{BAT} = 7.2$  V to 27 V (unless otherwise noted)

|                               | PARAMETER                   | TEST CONDITIONS                                                                                                                                                                                               | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY CUR                    | RENT                        |                                                                                                                                                                                                               |      |      |      |      |

| ICC <sub>SLEEP</sub>          | Supply current              | No load at REG50, SCLK_N, SDI_N, SDO_N, FAULT_N,<br>CONV_N, DRDY_S, ALERT_N, TSx, AUX, or CBx;<br>CB_CTRL = 0; CBT_CONTROL = 0;<br>CONV_H = 0 (not converting), IO_CONTROL[SLEEP] = 1                         |      | 12   | 22   | μA   |

| ICC <sub>PROTECT</sub>        | Supply current              | No load at REG50, SCLK_N, SDI_N, SDO_N, FAULT_N,<br>CONV_N, DRDY_S, ALERT_N, TSx, AUX, or CBx;<br>CB_CTRL = 0; CBT_CONTROL = 0; CONV_H = 0 (not converting),<br>IO_CONTROL[SLEEP] = 0                         |      | 45   | 60   | μA   |

| ICC <sub>BALANCE</sub>        | Supply current              | No load at REG50, SCLK_N, SDI_N, SDO_N, FAULT_N,<br>CONV_N, DRDY_S, ALERT_N, TSx, or AUX;<br>No DC load at CBx; CB_CTRL $\neq$ 0; CBT_CONTROL $\neq$ 0; CONV_H<br>= 0 (not converting), IO_CONTROL[SLEEP] = 0 |      | 46   | 60   | μA   |

| ICC <sub>CONVERT</sub>        | Supply current              | No load at REG50, SCLK_N, SDI_N, SDO_N, FAULT_N,<br>CONV_N, DRDY_S, ALERT_N, TSx or CBx; CONV_S = 1<br>(conversion active) , IO_CONTROL[SLEEP] = 0                                                            |      | 10.5 | 15   | mA   |

| ICC <sub>TSD</sub>            | Supply current              | Thermal shutdown activated; ALERT_STATUS[TSD] = 1                                                                                                                                                             |      | 1.6  |      | mA   |

| REG50, INTE                   | GRATED 5-V LDO              |                                                                                                                                                                                                               |      |      |      |      |

| V <sub>REG50</sub>            | Output voltage              | $I_{REG500UT} \le 0.5$ mA, C = 2.2 $\mu$ F to 22 $\mu$ F                                                                                                                                                      | 4.9  | 5    | 5.1  | V    |

| $\Delta V_{\text{REG50LINE}}$ | Line regulation             | 7.2 V $\leq$ BAT $\leq$ 27 V, I <sub>REG500UT</sub> = 2 mA                                                                                                                                                    |      | 10   | 25   | mV   |

| ΔV <sub>REG50LOAD</sub>       | Load regulation             | $0.2 \text{ mA} \le I_{\text{REG50OUT}} \le 2 \text{ mA}$                                                                                                                                                     |      |      | 15   | mV   |

| △ V REG50LOAD                 | Load regulation             | $0.2 \text{ mA} \le I_{\text{REG50OUT}} \le 5 \text{ mA}$                                                                                                                                                     |      |      | 25   | IIIV |

| I <sub>REG50MAX</sub>         | Current limit               |                                                                                                                                                                                                               | 12   | 25   | 35   | mA   |

| I <sub>AUXMAX</sub>           | Maximum load                | AUX pin                                                                                                                                                                                                       |      |      | 5    | mA   |

| R <sub>AUX</sub>              | AUX output                  | I = 1 mA, max. capacitance = $V_{REG50}$<br>Capacitor: $C_{VAUX} \le C_{VREG50} / 10$                                                                                                                         |      |      | 50   | Ω    |

| LEVEL SHIFT                   | INTERFACE                   |                                                                                                                                                                                                               |      |      |      |      |

| I <sub>NTX1</sub>             | North 1 transmitter current | SCLK_N, CS_N, SDI_N, CONV_N                                                                                                                                                                                   | 1000 | 1350 | 1800 | μA   |

| I <sub>NTX0</sub>             | North 0 transmitter current | CS_N, CONV_N                                                                                                                                                                                                  |      |      | 1    | μA   |

| I <sub>NTX0A</sub>            | North 0 transmitter current | SCLK_N, SDI_N (BASE device CS_H = 1)                                                                                                                                                                          |      |      | 1    | μA   |

| I <sub>NTX0B</sub>            | North 0 transmitter current | SCLK_N, SDI_N (BASE device CS_H = 0)                                                                                                                                                                          | 50   | 75   | 110  | μA   |

| I <sub>SRX</sub>              | South 1 receiver threshold  | SCLK_S, CS_S, SDI_S, CONV_S                                                                                                                                                                                   | 430  | 550  | 680  | μA   |

| I <sub>SRXH</sub>             | South receiver hysteresis   | SCLK_S, CS_S, SDI_S, CONV_S                                                                                                                                                                                   |      | 100  | 200  | μA   |

| I <sub>STX1</sub>             | South 1 transmitter current | ALERT_N, FAULT_S, DRDY_S                                                                                                                                                                                      | 800  | 1100 | 1400 | μA   |

| I <sub>STX0</sub>             | South 0 transmitter current | ALERT_S, FAULT_S, DRDY_S                                                                                                                                                                                      |      |      | 1    | μA   |

| I <sub>STX0A</sub>            | South 0 transmitter current | SDO_S (BASE device CS_H = 1)                                                                                                                                                                                  |      |      | 1    | μA   |

| I <sub>STX0B</sub>            | South 0 transmitter current | SDO_S (BASE device CS_H = 0)                                                                                                                                                                                  | 1    | 4    | 7    | μA   |

| I <sub>NRX</sub>              | North 1 receiver threshold  | SDO_N, ALERT_N, FAULT_N, DRDY_N                                                                                                                                                                               | 420  | 580  | 720  | μA   |

| I <sub>NRXH</sub>             | North receiver hysteresis   | SDO_N, ALERT_N, FAULT_N, DRDY_N                                                                                                                                                                               | 50   | 100  | 200  | μA   |

| CIN                           | Input capacitance           |                                                                                                                                                                                                               |      | 15   |      | pF   |

# Electrical Characteristics (接下页)

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 22$  V, Min/Max values stated where  $T_A = -40^{\circ}C$  to +105°C and  $V_{BAT} = 7.2$  V to 27 V (unless otherwise noted)

|                         | PARAMETER                                                                                                                              | TEST CONDITIONS                                                                                                            | MIN               | TYP  | MAX               | UNIT              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------|------|-------------------|-------------------|

| HOST INTER              | FACE                                                                                                                                   |                                                                                                                            |                   |      |                   |                   |

| V <sub>OH</sub>         | Logic-level output voltage,<br>high; SDO_H, FAULT_H,<br>ALERT_H, DRDY                                                                  | $C_{L} = 20 \text{ pF}, \text{ I}_{OH} < 5 \text{ mA}^{(1)}$                                                               | 4.5               |      | V <sub>LDOD</sub> | V                 |

| V <sub>OL</sub>         | Logic-level output voltage,<br>low; SDO_H, FAULT_H,<br>ALERT_H, DRDY                                                                   | C <sub>L</sub> = 20 pF, I <sub>OL</sub> < 5 mA <sup>(1)</sup>                                                              | VSS               |      | 0.5               | V                 |

| V <sub>IH</sub>         | Logic-level input voltage, high;<br>SCLK_H, SDI_H, CS_H,<br>CONV                                                                       |                                                                                                                            | 2                 |      |                   | V                 |

| V <sub>IL</sub>         | Logic-level input voltage, low;<br>SCLK_H, SDI_H, CS_H,<br>CONV                                                                        |                                                                                                                            |                   |      | 0.8               | V                 |

| C <sub>IN</sub>         | Input Capacitance CONV_H <sup>(2)</sup><br>Input Capacitance CS_H <sup>(3)</sup><br>Input Capacitance SCLK_H,<br>SDI_H                 |                                                                                                                            |                   | 5    |                   | pF                |

| I <sub>LKG</sub>        | IInput leakage current<br>CONV_H <sup>(2)</sup><br>Input leakage current CS_H <sup>(3)</sup><br>Input leakage current<br>SCLK_H, SDI_H |                                                                                                                            |                   |      | 1                 | μΑ                |

| GENERAL P               | URPOSE INPUT/OUTPUt (GPIO)                                                                                                             | , i i i i i i i i i i i i i i i i i i i                                                                                    |                   |      |                   |                   |

| V <sub>IH</sub>         | Logic-level input voltage, high                                                                                                        | $Vin \le V_{REG50}$                                                                                                        | 2                 |      |                   | V                 |

| V <sub>IL</sub>         | Logic-level input voltage, low                                                                                                         |                                                                                                                            |                   |      | 0.8               | V                 |

| V <sub>OH</sub>         | Output high-voltage pull-up voltage                                                                                                    | Supplied by external approximately 100-k $\Omega$ resistor                                                                 |                   |      | $V_{REG50}$       | V                 |

| V <sub>OL</sub>         | Logic-level output voltage, low                                                                                                        | I <sub>OL</sub> = 1 mA                                                                                                     | 0.3               |      |                   | V                 |

| C <sub>IN</sub>         | Input capacitance(1)                                                                                                                   |                                                                                                                            |                   | 5    |                   | pF                |

| I <sub>LKG</sub>        | Input leakage current                                                                                                                  |                                                                                                                            |                   |      | 1                 | μΑ                |

| CELL BALAN              | NCING CONTROL OUTPUT (CB                                                                                                               | x)                                                                                                                         |                   |      |                   |                   |

| CBz                     | Output impedance                                                                                                                       | 1 V < V <sub>CELL</sub> < 5 V                                                                                              | 80                | 100  | 125               | kΩ                |

| V <sub>RANGE</sub>      | Output V                                                                                                                               |                                                                                                                            | V <sub>Cn-1</sub> |      | $V_{Cn}$          | V                 |

| ADC COMMO               | ON SPECIFICATIONS                                                                                                                      |                                                                                                                            |                   |      | ·                 |                   |

|                         | CONV high to conversion                                                                                                                | ADC_CONTROL[ADC_ON] = 1                                                                                                    | 5.4               | 6    | 6.6               | μs                |

| t <sub>CONV_START</sub> | start <sup>(4) (5)</sup>                                                                                                               | ADC_CONTROL[ADC_ON] = 0                                                                                                    |                   | 500  |                   | μs                |

| t <sub>CONV</sub>       | Conversion time per selected channel <sup>(6)</sup>                                                                                    | ADC_CONTROL[ADC_ON] = 1                                                                                                    | 5.4               | 6    | 6.6               | μs                |

| I <sub>LKG</sub>        | Input leakage current                                                                                                                  | Not converting, measured differentially                                                                                    |                   | <10  | 100               | nA                |

| VCn (CELL)              | INPUTS <sup>(7)</sup>                                                                                                                  |                                                                                                                            |                   |      |                   |                   |

| V <sub>IN</sub>         | Input voltage range <sup>(8)</sup>                                                                                                     | VCn - VCn-1, where n = 1 to 6                                                                                              | 0                 |      | 6                 | V                 |

| V <sub>RES</sub>        | Voltage resolution <sup>(9)</sup>                                                                                                      | 14 bits                                                                                                                    |                   | ~378 |                   | μV                |

| V <sub>ACC</sub>        | Voltage accuracy, total error,<br>V <sub>IN</sub> = VCn to VCn–1                                                                       | $-10^{\circ}\text{C} \le \text{T}_{\text{A}} \le 50^{\circ}\text{C}, 1.2 \text{ V} < \text{V}_{\text{IN}} < 4.5 \text{ V}$ | -2.5              | ±1   | 2.5               | mV                |

|                         |                                                                                                                                        | $-40^{\circ}C \le T_{A} \le 105^{\circ}C, 1.2 V < V_{IN} < 4.5 V$                                                          | -5                | 2    | 5                 | Mo                |

| R <sub>IN</sub>         | Effective input resistance                                                                                                             | Converting                                                                                                                 |                   | 2    |                   | MΩ                |

| C <sub>IN</sub>         | Input capacitance                                                                                                                      | Converting                                                                                                                 |                   | 1    |                   | pF                |

| E <sub>N</sub>          | Noise                                                                                                                                  | V <sub>IN</sub> = 3 V                                                                                                      |                   |      | 250               | μV <sub>RMS</sub> |

(1) Total simultaneous current drawn from all pins is limited by LDOD current to  $\leq$  10 mA.

Pin has 250-nA internal sink to VSS. (2)

(3) Pin has 100-k $\Omega$  internal pull-up resistor.

If ADC\_CONTROL[ADC\_ON] = 0, add 500  $\mu$ s to conversion time to allow ADC subsystem to stabilize. This is self-timed by the part. Additional 50 ms (POR) is required before first conversion after a) initial cell connection; or b) V<sub>BAT</sub> falls below V<sub>POR</sub>. Plus t<sub>CONV\_START</sub>, that is, if device is programmed for six channel conversions, total time is approximately 6 x 6 + 6 = 42  $\mu$ s. FUNCTION\_CONFIG[]=01xxxx00b for all test conditions (6- $\mu$ s conversion time selected). (4)

(5)

(6)

(7)

0 V may not lie within the range of measured values due to offset voltage limit and device calibration. (8)

See text for specific conversion formula. (9)

版权 © 2011-2016, Texas Instruments Incorporated

ZHCS267A-MAY 2011-REVISED DECEMBER 2016

www.ti.com.cn

STRUMENTS

XAS

# Electrical Characteristics (接下页)

Typical values stated where  $T_A = 25^{\circ}$ C and  $V_{BAT} = 22$  V, Min/Max values stated where  $T_A = -40^{\circ}$ C to +105°C and  $V_{BAT} = 7.2$  V to 27 V (unless otherwise noted)

|                         | PARAMETER                                              | TEST CONDITIONS                                                            | MIN     | TYP    | MAX   | UNIT              |

|-------------------------|--------------------------------------------------------|----------------------------------------------------------------------------|---------|--------|-------|-------------------|

| VBAT (VBRICK)           | MEASUREMENT <sup>(10)</sup>                            |                                                                            |         |        |       |                   |

| V <sub>IN</sub>         | Input voltage range, BATn to VSS                       | FUNCTION_CONFIG[] = 0101xx00b                                              | 0       |        | 30    | V                 |

| V <sub>RES</sub>        | Voltage resolution <sup>(11)</sup>                     | 14 bits                                                                    |         | ~1.831 |       | mV                |

| V <sub>ACC</sub>        | Voltage accuracy                                       | Total error 7.2 V $\leq$ V <sub>IN</sub> $\leq$ 27 V                       | -80     | -30    | 20    | mV                |

| C <sub>IN</sub>         | Input capacitance                                      | Converting                                                                 | verting |        |       | pF                |

| R <sub>IN</sub>         | Effective input resistance                             | Converting                                                                 |         | 50     |       | kΩ                |

| E <sub>N</sub>          | Noise                                                  |                                                                            |         |        | 1.5   | mV <sub>RMS</sub> |

| GPAI MEASU              | IREMENT <sup>(12)</sup>                                |                                                                            |         |        |       |                   |

| V <sub>IN</sub>         | Input voltage range, <sup>(13)</sup> GPAI+<br>to GPAI– |                                                                            | 0       |        | 2.5   | V                 |

| V <sub>RES</sub>        | Voltage resolution <sup>(14)</sup>                     | 14 bits                                                                    |         | ~153   |       | μV                |

|                         | Voltage accuracy, V <sub>IN</sub> =                    | $0.25 \text{ V} \le \text{V}_{IN} \le 2.5 \text{ V}$                       | -7      |        | 7     |                   |

| V <sub>ACC</sub>        | GPAI+ – GPAI–                                          | V <sub>IN</sub> = 1.25 V, T <sub>A</sub> = 25°C                            |         | ±2     |       | mV                |

| C <sub>IN</sub>         | Input capacitance                                      | Converting                                                                 |         | 40     |       | pF                |

| R <sub>IN</sub>         | Effective input resistance                             | Converting                                                                 |         | 50     |       | kΩ                |

| E <sub>N</sub>          | Noise                                                  |                                                                            |         |        | 150   | μV <sub>RMS</sub> |

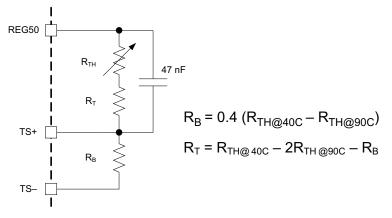

| TSn MEASUF              | REMENT <sup>(15)</sup>                                 |                                                                            |         |        |       |                   |

| V <sub>IN</sub>         | Input voltage range, <sup>(16)</sup> TSn+<br>TSn–      |                                                                            | 0       |        | 2.5   | V                 |

| V <sub>RES</sub>        | Voltage resolution <sup>(17)</sup>                     | 14 bits, REG50 = 5 V,<br>(Resolution $\approx V_{\text{REG50}} / 2^{15}$ ) |         | ≈153   |       | μV                |

|                         | D (17)                                                 | $45 \text{ mV} \le \text{V}_{\text{IN}} < 250 \text{ mV}$                  | -3.5%   | ±1%    | +3.5% |                   |

| V <sub>ACC</sub>        | Ratio accuracy, % of input <sup>(17)</sup>             | $250 \text{ mV} \le \text{V}_{\text{IN}} \le 2.4 \text{ V}$                | -0.5%   | ±0.2%  | +0.5% |                   |

| CIN                     | Input capacitance                                      | Converting                                                                 |         | 40     |       | pF                |

| R <sub>IN</sub>         | Effective input resistance                             | Converting                                                                 |         | 50     |       | kΩ                |

| E <sub>N</sub>          | Noise                                                  |                                                                            |         |        | 150   | μV <sub>RMS</sub> |

| THERMAL SI              | IUTDOWN                                                | I                                                                          |         |        | 1     |                   |

| T <sub>SD</sub>         | Shutdown threshold                                     | V <sub>BAT</sub> = 22 V                                                    | 125     | 142    | 156   | °C                |

| T <sub>HYS</sub>        | Recovery hysteresis                                    |                                                                            |         | 8      | 25    | °C                |

| JNDERVOLT               | AGE LOCKOUT (UVLO) and PO                              | WER-ON RESET (POR)                                                         |         |        |       |                   |

| V <sub>UVLO</sub>       | Negative-going threshold                               |                                                                            | 5       |        | 5.6   | V                 |

| V <sub>UVLO HSY</sub>   | Hysteresis                                             |                                                                            | 250     | 375    | 500   | mV                |

|                         | Delay to locked-out condition                          | V ≤ V <sub>UVLO</sub> MIN                                                  |         | 15     |       | μS                |

| V <sub>POR</sub>        | Negative-going threshold                               |                                                                            | 4       |        | 5     | V                 |

| V <sub>POR_HSY</sub>    | Hysteresis                                             |                                                                            | 250     | 500    | 750   | mV                |

| POR <sub>DELAY</sub>    | Delay to disabled condition                            | V ≤ V <sub>POR</sub> MIN                                                   |         | 15     |       | μs                |

| RST                     | Reset delay time                                       | $V \ge V_{POR} + V_{POR_{HSY}}$                                            | 40      | 56     | 70    | ms                |

| V <sub>DELTA_RISE</sub> | Voltage delta between trip points                      | V <sub>UVLO</sub> – V <sub>POR</sub> (V <sub>BAT</sub> rising)             | 0.25    | 0.4    | 0.7   | V                 |

| V <sub>DELTA_FALL</sub> | Voltage delta between trip points                      | V <sub>UVLO</sub> – V <sub>POR</sub> (V <sub>BAT</sub> falling)            | 0.4     | 0.52   | 0.7   | V                 |

|                         | OTECTION THRESHOLDS                                    |                                                                            | 4       |        |       |                   |

(10) FUNCTION\_CONFIG[] = 01xxxx00b for all test conditions

(11) See text for specific conversion formula.

(12) FUNCTION\_CONFIG[] = 0101xx00b for all test conditions

(13) 0 V may not lie within the range of measured values due to offset voltage limit and device calibration.

(14) See text for specific conversion formula.

(15) FUNCTION\_CONFIG[]=01xxxx00b for all Test Conditions

(16) 0 V may not lie within the range of measured values due to offset voltage limit and device calibration.

(17) See text for specific conversion formula.

# Electrical Characteristics (接下页)

Typical values stated where  $T_A = 25^{\circ}$ C and  $V_{BAT} = 22$  V, Min/Max values stated where  $T_A = -40^{\circ}$ C to +105°C and  $V_{BAT} = 7.2$  V to 27 V (unless otherwise noted)

|                   | PARAMETER                                                    | TEST CONDITIONS                                                                   | MIN    | TYP      | MAX  | UNIT |

|-------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|----------|------|------|

| V <sub>OVR</sub>  | OV detection threshold range <sup>(18)</sup>                 | $V_{BAT}$ = 12 V and 27 V                                                         | 2      |          | 5    | V    |

| $\Delta V_{OVS}$  | OV detection threshold<br>program step                       | $V_{BAT}$ = 12 V and 27 V                                                         |        | 50       |      | mV   |

| V <sub>OVH</sub>  | OV detection hysteresis                                      | V <sub>BAT</sub> = 12 V and 27 V                                                  |        | 50       |      | mV   |

| V <sub>OVA1</sub> | OV detection threshold<br>accuracy                           | $3.3 \le V_{OV\_SET} \le 4.5$                                                     | -50    | 0        | 50   | mV   |

| V <sub>OVA2</sub> | OV detection threshold<br>accuracy                           | <sub>OV_SET</sub> < 3.3 or V <sub>OV_SET</sub> > 4.5                              |        | 0        | 70   | mV   |

| V <sub>UVR</sub>  | UV detection threshold range <sup>(18)</sup>                 | $V_{BAT} = 22 V$                                                                  | 700    |          | 3300 | mV   |

| ΔV <sub>UVS</sub> | UV detection threshold<br>program step                       | V <sub>BAT</sub> = 22 V                                                           |        | 100      |      | mV   |

| V <sub>UVH</sub>  | UV detection hysteresis                                      | V <sub>BAT</sub> = 22 V                                                           |        | 100      |      | mV   |

| V <sub>UVA</sub>  | UV detection threshold<br>accuracy                           |                                                                                   | -100   | 0        | 100  | mV   |

| V <sub>OTR</sub>  | OT detection threshold range <sup>(19)</sup>                 | $V_{\text{REG50}} = 5 \text{ V}$                                                  | 1      |          | 2    | V    |

| Δ <sub>VOTS</sub> | OT detection threshold program step <sup>(19)</sup>          |                                                                                   |        | See (20) |      | V    |

| V <sub>OTA</sub>  | OT detection threshold accuracy <sup>(19)</sup>              | $T = 40^{\circ}C \text{ to } 90^{\circ}C$                                         | -0.015 | 0.01     | 0.05 | V    |

| $\Delta V_{OTH}$  | OT reset hysteresis <sup>(21)</sup>                          | $T = 40^{\circ}C$ to $90^{\circ}C$                                                | 8%     | 12%      | 15%  |      |

| BATTERY           | PROTECTION DELAY TIMES                                       |                                                                                   |        |          |      |      |

| tov               | OV detection delay-time<br>range                             |                                                                                   | 0      |          | 3200 | ms   |

| ۸+                | OV detection delay-time step                                 | COVT [µs] = 0                                                                     |        | 100      |      | μs   |

| ∆t <sub>OV</sub>  | Ov detection delay-time step                                 | COVT [ms] = 1                                                                     |        | 100      |      | ms   |

| uv                | UV detection delay-time range                                |                                                                                   | 0      |          | 3200 | ms   |

| ∆t <sub>UV</sub>  | UV detection delay-time step                                 | CUVT[7] (µs) = 0                                                                  |        | 100      |      | μs   |

| 7 <b>1</b> 00     |                                                              | CUVT[7] (ms) = 1                                                                  |        | 100      |      | ms   |

| <sup>t</sup> от   | OT detection delay-time range                                |                                                                                   | 0      |          | 2550 | ms   |

| $\Delta t_{OT}$   | OT detection delay-time step                                 |                                                                                   |        | 10       |      | ms   |

| t <sub>acr</sub>  | OV, UV, and OT detection delay-time accuracy <sup>(22)</sup> | CUVT, (COVT) ≥ 500 µs                                                             | -12%   | 0%       | 10%  |      |

| (DETECT)          | Protection comparator detection time                         | $V_{\text{OT}}$ or $V_{\text{OV}}$ or $V_{\text{UV}}$ threshold exceeded by 10 mV |        |          | 100  | μs   |

| OTP EPRO          | M PROGRAMMING CHARACTER                                      | ISTICS                                                                            |        |          |      |      |

| V <sub>PROG</sub> | Programming voltage                                          |                                                                                   | 6.75   | 7        | 7.25 | V    |

| t <sub>PROG</sub> | Programming time                                             | V <sub>BAT</sub> ≥ 22 V                                                           |        |          | 50   | ms   |

| I <sub>PROG</sub> | Programming current                                          |                                                                                   |        | 10       | 20   | mA   |

(18) COV and CUV thresholds must be set such that COV – CUV  $\geq$  300 mV

(19) Using recommended components. Consult 表 2 in text for voltage levels used.

(20) See 表 2 for trip points.

(21) Hysteresis measured to trip point voltage.

(22) Under double or multiple fault conditions (of a single type), the second or greater fault may have its delay time shortened by up to the step time for the fault. For example, the second and subsequent COV faults occurring within the delay time period for the first fault may have their delay time shortened by up to 100 µs.

ZHCS267A-MAY 2011-REVISED DECEMBER 2016

www.ti.com.cn

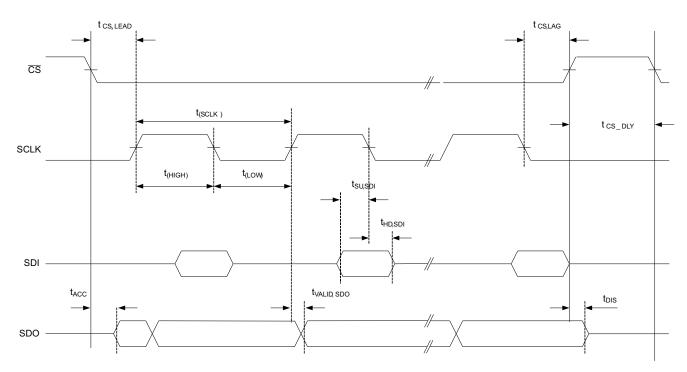

# 6.6 Timing Requirements: AC SPI Data Interface

Typical values stated where  $T_A = 25^{\circ}$ C and  $V_{BAT} = 22$  V, Min/Max values stated where  $T_A = -40^{\circ}$ C to +105°C and  $V_{BAT} = 7.2$  V to 27 V (unless otherwise noted) See 1.

|                        |                                                                          |                        | MIN | NOM    | MAX  | UNIT |

|------------------------|--------------------------------------------------------------------------|------------------------|-----|--------|------|------|

| f <sub>SCLK</sub>      | SCLK frequency <sup>(1)</sup>                                            |                        | 10  | 250    | 1000 | kHz  |

| SCLK <sub>DC</sub>     | SCLK_H duty cycle, $t_{(HIGH)} / t_{(SCLK)}$ or $t_{(LOW)} / t_{(SCLK)}$ | t(SCLK)                | 40% |        | 60%  |      |

| t <sub>CS,LEAD</sub>   | CS_H lead time, CS_H low to clock                                        |                        |     | SCLK/2 |      | ns   |

| t <sub>CS,LAG</sub>    | CS_H lag time. Last clock to CS_H high                                   |                        |     | SCLK/2 |      | ns   |

| t <sub>CS,DLY</sub>    | CS_H high to CS_H low (inter-packet delay requirement)                   |                        |     |        |      | μs   |

| t <sub>ACC</sub>       | CS_H access time <sup>(2)</sup> : CS_H low to SDO_H da                   | ita out                |     | 125    | 250  | ns   |

| t <sub>DIS</sub>       | CS_H disable time <sup>(2)</sup> : CS_H high to SDO_H h                  | igh impedance          |     | 2.5    | 2.7  | μs   |

| t <sub>SU,SDI</sub>    | SDI_H input-data setup time                                              |                        | 15  |        |      | ns   |

| t <sub>HD,SDI</sub>    | SDI_H input-data hold time                                               |                        | 10  |        |      | ns   |

| t <sub>VALID,SDO</sub> | SDO_H output-data valid time<br>SCLK_H edge to SDO_H valid               | C <sub>L</sub> ≤ 20 pF |     | 75     | 110  | ns   |

(1) Maximum SCLK frequency is limited by the number of bq76PL536A-Q1 devices in the vertical stack. The maximum listed here may not be realizable in systems due to delays and limits imposed by other components including wiring, connectors, PCB material and routing, and so forth. See text for details.

(2) Time listed is for single device.

# 6.7 Vertical Communications Bus

Typical values stated where  $T_A = 25^{\circ}C$  and  $V_{BAT} = 22$  V (unless otherwise noted)

|                       |                                       |          | MIN NOM <sup>(1)</sup> MA | X UNIT |

|-----------------------|---------------------------------------|----------|---------------------------|--------|

| t <sub>HV_SCLK</sub>  | Propagation delay, SCLK_H to SCLK_N   | HOST = 0 | 40                        | ns     |

| t <sub>VB_SCLK</sub>  | Propagation delay, SCLK_S to SCLK_N   | HOST = 1 | 30                        | ns     |

| t <sub>HV_CS</sub>    | Propagation delay, CS_H to CS_N       | HOST = 0 | 40                        | ns     |

| t <sub>VB_CS</sub>    | Propagation delay, CS_S to CS_N       | HOST = 1 | 30                        | ns     |

| t <sub>HV_SDI</sub>   | Propagation delay, SDI_H to SDI_N     | HOST = 0 | 40                        | ns     |

| t <sub>VB_SDI</sub>   | Propagation delay, SDI_S to SDI_N     | HOST = 1 | 30                        | ns     |

| t <sub>HV_CONV</sub>  | Propagation delay, CONV_H to CONV_N   | HOST = 0 | 100                       | ns     |

| t <sub>VB_CONV</sub>  | Propagation delay, CONV_S to CONV_N   | HOST = 1 | 30                        | ns     |

| t <sub>HV_SDO</sub>   | Propagation delay, SDO_N to SDO_H     | HOST = 0 | 10                        | ns     |

| t <sub>VB_SDO</sub>   | Propagation delay, SDO_N to SDO_S     | HOST = 1 | 40                        | ns     |

| t <sub>HV_DRDY</sub>  | Propagation delay, DRDY_N to DRDY_H   | HOST = 0 | 60                        | ns     |

| t <sub>VB_DRDY</sub>  | Propagation delay, DRDY_N to DRDY_S   | HOST = 1 | 40                        | ns     |

| t <sub>HV_FAULT</sub> | Propagation delay, FAULT_N to FAULT_H | HOST = 0 | 55                        | ns     |

| t <sub>VB_FAULT</sub> | Propagation delay, FAULT_N to FAULT_S | HOST = 1 | 30                        | ns     |

| t <sub>HV_ALERT</sub> | Propagation delay, ALERT_N to ALERT_H | HOST = 0 | 65                        | ns     |

| t <sub>VB_ALERT</sub> | Propagation delay, ALERT_N to ALERT_S | HOST = 1 | 30                        | ns     |

(1) Nominal values are quoted in place of MIN/MAX for design guidance only. Actual propagation delay depends heavily on wiring and capacitance in the signal path. These parameters are not tested in production due to these dependencies on system design considerations.

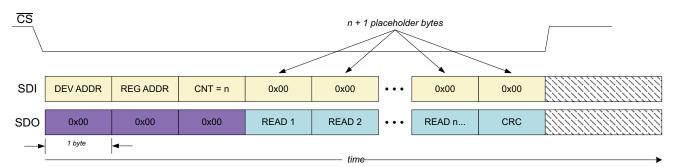

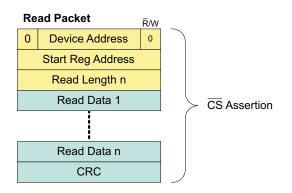

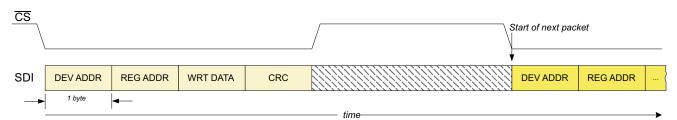

图 1. SPI Host Interface Timing

bq76PL536A-Q1 ZHCS267A-MAY 2011-REVISED DECEMBER 2016

www.ti.com.cn

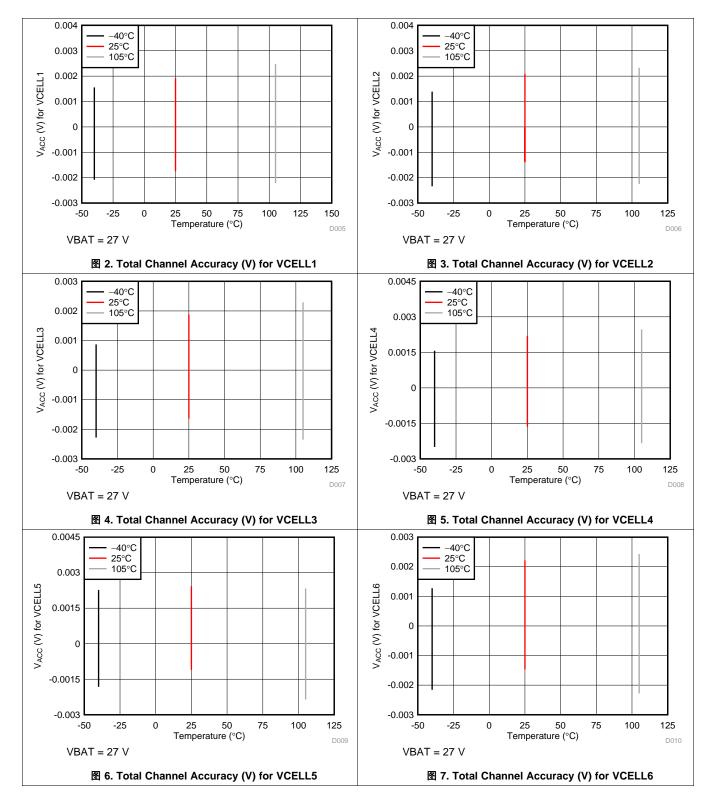

# 6.8 Typical Characteristics

# Typical Characteristics (接下页)

TEXAS INSTRUMENTS

# 7 Detailed Description

# 7.1 Overview

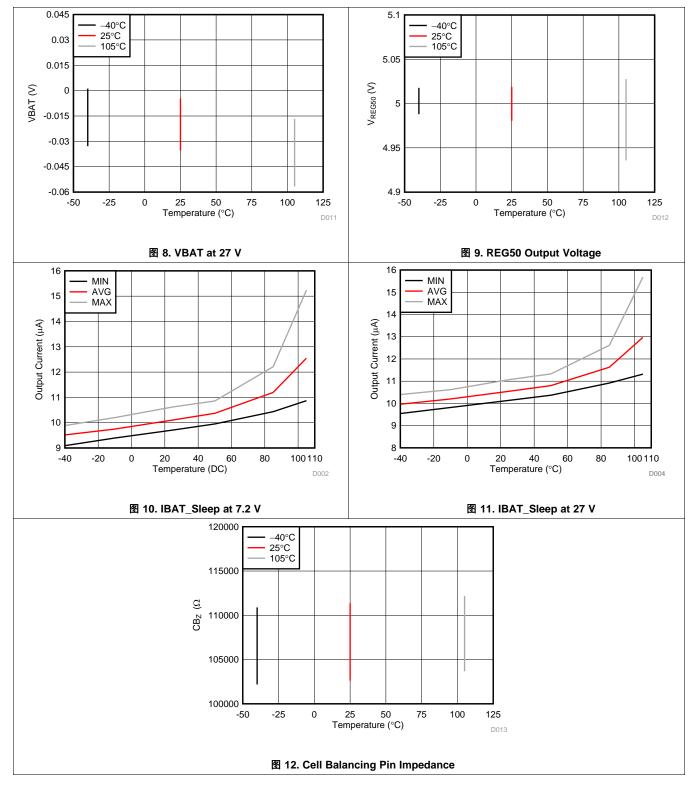

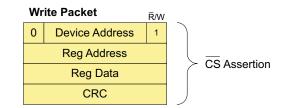

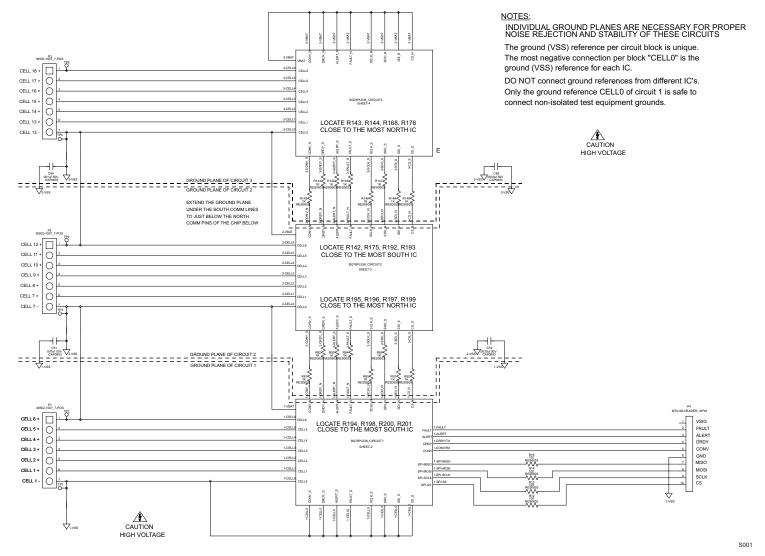

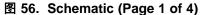

The bq76PL536A-Q1 is a 3-to-6 series Lithium-ion battery monitor, secondary protector and analog front end (AFE) that can be stacked vertically to monitor up to 192 cells without the need for additional isolation components between ICs.

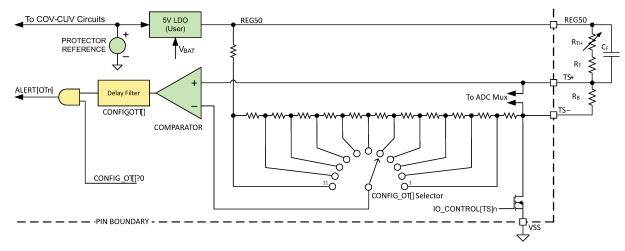

This device incorporates a precision analog-to-digital converter (ADC); independent cell voltage and temperature protection; cell balancing, and precision 5-V regulator to power user circuitry. The bq76PL536A-Q1 additionally provides full (secondary) protection for overvoltage, undervoltage, and overtemperature conditions.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

# 7.3.1 Analog-to-Digital Conversion (ADC)

# 7.3.1.1 General Features

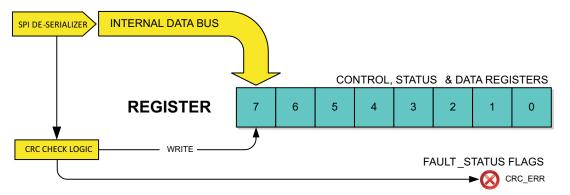

The integrated 14-bit (unsigned) high-speed successive approximation register (SAR) analog-to-digital converter uses an integrated band-gap reference voltage ( $V_{REF}$ ) for the cell and brick measurements. The ADC has a frontend multiplexer for nine inputs – six cells, two temperature sensors, and one general-purpose analog input (GPAI). The GPAI input can further be multiplexed to measure the *brick* voltage between the BATx pin and VSS or the voltage between the GPAI+ and GPAI– pins.

The ADC and reference are factory trimmed to compensate for gain, offset, and temperature-induced errors for all inputs. The measurement result is not allowed to roll over due to offset error at the top and bottom of the range. For example, a reading near zero does not underflow to 0x03ff due to offset error and vice-versa.

The converter returns 14 valid unsigned magnitude bits in the following format:

<00xxxxxx xxxxxxx>

Each word is returned in big-endian format in a register pair consisting of two adjacent 8-bit registers. The MSB of the word is located in the lower-address register of the pair, that is, data for cell 1 is returned in registers 0x03 and 0x04 as 00xxxxx xxxxxxb.

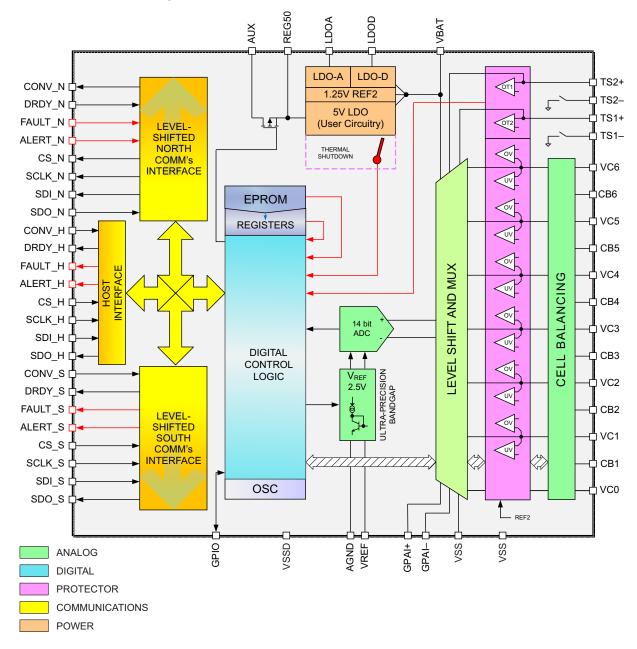

# 7.3.1.2 3-to-6 Series Cell Configuration

When fewer than 6 cells are used, the most-positive cell voltage of the series string should be connected to the BAT1/BAT2 pins, through the RC input network shown in the *Typical Application* section. Unused VCx inputs should be connected to the next VCx input down until an input connected to a cell is reached – that is, in a four cell stack, VC6 connects to VC5, which connects to VC4 (图 13).

The internal multiplexer control can be set to scan only the inputs which are connected to cells, thereby speeding up conversions slightly. The multiplexer is controlled by the ADC\_CONTROL[CN2:0] bits.

图 13. Connecting < 6 Cells (4 Shown)

# Feature Description (接下页)

# 7.3.1.3 Cell Voltage Measurements

Use the following formula (all values are in decimal) to convert the returned cell measurement value to a dc voltage (in mV).

$\mathsf{mV} = (\mathsf{REG}_{\mathsf{MSB}} \times 256 + \mathsf{REG}_{\mathsf{LSB}}) \times 6250 \ / \ 16383$

Example:

Cell\_1 ==  $3.35 \vee (3350 \text{ mV})$ ; After conversion, REG\_03 == 0x22; REG\_04 == 0x4d $0x22 \times 0x100 + 0x4d = 0x224d$  (8781.) 8781  $\times 6250 / 16,383 = 3349.89 \text{ mV} \approx 3.35 \vee$

# 7.3.1.4 GPAI or V<sub>BAT</sub> Measurements

The bq76PL536A-Q1 features a differential input to the ADC from two external pins, GPAI+ and GPAI-. The ADC GPAI result register can be configured (via the FUNCTION\_CONFIG[GPAI\_SRC] to provide a measurement of the voltage on these two pins, or of the *brick* voltage present between the BATx pins and VC0.