## LM4030,LM4128,LM4132

?????????

Literature Number: ZHCA411

## Expert tips, tricks, and techniques for powerful designs

#### No. 123

| _          |       |          |      |

|------------|-------|----------|------|

| Foaturo    | Artic | е        | 1_10 |

| i catare i |       | <b>G</b> | 1-10 |

High-Precision References.....2

### **Voltage Reference Selection Basics**

— By David Megaw, Design Engineer

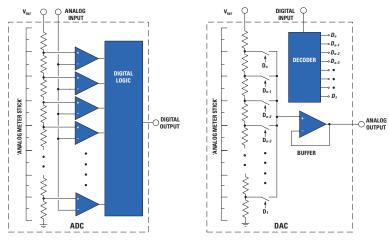

Voltage references are a key building block in data conversion systems, and understanding their specifications and how they contribute to error is necessary for selecting the right reference for the application. Figure 1 shows the application of a voltage reference in a simple analog-to-digital converter (ADC) and digital-to-analog converter (DAC). In each case, the reference voltage (V<sub>REF</sub>) acts as a very precise analog 'meter stick' against which the incoming analog signal is compared (as in an ADC) or the outgoing analog signal is generated (DAC). As such, a stable system reference is required for accurate and repeatable data conversion; and as the number of bits increases, less reference error can be tolerated. Monolithic voltage references produce an output voltage which is substantially immune to variations in ambient temperature as well as loading, input supply, and time. While many ADCs and DACs incorporate an internal reference, beyond 8 to10 bits it is rare to find one with sufficient precision as high-density CMOS technologies commonly used for data converters typically produce low-quality references. In most cases, the internal reference can be overdriven by an external one to improve performance. Terms such as "high precision" and "ultra-high precision" are common in reference datasheets but do little to help designers in their selection. This article seeks to provide an explanation of common reference specifications, rank their relative importance and show how a designer can use them in some simple calculations to narrow his or her search.

Figure 1. Simplified ADC/DAC Diagrams

## The Best Voltage Reference for Your Application

national.com/power

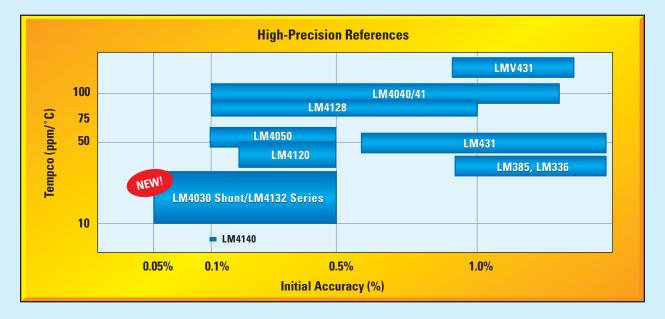

## High-Precision LM4030 Shunt Reference Features 0.05% Initial Accuracy and Low 10 ppm Tempco Over Temperature

|     | Product ID | Туре         | V <sub>OUT</sub> Options (V)          | Initial Accuracy (%)     | Tempco<br>(ppm/°C) | Quiescent<br>Current (µA) | Noise<br>(µVpp) | Package |

|-----|------------|--------------|---------------------------------------|--------------------------|--------------------|---------------------------|-----------------|---------|

| NEW | LM4140     | Series (LDO) | 1.024, 1.25, 2.048, 2.5,<br>4.096     | 0.1                      | 3, 6, 10           | 230                       | 2.2             | SO-8    |

|     | LM4132     | Series (LDO) | 1.8, 2.0, 2.5, 3.0, 3.3,<br>4.096     | 0.05, 0.1, 0.2, 0.4, 0.5 | 10, 20, 30         | 60                        | 170             | SOT23-5 |

| NEW | LM4030     | Shunt        | 2.5, 4.096                            | 0.05, 0.1, 0.15          | 10, 20, 30         | 120                       | 100             | SOT23-5 |

|     | LM4120     | Series (LDO) | 1.8, 2.048, 2.5, 3.0, 3.3,<br>4.09, 5 | 0.2, 0.5                 | 50                 | 160                       | 20              | SOT23-5 |

|     | LM4050     | Shunt        | 2.0, 2.5, 4.096, 5.0,<br>8.2, 10      | 0.1, 0.2, 0.5            | 50                 | 39                        | 48              | SOT23-3 |

| NEW | LM4128     | Series (LDO) | 1.8, 2.0, 2.5, 3.0, 3.3,<br>4.096     | 0.1, 0.2, 0.5, 1         | 75, 100            | 60                        | 170             | SOT23-5 |

For FREE samples, datasheets, and more, visit:

national.com/power Or call: 1-800-272-9959

### **Voltage Reference Selection Basics**

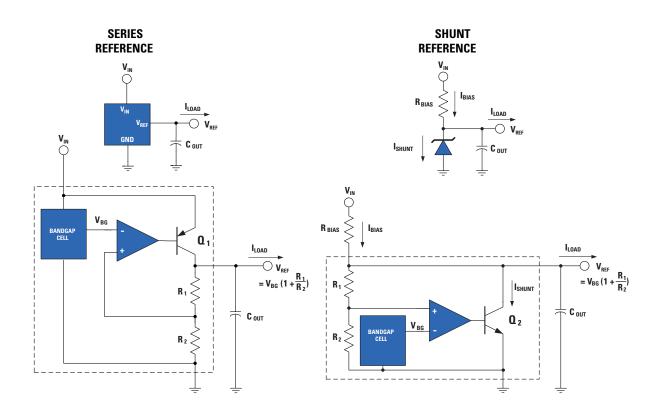

*Figure 2* shows the two available voltage references topologies: series and shunt. A series reference provides load current through a series transistor located between  $V_{IN}$  and  $V_{REF}$  (Q<sub>1</sub>), and is basically a high-precision, low-current linear regulator. A shunt reference regulates  $V_{REF}$  by shunting excess current to ground via a parallel transistor (Q<sub>2</sub>). In general, series references require less power than shunt references because load current is provided as it is needed. The bias current of a shunt reference (I<sub>BIAS</sub>) is set by the value of R<sub>BIAS</sub> and must be greater than or equal to the maximum load current plus the reference's minimum operating current (the minimum bias current required for regulation). In applications where the maximum load current is low (e.g. below

100  $\mu$ A to 200  $\mu$ A), the disparity in power consumption between series and shunt references shrinks. There is no inherent difference in accuracy between the two topologies and high- and low-precision examples are available in both varieties. The advantages and disadvantages of the two architectures are summarized in *Table 1*. Overall, shunt references offer more flexibility (V<sub>IN</sub> range, creation of negative or floating references) and better power supply rejection at the expense of higher power consumption. The typical application diagram of data converters will often show a zener diode symbol representing the reference, indicating the use of a shunt reference. This is merely a convention, and in nearly all cases a series reference could be used as well.

Figure 2. Circuit Symbols and Simplified Schematics of Series and Shunt Architectures

national.com/power

## **Voltage Reference Selection Basics**

#### **Table 1. Series vs Shunt Architectures**

|                      | Series                                          | Shunt                                                                           |

|----------------------|-------------------------------------------------|---------------------------------------------------------------------------------|

| Number of Terminals  | 3 (V <sub>IN</sub> , V <sub>REF</sub> , GND)    | 2 (V <sub>REF</sub> , GND)                                                      |

| Current Requirements | $I_{Q} + I_{LOAD}$ (as needed)                  | Min. operating current + I <sub>LOAD_MAX</sub> (continuous)                     |

| Advantages           | Low power dissipation                           | No limit on maximum V <sub>IN</sub>                                             |

|                      | Shutdown/power-saving mode possible             | Excellent power supply rejection                                                |

|                      |                                                 | Can be used to create negative reference voltages                               |

|                      |                                                 | Can be used to create floating references (cathode to a voltage other than GND) |

|                      |                                                 | Inherent current sourcing and sinking                                           |

| Disadvantages        | Limited maximum V <sub>IN</sub>                 | Must idle at maximum load current                                               |

|                      | More sensitive to V <sub>IN</sub> supply (PSRR) | Shutdown/power-saving mode not possible                                         |

|                      | May only be capable of sourcing current         |                                                                                 |

### Voltage Reference Specifications In Order of Importance

#### 1.) Temperature Coefficient

The variation in  $V_{REF}$  over temperature is defined by its temperature coefficient (TC, also referred to as "drift") which has units of parts-per-million per degree Celsius (ppm/°C). It is convenient to represent the reference voltage temperature dependence as a polynomial for the sake of discussion:

$$V_{\text{REF}}(T) = V_{\text{REF}} \left|_{25^{\circ}\text{C}} \left(1 + TC_{1} \left(\frac{T}{25^{\circ}\text{C}}\right) + TC_{2} \left(\frac{T}{25^{\circ}\text{C}}\right)^{2} + TC_{3} \left(\frac{T}{25^{\circ}\text{C}}\right)^{3} + ...\right)$$

$TC_1$  represents the first-order (linear) temperature dependence,  $TC_2$  the second-order, and so on. Higher than first-order terms are usually lumped together and described as the "curvature" of the drift. The majority of monolithic references are based on a bandgap reference. A bandgap reference is created when a specific Proportional To Absolute Temperature (PTAT) voltage is added to the Complementary To Absolute Temperature (CTAT) baseto-emitter voltage of a bipolar transistor yielding a voltage at roughly the bandgap energy of silicon (~1.2V) where  $TC_1$  is nearly zero. Neither the PTAT nor CTAT voltage is perfectly linear leading to non-zero higher-order TC coefficients, with  $TC_2$  usually being dominant. References designed for drifts less than 20 ppm/°C generally require special circuitry to reduce TC<sub>2</sub> (and possibly higher-order terms), and their datasheets will often mention some form of "curvature correction." Another common type of reference is based on a buried-zener diode voltage plus a bipolar base-to-emitter voltage to produce a stable reference voltage on the order of 7V. The drift performance of buried-zener references is on par with that of bandgap references, although

$\left(\frac{1}{C}\right)^3 + \dots$  their noise performance is superior. Buried-zener references usually require large quiescent currents and must have an input supply greater than 7.2V, so they cannot be used in low-voltage applications (V<sub>IN</sub> = 3.3V, 5V, etc.).

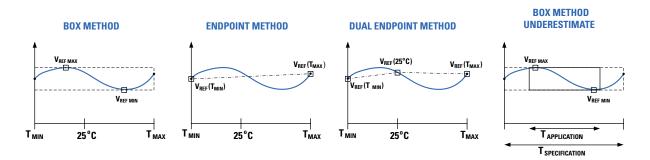

The temperature coefficient can be specified over several different temperature ranges, including the commercial temperature range (0 to 70°C), the industrial temperature range (-40 to 85°C), and the extended temperature range (-40 to 125°C). There are several methods of defining TC, with the "box" method being used most often. The box method calculates TC using the difference in the maximum and minimum V<sub>REF</sub> measurements over the entire temperature range. Whereas other methods use the values of V<sub>REF</sub> at the endpoints of the temperature range (T<sub>MIN</sub>, T<sub>MAX</sub>).

## **Voltage Reference Selection Basics**

$$TC_{BOX} = 10^{6} \cdot \left(\frac{V_{REF\_MAX} |_{T} - V_{REF\_MIN} |_{T}}{V_{REF} |_{25'C}}\right) \cdot \left(\frac{1}{T_{MAX} - T_{MIN}}\right)$$

$$TC_{ENDPOINTS} = 10^{6} \cdot \left(\frac{V_{REF} |_{TMAX} - V_{REF} |_{TMIN}}{V_{REF} |_{25'C}}\right) \cdot \left(\frac{1}{T_{MAX} - T_{MIN}}\right)$$

Neither method is ideal. The weakness of the endpoints method is the failure to account for any curvature in the drift (TC<sub>2</sub>, TC<sub>3</sub>, etc.). Calculating the incremental TC from room temperature to both the minimum and maximum temperatures improves the situation as information on TC<sub>2</sub> can be garnered using three data points rather than two. While the box method is more accurate than using endpoints, it may underestimate TC if the temperature range of the application is smaller than the range over which the TC is specified.

#### 2.) Initial Accuracy

The initial accuracy of  $V_{REF}$  indicates how close to the stated nominal voltage the reference voltage is guaranteed to be at room temperature under stated bias conditions. It is typically specified as a percentage and ranges from 0.01% to 1% (100-10,000 ppm). For example, a 2.5V reference with 0.1% initial accuracy should be between 2.4975V and 2.5025V when measured at room temperature. The importance of initial accuracy depends mainly on whether the data conversion system is calibrated. Buried-zener references have very loose initial accuracy (5-10%) and will require some form of calibration.

#### 3.) 0.1-10 Hz Peak-to-Peak Noise

The internally-generated noise of a voltage reference causes a dynamic error that degrades the signal-tonoise ratio (SNR) of a data converter, reducing the estimated number of bits of resolution (ENOB). Datasheets provide separate specifications for lowand high-frequency noise. Broadband noise is typically specified as an rms value in microvolts over the 10 Hz to 10 kHz bandwidth. Broadband noise is the less troublesome of the two as it can be reduced to some degree with a large  $V_{REF}$  bypass capacitor. Broadband noise may or may not be important in a given application depending on the bandwidth of the signal the designer in interested in. Lowfrequency V<sub>REF</sub> noise is specified over the 0.1 Hz to 10 Hz bandwidth as a peak-to-peak value (in  $\mu$ V or ppm). Filtering below 10 Hz is impractical, so the low-frequency noise contributes directly to the total reference error. Low-frequency noise is characterized using an active bandpass filter composed of a 1<sup>st</sup>-order high-pass filter at 0.1 Hz followed by an n<sup>th</sup>-order low-pass filter at 10 Hz. The order of the low-pass filter has a significant effect on measured peak-to-peak value. Using a 2<sup>nd</sup>-order low pass at

Figure 3. Different Methods for TC Calculation

### **Voltage Reference Selection Basics**

10 Hz will reduce the peak-to-peak value by 50 to 60% compared to a 1st-order filter. Some manufacturers use up to 8<sup>th</sup>-order filters, so a designer should read the datasheet notes carefully when comparing references. From a design perspective, the 0.1 Hz to 10 Hz noise is mainly due to the flicker (1/f) noise of the devices and resistors in the bandgap cell, and therefore scales linearly with V<sub>REF</sub>. For example, a 5V reference will have twice the peak-to-peak noise voltage as the 2.5V option of the same part. Reducing the noise requires considerably higher current and larger devices in the bandgap cell, so very low noise references (<5 µVp-p) often have large quiescent currents (hundreds of microamps to milliamps) and tend to be in larger packages. Buriedzener references have the best noise performance available because no gain is required to generate the output voltage. Bandgap cells typically have a closedloop gain of 15 V/V to 20 V/V, causing device and resistor noise to be amplified.

#### 4.) Thermal Hysteresis

Thermal hysteresis is the shift in  $V_{REF}$  due to one or more thermal cycles and is specified in parts-permillion. A thermal cycle is defined as an excursion from room temperature to a minimum and a maximum temperature and finally back to room temperature (for example, 25°C to -40°C to 125°C to 25°C). The temperature range (commercial, industrial, extended) and number of thermal cycles vary by manufacturer, making direct comparison difficult. More thermal cycles over a wider temperature range leads to a larger shift in V<sub>REF</sub>. Even if the temperature range of the application is narrow, the heating of the part when soldering it to the PCB and any subsequent solder reflows will induce shifts

in  $V_{REF}$ . The main cause of thermal hysteresis is a change in die stress and therefore is a function of the package, die-attach material and L molding compound, as well as the layout of the IC itself. As a rule of thumb, references in larger

packages tend to have lower hysteresis. Thermal hysteresis is not tested in production and datasheets only provide a typical shift.

#### 5.) Long-Term Stability

Long-term stability describes the typical shift in  $V_{REF}$  after 1000 hours (6 weeks) of continuous operation under nominal conditions. It is meant to give the designer a rough idea of the stability of the reference voltage over the life of the application. The prevailing wisdom is that the majority of the shift in  $V_{REF}$  occurs in the first 1000 hours as long-term stability is related logarithmically with time. A six-week test time is not feasible in production, so long-term stability is characterized on a small sample of parts (15 to 30 units) at room temperature and the typical shift is specified.

Once a reference is soldered down on a PCB, changes in the board stress can also cause permanent shifts in  $V_{REF}$ . Board stress dependence is not currently captured in datasheets, so the designer should locate the reference on a portion of the PCB least prone to flexing. Different packages will have different sensitivity to stress; metal cans are largely immune, and surface-mount plastic packages become progressively more sensitive the smaller the package (for example, the same die will perform better in an SO-8 than a SC70 package).

#### 6.) Load Regulation

Load regulation is the measure of the variation in  $V_{REF}$  as a function of load current and is specified either as a percentage or in parts-per-million per milliamp (ppm/mA). It is calculated by dividing the relative change in  $V_{REF}$  at minimum and maximum load currents by the range of the load current.

$$DAD_REG(ppm/mA) = 10^{6} \cdot \left( \frac{V_{REF}|_{ILOAD_MAX} - V_{REF}|_{ILOAD_MIN}}{V_{REF}|_{ILOAD_MIN}} \right) \left( \frac{1}{I_{LOAD_MAX} - I_{LOAD_MIN}} \right)$$

## **Voltage Reference Selection Basics**

Load regulation depends on both the design of the reference and the parasitic resistance separating it from the load, so the reference should be placed as close to the load as the PCB layout will allow. References with pins for both forcing and sensing V<sub>REF</sub> provide some immunity to this problem. The impedance of the reference input is large enough  $(>10 \text{ k}\Omega)$  on many data converters that load regulation error may not be significant. Maximum load current information can be found in ADC/DAC datasheets specified as either a minimum reference pin resistance (R<sub>REF</sub>) or a maximum reference current (I<sub>REF</sub>). In situations where the reference is buffered with a high-speed op amp, load regulation error can usually be ignored. The dual of load regulation for shunt references is the 'change in reverse breakdown voltage with current' that specifies the change in V<sub>REF</sub> as a function of the current shunted away from the load. It is calculated with the same equation as load regulation where load current is replaced with shunted current (I<sub>SHUNT</sub>). The amount of shunted current depends on both the load current and the input voltage so the 'change in reverse voltage with current' specification also indicates line sensitivity.

#### 7.) Line Regulation

Line regulation applies only to series voltage references and is the measure of the change in the reference voltage as a function of the input voltage.

$$LINE\_REG = 10^{6} \cdot \left(\frac{V_{REF}|_{VIN\_MAX} - V_{REF}|_{VIN\_MIN}}{V_{REF}|_{VIN\_MIN}}\right) \cdot \left(\frac{1}{V_{IN\_MAX} - V_{IN\_MIN}}\right)$$

The importance of line regulation depends on the tolerance of the input supply. In situations where the input voltage tolerance is within 10% or less, it may not contribute significantly to the total error. The extension of line regulation over frequency is the Power Supply Rejection Ratio (PSRR). PSRR is

rarely specified but typical curves are usually provided in the datasheet. As with line regulation, the importance of PSRR depends on specifics of the input supply. If  $V_{IN}$  is noisy (generated with a switching regulator, sensitive to EMI, subject to large load transients), PSRR may be critical. The analogous specification for shunt references is the reverse dynamic impedance, which indicates the sensitivity of  $V_{REF}$  to an AC current. Noise on the supply powering a shunt reference is converted to a noise current through  $R_{BIAS}$ . Some shunt reference datasheets will specify the reverse dynamic impedance at 60 Hz and 120 Hz, and nearly all will provide a plot of reverse dynamic impedance versus frequency.

#### 8.) Other Considerations

In applications where power consumption is crucial, a series reference is usually the right choice. The quiescent current of most series references ranges from 25  $\mu$ A to 200  $\mu$ A, although several are available with I<sub>Q</sub><1  $\mu$ A. Low quiescent current generally comes at the expense of precision (TC and initial accuracy) and higher noise. Some series references can also be disabled via an external ENABLE/ SHUTDOWN pin causing the quiescent current to drop to a few microamps or less when V<sub>REF</sub> is not needed. A power-saving mode is not possible in shunt references. Additionally, series references can have dropout voltages less than 200 mV, allowing

them to be used at lower input voltages. Shunt references can also be used at low voltages, but the bias current may vary widely with changes in  $V_{\rm IN}$  due to the small  $R_{\rm BIAS}$  resistor required.

References do not require many external passive components but proper selection can improve performance. A bypass capacitor on  $V_{REF}$  substantially improves PSRR (or reverse dynamic impedance in the case of a shunt reference) at higher frequencies. It will also improve the load transient response, and

### **Voltage Reference Selection Basics**

reduce high-frequency noise. Generally speaking, the best performance is achieved with the largest bypass capacitor allowed. The range of allowable bypass capacitors depends on the stability of the reference, which should be detailed along with ESR restrictions in the component selection section of the datasheet. When using a large bypass capacitor (>1  $\mu$ F) it may be advantageous to bypass it with a smaller value, lower-ESR capacitor to reduce the effects of the ESR and ESL. The reverse dynamic impedance of a shunt reference varies inversely with the amount of current shunted. If noise immunity is more important than power consumption in a given application, a smaller R<sub>BIAS</sub> may be used to increase I<sub>SHUNT</sub>.

#### **Selecting a Voltage Reference**

Voltage reference selection begins with satisfying the application operating conditions, specifically: nominal  $V_{REF}$ ,  $V_{IN}$  range, current drive, power consumption, and package size. Beyond that, a reference is chosen based on the accuracy requirements of a given data converter application. The most convenient unit for understanding how the reference error affects accuracy is in terms of the least significant bit (LSB) of the data converter. The LSB in units of parts-per-million is simply one million divided by two raised to the number of bits power. *Table 2* provides the LSB values for common resolutions.

$LSB(ppm) = 10^{6} \cdot \left(\frac{1}{2}\right)^{NOB}$

NOB: Number of Bits

Table 2. LSB Values in PPM for Common Data Converter Resolutions

| BITS | LSB (ppm) |

|------|-----------|

| 8    | 3906      |

| 10   | 977       |

| 12   | 244       |

| 14   | 61        |

| 16   | 15        |

ADCs/DACs have their own sources of error including integral nonlinearity (INL), differential nonlinearity (DNL), and gain and offset error. If we consider the case of the more common unipolar data converter, voltage reference error is functionally equivalent to a gain error. INL and DNL gauge the nonlinearity of a data converter, on which the reference voltage has no effect. The gain and offset errors can be understood conceptually by recognizing that ADCs/DACs have two reference voltages: V<sub>REF</sub> and GND in the case of a unipolar data converter, and  $V_{REF}$  and  $-V_{REF}$  for bipolar data converters. The offset error is the deviation in the output (in bits for an ADC and voltage for a DAC) from the ideal minus full-scale (MFS) value when a MFS input is applied. The MFS reference voltage is GND so V<sub>REF</sub> error has no effect. The gain error is the deviation from the ideal positive full-scale (PFS) output for a PFS input, minus the offset error. The PFS reference voltage is V<sub>REF</sub>, so any shift in the reference voltage equates to a gain error. As such, the reference error can cause loss of dynamic range for input signals near PFS, which is also where it has the most pronounced effect on accuracy. The effect of reference error on a mid-scale (MS) input signal is half that for a PFS input, and is negligible for inputs near MFS. For example, a worst-case reference error of 8 LSB would result in a loss of 3 bits of accuracy for a PFS input, 2 bits of lost accuracy at mid-scale, and no loss of accuracy at MFS. If the designer has no idea what kind of reference error they can live with, matching the worst-case reference error to the maximum gain error is a reasonable starting point. In systems where error contributors are statistically independent, and consequently add together as a root mean squared sum, balancing the error contributions represents the optimal case. Otherwise, the error will tend to be dominated by one variable and the accuracy of the other variable(s) is essentially wasted.

### **Voltage Reference Selection Basics**

In calculating the total error in  $V_{REF}$  it is helpful to separate the specifications where a maximum value is guaranteed (TC, initial accuracy, load regulation, line regulation) and those where only a typical value is provided (0.1 Hz to10 Hz noise, thermal hysteresis, and long-term stability). Other than initial accuracy, the guaranteed specifications are all linear coefficients and their contribution to the total error can be calculated based on the operating ranges of the reference (temperature range, load current, and input voltage). In calibrated systems, initial accuracy can be dropped from the equation.

$$\begin{split} & \mathsf{ERROR}\mid_{\mathsf{TEMP}} = \mathsf{TC} \cdot (\mathsf{T}_{\mathsf{MAX}} - \mathsf{T}_{\mathsf{MIN}}) \\ & \mathsf{ERROR}\mid_{\mathsf{LOAD}} = \mathsf{LOAD\_REG} \cdot (\mathsf{I}_{\mathsf{LOAD\_MAX}} - \mathsf{I}_{\mathsf{LOAD\_MIN}}) \\ & \mathsf{ERROR}\mid_{\mathsf{LINE}} = \mathsf{LINE\_REG} \cdot (\mathsf{V}_{\mathsf{IN\_MAX}} - \mathsf{V}_{\mathsf{IN\_MIN}}) \\ & \mathsf{ERROR}\mid_{\mathsf{GUARANTEED}} = \mathsf{ERROR}\mid_{\mathsf{INITIAL\_ACCURACY}} + \mathsf{ERROR}\mid_{\mathsf{TEMP}} + \mathsf{ERROR}\mid_{\mathsf{LOAD}} + \mathsf{ERROR}\mid_{\mathsf{LINE}} \end{split}$$

#### Example (LM4132A\_2.5V):

$$\begin{split} & \mathsf{ERROR}\mid_{\mathsf{TEMP}} = (10 \; \mathsf{ppm/^{\circ}C}) \cdot (55 \;^\circ \mathrm{C} - 0 \;^\circ \mathrm{C}) = 550 \; \mathsf{ppm} \\ & \mathsf{ERROR}\mid_{\mathsf{LOAD}} = (120 \; \mathsf{ppm/mA}) \cdot (0.5 \; \mathsf{mA} - 0 \; \mathsf{mA}) = 60 \; \mathsf{ppm} \\ & \mathsf{ERROR}\mid_{\mathsf{LINE}} = (50 \; \mathsf{ppm/V}) \cdot (5.5 \mathrm{V} - 4.5 \mathrm{V}) = 50 \; \mathsf{ppm} \\ & \mathsf{ERROR}\mid_{\mathsf{GUARANTEED}} = (0.05\% \; = 500 \; \mathsf{ppm}) + 550 \; \mathsf{ppm} + 60 \; \mathsf{ppm} + 50 \; \mathsf{ppm} = 1160 \; \mathsf{ppm} \end{split}$$

The above calculation represents the worst case, and most of the time a reference will perform better than the guaranteed maximums (especially when it comes to line and load regulation where the maximum may be more a function of the testing system due to the very low signal-to-noise ratio of the measurement). It is worth noting that the statistical

methods through which the guaranteed maximum specifications are calculated vary by manufacturer, so comparing datasheets may not tell the full story. If the designer wants to estimate the average reference error, they can take the rms sum of the individual error sources rather than just adding them up. In most cases, the TC error will be dominant, so TC error by itself gives a good indication of average reference performance.

Datasheets only provide typical values for thermal hysteresis and long-term stability, but both are likely to vary a great deal unit to unit. The typical specification is not very helpful in estimating worst-case error without knowing the standard deviation of the distribution. Many times this information can be obtained by calling the manufacturer. Otherwise,

a conservative, albeit crude, approach would be to multiply the typical specification by three or four to get a ballpark estimate of the worst-case shift. This is assuming that the standard deviation of the distribution is on the order of the mean value and designing for a two or three standard deviation worst case.

The loss of resolution due to noise is harder to predict and can only really

be known by testing a reference in the application. Low-frequency noise should be very consistent on a unit-to-unit basis and no 'sand-bagging' of the typical value is required. Over a 10-second window, one can expect the  $V_{REF}$  to shift by an amount equal to the 0.1 Hz to 10 Hz peak-to-peak specification.

$\begin{array}{ll} & \mbox{ERROR} \mid_{\mbox{THERMAL}_{\mbox{HYSTERESIS}} \approx 3 \times (\mbox{Typ. Thermal Hysteresis}) \\ & \mbox{ERROR} \mid_{\mbox{LONG}_{\mbox{TERM}_{\mbox{STABILITY}}} \approx 3 \times (\mbox{Typ. Long}_{\mbox{Term Stability}}) \\ & \mbox{ERROR} \mid_{\mbox{LF}_{\mbox{NOISE}}} = 10^6 \cdot \left( \frac{0.1 - 10 \mbox{Hz Peak} - to - \mbox{Peak}}{V_{\mbox{ReF}}} \right) \\ & \mbox{ERROR} \mid_{\mbox{LF}_{\mbox{NOISE}}} = 10^6 \cdot \left( \frac{0.1 - 10 \mbox{Hz Peak} - to - \mbox{Peak}}{V_{\mbox{ReF}}} \right) \\ & \mbox{ERROR} \mid_{\mbox{LF}_{\mbox{NOISE}}} = \mbox{ERROR} \mid_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{Term Stability}}}} + \mbox{ERROR} \mid_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mbox{LGM}_{\mb$

#### Example (LM4132A\_2.5V):

$$\begin{split} & \mathsf{ERROR} \mid_{\mathsf{THERMAL}_{\mathsf{HYSTERESIS}} \approx 3 \times (75 \text{ ppm}) = 225 \text{ ppm} \\ & \mathsf{ERROR} \mid_{\mathsf{LONG}_{\mathsf{-TERM}_{\mathsf{STABILITY}}} \approx 3 \times (50 \text{ ppm}) = 150 \text{ ppm} \\ & \mathsf{ERROR} \mid_{\mathsf{LF}_{\mathsf{NOISE}}} = 10^6 \cdot \left(\frac{240 \, \mu \, \mathsf{V}_{\mathsf{P}_{\mathsf{P}}}}{2.5 \mathsf{V}}\right) = 96 \text{ ppm} \\ & \mathsf{ERROR} \mid_{\mathsf{TOT}} = 1160 \text{ ppm} + 225 \text{ ppm} + 150 \text{ ppm} + 96 \text{ ppm} = 1631 \text{ ppm} \end{split}$$

### **Voltage Reference Selection Basics**

Once the worst-case reference error in parts-permillion is estimated, it can be converted into LSB for different data converter resolutions using the values in *Table 2*. The worst-case accuracy loss at positive full-scale and mid-scale can then be calculated taking the log base-2 of the number of LSB of error.

$\begin{aligned} & \mathsf{ERROR} \mid_{\mathsf{TOTAL}} (\mathsf{LSB}) = \frac{1631\,\mathsf{ppm}}{\left(\begin{array}{c}\mathsf{ppm}/\mathsf{LSB}\end{array}\right)} = 1.7\,\mathsf{LSB}\,(10\,\mathsf{bit}) = 6.7\,\mathsf{LSB}\,(12\,\mathsf{bit}) = 26.7\,\mathsf{LSB}\,(14\,\mathsf{bit}) \end{aligned} \\ & \mathsf{Worst}\,\mathsf{Case}\,\mathsf{Lost}\,\mathsf{Accuracy} = \log_2\left(\mathsf{ERROR}\right|_{\mathsf{TOTAL}}(\mathsf{LSB})\right) \end{aligned} \\ & \mathsf{Worst}\,\mathsf{Case}\,\mathsf{Lost}\,\mathsf{Accuracy}\,(\mathsf{PFS}) = 0.8\,\mathsf{bit}\,(10\,\mathsf{bit}) = 2.7\,\mathsf{bits}\,(12\,\mathsf{bit}) = 4.7\,\mathsf{bits}\,(14\,\mathsf{bit}) \end{aligned}$

If the average rather than the worst case is considered, the rms sum of reference error contributors can be taken (replacing the maximums for the typicals).

#### Example (**LM4132A\_2.5V**):

$\begin{aligned} & \mathsf{ERROR} \mid_{\mathsf{RMS}} = \sqrt{(550)^2 + (500)^2 + (50)^2 + (60)^2 + (75)^2 + (50)^2 + (96)^2 = 760 \text{ ppm}} \\ & \mathsf{ERROR} \mid_{\mathsf{RMS}} (\mathsf{LSB}) = \frac{760 \text{ ppm}}{\left( \begin{array}{c} \mathsf{ppm} \\ \mathsf{LSB} \end{array} \right)} = 0.8 \text{ LSB (10 bit)} = 3.1 \text{ LSB (12 bit)} = 12.5 \text{ LSB (14 bit)} \\ & \mathsf{Typical Lost Accuracy} = \log_2 \left( \mathsf{ERROR} \mid_{\mathsf{TOTAL}} (\mathsf{LSB}) \right) \\ & \mathsf{Typical Lost Accuracy (PFS)} = 0 \text{ bit (10 bit)} = 1.6 \text{ bits (12 bit)} = 3.6 \text{ bits (14 bit)} \\ & \mathsf{Typical Lost Accuracy (MS)} = 0 \text{ bit (10 bit)} = 0.6 \text{ bits (12 bit)} = 2.6 \text{ bits (14 bit)} \end{aligned}$

Using the above analysis, a designer should be able to predict the typical and worst-case accuracy loss due to reference error in their data conversion system. Repeating this exercise for several different references should provide the designer with more insight into what reference specifications are most critical in their application, allowing them to make a more informed selection.

## **Power Design Tools**

### **Tools for Energy-Efficient Designs**

Access white papers, reference designs, and application notes on PowerWise<sup>®</sup> products and systems. www.national.com/powerwise

### Analog Edge<sup>™</sup> App Notes

National's monthly analog design technical journal. www.national.com/analogedge

### **Online Seminars**

Free online seminars by industry experts. Log onto National's analog online seminars today. www.national.com/onlineseminars

#### National Semiconductor

2900 Semiconductor Drive Santa Clara, CA 95051 1 800 272 9959

Mailing address: PO Box 58090 Santa Clara, CA 95052

Visit our website at: www.national.com

For more information, send email to: new.feedback@nsc.com

## Don't miss a single issue!

Subscribe now to receive email alerts when new issues of Power Designer are available:

www.national.com/powerdesigner

Read our Signal Path Designer<sup>®</sup> online today at:

www.national.com/spdesigner

©2008, National Semiconductor Corporation. National Semiconductor, 🔗 PowerWise, and Signal Path Designer are registered trademarks and Analog Edge is a service mark of National Semiconductor. All other brand or product names are trademarks or registered trademarks of their respective holders. All rights reserved.

#### 重要声明

德州仪器(TI)及其下属子公司有权在不事先通知的情况下,随时对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权随时中止提供任何产品和服务。客户在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。所有产品的 销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI保证其所销售的硬件产品的性能符合TI标准保修的适用规范。仅在TI保证的范围内,且TI认为有必要时才会使用测试或其它质量控制技术。除非政府做出了硬性规定,否则没有必要对每种产品的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用TI 组件的产品和应用自行负责。为尽量减小与客户产品和应用相关的风险,客户应提供充分的设计与操作安全措施。

TI不对任何TI专利权、版权、屏蔽作品权或其它与使用了TI产品或服务的组合设备、机器、流程相关的TI知识产权中授予的直接 或隐含权限作出任何保证或解释。TI所发布的与第三方产品或服务有关的信息,不能构成从TI获得使用这些产品或服务的许可、授 权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是TI的专利权或其它知识产权方面的许可。

对于TI的产品手册或数据表,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许进行复制。在复制信息的过程中对内容的篡改属于非法的、欺诈性商业行为。TI对此类篡改过的文件不承担任何责任。

在转售TI产品或服务时,如果存在对产品或服务参数的虚假陈述,则会失去相关TI产品或服务的明示或暗示授权,且这是非法的、 欺诈性商业行为。TI对此类虚假陈述不承担任何责任。

TI 产品未获得用于关键的安全应用中的授权,例如生命支持应用(在该类应用中一旦TI产品故障将预计造成重大的人员伤亡),除 非各方官员已经达成了专门管控此类使用的协议。购买者的购买行为即表示,他们具备有关其应用安全以及规章衍生所需的所有专业 技术和知识,并且认可和同意,尽管任何应用相关信息或支持仍可能由TI 提供,但他们将独力负责满足在关键安全应用中使用其产品及TI 产品所需的所有法律、法规和安全相关要求。此外,购买者必须全额赔偿因在此类关键安全应用中使用TI产品而对TI 及其代表造成的损失。

TI 产品并非设计或专门用于军事/航空应用,以及环境方面的产品,除非TI 特别注明该产品属于"军用"或"增强型塑料"产品。只有TI 指定的军用产品才满足军用规格。购买者认可并同意,对TI 未指定军用的产品进行军事方面的应用,风险由购买者单独承担, 并且独力负责在此类相关使用中满足所有法律和法规要求。

TI 产品并非设计或专门用于汽车应用以及环境方面的产品,除非TI 特别注明该产品符合ISO/TS 16949 要求。购买者认可并同意,如果他们在汽车应用中使用任何未被指定的产品,TI 对未能满足应用所需要求不承担任何责任。

可访问以下URL 地址以获取有关其它TI 产品和应用解决方案的信息:

|               | 产品                                 |                     | 应用                       |

|---------------|------------------------------------|---------------------|--------------------------|

| 数字音频          | www.ti.com.cn/audio                | 通信与电信               | www.ti.com.cn/telecom    |

| 放大器和线性器件      | www.ti.com.cn/amplifiers           | 计算机及周边              | www.ti.com.cn/computer   |

| 数据转换器         | www.ti.com.cn/dataconverters       | 消费电子                | www.ti.com/consumer-apps |

| DLP® 产品       | www.dlp.com                        | 能源                  | www.ti.com/energy        |

| DSP - 数字信号处理器 | www.ti.com.cn/dsp                  | 工业应用                | www.ti.com.cn/industrial |

| 时钟和计时器        | www.ti.com.cn/clockandtimers       | 医疗电子                | www.ti.com.cn/medical    |

| 接口            | www.ti.com.cn/interface            | 安防应用                | www.ti.com.cn/security   |

| 逻辑            | www.ti.com.cn/logic                | 汽车电子                | www.ti.com.cn/automotive |

| 电源管理          | www.ti.com.cn/power                | 视频和影像               | www.ti.com.cn/video      |

| 微控制器 (MCU)    | www.ti.com.cn/microcontrollers     |                     |                          |

| RFID 系统       | www.ti.com.cn/rfidsys              |                     |                          |

| OMAP 机动性处理器   | www.ti.com/omap                    |                     |                          |

| 无线连通性         | www.ti.com.cn/wirelessconnectivity |                     |                          |

|               | 德州仪器在线技术支持社区                       | www.deyisupport.com |                          |

邮寄地址: 上海市浦东新区世纪大道 1568 号,中建大厦 32 楼 邮政编码: 200122 Copyright © 2011 德州仪器 半导体技术(上海)有限公司