# AN-1398 Printed Circuit Board Design Techniques for DS40MB200

# ABSTRACT

The high speed, high gain and fast edge rate attributes of any high-speed circuit requires you to use the high-speed printed circuit board (PCB) techniques to achieve good performance. This application report outlines the techniques to achieve this goal.

#### Contents

| 1 | Introduction             | 2 |

|---|--------------------------|---|

| 2 | Differential Pairs       | 2 |

| 3 | Components' Landing Pads | 4 |

| 4 | Power Pins               | 5 |

| 5 | Conclusion               | 6 |

| 6 | Reference                | 6 |

|   |                          |   |

#### List of Figures

| 1 | DS40MB200 Routing Example Using Coupled Microstrips                      | 2 |

|---|--------------------------------------------------------------------------|---|

| 2 | Differential Vias With Oval Anti-Pad                                     | 3 |

| 3 | Bad Example Of Matching Trace Length Of Coupled Board Traces             | 3 |

| 4 | Good Example Of Matching Trace Length Of Coupled Board Traces            | 3 |

| 5 | Fine Board Traces Used With Large Component Landing Pads                 | 4 |

| 6 | Cross-Section Of Board Trace And Component Pad                           | 4 |

| 7 | V <sub>cc</sub> and GND Hook-Up For The DS40MB200                        | 5 |

| 8 | PCB Stack-Up With "Buried" Capacitor And Short V <sub>cc</sub> /GND Vias | 6 |

|   |                                                                          |   |

All trademarks are the property of their respective owners.

1

# 1 Introduction

The DS40MB200 is a high speed 2:1 multiplexer and 1:2 fan-out repeater designed to support redundancy and extend copper backplanes up to 4 Gb/s. The output driver features fast edge rates, typically about 80 ps. Each input stage features fixed equalizer, followed by a high-gain limiting amplifier that re-shapes the output waveforms. The DS40MB200 accepts input signal as low as 100 mV (peak-to-peak).

# 2 Differential Pairs

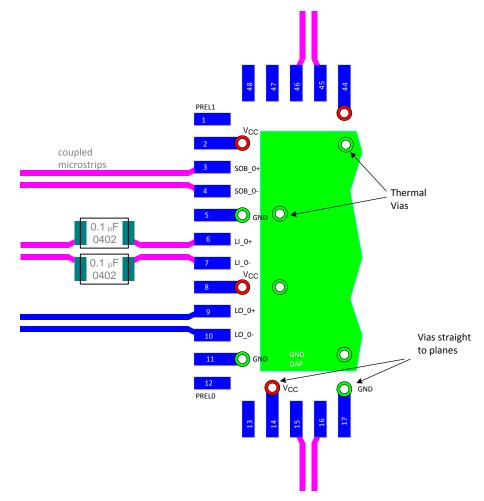

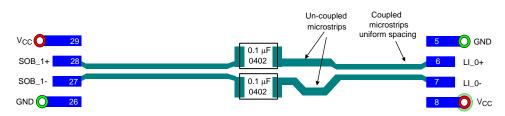

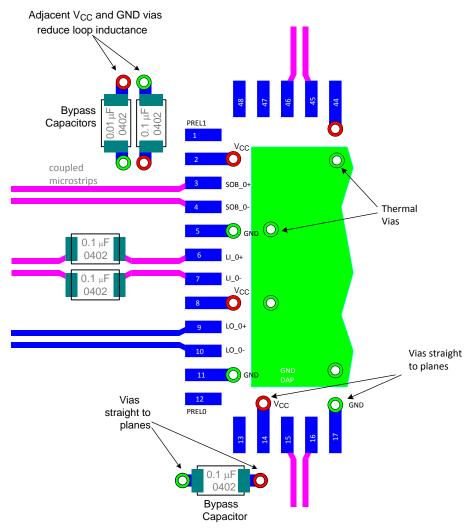

The DS40MB200 uses a 48-lead lead-less LLP package. The LLP offers low package parasitics and is the package of choice for high-speed communication designs. The high speed differential IO's are assigned to the center portion of the package such that each differential pair is sandwiched by a power or ground pin, providing isolation and ground shielding. Coupled microstrip board traces are the preferred transmission line structures for best signal fidelity. The optimum trace width is 10 mils, being equal to the 10-mil landing pad of the LLP-48 package. Finer trace width, such as 5 mils, can also be used with slightly higher impedance mismatch caused by changes in trace width between the traces and the pads. The differential board traces should be routed with constant spacing to ensure impedance uniformity along the length of the traces. Figure 1 shows a partial layout arrangement with 5-mil trace width.

Figure 1. DS40MB200 Routing Example Using Coupled Microstrips

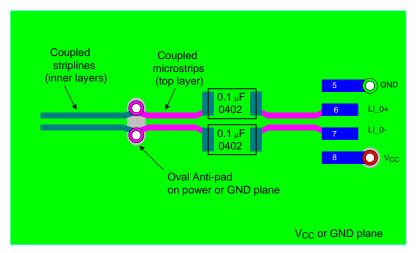

In high routing density boards, coupled striplines are commonly used, but requires the use of plated through holes. These plated through holes introduce parasitic capacitance and may degrade signal fidelity. Small via, with less than 8 mils hole size, should be used to minimize mutual capacitive coupling between the via and nearby ground or power planes. Differential via structure with shared oval-shaped anti-pad can further reduce parasitic capacitance. Figure 2 shows a pair of differential vias with shared oval anti-pad.

www.ti.com

Figure 2. Differential Vias With Oval Anti-Pad

The electrical length of each differential pair should be well matched. As a rule of thumb, the delay skew of the complimentary signals are matched within a small fraction of the signal's edge rate. With an edge rate of about 80 ps, it is acceptable to have a delay skew within 10 ps. For a FR4 board, matching trace lengths within 50 mils achieves less than 10 ps skew between the complimentary signals of the differential pair. Note that it is the matched electrical length instead of matched physical length that matters. Identical geometries should be used for the complimentary signals, and their trace widths in each signal layer should be matched.

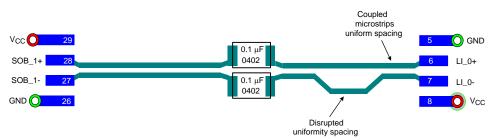

In adjusting the trace lengths of a pair of coupled board traces, never disrupt the uniform spacing of the differential pair. Figure 3 shows a bad example of matching trace lengths. Disrupting the uniform spacing of the coupled differential pair will create impedance discontinuity and impact signal quality. Figure 4 shows a good example of matching trace lengths. In this example, the lengths of the uncoupled segments of the differential pair are adjusted to achieve the desired match lengths. The coupled board traces maintain their uniform spacing, while the trace width of the uncoupled traces are slightly widened to maintain the same characteristic impedance.

Figure 4. Good Example Of Matching Trace Length Of Coupled Board Traces

3

4

### 3 Components' Landing Pads

AC coupling capacitors should be placed on the receive inputs of the DS40MB200. The transition time of the bit stream at the receive side is significantly slowed down by interconnect, making it more tolerant to impedance mismatch caused by the AC coupling capacitors and the parasitic capacitance caused by their landing pads. Small physical size, surface mount capacitors, such as 0402, should be used to reduce impedance mismatch caused by the landing pads of the capacitors.

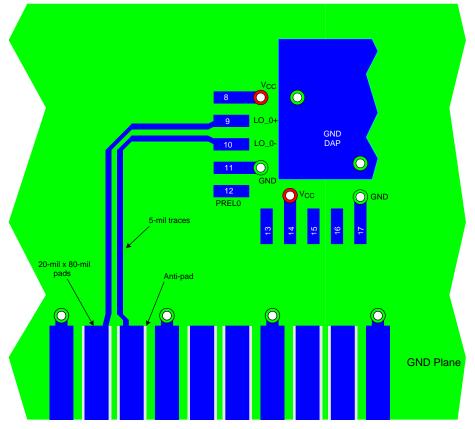

When fine trace width is used with large components, the landing pads of the components are huge relative to the trace width. Figure 5 shows an example of 5-mil traces routing to an edge connector with 20 mil pads.

Figure 5. Fine Board Traces Used With Large Component Landing Pads

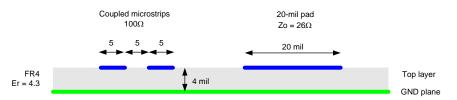

The huge landing pads of the edge connector effectively form a short segment of wide trace, significantly lowering the impedance and introduce relatively large excess capacitance between the pad and the ground plane immediately below it. Figure 6 depicts the cross-sectional view of the board showing the effect of impedance drop from landing pads.

You can use anti-pads on the power and ground planes below the landing pads. This technique is used to reduce the parasitic capacitance formed between the pad and the nearby power or ground plane. Figure 5 illustrates anti-pads used with an edge connector to minimize excess capacitance. A 3-D electromagnetic field solver is usually used to determine the size of the anti-pad to optimize compensation.

www.ti.com

### 4 Power Pins

Each power or ground lead of the DS40MB200 should be connected to the power or ground plane through a low impedance path. For best results, one or more vias should be used to connect a power or ground pin to nearby power or ground plane. Ideally, vias are placed tangent to the IC pads to avoid adding trace inductance. Placing power planes closer to the top of the board reduces the length and inductance of the vias.

Figure 7. V<sub>cc</sub> and GND Hook-Up For The DS40MB200

Bypass capacitors should be placed close to VCC pins. They can be conveniently placed at four corners of the LLP package. Small physical size capacitors, such as 0402, X7R, surface mount capacitors should be used to minimize body inductance of capacitors. Each bypass capacitor is connected to the power and ground plane through vias tangent to the pads of the capacitor. Figure 7 shows  $V_{cc}$  and GND hook-up for the DS40MB200 and placement of bypass capacitors.

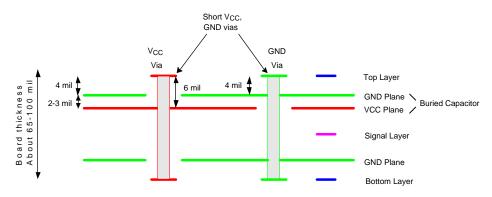

An X7R surface mount capacitor of size 0402 has about 0.5 nH of body inductance. At frequencies above 20–30 MHz, X7R capacitors behave as low impedance inductors. To extend the operating frequency range of these capacitors to a few hundred MHz, an array of different capacitance ranging from 100 pF, 1 nF, 0.01  $\mu$ F, 0.1  $\mu$ F are commonly used in parallel. A more effective bypass capacitor can be built using sandwiched layers of power and ground planes at a separation of 2–3 mils. An ideal high frequency bypass capacitor is formed. With a 2-mil FR4 dielectric, there is about 500 pF capacitance per square inch. Figure 8 depicts a PCB stack-up with V<sub>cc</sub>-GND planes placed on the top side of the board. This stack-up arrangement provides a high frequency "buried" capacitor, and lowers the inductance of power and ground via by reducing the lengths of the vias.

Power Pins

Conclusion

www.ti.com

The center dap of the package should be connected to ground plane through an array of vias. The array of via reduces the effective inductance to ground, and also offer enhanced thermal performance for the package.

#### 5 Conclusion

High speed printed circuit boards require designers to go beyond connectivity. Multi-gigabit boards require attention to board geometry details. These details include dimensions of trace width, component pads, plated-through holes, anti-pads, board thickness and board stack-up. Board material properties such as dielectric constant and loss tangent are important considerations in choosing proper board structures. The techniques described in this application report apply to multi-gigabit board design, with examples illustrated for DS40MB200 mux and buffer. In a multi-gigabit board design, board designers have to find the unwanted L's and C's and devise geometries to overcome their impacts. Very often, a 2-D electromagnetic field solver is used to predict the electrical behavior of board traces, and a 3-D field solver is needed to deal with 3-dimensional geometries such as via and anti-pad. With a little extra time spent on attention to details, the reward is a high performance board running at multi-gigabit and beyond.

#### 6 Reference

6

- Dual 4.0 Gbps 2:1/1:2 CML Mux/Buffer With Transmit Pre-Emphasis and Receive Equalization Data Sheet SNLS144

- AN-1389 Setting Pre-Emphasis Level for DS40MB200 Dual 4Gb/s Mux/Buffer (SNLA073)

- AN-1187 Leadless Leadframe Package (LLP) (SNOA401) •

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated