# Handling System Transients in Hot Swap Applications

Artem Rogachev

#### ABSTRACT

Hot Swap circuits are critical for inrush management and fault protection in high availability systems. To protect the bus and ensure system availability, Hot Swaps are designed to quickly shut off in case of faults with a downstream load. It is also typical for the bus to experience various transients from adjacent card insertion/removal and faults on adjacent cards. These transients can appear as an over-current condition to the Hot Swap circuit and can cause undesired shut downs that are often referred to as a nuisance trips.

This report provides theoretical analysis and experimental results of this phenomenon. In addition, application level solutions are proposed to ensure robust designs.

#### Contents

| 1 | Transients Experienced by Hot Swaps in a Backplane | 2  |

|---|----------------------------------------------------|----|

| 2 | The Response of LM5066 EVM to Transients           | 7  |

| 3 | Mitigating Nuisance Trips in Hot Swap Circuits     | 10 |

#### List of Figures

| 1  | Key System Considerations for Hot Swap Design                                | . 2              |

|----|------------------------------------------------------------------------------|------------------|

| 2  | Experimental Set-up for Understanding Card-to-Card Interactions              | . 3              |

| 3  | Adjacent Card Insertion, I <sub>LOAD,A</sub> = 0 A                           | . 4              |

| 4  | Adjacent Card Insertion, I <sub>LOAD,A</sub> = 7.5 A                         | . 5              |

| 5  | Adjacent Card Removal (I <sub>LOAD,A</sub> = I <sub>LOAD,B</sub> ~8 A)       | . <mark>6</mark> |

| 6  | Adjacent Card Removal (I <sub>LOAD,A</sub> = 8 A, I <sub>LOAD,B</sub> ~12 A) | . 6              |

| 7  | Set up for Electrical Glitching                                              | . 7              |

| 8  | Set up for Mechanical Glitching                                              | . 7              |

| 9  | $V_{IN}$ Transient Generated by $V_{BIAS}$ = 25 V and $C_{GLITCH}$ = 100 nF  | . 8              |

| 10 | Mechanical Glitch With a 1- $\mu$ F C <sub>out</sub>                         | . 9              |

| 11 | Hot Swap Circuit With Key Parasitics                                         | 10               |

#### List of Tables

| 1 | Settings for Exploring Card-to-Card Interactions           | 3  |

|---|------------------------------------------------------------|----|

| 2 | Test Results for Adjacent Card Insertion                   | 5  |

| 3 | Test Results for Adjacent Card Removal                     | 5  |

| 4 | Electrical Glitching Test Results on the EVM               | 8  |

| 5 | Mechanical Glitching Test Results on the EVM               | 9  |

| 6 | Test Results with $C_{out}$ and Differential Filtering     | 11 |

| 7 | Example Test to Ensure Margin with Adjacent Card Insertion | 12 |

| 8 | Example Test to Ensure Margin with Adjacent Card Hot-Short | 12 |

All trademarks are the property of their respective owners.

## 1 Transients Experienced by Hot Swaps in a Backplane

#### 1.1 General System Overview

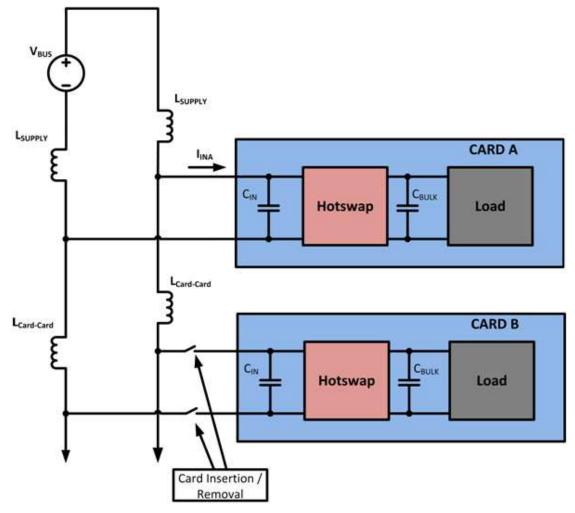

To understand the typical transients experienced by a Hot Swap, the typical backplane should be considered. Figure 1 provides a simplified diagram to demonstrate the key parameters that relate to the Hot Swap. For most systems the following is true:

- C<sub>BULK</sub> is the input to the DC/DC converters and is large. The Hot Swap manages the inrush current to C<sub>BULK</sub> by gradually turning on the Hot Swap FET.

- C<sub>IN</sub> is generally quite small and combines the effect of real and parasitic capacitance that is "hotplugged" into the bus.

- The backplane has little capacitance and the cards are far away from the DC source ( $V_{BUS}$ ), which results in significant inductance from  $V_{BUS}$  to input of the cards ( $L_{SUPPLY}$ ).

- The card to card inductance ( $L_{CARD-CARD}$ ) is small, because the cards are close to each other.

- Since L<sub>CARD-CARD</sub> << L<sub>SUPPLY</sub> the transients caused by insertion/removal/faults on card B translates into a voltage and/or current transient on card A.

Figure 1. Key System Considerations for Hot Swap Design

# 1.2 Experimental Set-up for Exploring Card to Card Interactions

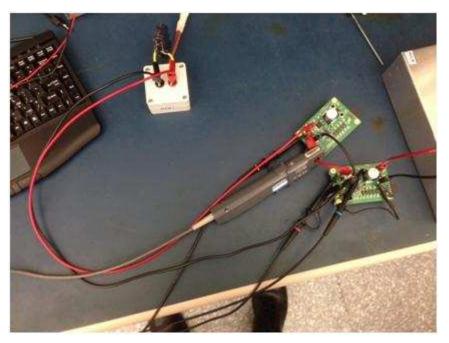

To better understand the nature of the transients present in a typical backplane, lab experiments were performed using two LM5066 EVMs. To best mimic a real system, the shortest available cables were used to connect the two EVMs. Long cables were connected to a low impedance source provided by the bulk cap on the output of the power supply as shown in Figure 2.

Figure 2. Experimental Set-up for Understanding Card-to-Card Interactions

Unless otherwise noted, the experiments were performed with the setting summarized in Table 1.

# Table 1. Settings for Exploring Card-to-Card Interactions

| Category                          | Value   | Comments                       |

|-----------------------------------|---------|--------------------------------|

| R <sub>SNS</sub>                  | 3 mΩ    | EVM setting                    |

| COUT                              | 220 µF  | EVM setting                    |

| CL setting                        | 26 mV   | Current limit of ~8 A          |

| CB setting                        | ~50 mV  | Circuit breaker limit of ~16 A |

| L <sub>SUPPLY</sub>               | >1 µH   |                                |

| L <sub>CARD-CARD</sub>            | ~250 nH | Inferred from test results     |

| C <sub>IN</sub> (with parasitics) | 3 nF    | interted from test results     |

| Filtering?                        | no      |                                |

## 1.3 Adjacent Card Insertion

When a card is inserted, its input capacitor is charged to  $V_{BUS}$ , pulling charge out of the bus and causing an LC ring. This results in transients on adjacent cards, which could cause a nuisance trip. The following occurs when card B is "hot-plugged" and card A is ON with no load:

- Since L<sub>SUPPLY</sub> >> L<sub>CARD-CARD</sub>, C<sub>IN</sub> of card B is charged from card A, resulting in negative I<sub>INA</sub>.

- There is an LC ring of both  $V_{INB}$ , and  $I_{INA}$ , which dampens out due to parasitic resistance.

- The transient on VINA is much smaller than the transient on  $V_{\text{INB}}$ , because  $L_{\text{CARD-CARD}}$  along with  $C_{\text{BULK}}$  provides filtering.

- I<sub>INA</sub> does not exceed the CB threshold of ~16 A and the gate voltage of card A stays high.

Figure 3. Adjacent Card Insertion, ILOAD,A = 0 A

Finally, the total input capacitance of the EVM ( $C_{IN}$ ) can be estimated from Figure 3. The period of the ring is ~ 200 ns.  $C_{IN}$  is charged from 0 V to 40 V in the first ¼ of the period and the peak current from card A to card B is 5 A. Using Equation 1,  $C_{IN}$  is estimated to be 3 nF. Given that the real input capacitor is 1 nF, the other 2 nF can be attributed to the parasitics of the board, the Hot Swap FET, and the input TVS.

$$C_{IN} \times \Delta V_{IN} = \int i \times dt \ge C_{IN} = \frac{50 \text{ ns} \times 5A/2}{40 \text{ V}} \sim 3 \text{ nF}$$

(1)

The behavior is similar when there is a load on card A, but this moves the  $I_{IN,A}$  waveform by the load current. Using maximum current is the worst case, because the maximum  $I_{IN,A}$  comes closest to the circuit breaker threshold.

Figure 4. Adjacent Card Insertion, I<sub>LOAD,A</sub> = 7.5 A

These tests were performed for several other conditions listed in the Table 2. Note that a lower  $L_{CARD-CARD}$  would result in ringing on  $V_{IN,A}$  that is higher amplitude and higher frequency. This could result in a maximum current going above the CB threshold and causing a nuisance trip.

| Table 2. | Test Result | ts for Adjacer | nt Card Insertion |  |

|----------|-------------|----------------|-------------------|--|

|          |             |                |                   |  |

| V <sub>IN</sub> | CL Setting | LOAD A | Gate Tripped? |

|-----------------|------------|--------|---------------|

| 48              | 50 mV      | 0 A    | No            |

| 65              | 50 mV      | 0 A    | No            |

| 40              | 50 mV      | 0 A    | No            |

| 48              | 50 mV      | 8 A    | No            |

| 48              | 26 mV      | 0 A    | No            |

| 40              | 26 mV      | 8 A    | No            |

# 1.4 Adjacent Card Removal

Removal of a card can also cause a transient on an adjacent card. Several test conditions were evaluated and are summarized in the table below.

| V <sub>IN</sub> | CL Setting | LOAD A | LOAD B | Gate Tripped? |

|-----------------|------------|--------|--------|---------------|

| 48              | 26 mV      | 0 A    | 8 A    | N             |

| 48              | 26 mV      | 8 A    | 8 A    | N             |

| 48              | 26 mV      | 0 A    | 11 A   | N             |

| 48              | 26 mV      | 8 A    | 12 A   | Y             |

#### Table 3. Test Results for Adjacent Card Removal

Figure 5 shows the waveform for a typical case. Here both cards are running close to full load (a little under current limit) and card B is removed. The following occurs:

- Since  $L_{SUPPLY} >> L_{CARD-CARD}$ ,  $I_{SUPPLY}$  continues to be ~ 16 A

- Most of the I<sub>SUPPLY</sub> goes into card A and I<sub>INA</sub> rises up to 14 A.

- 14 A is below the circuit breaker threshold and the gate of the FET stays high.

- I<sub>INA</sub> slowly returns to the original 8 A level. The di/dt is low, because L<sub>SUPPLY</sub> is large and the V<sub>L,Supply</sub> is small (< 1 V).</li>

Transients Experienced by Hot Swaps in a Backplane

Figure 5. Adjacent Card Removal (I<sub>LOAD,A</sub> = I<sub>LOAD,B</sub> ~8 A)

Figure 6 shows the waveform for an atypical case. Here the load current of card B is 13A, which is above the current limit of card A. This is not the case in most systems, but serves as a good example. The following occurs:

- Since  $L_{SUPPLY} >> L_{CARD-CARD}$ ,  $I_{SUPPLY}$  continues to be ~ 21 A.

- All of the  $I_{SUPPLY}$  goes into card A and  $I_{INA}$  rises up to 21 A.

- 21 A is above the circuit breaker threshold and the gate of the FET is quickly pulled down.

- When the gate is turned off, this causes a sudden interruption in I<sub>IN,A</sub> and the voltage on V<sub>INA</sub> spikes up followed by a ring.

Figure 6. Adjacent Card Removal (I<sub>LOAD,A</sub> = 8 A, I<sub>LOAD,B</sub> ~12 A)

# 2 The Response of LM5066 EVM to Transients

Section 1 focused on identifying the typical transients that can be seen by a Hot Swap in a backplane. In this section arbitrary transients are applied to the EVM to check its behavior.

# 2.1 Set-up for Transient Testing

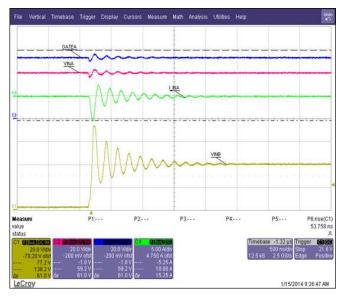

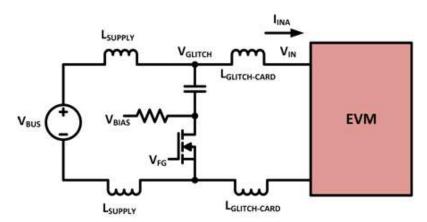

Two types of transient injection methods were used. The first one shown in Figure 7 relies on a power MOSFETs that is connected to a function generator. Since an electrical signal is used to generate the transient, this method is referred to as "Electrical Glitching".

$V_{BIAS}$  determines the amplitude of the transient injected into  $V_{GLITCH}$ . For example, if  $V_{BIAS} = 10$  V when the FET turns ON, the lower node of the capacitor goes to zero (a 10-V step), which results in a 10-V step on the  $V_{GLITCH}$  node. The frequency of the transient is determined by the LC time constant. Thus different glitch capacitors generate transients of a different frequency. With this set-up a variety of transients can be injected onto the EVM to find out which ones would make it "trip". The wire from  $V_{GLITCH}$  to  $V_{IN}$  was ~2" so that a current probe can be used in order to measure  $I_{INA}$ .

Figure 7. Set up for Electrical Glitching

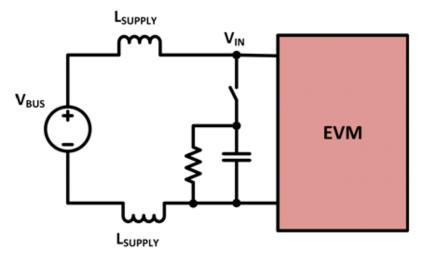

The second method relies on simply shorting a cap onto  $V_{IN}$ . A resistor is used to pre-bias the capacitor to 0 volts. The capacitor is connected directly on the  $V_{IN}$  of the EVM, which prevents the measurement of  $I_{INA}$ . However, this removes the  $L_{GLITCH-CARD}$  allowing for faster transients to be injected on the EVM. Since the transient is injected by physically connected the positive side of the cap to  $V_{IN}$ , this is referred to as "Mechanical Glitching".

Figure 8. Set up for Mechanical Glitching

# 2.2 Transient Testing Results with the EVM

Table 4 summarizes the results of the "Electrical Glitching" that was performed on the LM5066 EVM. The experiments were performed with a maximum load, since that is the worst case, because the transient adds on top of the DC input current. In general, a gate trip occurred when the maximum input current was around or above the circuit breaker threshold. Note that the threshold is lower for higher frequency transients that were generated with a lower size capacitor. This can attributed to the inductance of the sense resistors and some sensitivity of the part to common mode and will be described in the following sections.

| V <sub>IN</sub> | CL Setting | C <sub>GLITCH</sub> | LOAD A | V <sub>BIAS</sub> | Gate Tripped? | I <sub>IN,MAX</sub> |

|-----------------|------------|---------------------|--------|-------------------|---------------|---------------------|

| 48 V            | 26 mV      | 10 nF               | 8 A    | 35 V              | N             | 12.5 A              |

| 48 V            | 26 mV      | 10 nF               | 8 A    | 40 V              | Y             | 12.6 A              |

| 48 V            | 26 mV      | 100 nF              | 8 A    | 20 V              | N             | 15 A                |

| 48 V            | 26 mV      | 100 nF              | 8 A    | 25 V              | Y             | 19 A                |

| 48 V            | 26 mV      | 600 nF              | 8 A    | 15 V              | N             | 19 A                |

| 48 V            | 26 mV      | 600 nF              | 8 A    | 20 V              | Y             | 22 A                |

Table 4. Electrical Glitching Test Results on the EVM

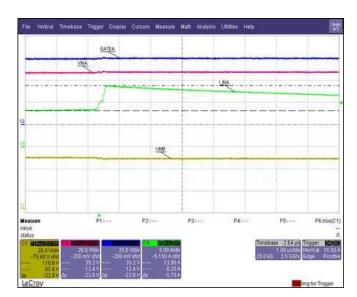

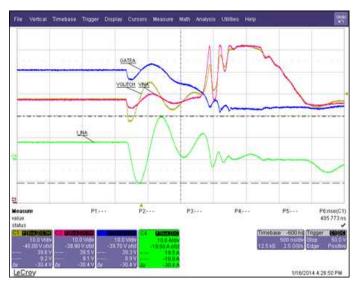

The waveform in Figure 9 is an example of the response of the LM5066 EVM to a transient generated with a 100 nF glitch capacitor and  $V_{BIAS} = 25$  V. The voltage glitch on  $V_{GLITCH}$  results in a current transient on  $I_{INA}$  due to  $C_{BULK}$ .  $I_{INA}$  exceeds the CB threshold, which results in the gate falling.

Figure 9. V<sub>IN</sub> Transient Generated by  $V_{BIAS}$  = 25 V and  $C_{GLITCH}$  = 100 nF

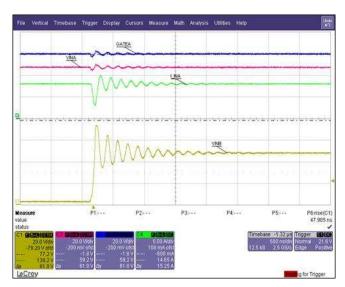

#### 2.3 Mechanical Glitching

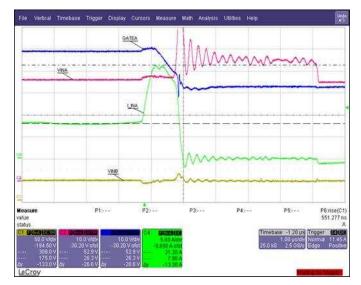

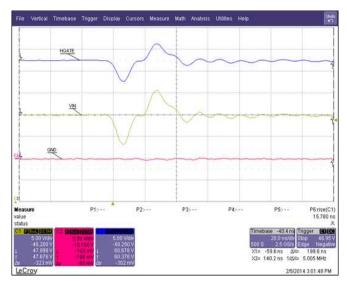

To test the EVM with very fast transients the L<sub>GLITCH-CARD</sub> has to be minimized. To accomplish this, a capacitor was directly hot-plugged on the V<sub>IN</sub> as shown in Figure 8. Unfortunately, the input current cannot be measured with this set-up. A 1- $\mu$ F ceramic capacitor was added on the output. As a result this helps to limit the transient on V<sub>IN</sub>, because 1  $\mu$ F >> 3 nF.

Note that every comparator has some susceptibility to high amplitude and fast common mode transients. The 1- $\mu$ F output capacitor serves to limit the common mode seen by comparator. Note that the V<sub>IN</sub> transient is not completely squashed due to impedance between V<sub>IN</sub> and C<sub>OUT</sub>. The theory is discussed further in the next section.

The result is shown in Figure 10. Note that there was no load current for this experiment and the voltage transient is roughly 7 V.

Figure 10. Mechanical Glitch With a 1-µF Cout

Additional experiments were performed and are shown in Table 5. Note that gate trips were observed when there was a load current present. This is consistent with previous results. Note that the addition of  $C_{OUT}$  does generate a current transient through  $R_{SENSE}$  creating a differential voltage which can result in the circuit breaker tripping. This is analyzed further in *Section 3*.

| V <sub>IN</sub> | CL Setting | C <sub>GLITCH</sub> | LOAD A | C <sub>OUT</sub> | Gate Tripped? |

|-----------------|------------|---------------------|--------|------------------|---------------|

| 48              | 26 mV      | 3 nF                | 0 A    | 1-µF ceramic     | N             |

| 48              | 26 mV      | 3 nF                | 8 A    | 1-µF ceramic     | Y             |

| 48              | 26 mV      | 8 nF                | 0 A    | 1-µF ceramic     | N             |

| 48              | 26 mV      | 8 nF                | 8 A    | 1-µF ceramic     | Y             |

## 3 Mitigating Nuisance Trips in Hot Swap Circuits

Managing the common mode and differential signal across  $V_{IN_K}$  and  $V_{SENSE}$  is the key to preventing nuisance trips in Hot Swap circuits. This section provides further theoretical insight along with experimental results to show how this can be accomplished.

# 3.1 Understanding Key Parasitics in the Hot Swap Circuit

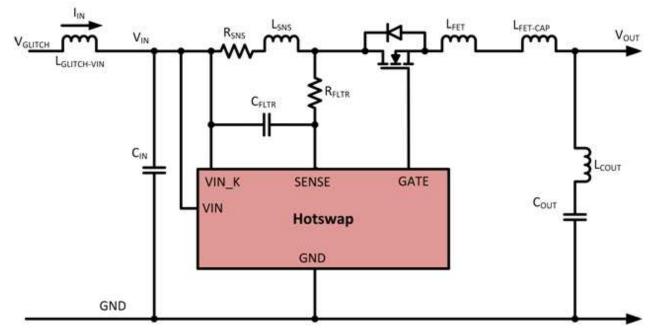

Figure 11 shows the key components and parasitic elements that need to be considered when evaluating the differential and common mode signal seen on  $V_{IN,K}$  and  $V_{SENSE}$ . The designer should keep the following in mind:

- L<sub>GLITCH,VIN</sub> is the inductance between the source of the transient (ie adjacent card) and the board under test. Larger L<sub>GLITCH,VIN</sub> helps decouple the transients between cards. It is a combination of parasitic inductance and the inductance of a series inductor (if added).

- The sense resistor has an inductance between 1 nH and 5 nH, which could add significantly to  $V_{IN_{-}K} V_{SENSE}$ , when large di/dt is present.

- $C_{OUT}$  is quite large and reduces the common mode seen on  $V_{IN,K}$  and  $V_{SENSE}$ . However, the series inductance from  $C_{OUT}$  to  $V_{SENSE}$  reduces its impact. It is effectively an inductor divider with  $L_{GLITCH,VIN}$ .

- Since the FET is ON, its resistance is very small and it is essentially a short. The FET inductance is not specified on all FETs, but is ~12 nH for a FET in a D2PACK (IRLR3110).

Figure 11. Hot Swap Circuit With Key Parasitics

# 3.2 Controlling the Differential Signal ( $V_{IN_{-}K} - V_{SENSE}$ )

To work around the differential signal that appears across  $R_{SNS}$ , use an RC filter as shown in Figure 11. Note that the SENSE pin will draw ~25 µA of current, which introduces a voltage offset into current monitoring. However, as long as a low  $R_{FLTR}$  is used this offset can be minimized.

Also note that adding a differential filter increases the response time of the Hot Swap to a short circuit. The RC value has to be tuned to optimize the short circuit response and the immunity to nuisance trips.

# 3.3 Controlling the Common Mode on V<sub>IN\_K</sub> and V<sub>SENSE</sub>

Controlling the common mode signal is trickier than the differential signal. It is tempting to use an RC network to filter the common mode. However, any mismatch in the filtering of  $V_{IN_K}$  and SENSE would result in a common mode to differential mode conversion exacerbating the problem.

For a given transient, using a larger  $C_{IN}$  would definitely reduce the perturbation on  $V_{IN}$  and SENSE. However,  $C_{IN}$  is hot-plugged so increasing its value would result in larger perturbations.

The following would help avoid nuisance trips from common mode signal on  $V_{INK}$  and  $V_{SENSE}$ :

- Minimize  $L_{FET-CAP}$ , by placing the  $C_{OUT}$  next to the FET.

- Minimize L<sub>CAP</sub>, by using a ceramic 1- $\mu$ F capacitor on C<sub>OUT</sub> in addition to any bulk electrolytic capacitor that is already used. Note that 1  $\mu$ F >> C<sub>IN</sub>, so it should absorb the transient introduced from an adjacent card insertion.

- Keep the sense resistor close to the FET to avoid additional parasitic inductance.

- Add a real inductor to increase L<sub>GLITCH-VIN</sub>. The saturation current of the inductor should be larger than the maximum load current to avoid saturation.

- Using a higher CB threshold by setting the CB/CL ratio bit to 1 (CB/CL ratio ~3.9) or using a CL = 50 mV.

# 3.4 Experimental Results

To test the proposed solutions the following settings were used on a TI evaluation board:

- C<sub>OUT</sub> = 1 µF. Ceramic capacitor was used to improve response to fast transients

- $R_{FLTR} = 0.3 \ \Omega$  and  $C_{FLTR} = 1 \ \mu F$  for a 300 ns time constant on the circuit breaker.

- Sense resistor of 2 mΩ (standard setting)

- CL setting of 26 mV and a load current of 11 A (close to max)

Then several tests were performed to evaluate the worst case conditions as shown in Table 6.

| Glitch Type                      | V <sub>IN</sub> | C <sub>GLITCH</sub> | Gate Tripped? |

|----------------------------------|-----------------|---------------------|---------------|

| Mechanical                       | 48              | 3 nF                | N             |

| Mechanical                       | 48              | 8 nF                | N             |

| Electrical – $V_{BIAS} = V_{IN}$ | 48              | 10 nF               | N             |

| Electrical – $V_{BIAS} = V_{IN}$ | 48              | 100 nF              | Ν             |

| Electrical – $V_{BIAS} = V_{IN}$ | 48              | 600 nF              | Y             |

#### Table 6. Test Results with Cout and Differential Filtering

The gate did not trip for neither of the mechanical glitches, which would be considered the worst case. The gate trip did occur when a 600 nF  $C_{GLITCH}$  was used. Note that hot-plugging a 600-nF capacitor on the bus is not a real system usage case, because the typical  $C_{IN}$  of the board is < 10 nF.

# 3.5 Considerations For Systems with Multiple Cards

Note that most systems will have more than 2 cards plugged in at a time. In this case, a transient caused by a card insertion/removal/fault is split up amongst the nearby cards. It is split based on the parasitic inductance of each card to the one that had an insertion/removal/fault. Therefore, the experiments shown in this report can be considered as "worst case condition" and a typical system would exhibit better performance.

#### 3.6 Ensuring that a Hot Swap Design Passes with Margin

Since nuisance trips are dependent on the system and layout Parasitics, it is hard to ensure that a given board design will pass all of the conditions desired by the user. The design needs to be tested in a real system and tweaked as necessary.

Many designers will want to ensure there is margin in their design. This can be accomplished with the procedure outlined in Table 7. In a typical usage case, the input capacitance of card A and card B is matched and could equal 3 nF. Also, the designer may set  $R_{FLTR} \times C_{FLTR} = 0.6 \mu s$ . The margin can be checked by performing a test in the right column. By doubling the  $C_{INB}$  the transient seen by card A is increased and by reducing the filtering time constant the sensitivity of card A to transients is also increased. Thus if the board passes this test, the designer will have confidence that the design is robust.

|                                      | Standard Usage Case | Checking Margin |

|--------------------------------------|---------------------|-----------------|

| C <sub>INA</sub>                     | 3 nF                | 3 nF            |

| C <sub>INB</sub>                     | 3 nF                | 6 nF            |

| Differential RC filter time constant | 0.6 µs              | 0.3 µs          |

| Table 7. Example | Test to Ensure | Margin with | Adjacent | <b>Card Insertion</b> |

|------------------|----------------|-------------|----------|-----------------------|

|                  |                |             |          |                       |

Some systems may require that a short circuit fault on a card does not cause a nuisance trip on any of the adjacent cards. Note that this is tough to pass and may require an input inductor. A similar procedure can be used to check margin for this test condition. This is shown in Table 8. The hot-short is applied to card B and using a longer time constant results in a slower response time of card B and a more severe transient on the bus. Using a shorter time constant on card A makes it more sensitive to transients. Again, passing this test case provides the designer with confidence that the design is robust.

#### Table 8. Example Test to Ensure Margin with Adjacent Card Hot-Short

|                                                | Standard Usage Case | Checking Margin |

|------------------------------------------------|---------------------|-----------------|

| C <sub>INA</sub>                               | 3 nF                | 3 nF            |

| C <sub>INB</sub>                               | 3 nF                | 3 nF            |

| Differential RC filter time constant on Card A | 0.6 µs              | 0.3 µs          |

| Differential RC filter time constant on Card B | 0.6 µs              | 1.2 µs          |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated