# Fully Differential Op Amps Made Easy

Bruce Carter

High Performance Linear

#### ABSTRACT

Fully differential op amps may be unfamiliar to some designers. This application report gives designers the essential information to get a fully differential design up and running.

| 1 | Introduction                                | 2 |

|---|---------------------------------------------|---|

| 2 | What Does Fully Differential Mean?          | 2 |

| 3 | How Is the Second Output Used?              | 3 |

|   | 3.1 Differential Gain Stages                |   |

|   | 3.2 Single-Ended to Differential Conversion |   |

|   | 3.3 Working With Terminated Inputs          | 5 |

| 4 | A New Function                              | 7 |

| 5 | Conclusions                                 | 8 |

| 6 | References                                  | 9 |

#### List of Figures

| 1 | Single-Ended Op Amp Schematic Symbol                                  | . 2 |

|---|-----------------------------------------------------------------------|-----|

| 2 | Fully Differential Op Amp Schematic Symbol                            | . 2 |

| 3 | Closing the Loop on a Single-Ended Op Amp                             | . 3 |

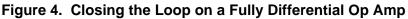

| 4 | Closing the Loop on a Fully Differential Op Amp                       | . 3 |

| 5 | Single Ended to Differential Conversion                               | . 4 |

| 6 | Relationship Between Vin, Vout+, and Vout-                            | . 5 |

| 7 | Fully Differential Amplifier Component Calculator                     | . 6 |

| 8 | Using a Fully Differential Op Amp to Drive an ADC                     | . 7 |

| 9 | Effect of V <sub>ocm</sub> on V <sub>out+</sub> and V <sub>out-</sub> | . 8 |

## 1 Introduction

Fully differential op amps may be intimidating to some designers, But op amps began as fully differential components over 50 years ago. Techniques about how to use the fully differential versions have been almost lost over the decades. However, today's fully differential op amps offer performance advantages unheard of in those first units.

This report does not attempt a detailed analysis of op amp theory; reference 1 covers theory well. Instead, this report presents just the facts a designer needs to get started, and some resources for further design assistance. After reading this document, a designer can approach a fully differential op amp design with confidence.

# 2 What Does Fully Differential Mean?

Single-ended op amps have two inputs—a positive and negative input—which are understood to be fully differential. They have a single output, which is referenced to system ground.

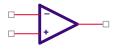

Figure 1. Single-Ended Op Amp Schematic Symbol

The op amp has two power supply inputs, which are connected to bipolar power supplies (equal and opposite positive and negative potentials), or a single potential, with a positive supply and a ground connected to the power supply pins. These power supply pins are often omitted from the schematic symbol, when power supply connections are implied elsewhere on the schematic.

Fully differential op amps add a second output:

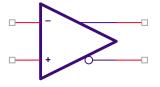

Figure 2. Fully Differential Op Amp Schematic Symbol

The output is fully differential—the two outputs are called *positive output* and *negative output*—similar terminology to the two inputs. Like the inputs, they are differential. The output voltages are equal, but opposite in polarity (referenced to the common-mode operating point of the circuit).

# 3 How Is the Second Output Used?

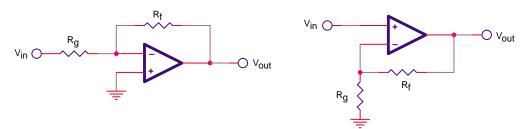

An op amp is used as a closed-loop device. Most designers know how to close the loop on a single-ended op amp:

Figure 3. Closing the Loop on a Single-Ended Op Amp

Whether the single ended op amp is used in an inverting or a noninverting mode, the loop is closed from the output to the inverting input.

#### 3.1 Differential Gain Stages

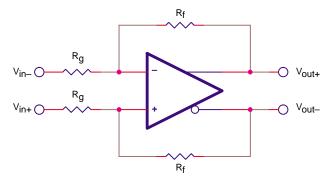

So, how is the loop closed on a fully differential op amp? If there are two outputs, both of them have to be operated closed loop. Therefore, the equivalent way of closing the loop on a fully differential op amp is:

Two identical feedback loops are required to close the loops for a fully differential op amp. If the loops are not matched, there can be significant second order harmonic distortion.

For a fully differential op amp, each feedback loop is an inverting feedback loop. Both polarities of output are available, so terms like *inverting* and *noninverting* are meaningless. Instead, think of the single-ended schematics in Figure 3. In both cases, the loop goes from the noninverting output to the inverting input, introducing a 180° phase shift. For the fully differential op amp, the top feedback loop has a 180° phase shift from the noninverting output to the inverting input, and the bottom feedback loop has a 180° phase shift from the inverting output to the noninverting input. Both feedback paths are therefore inverting. There is no *noninverting* fully differential op amp gain circuit.

The gain of the differential stage is:

$$\frac{V_{O}}{V_{I}} = \frac{R_{f}}{R_{g}}$$

(1)

#### 3.2 Single-Ended to Differential Conversion

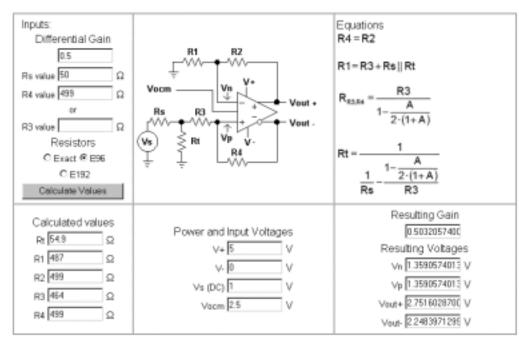

The schematic shown in Figure 4 is a fully differential gain circuit. Fully differential applications, however, are somewhat limited. Very often the fully differential op amp is used to convert a single-ended signal to a differential signal—perhaps to connect to the differential input of an A/D converter.

Figure 5. Single Ended to Differential Conversion

The two configurations shown in Figure 5 are equivalent. At first glance, they look identical, but they are not. The difference is that in the left configuration, the inverting input is used for signal and the noninverting input for reference. In the right configuration, the noninverting input is used for signal and the inverting input for reference. Either one works.

The gain of the single-ended to differential stage is:

$$\frac{V_{O}}{V_{I}} = \frac{R_{f}}{R_{g}}$$

(2)

The only difference between this configuration and the previous is that one side of the input voltage is referenced to ground.

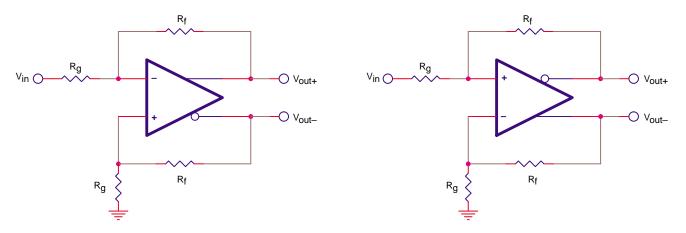

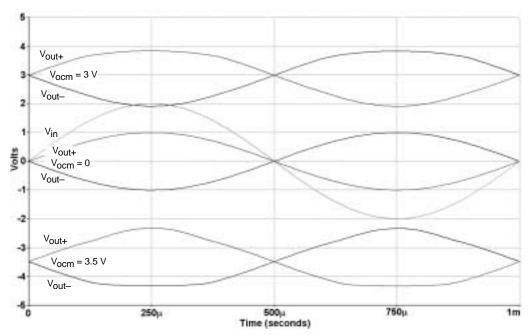

The dynamics of the gain are sometimes best described pictorially. Figure 6 shows the relationship between  $V_{in}$ ,  $V_{out+}$ , and  $V_{out-}$ .

Figure 6. Relationship Between Vin, Vout+, and Vout-

## 3.3 Working With Terminated Inputs

The design becomes more complicated if a single-ended input signal must be terminated. This upsets the balance of the loop, and changes the impedance. The design technique is anything but simple. There are two equations in two variables that interact, making design an interactive process. To simplify this difficult task for designers, Texas Instruments provides an on-line calculator on its web site. This tool can be accessed either through the *Analog and Mixed-Signal Knowledgebase*, or through the *Engineering Design Utilities* section on the *Analog and Mixed-Signal Mixed-Signal* portion of the TI web site.

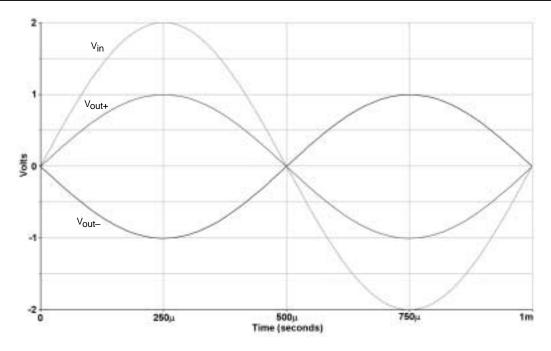

Figure 7 shows a screen shot of the fully differential amplifier component calculator.

FULLY DIFFERENTIAL AMPLIFIER COMPONENT CALCULATOR

#### Figure 7. Fully Differential Amplifier Component Calculator

The fully differential component calculator has six panes. Data entry is primarily made in the upper left pane, although the bottom middle pane contains some secondary entry fields.

The top middle pane contains the schematic for a terminated single-ended to fully differential conversion. Design equations are shown in the upper right hand pane. The equations for  $R_{R3,R4}$  and Rt are interrelated through the *A* parameter. The tool makes a preliminary calculation to get close to the correct values, and then it refines the calculation and *goal seek* to the final value. The execution time depends on the step size used in the goal seeking calculation, and therefore selecting *E96* resistor values executes much faster than *Exact* values. Execution times of several seconds or longer are possible, especially if gain is changed radically when *Exact* values is selected. The designer selects the desired gain and the impedance of the signal source (default value of 50  $\Omega$ ). The designer attempts to select both, only the last value entered is used for calculation.

The designer should initially try to select the value of R4, because it is often specified on the data sheet. The designer should experiment with R3 only if the recommended value of R4 does not yield an acceptable design (the tool has internal limits set to resistor values that make sense for real designs).

When the designer selects *Calculate Values*, the tool calculates resistor values in the bottom left pane and circuit simulation results in the bottom right pane. If the designer wishes, the power and input voltages can be changed in the bottom middle pane, and these affect the simulation results in the bottom right.

Note that this tool provides dc operating point only—it does not give ac simulation.

# 4 A New Function

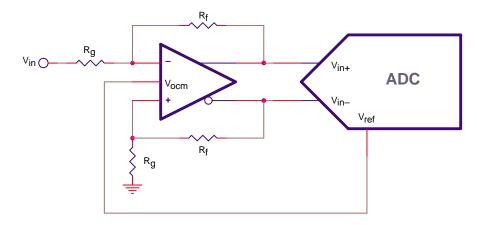

Texas Instruments fully differential op amps have an additional pin,  $V_{ocm}$ , which stands for *common-mode output voltage (level)*. The function of this pin can be either an input or an output, because its source is just a voltage divider off the power supply, but it is seldom used as an output. When it is used as an output, it corresponds to the common-mode voltage about which the  $V_{out+}$  and  $V_{out-}$  outputs swing.

The most common use of the V<sub>ocm</sub> pin is to set the output common-mode level of the fully differential op amp. This is a very useful function, because it can be used to match the common mode point of a data converter to which the fully differential amplifier is connected. High-precision/high-speed data converters often employ differential inputs and provide a reference output.

Figure 8. Using a Fully Differential Op Amp to Drive an ADC

The schematic of Figure 8 is simplified, and does not show compensation, termination, or decoupling components for clarity. Nevertheless, it shows the basic concept.

There are misconceptions associated with the  $V_{\mbox{\scriptsize ocm}}$  pin:

- **Misconception 1: The V<sub>ocm</sub> pin can be used as a third input.** The V<sub>ocm</sub> pin is not a *third signal input*. Texas Instruments continually receives requests to know the bandwidth of the V<sub>ocm</sub> *input*. This is not the intended use. The intended use of the V<sub>ocm</sub> pin is to allow an external voltage to set the common-mode point of the output of the fully differential op amp.

- **Misconception 2: The V<sub>ocm</sub> pin can be used to set the dc operating point.** Texas Instruments receives many customer inquiries about single supply operation of fully differential op amps, where the customer is attempting to use the V<sub>ocm</sub> pin to set the *half supply* reference. This invariably causes the circuit to draw excess current, and it can violate the input common mode range of the device. Proper dc operating point must be set with conventional op amp design techniques. Reference 2 describes the proper way to set the dc operating point of fully differential op amps.

- Misconception 3: The V<sub>ocm</sub> voltage level, reflected at the output, is affected by the stage gain. The common-mode output voltage is not affected by the values of R<sub>f</sub> and R<sub>g</sub>. The actual relation governing V<sub>ocm</sub> is:

$$V_{\text{ocm}} = \frac{\left(V_{\text{out}}+\right)+\left(V_{\text{out}}-\right)}{2}$$

(3)

The designer can think of V<sub>ocm</sub> in this way: as V<sub>ocm</sub> is shifted from zero to higher values, the dc portion of V<sub>out+</sub> and V<sub>out-</sub> shifts by the same amount. The differential voltage between the two outputs, however, remains constant—determined by the values of  $R_f$  and  $R_q$ .

The value of V<sub>ocm</sub> affects the maximum output voltage swing. The maximum output voltage swing happens when V<sub>ocm</sub> is at zero. Adding 1 Vdc to V<sub>ocm</sub> decreases the output voltage swing range by one volt. For example, the voltage swing range for THS4131 is 3.7 V, –4.3 V when the supply voltage is  $\pm 5$  V. This means that the output signal may reach 1.3 V below the upper rail and 0.7 V above the negative rail.

Consider the case when the input signal is 2 VPP, and the gain of the circuit is one:

- If V<sub>ocm</sub> is zero, the V<sub>out+</sub> and V<sub>out-</sub> outputs swing to ±1 Vac, and since the voltage rail is 3.7 Vdc, there is plenty of headroom on both rails, and the design works.

- If V<sub>ocm</sub> is raised to 3 Vdc, then both outputs attempt to swing between 2 V and 4 V, and alternately hit the positive rail, clipping at 3.7 V.

- Similarly, if V<sub>ocm</sub> is lowered to –3.5 Vdc, then both outputs attempt to swing between –2.5 V and –4.5 V, and alternately hit the negative rail, clipping at –4.3 V

These three cases are combined in Figure 9.

Figure 9. Effect of Vocm on Vout+ and Vout-

# 5 Conclusions

Fully Differential op amps, although not a new type of component, are new to most designers. Techniques to use these components are similar to the techniques used to design inverting single-ended op amps. The number of outputs and feedback paths is increased to 2, doubling the number of passive components needed to support a fully differential design. The V<sub>ocm</sub> pin of the device is a new concept, which facilitates connection to a reference output from a data converter.

## 6 References

- 1. Fully-Differential Amplifiers, Texas Instruments, SLOA054

- 2. Differential Op Amp Single-Supply Design Techniques, Texas Instruments, SLOA072

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated