# Application Clip Standard Linear and Logic P

## **SN74VMEH22501** Universal Bus Transceiver for the VMEbus<sup>™</sup> Backplane

#### **Overview of VMEbus Evolution**

For over 20 years the VMEbus has served the market well. Like all well-designed technologies, the VMEbus has gone through several performance improvements. Each improvement has been compatible with the previous one, thus allowing for the longevity of the VMEbus technology.

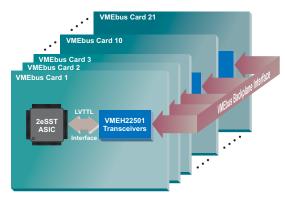

The table (top right) shows the latest transfer protocol, 2eSST (two-edge source synchronous transfer), has an achievable performance of 320 MBps. The only logic transceiver in the industry today that can transmit clean signals at 2eSST speeds down a standard VMEbus is the SN74VMEH22501.

#### Co-Development Effort Between Key Players

Texas Instruments and the VITA Standards Organization teamed to co-develop the 2eSST transceiver that meets the needs of the VMEbus community. This initiated the VME Renaissance, which is an industry-wide effort created by Motorola to boost VME technology acceptance.

| Date | Backplane                 | Protocol | Data Transfer<br>Protocol               | Theoretical<br>Performance<br>(MBps) | Achievable<br>Performance<br>(MBps) |

|------|---------------------------|----------|-----------------------------------------|--------------------------------------|-------------------------------------|

| 1981 | VME<br>3-row P1 and P2    | BLT      | Asynchronous 32-bit<br>4-edge handshake | 40                                   | ~20                                 |

| 1989 | VME64                     | MBLT     | Asynchronous 64-bit<br>4-edge handshake | 80                                   | ~40                                 |

| 1996 | VME64x<br>5-row P1 and P2 | 2eVME    | Asynchronous 64-bit<br>2-edge handshake | 160                                  | 8x ~70                              |

| 1999 | No change                 | 2eSST    | Synchronous 64-bit<br>No handshake      | 320                                  | ~320                                |

An 8x improvement in achievable performance from the VME64 backplane to 2eSST is now possible without any changes to the existing legacy backplane architecture.

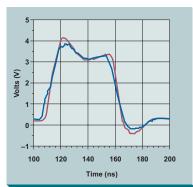

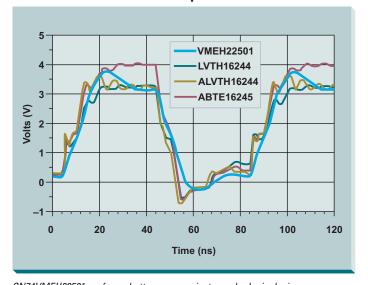

### Extensive Testing/Simulation Efforts Pay Back With Incredible Results

The proof is in the signal integrity. The waveforms presented are actual signals taken from a standard VME backplane under the tough, fully loaded case where the transmitting

signal is generated from the center of the backplane.

Typical drivers such as ABT, ABTE or LVT are incapable of producing well-behaved, monotonic signals on a standard VME backplane.

#### SN74VMEH22501 VMEbus Transceiver Features and Benefits

| OH ITHELECOL THEE DUO HANDOON OF TOURIST WHITE DONORS |                                                                                                                                                                                            |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Features                                              | Benefits                                                                                                                                                                                   |  |  |  |  |

| Backward compatible to existing logic                 | Can be used in systems where older backplane technologies such as ABT, ABTE and LVT are still present. New cards can use VME technology while the rest of the backplane remains unchanged. |  |  |  |  |

| V <sub>CC</sub> = 3.3 V                               | Functionality in most popular supply voltage in the industry.                                                                                                                              |  |  |  |  |

| Output edge control                                   | Reduces electromagnetic interference (EMI).                                                                                                                                                |  |  |  |  |

| Pseudo-ETL input thresholds                           | Improved noise margins over traditional logic such as ABTE.                                                                                                                                |  |  |  |  |

| 5-V-tolerant I/Os                                     | Ability to interface with 5-V devices.                                                                                                                                                     |  |  |  |  |

| Bus hold (3A ports)                                   | Eliminates the need for pull-up/-down resistors when bus is idle.                                                                                                                          |  |  |  |  |

| Series damping resistors                              | Improves ground bounce on the 3A port and Y outputs.                                                                                                                                       |  |  |  |  |

| Flow-through architecture                             | Facilitates printed circuit board layout.                                                                                                                                                  |  |  |  |  |

| Multiple ground and supply pins                       | Minimizes high-speed switching noise.                                                                                                                                                      |  |  |  |  |

| 64-mA I <sub>OL</sub> specification                   | Permits backward compatibility to older VMEbus pull-up termination for open-drain outputs.                                                                                                 |  |  |  |  |

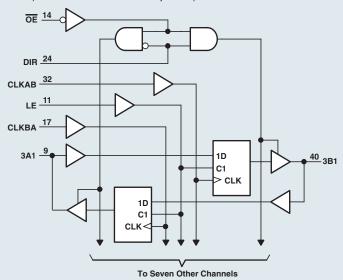

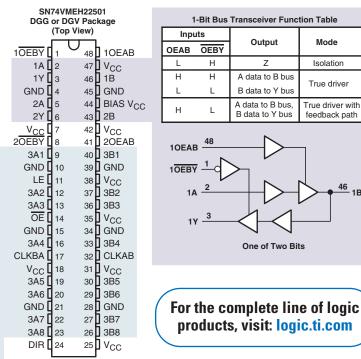

#### SN74VMEH22501 VMEbus Transceiver — Pin Configurations and Functionality

| UBT Transceiver Function Table |     |       |    |                  |                             |  |

|--------------------------------|-----|-------|----|------------------|-----------------------------|--|

|                                | Inp | uts   |    | Output           | Mode                        |  |

| ŌĒ                             | LE  | CLKAB | 3A | 3B               |                             |  |

| Η                              | Х   | Χ     | Х  | Z                | Isolation                   |  |

| L                              | L   | Н     | Χ  | В0               | Latebard stayons of OA data |  |

| L                              | L   | L     | X  | B <sub>0</sub> § | Latched storage of 3A data  |  |

| L                              | Н   | Х     | L  | L                | True transparent            |  |

| L                              | Н   | X     | Н  | Н                |                             |  |

| L                              | L   |       | L  | L                | Clasical starons of 04 data |  |

| L                              | L   |       | Н  | Н                | Clocked storage of 3A data  |  |

3A-to-3B data flow is shown; 3B-to-3A data flow is similar, but uses CLKBA. Output level before the indicated steady-state input conditions were established, provided that CLKAB was high before LE went low. § Output level before the indicated steady-state input conditions were established.

**Ordering Information**

| TA        | Package |     |               | Orderable<br>Part Number | Top-Side<br>Marking |

|-----------|---------|-----|---------------|--------------------------|---------------------|

|           | TSSOP   | DGG | Tape and reel | SN74VMEH22501DGGR        | VMEH22501           |

| 0 to 85"C | TVSOP   | DGV | Tape and reel | SN74VMEH22501DGVR        | VK501               |

|           | VFBGA   | GQL | Tape and reel | SN74VMEH22501GQLR        | VK501               |

Package drawings, standard packing quantities, thermal data. symbolization and PCB design guidelines are available at: www.ti.com/sc/package

#### **Transceiver Performance Comparison**

SN74VMEH22501 performs better even against popular logic devices on a standard backplane with Thevenin termination.

#### For More Information about SN74VMEH22501

Product Folder:

www.ti.com/sc/device/SN74VMEH22501

Data Sheet:

www-s.ti.com/sc/techlit/sces357

Application Report:

www-s.ti.com/sc/techlit/scea028

VME Home Page:

www.ti.com/vme

For up-to-date information to support your design and development needs, visit:

support.ti.com

This publication contains forward-looking statements that involve a number of risks and uncertainties. These "forward-Inis publication contrains forward-looking statements that movine a unimber of risks and uncertainties. These forward-looking statements' are intended to qualify for the safe harbor from liability established by the Private Securities Litigation Reform Act of 1995. These forward-looking statements generally can be identified by phrases such as TI or its management "believes," "expects," "anticipates," "foresees," "forecasts," "estimates" or other words or phrases of similar import. Similarly, such statements herein that describe the company's products, business strategy, outlook, objectives, plans, intentions or goals also are forward-looking statements. All such forward-looking statements are subject to certain risks and uncertainties that could cause actual results to differ materially from those in forward-looking statements. Please refer to Tl's most recent Form 10-K for more information on the risks and uncertainties that could materially affect future results of operations. We disclaim any intention or obligation to update any forward-looking statements as a result of developments occurring after the date of this publication

46 1B

**Available**

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated